一种适用于SiC MOSFET的桥臂互锁电路

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及互锁电路领域,具体涉及一种适用于SiC MOSFET的桥臂互锁电路。

背景技术

在电力电子行业中,半桥、全桥、推挽结构应用极其广泛,而此类电路的同桥臂的两个功率管在任何情况下都不能同时导通,一般的处理方式是在驱动信号上添加死区时间。

而对于日渐兴起的SiC MOSFET器件来说,SiC MOSFET工作频率高,导致死区时间小,当死区时间小于SiC MOSFET本身的延时时间时,则会发生上下桥臂导通,同时因为SiCMOSFET器件的工作频率高,容易受到外界的电磁干扰,造成驱动信号电平发生偏转,导致上下桥臂同时导通,损坏SiC MOSFET功率器件。

发明内容

本发明的目的在于提供一种适用于SiC MOSFET的桥臂互锁电路,通过在SiCMOSFET的驱动芯片前加入桥臂互锁电路,使用与非门芯片74LS00和与门芯片74LS08,通过逻辑电路,确保半桥、全桥、推挽等电路上下桥臂不会同时导通。设计所需器件少,无需占用太大的PCB板空间,同时可以保护SiC MOSFET不被损坏。

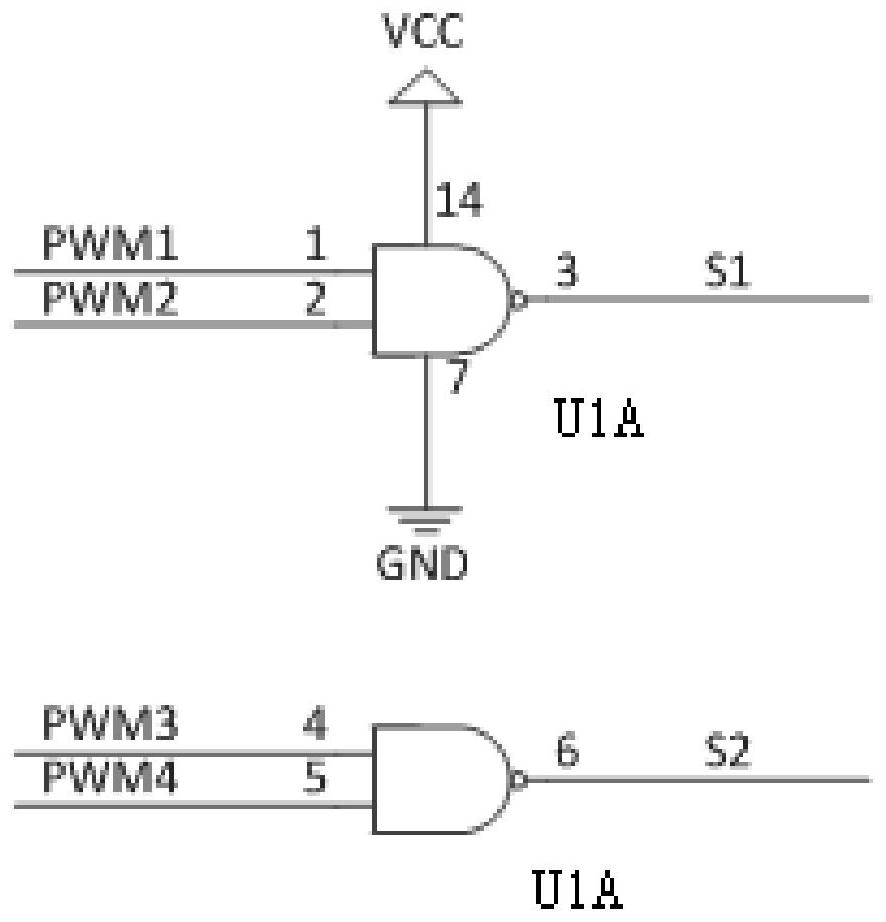

一种适用于SiC MOSFET的桥臂互锁电路,包括基础全桥电路和4路PWM波信号,4路PWM波信号中PWM1信号和PWM2信号为左桥臂两个SiC MOSFET的驱动信号,PWM3信号各PWM4信号为右桥臂两个SiC MOSFET的驱动信号,还包括与非门芯片U1A和与门芯片U1B,所述与非门芯片U1A的1号引脚连接PWM1信号,2号引脚连接PWM2信号,4号引脚连接PWM3信号,5号引脚连接PWM4信号,所述非门芯片U1A的3号引脚输出一路使能信号S1,6号引脚输出二路使能信号S2;

所述与门芯片U1B的1号引脚连接PWM1信号, 2号引脚连接一路使能信号S1,两者经过与逻辑运算得到的第一驱动信号OPWM1通过3号引脚输出;

所述与门芯片U1B的4号引脚接PWM2信号,5号引脚连接一路使能信号S1,两者经过与逻辑运算得到的第二驱动信号OPWM2通过6号引脚输出;

所述与门芯片U1B的9号引脚接PWM3信号,10号引脚连接二路使能信号S2,两者经过与逻辑运算得到的第三驱动信号OPWM3通过8号引脚输出;

所述与门芯片U1B的12号引脚接PWM4信号,13号引脚连接二路使能信号S2,,两者经过与逻辑运算得到的第四驱动信号OPWM2通过11号引脚输出。

优选的,所述第一驱动信号OPWM1需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动左桥臂上管SiC MOSFET的通断。

优选的,所述第二驱动信号OPWM2需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动左桥臂下管SiC MOSFET的通断。

优选的,所述第三驱动信号OPWM3需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动右桥臂上管SiC MOSFET的通断。

优选的,所述第四驱动信号OPWM4需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动右桥臂下管SiC MOSFET的通断。

优选的,所述与非门芯片U1A采用型号为74LS00的与非门芯片,所述与门芯片U1B采用型号为74LS08的与门芯片。

本发明的优点在于:通过在SiC MOSFET的驱动芯片前加入桥臂互锁电路,使用与非门芯片74LS00和与门芯片74LS08,通过逻辑电路,确保半桥、全桥、推挽等电路上下桥臂不会同时导通。设计所需器件少,无需占用太大的PCB板空间,同时可以保护SiC MOSFET不被损坏。

附图说明

图1为本发明装置中与非门芯片U1A的连接示意图;

图2为本发明装置中与门芯片U1B的连接示意图;

具体实施方式

为使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施方式,进一步阐述本发明。

如图1至图2所示,本发明以全桥电路为基础设计,共4路PWM波PWM1、PWM2、PWM3、PWM4,分别驱动左右桥臂的上下管,PWM1、PWM2为左桥臂两个SiC MOSFET的驱动信号,PWM3、PWM4为右桥臂两个SiC MOSFET的驱动信号。

与非门芯片U1A74LS00的1、2、4、5号引脚分别连接PWM1、PWM2、PWM3、PWM4,PWM1、PWM2经过与非逻辑运算得到的使能信号S1通过74LS00的3号引脚输出,PWM3、PWM4经过与非逻辑运算得到的使能信号S2通过74LS00的6号引脚输出。

与门芯片U1B74LS08的1号引脚连接PWM1信号,2号引脚连接74LS00生成的S1使能信号,两者经过与逻辑运算得到的驱动信号OPWM1通过74LS08的3号引脚输出,OPWM1需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动左桥臂上管SiC MOSFET的通断。

与门芯片U1B74LS08的4号引脚连接PWM2信号,5号引脚连接74LS00生成的S1使能信号,两者经过与逻辑运算得到的驱动信号OPWM2通过74LS08的6号引脚输出,OPWM2需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动左桥臂下管SiC MOSFET的通断。

与门芯片U1B74LS08的9号引脚连接PWM3信号,10号引脚连接74LS00生成的S2使能信号,两者经过与逻辑运算得到的驱动信号OPWM3通过74LS08的8号引脚输出,OPWM3需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动右桥臂上管SiC MOSFET的通断。

与门芯片U1B74LS08的12号引脚连接PWM4信号,13号引脚连接74LS00生成的S2使能信号,两者经过与逻辑运算得到的驱动信号OPWM4通过74LS08的11号引脚输出,OPWM4需要连接SiC MOSFET的驱动芯片的输入引脚,进而驱动右桥臂下管SiC MOSFET的通断。

正常情况下PWM1、PWM2的逻辑电平为00、01、10时,两者经过与非逻辑之后得到的S1使能信号为高电平1,PWM1、PWM2再与S1信号经过与逻辑生成SiC MOSFET的驱动信号OPWM1、OPWM2,此时OPWM1、OPWM2输出与PWM1、PWM2同相位,电平状态为00、01、10,不会发生桥臂上下管同时导通;当控制方式出现问题或者电路受到干扰导致PWM1、PWM2的逻辑电平变成11时,与非得到的S1信号为低电平0,生成的OPWM1、OPWM2逻辑电平为00,输出电平状态发生翻转,可以保证桥臂上下管不会同时导通。

另一组信号PWM3、PWM4情况与上述PWM1、PWM2现象一致,两者与非之后得到S2使能信号,再分别与PWM3、PWM4进行相与,得到OPWM3、OPWM4,同样不会发生桥臂上下管同时导通的情况。

下表是PWM1、PWM2、PWM3、PWM4、S1、S2、OPWM1、OPWM2、OPWM3、OPWM4。

等信号的真值表,如表1所示,

表1适用于SiC MOSFET的桥臂互锁电路真值表

在不加桥臂互锁电路时,桥臂上下管同时导通,即PWM1、PWM2电平状态为11的情况有4种,序号分别为13、14、15、16,当发生上述情况时,在添加桥臂互锁电路后,输出的驱动信号OPWM1、OPWM2的电平状态为00;同理,PWM3、PWM4电平状态为11的情况有4种,序号分别为4、8、12、16,当发生上述情况时,在添加桥臂互锁电路后,输出的驱动信号OPWM3、OPWM4的电平状态为00。可以确保同一桥臂上下管的SiC MOSFET不会发生直通现象,提高系统的可靠性。

具体实施方式及原理:

正常情况下PWM1、PWM2的逻辑电平为00、01、10时,两者经过与非逻辑之后得到的S1使能信号为高电平1,PWM1、PWM2再与S1信号经过与逻辑生成SiC MOSFET的驱动信号OPWM1、OPWM2,此时OPWM1、OPWM2输出与PWM1、PWM2同相位,电平状态为00、01、10,不会发生桥臂上下管同时导通;当控制方式出现问题或者电路受到干扰导致PWM1、PWM2的逻辑电平变成11时,与非得到的S1信号为低电平0,生成的OPWM1、OPWM2逻辑电平为00,输出电平状态发生翻转,可以保证桥臂上下管不会同时导通。

另一组信号PWM3、PWM4情况与上述PWM1、PWM2现象一致,两者与非之后得到S2使能信号,再分别与PWM3、PWM4进行相与,得到OPWM3、OPWM4,同样不会发生桥臂上下管同时导通的情况。

基于上述,本发明通过在SiC MOSFET的驱动芯片前加入桥臂互锁电路,使用与非门芯片74LS00和与门芯片74LS08,通过逻辑电路,确保半桥、全桥、推挽等电路上下桥臂不会同时导通。设计所需器件少,无需占用太大的PCB板空间,同时可以保护SiC MOSFET不被损坏。

由技术常识可知,本发明可以通过其它的不脱离其精神实质或必要特征的实施方案来实现。因此,上述公开的实施方案,就各方面而言,都只是举例说明,并不是仅有的。所有在本发明范围内或在等同于本发明的范围内的改变均被本发明包含。

- 一种适用于SiC MOSFET的桥臂互锁电路

- 一种适用于三电平IGBT桥臂的PWM互锁保护电路