半导体器件的蜂窝布局

文献发布时间:2023-06-19 18:27:32

技术领域

本文所公开的主题涉及半导体器件、例如碳化硅(SiC)功率器件,包括场晶体管(例如MOSFET、DMOSFET、UMOSFET、VMOSFET等)、绝缘栅双极晶体管(IGBT)、绝缘基MOS控制晶闸管(IBMCT)、结型场效应晶体管(JFET)和金属半导体场效应晶体管(MESFET)。

背景技术

这一节旨在向读者介绍可与本公开的各个方面相关的领域的各个方面。在为读者提供背景信息以便于对本公开的各个方面的更好理解方面,本论述被认为是有帮助的。相应地,应当理解,要以此来阅读这些陈述,而不是认可现有技术。

功率转换装置广泛地用于现代电气系统,以将电力从一种形式转换成另一种形式供负载消耗。许多功率电子系统利用各种半导体器件和组件,例如晶闸管、二极管和各种类型的晶体管(例如,金属氧化物半导体场效应晶体管(MOSFET)、结型栅场效应晶体管(JFET)、绝缘栅双极晶体管(IGBT)和其他适当晶体管)。

具体对于高频、高电压和/或高电流应用,与对应硅(Si)器件相比,利用宽带隙半导体(例如碳化硅(SiC)、氮化铝(AlN)、氮化镓(GaN)等)的器件在高温操作、降低的导通电阻和较小的管芯大小方面可提供多个优点。相应地,宽带隙半导体器件向功率转换应用(包括例如配电系统(例如在电力网中)、发电系统(例如在太阳能和风力转换器中)以及消费产品(例如电动车辆、电器、电力供应装置等))提供优点。

发明内容

在一实施例中,系统包括半导体器件单元,其设置在碳化硅(SiC)半导体层的表面。半导体器件单元包括:漂移区,具有第一导电类型;阱区,具有第二导电类型,设置成与漂移区相邻;源区,具有第一导电类型,设置成与阱区相邻,沟道区,具有第二导电类型,设置成与源区相邻并且接近表面;以及体接触件区,具有第二导电类型,设置在阱区的一部分之上,其中体接触件区没有在半导体器件单元中居中。该器件单元包括分段源和体接触件(SSBC:segmented source and body contact),其设置在表面的一部分之上,其中SSBC包括:体接触件部分,其设置在体接触件区之上;以及源接触件部分,设置成与体接触件区相邻并且在源区的一部分之上,其中源接触件部分没有完全包围SSBC的体接触件部分。

在一实施例中,系统包括蜂窝半导体器件布局,其具有设置在碳化硅(SiC)半导体层的表面的多个半导体器件单元。多个蜂窝半导体器件单元各包括:漂移区,具有第一导电类型;阱区,具有第二导电类型,设置成与漂移区相邻;源区,具有第一导电类型,设置成与阱区相邻。各器件单元的阱区包括设置成接近表面的体接触件区,以及各器件单元的源区包括设置成接近表面并且接近体接触件区的源接触件区。多个蜂窝半导体器件单元各包括不对称分段源和体接触件(SSBC),其设置在表面的一部分之上,其中,不对称SSBC包括设置在半导体器件单元的体接触件区之上的体接触件部分以及设置成与体接触件部分相邻并且在半导体器件单元的源接触件区之上的源接触件部分,其中不对称SSBC的源接触件部分没有完全包围不对称SSBC的体接触件部分。

在一实施例中,一种制作在碳化硅(SiC)半导体层的表面的半导体器件单元的方法包括在SiC半导体层的表面之上形成半导体器件单元的分段源和体接触件(SSBC)。SSBC包括体接触件部分,其设置在半导体层的表面之上并且接近半导体器件单元的体接触件区,其中体接触件部分没有与半导体器件单元的中心对齐。SSBC还包括源接触件部分,其设置在半导体层的表面之上并且接近半导体器件单元的源接触件区,其中至少一个源接触件部分仅部分包围SSBC的体接触件部分。

技术方案1:一种系统,包括:

半导体器件单元,设置在碳化硅(SiC)半导体层的表面,其中所述半导体器件单元包括:

漂移区,具有第一导电类型;

阱区,具有第二导电类型,设置成与所述漂移区相邻;

源区,具有所述第一导电类型,设置成与所述阱区相邻;

沟道区,具有所述第二导电类型,设置成与所述源区相邻并且接近所述表面;以及

体接触件区,具有所述第二导电类型,设置在所述阱区的一部分之上,其中所述体接触件区没有在所述半导体器件单元中居中;以及

分段源和体接触件(SSBC),设置在所述表面的一部分之上,其中所述SSBC包括:

体接触件部分,设置在所述体接触件区之上;以及

源接触件部分,设置成与所述体接触件区相邻并且在所述源区的一部分之上,其中所述源接触件部分没有由所述SSBC的所述体接触件部分完全包围。

技术方案2:如技术方案1所述的系统,其中,所述SSBC具有少于与所述表面垂直的对称的两个不同镜平面。

技术方案3:如技术方案1所述的系统,其中,所述源接触件部分的第一节段沿所述体接触件部分的第一侧设置。

技术方案4:如技术方案3所述的系统,其中,所述SSBC具有延长的矩形形状。

技术方案5:如技术方案3所述的系统,其中,所述源接触件部分的第二节段沿所述体接触件部分的第二侧设置。

技术方案6:如技术方案5所述的系统,其中,所述SSBC具有正方形形状或者六边形形状。

技术方案7:如技术方案1所述的系统,其中,所述SSBC的所述体接触件部分的至少一侧设置成接近没有设置在所述SSBC之下的所述源区的一部分。

技术方案8:如技术方案1所述的系统,其中,所述体接触件区基本上是菱形形状。

技术方案9:如技术方案1所述的系统,其中,所述体接触件区基本上是方形形状。

技术方案10:如技术方案1所述的系统,其中,所述半导体器件单元包括场晶体管、绝缘栅双极晶体管(IGBT)、绝缘基MOS控制晶闸管(IBMCT)、结型场效应晶体管(JFET)或者金属半导体场效应晶体管(MESFET)。

技术方案11:一种系统,包括:

蜂窝半导体器件布局,包括设置在碳化硅(SiC)半导体层的表面的多个半导体器件单元,其中所述多个蜂窝半导体器件单元各包括:

漂移区,具有第一导电类型;

阱区,具有第二导电类型,设置成与所述漂移区相邻,其中所述阱区包括设置成接近所述表面的体接触件区;

源区,具有所述第一导电类型,设置成与所述阱区相邻,其中所述源区包括设置成接近所述表面并且接近所述体接触件区的源接触件区;以及

不对称分段源和体接触件(SSBC),设置在所述表面的一部分之上,其中所述不对称SSBC包括:

体接触件部分,设置在所述半导体器件单元的所述体接触件区之上;以及

源接触件部分,设置成与所述体接触件部分相邻并且在所述半导体器件单元的所述源接触件区之上,其中所述不对称SSBC的所述源接触件部分没有完全包围所述不对称SSBC的所述体接触件部分。

技术方案12:如技术方案11所述的系统,其中,所述蜂窝半导体器件布局配置成使得(2L

技术方案13:如技术方案12所述的系统,其中,所述蜂窝半导体器件布局提供比具有与所述蜂窝半导体器件布局相同的L

技术方案14:如技术方案11所述的系统,其中,所述蜂窝半导体器件布局配置成使得((4L

技术方案15:如技术方案14所述的系统,其中,所述蜂窝半导体器件布局相对于具有与所述蜂窝半导体器件布局相同的L

技术方案16:如技术方案11所述的系统,其中,所述蜂窝半导体器件布局包括布置成行、成列或者两者的所述多个半导体器件单元,并且所述行或列相互偏离。

技术方案17:如技术方案11所述的系统,其中,各不对称SSBC没有与其相应半导体器件单元的中心对齐。

技术方案18:一种在碳化硅(SiC)半导体层的表面处制作半导体器件单元的方法,包括:

在所述SiC半导体层的所述表面之上形成半导体器件单元的分段源和体接触件(SSBC),其中所述SSBC包括:

体接触件部分,设置在所述半导体层的所述表面之上并且接近所述半导体器件单元的体接触件区,其中所述体接触件部分没有与所述半导体器件单元的中心对齐;以及

源接触件部分,设置在所述半导体层的所述表面之上并且接近所述半导体器件单元的源接触件区,其中所述源接触件部分没有完全包围所述SSBC的所述体接触件部分。

技术方案19:如技术方案18所述的方法,其中,所述SSBC具有少于与所述表面垂直的对称的两个平面。

技术方案20:如技术方案18所述的方法,其中,所述SSBC没有与所述表面垂直的对称的两个平面。

附图说明

通过参照附图阅读以下详细描述,将会更好地了解本发明的这些及其他特征、方面和优点,附图中,相似标号在附图中通篇表示相似部件,附图包括:

图1是典型平面MOSFET器件的示意图;

图2是示出典型MOSFET器件的各个区域的电阻的示意图;

图3A是按照本方式的实施例、具有对称分段源和体接触件(SSBC)区的半导体器件单元的俯视图;

图3B是具有对称SSBC区的器件单元的另一个实施例的俯视图,并且示出放大的制造缺陷;

图3C是按照本方式的实施例、具有带对称分段源和体接触件(SSBC)的矩形器件单元的SSBC蜂窝器件布局的俯视图;

图4是图3C所示的SSBC蜂窝器件布局实施例的一部分的截面图;

图5是图3C所示的SSBC蜂窝器件布局实施例的另一个部分的截面图;

图6是具有带对称SSBC的分段矩形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图7是具有带对称SSBC的延长六边形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图8是具有带不对称SSBC的矩形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图9是具有带不对称SSBC的六边形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图10是具有带不对称SSBC的正方形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图11是具有带不对称SSBC的六边形器件单元的SSBC蜂窝器件布局的另一个实施例的顶视图;

图12A是包括连续源接触件带和连续体接触件带的非蜂窝带器件布局的一实施例的俯视图;

图12B是包括具有分段源/体接触件带的非蜂窝带阶梯器件布局的一实施例的俯视图;

图12C是包括没有SSBC的正方形器件单元的蜂窝器件布局的一实施例的顶视图;

图13是示出归一化沟道宽度(W

图14是示出归一化JFET密度(D

图15是示出归一化沟道宽度(W

图16是示出归一化JFET密度(D

具体实施方式

下面将描述一个或多个具体实施例。在提供这些实施例的简要描述的过程中,在本说明书中并非描述实际实现的所有特征。应当理解,在任何这种实际实现的开发中,如同任何工程或设计项目中那样,必须进行许多实现特定的判定以便实现开发人员的特定目标,例如符合系统相关和业务相关限制,这些限制可对每个实现而改变。此外,应当理解,这种开发工作可能是复杂且费时的,但仍然是获益于本公开的技术人员进行的设计、制作和制造的日常事务。

在介绍本公开的各个实施例的元件时,限定词“一”、“一个”、“该”和“所述”预计表示存在元件的一个或多个。术语“包含”、“包括”和“具有”预计包含在内,并且表示可存在除了列示元件之外的附加元件。另外,应当理解,本公开的“一个实施例”或“一实施例”的说法不是要被理解为排除同样结合了所述特征的附加实施例的存在。如本文用来描述特征的形状、位置或对齐的术语“基本上”意在包含理想或目标形状、位置和对齐以及产生于半导体制作过程的可变性的不完善实现的形状、位置和对齐,如本领域的技术人员可理解。术语“对称”或“对称的”在本文中可用来描述具有与半导体表面的平面垂直定位的对称的至少两个镜平面的分段源/体接触件区、分段源/体接触件或器件单元。术语“不对称”或“不对称的”在本文中可用来描述具有少于与半导体表面的平面垂直定位的对称的两个镜平面的分段源/体接触件区、分段源/体接触件或器件单元。术语“居中”在本文中可用来描述其中体接触件区基本上分别设置在分段源/体接触件区、分段源/体接触件或器件单元的中心的分段源/体接触件区、分段源/体接触件或器件单元。术语“偏心”或词语“没有居中”在本文中可用来描述其中体接触件区不是基本上分别设置在分段源/体接触件区、分段源/体接触件或器件单元的中心的分段源/体接触件区、分段源/体接触件或器件单元。另外,本文中描述为在半导体层的“表面”所设置或制作的半导体器件单元意在包括半导体器件单元,其具有设置在半导体层的大部分中的部分、设置成接近半导体层的表面的部分、设置成与半导体层的表面齐平的部分和/或设置在半导体层的表面上方或顶部的部分。

现代功率电子器件的基本构建块之一是场效应晶体管(FET)器件。例如,图1示出平面n沟道场效应晶体管、即DMOSFET、以下称作MOSFET器件10的有源单元。可以理解,为了更清楚地示出MOSFET器件10的某些组件以及以下所述的其他器件,可省略某些通常理解的设计元素(例如顶部金属化、钝化、边缘端接等)。图1的所示MOSFET器件10包括半导体层2(例如碳化硅半导体层),其具有第一表面4和第二表面6。半导体层2包括:漂移区16,具有第一导电类型(例如n型漂移层16);阱区18,与漂移区相邻并且接近第一表面,阱区具有第二导电类型(例如p阱18)。半导体层2还包括与阱区18相邻的源区20,源区具有第一导电类型(例如n型源区20)。栅绝缘层24设置在半导体层2的第一表面4的一部分上,以及栅电极26设置在栅绝缘层24上。半导体层2的第二表面6是衬底层14,以及漏极接触件12沿衬底层14设置在器件10的底部。源/体接触件22设置在半导体层2的顶部,部分覆盖源区20和阱/体区18。在操作期间,适当的栅电压(例如处于或超过MOSFET器件10的阈值电压(V

如图2所示,MOSFET器件10的各个区域各可具有关联电阻以及MOSFET器件10的总电阻(例如通态电阻R

有鉴于以上所述,当前实施例针对实现改进半导体器件性能的蜂窝器件设计和布局。具体来说,为了使器件通态传导损耗降低或者为最小(例如使Rds(on)为最小),可期望降低MOSFET器件10的组件的电阻。在某些情况下,一个或多个电阻组件可主导传导损耗,以及解决这些因素能够显著影响R

如图2所示,MOSFET器件10的接触件22(其一般提供到源电极的欧姆连接)设置在n+区域20的一部分以及p阱区或p+体区18的一部分之上。接触件22一般是金属界面,其包括位于MOSFET器件10的这些半导体部分与金属源电极之间的一个或多个金属层。具体来说,MOSFET器件10的n+区20中设置在接触件22下面的部分在本文中可称作MOSFET器件10的源接触件区42。此外,MOSFET器件10的p阱区或p+体区18中设置在接触件22(其能够是以比p阱区18的其余部分要高的水平经过p+掺杂的)下面的部分在本文中可称作MOSFET器件10的体接触件区44。为了一致起见,接触件22的部分在本文中可基于半导体器件中设置在接触件22下面的部分来指定。例如,接触件22中设置在体接触件区44上方的部分在本文中可称作接触件22的体接触件部分22A。类似地,接触件22中设置在MOSFET器件10的源接触件区42上方的部分在本文中可称作接触件22的源接触件部分22B。

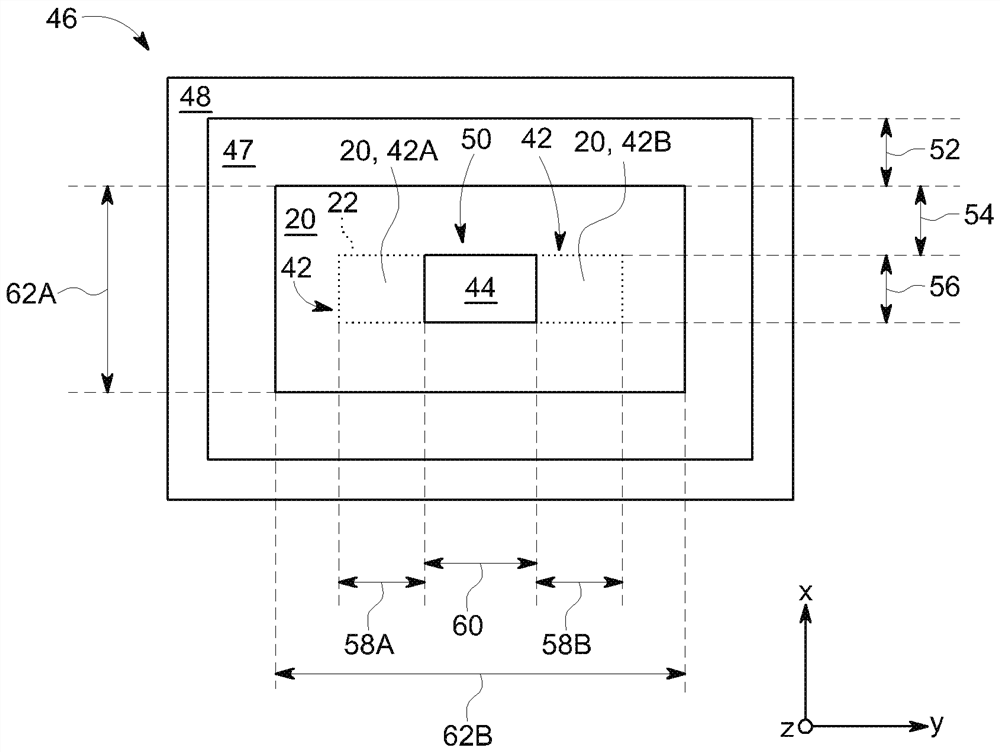

有鉴于以上所述,图3A是可实现如上所述的降低通态传导损耗的矩形半导体器件单元46(例如MOSFET半导体器件单元46)的一实施例的俯视图或平面图。可以理解,对于图3A,器件单元46的接触件22的最终位置示为轮廓线(即,虚线矩形22),以便示范将设置在接触件22下面的器件单元46的层。例如,所示器件单元46包括矩形体接触件区44,其设置在器件单元46的中间。器件单元42的体接触件区44由n+区20来包围,n+区20又由半导体器件单元46的n沟道区47来包围。另外,所示半导体器件单元46包括结型场效应晶体管(JFET)区48,其包围器件单元46的p沟道区47。

可以理解,如图3A所示,n+部分20中设置在接触件22下面的部分用作器件单元46的源接触件区42的部分42A和42B。因此,器件单元46中设置在接触件22之下的面积(即,体接触件区44连同源接触件区42的两个部分42A和42B)在本文中可一般称作分段源和体接触件(SSBC)区50。类似地,接触件22一旦被形成则在本文中可一般称作分段源和体接触件(SSBC)22。在图3A所示的半导体器件46的SSBC区50中,应当注意,体接触件区44仅由源接触件区42的部分42A和42B部分(即,不是完全)包围。换言之,在某些实施例中,源接触件区42(例如源接触件区42的部分42A和42B)可描述为沿少于体接触件区44的全部侧面(例如边缘、下面)设置。例如,在某些实施例中,源接触件区42的部分可描述为沿少于体接触件区44的六个侧面、少于五个侧面、少于四个侧面、少于三个侧面、少于二个侧面或者仅沿一个侧面来定位;或者源接触件可描述为沿少于体接触件区的整个周长来设置。另外,所示器件单元46可描述为具有设置在体接触件区44的相对侧上的源接触件区42的部分42A和42B。因此,当前所公开的SSBC设计使单元大小为最小,并且增加每单位单元的导通区(例如沟道、JFET、扩展)的密度。

可以理解,对于图3A所示的实施例,半导体器件单元46、SSBC区50和/或SSBC 22可描述为居中和/或对称的。例如,器件单元46、SSBC区50和/或SSBC 22可描述为居中,因为所示体接触件区44设置在SSBC区50的中心以及半导体器件单元46的中心。此外,一旦形成SSBC 22,SSBC 22的体接触件部分也将在图3A所示的体接触件区之上设置在器件单元46的中心。作为补充或替代,半导体器件单元46、SSBC区50和/或SSBC 22可描述为基于对称的多个镜平面是对称的,其中对称的镜平面与包含器件单元46的半导体表面垂直定向(即,沿与x-y平面垂直的z轴来定向)。例如,如图3A所示,半导体器件单元46、SSBC区50和SSBC 22具有沿z轴所定向的对称的两个镜平面:第一个是设置在器件单元46的中心的x-y平面,以及第二个是设置在器件单元46的中心的y-z平面,其两者均匀地对分器件单元46、SSBC区50和SSBC 22。如以下针对图3B所述,在某些实施例中,器件单元46因制造变化和公差而可具有少于理想对齐和/或特征定义。对于这类实施例,可以理解,目标结构(即,预计基于设计来实现的结构)在本文中可被理解为居中和/或对称的,即使如所制造的器件单元46的实际结构可包括基于制作过程的限制的不规则性。例如,如以下针对图3B所述,在某些实施例中,体接触件区44可略微偏离器件单元46的中心,SSBC 22可能没有与沟道区48完全,体接触件区44可略微延伸到SSBC 22的上方或下面,等等。但是,甚至当现实世界制造因制作过程所引入的变化而可偏离目标结构时,器件单元46也仍然可被认为基于目标结构是居中和/或对称的。

图3A还示范所示器件单元46的尺寸。例如,图3A示出沟道长度(L

还可理解,通过图3A所示虚线矩形22所表示的SSBC 22的最终位置示范接触件22的理想(例如完全)对齐以及理想(例如完善)特征定义。也就是说,对于图3A的器件46,接触件22的长度一般与n+区20的长度完全平行地延伸。此外,器件46的源接触件区44基本上没有在SSBC 22之上或下面延伸。可以注意,虽然示出特征的理想对齐和特定形状以简化论述,但是本方式并不局限于这些特定形状、尺寸或对齐。因此,虽然理想或完全对齐的器件(例如目标器件结构)在本文中一般示出和论述,但是应当注意,在某些实施例中,本方式的器件单元(例如器件单元46)的SSBC(例如SSBC 22)可因制造过程中允许的公差而没有理想或完全对齐,如图3B所示。

例如,图3B示出本方式的器件46的一实施例,其示范接触件22的不太理想(例如不完善)对齐以及不太理想(例如不完善)特征定义。如图3B所示,在某些实施例中,基于半导体制作中使用的对齐技术的限制,SSBC 22的长度可能没有与n+区20的长度完全平行(例如有意或无意偏移1°、2°、3°、4°或5°或者以上)。如图3B所示,在某些实施例中,基于半导体制作中使用的对齐的限制,SSBC 22可略微在源接触件区44上方或下面延伸,或者源接触件区44可略微在SSBC 22上方或下面延伸。例如,在某些实现中,SSBC 22可在源接触件区44之上和/或下面延伸超出少于W

图3C是包括如上所述实现降低通态传导损耗的分段源和体接触件(SSBC)蜂窝器件布局72A的一实施例的半导体表面70(例如SiC外延半导体层)的俯视图或平面图。所示SSBC蜂窝布局72A包括多个MOSFET器件单元46、例如以上所述的图3A的器件单元46。具体来说,图3C中的各所示器件单元46包括如以上针对图3A所述设置在基础分段源和体接触件(SSBC)区50(未示出)之上的分段源和体接触件(SSBC)22。也就是说,与图3A不同,图3C所示的SSBC 22示为实线,其隐藏如上所述的基础分段源和体接触件(SSBC)区50。各所示SSBC22包括体接触件部分22A以及两个源接触件部分22B(其在一些实施例中具有相等尺寸(例如对称)或者可具有不同尺寸(例如不对称))。对于图3C所示的器件46,SSBC 22的体接触件部分22A仅部分(即,不完全)由SSBC 22的源接触件部分22B包围。换言之,SSBC 22的源接触件部分22B示为设置在少于SSBC 22的体接触件部分22A的所有侧面上(例如仅二个侧面上)。例如,对于具有不同成形的SSBC 22的实施例,SSBC 22的源接触件部分22B的部分可沿少于SSBC 22的体接触件部分22A的六个侧面、少于五个侧面、少于四个侧面、少于三个侧面、少于二个侧面或者仅沿一个侧面定位。

图3C还示范所示SSBC器件布局72A的特定尺寸。例如,图3C对于SSBC器件布局72A的所示实施例示出JFET区的宽度(W

图4是沿图3C的线条4-4所截取的MOSFET器件单元布局72A的一部分的截面图90。具体来说,截面图90示范在形成栅电极26、介电层24和SSBC 22之后的MOSFET器件单元器件布局72A的一部分。如图3C所示,线条4-4穿过SSBC 22的体接触件部分22A,其设置在MOSFET器件单元46的SSBC区50的体接触件区44之上,如以上针对图3A所述。相应地,对于图4所示的实施例,SSBC 22的体接触件部分22A设置在p阱区18的表面处的p+体接触件区44之上(例如与其物理和电接触)。对于所示实施例,SSBC 22的体接触件部分22A没有设置在截面图90中的n+区20之上(例如与其物理或电接触)。但是,在其他实施例中,接触件22的体接触件部分22A可有意地或者因半导体制作过程的限制而部分设置在n+区20之上(例如与其有限地物理或电接触)。

图5是沿线条5-5所截取的图3C的MOSFET器件单元布局72A的截面图100。如同图4一样,图5的截面图100示范在形成栅电极26、介电层24和SSBC 22之后的MOSFET器件单元布局72A。如图3C所示,线条5-5穿过SSBC 22的源接触件部分22B,其设置在MOSFET器件单元46的SSBC区50的源接触件区42的部件42A之上,如以上针对图3A所述。相应地,对于图5所示的实施例,SSBC 22的源接触件部分22B设置在n+区20之上(例如与其物理和电接触)。因此,对于所示截面图100,SSBC 22的源接触件部分22B没有设置在截面图100中的p阱区18或者体接触件区44之上(例如与其物理和电接触)。

图6是包括SSBC器件布局72B的另一个实施例的半导体衬底70的俯视图或平面图。与图3C所示的SSBC器件布局72A相似,图6所示的SSBC器件布局72B包括多个MOSFET器件单元46,其如上所述具有设置在基础SSBC区50(未示出)之上的SSBC 22。也就是说,如以上针对图3A所述,SSBC 22包括设置在各器件单元46的体接触件区44之上的体接触件部分22A,并且还包括设置在源接触件区42的部分42A和42B之上的源接触件部分22B。此外,所示器件单元46还包括其他特征(例如JFET区48、沟道区47、n+区20),如上所述。因此,对于图6的SSBC器件布局72B,设置在每个SSBC 22之下,SSBC区50具有在少于所有侧面上由源接触件区42A和42B所包围(例如,没有完全包围)的体接触件区44,如以上针对图3A所述。相应地,对于图6所示的SSBC器件布局72B,每个SSBC 22具有在少于所有侧面上由一个或多个源接触件部分22B所包含(例如,没有完全包围)的体接触件部分22A。

另外,如图6所示,器件布局72B的器件单元46、SSBC 22和基础SSBC区(未示出)可描述为居中,因为体接触件部分22A(和基础体接触件区)设置在器件单元46的中心。作为补充或替代,这些特征可描述为是对称的,因为器件布局72B的器件单元46、SSBC 22和基础SSBC区(未示出)具有对称的至少两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。例如,所示器件单元46各包括至少对称的两个镜平面:作为垂直对分各器件单元46的z-y平面的第一镜平面,以及作为水平对分各器件单元46的z-x平面的第二镜平面。

与图3C所示的SSBC器件布局72A相似,图6所示SSBC器件布局72B的MOSFET器件单元46设置成行110。但是,与图3C所示SSBC器件布局72A不同,图6中的MOSFET器件单元的每行110偏移或交错距离112。SSBC器件布局72B的水平间距111和垂直间距113也在图6中示出。可以理解,图6的交错设计实现p阱区18的角附近以及还有定位在JFET区的中心之上的栅极氧化物24中降低的电场,如图4和图5所示。相应地,与图3C中的布局相比,图6的交错设计可实现改进阻断电压(VB)和器件可靠性。

图7是包括SSBC器件布局72C的另一个实施例的半导体衬底70的俯视图或平面图。与图3B和图6所示的SSBC器件布局72A-B相似,图7所示的SSBC器件布局72C包括多个MOSFET器件单元118。SSBC器件布局72C的水平间距120和垂直间距123也在图7中示出。此外,MOSFET器件单元118的每个包括上述SSBC 22,其设置在SSBC区50之上(如以上针对图3A所述)。类似地,设置在每个SSBC 22之下,SSBC区50(未示出)包括在少于所有侧面上由源接触件区42A和42B所包围(例如没有完全包围)的体接触件区44,如以上在图3A中所述。

另外,如图7所示,器件布局72C的器件单元118、SSBC 22和基础SSBC区(未示出)可描述为居中,因为体接触件部分22A(和基础体接触件区)设置在器件单元118的中心。作为补充或替代,这些特征可描述为是对称的,因为器件布局72C的器件单元118、SSBC 22和基础SSBC区(未示出)具有对称的至少两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。例如,所示器件单元118各包括至少对称的两个镜平面:作为垂直对分各器件单元118的z-y平面的第一镜平面,以及作为水平对分各器件单元118的z-x平面的第二镜平面。

图7所示的MOSFET器件单元1118各包括n+掺杂区121,其将SSBC区22与MOSFET器件单元118的每个的沟道区122分隔。所示MOSFET器件单元118还包括包围沟道区122的JFET区124。与图3A、图3C和图6所示的MOSFET器件单元46不同,图7所示的MOSFET器件单元118具有延长(例如伸长或扩大)的六边形形状和“蜂房”单元布置,其实现p阱区18附近以及还有在JFET区的中心上方的栅极氧化物24中的更低电场。可以理解,相对于没有利用当前SSBC设计的其他六边形器件单元布局,SSBC 22和基础SSBC区50实现降低的器件间距123。

图8是包括SSBC器件布局72D的又一个实施例的半导体衬底70的俯视图或平面图。图8所示的SSBC器件布局72D包括多个矩形MOSFET器件单元130,其相互之间以特定偏移132设置,各包括分段源和体接触件(SSBC)134。SSBC器件布局72D的水平间距133和垂直间距135也在图8中示出。对于所示实施例,通过将SSBC 134与MOSFET器件单元130的每个的p沟道区138分隔的n+掺杂区136来包围SSBC 134。所示MOSFET器件单元130还包括包围p沟道区138的JFET区140。

图8所示的SSBC 134的每个包括体接触件部分134A,其设置在SSBC 134的源接触件部分134B旁边(例如与其紧邻或相邻)。SSBC 134的源接触件部分134B沿少于SSBC 134的体接触件部分134A的所有侧面(例如没有完全被包围、沿一个侧面、沿少于二个侧面、沿少于三个侧面所设置)来设置。类似地,在每个SSBC 134下面,基础SSBC区(未示出)包括源接触件区,其沿少于体接触件区的所有侧面(例如,没有完全包围,沿一个侧面、沿少于二个侧面、沿少于三个侧面所设置)来设置。

另外,器件布局72D的器件单元130、SSBC 134和基础SSBC区(未示出)可描述为偏心,因为体接触件部分134A(和基础体接触件区)没有设置在器件单元130的中心。作为补充或替代,这些特征可描述为是不对称的,因为器件布局72D的器件单元130、SSBC 134和基础SSBC区(未示出)具有少于对称的两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。实际上,所示器件单元130各仅包括对称的一个镜平面,其设置在对分器件单元130的每个的z-y平面中。

图9是包括SSBC器件布局72E的又一个实施例的半导体衬底70的俯视图或平面图。图9所示的SSBC器件布局72E包括多个延长(例如伸长或扩大)的六边形MOSFET器件单元150,其相互之间以特定间距152来设置。SSBC器件布局72E的垂直间距153也在图9中示出。与图8的MOSFET器件单元130相似,图9的所示MOSFET器件单元150的每个包括SSBC 134。每个SSBC 134包括体接触件部分134A,其设置在SSBC 134的源接触件部分134B旁边(例如与其紧邻或相邻)。如上所述,源接触件部分134B沿少于所示SSBC 134的每个的体接触件部分134A的所有侧面(例如没有完全被包围、沿一个侧面、沿少于二个侧面、沿少于三个侧面所设置)来设置。类似地,在每个SSBC 134下面,基础SSBC区(未示出)包括源接触件区,其沿少于体接触件区的所有侧面(例如,没有完全包围,沿一个侧面、沿少于二个侧面、沿少于三个侧面所设置)来设置。

另外,器件布局72E的器件单元150、SSBC 134和基础SSBC区(未示出)可描述为偏心,因为体接触件部分134A(和基础体接触件区)没有设置在器件单元150的中心。作为补充或替代,这些特征可描述为是不对称的,因为器件布局72E的器件单元150、SSBC 134和基础SSBC区(未示出)具有少于对称的两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。实际上,所示器件单元150各仅包括对称的一个镜平面,其设置在对分器件单元150的每个的z-y平面中。

对于图9的所示布局72E,通过将SSBC区134与MOSFET器件单元150的每个中的p沟道区156分隔的n+掺杂区154来包围SSBC 134。所示MOSFET器件单元150还包括包围p沟道区156的JFET区158。可以理解,在某些实施例中,图9所示的六边形MOSFET器件单元150和“蜂房”单元布置实现p阱区18的角附近以及还有在JFET区的中心上方的栅极氧化物24中的更低电场,如图4和图5所示。此外,相对于没有利用当前SSBC设计的其他六边形器件单元布局,SSBC 134实现降低的器件间距153。

图10是包括SSBC器件布局72F的又一个实施例的半导体衬底70的俯视图或平面图。图10所示的SSBC器件布局72F包括多个正方形MOSFET器件单元160,其相互之间以特定偏移162设置。SSBC器件布局72F的水平间距161和垂直间距163也在图10中示出。器件单元60的每个包括分段源和体接触件(SSBC)164,其设置在分段源和体接触件(SSBC)区(未示出)之上。通过将SSBC区164与MOSFET器件单元160的每个的p沟道区170分隔的n+掺杂区168来包围SSBC 164。所示MOSFET器件单元160还包括包围p沟道区170的JFET区172。

图10所示的SSBC 164各包括体接触件部分164A,其设置在源接触件区164B旁边(例如与其紧邻或相邻)。SSBC 164的源接触件部分164B沿少于SSBC 164的体接触件部分164A的所有侧面(例如没有完全被包围、沿其二个侧面、沿少于其三个侧面、沿少于其四个侧面)来设置。具体来说,图10的SSBC 164包括体接触件部分164A,其在二个侧面上通过“L”形源接触件部分164B来接触。换言之,源接触件部分164B仅部分包围或围绕每个SSBC 164的体接触件部分164A。可以理解,在某些实施例中,图10所示的正方形MOSFET器件单元160可在沟道区170的增加周边和/或JFET区172的增加密度方面提供优于其他MOSFET器件单元形状(例如没有SSBC区164的设计)的优点。

另外,器件布局72F的器件单元160、SSBC 164和基础SSBC区(未示出)可描述为偏心,因为体接触件部分164A(和基础体接触件区)没有设置在器件单元160的中心。作为补充或替代,这些特征可描述为是不对称的,因为器件布局72F的器件单元160、SSBC 164和基础SSBC区(未示出)具有少于对称的两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。实际上,所示器件单元150各仅包括对称的一个镜平面,其沿以对角线对分器件单元160的每个的z轴定向。

图11是包括SSBC器件布局的又一个实施例的半导体衬底70的俯视图或平面图。图11所示的SSBC器件布局72G包括多个六边形MOSFET器件单元180,各包括分段源和体接触件(SSBC)182。另外,SSBC器件布局72F的MOSFET器件单元180相互之间以特定间隔183(例如,垂直间距=正六边形形状的水平间距)来设置。对于所示实施例,通过将SSBC 182与MOSFET器件单元180的每个的沟道区190分隔的n+区188来包围SSBC 182的每个。所示MOSFET器件单元180还包括包围p沟道区190的JFET区192。

图11所示的SSBC 182各包括体接触件部分182A,其设置在源接触件部分182B旁边(例如与其紧邻或相邻)。SSBC 182的源接触件部分182B沿少于SSBC 182的体接触件部分182A的所有侧面(例如没有完全被包围、沿其二个侧面、沿少于其三个侧面或者沿少于其四个侧面)来设置。可以理解,图11中的SSBC 182的形状和定位只是作为示例来提供。例如,如所示,SSBC 182定位在各六边形器件单元180的中心,并且包括风筝形状体接触件部分182A和臂章形状源接触件部分182B。在其他实施例中,体接触件部分182A和源接触件部分182B的形状和/或相对大小例如根据接触电阻和器件设计要求可以是不同的。还可以理解,在某些实施例中,图11所示的六边形MOSFET器件单元180可在沟道区190的增加周边和/或JFET区192的增加密度方面提供优于矩形或正方形形状MOSFET器件单元46、130和160的优点。器件布局72G还实现p阱区18的角附近以及还有在JFET区的中心上方的栅极氧化物24中的较低电场。此外,相对于没有利用当前SSBC设计的其他六边形器件单元布局,SSBC 182实现降低的器件间距。

另外,器件布局72G的器件单元180、SSBC 182和基础SSBC区(未示出)可描述为偏心,因为体接触件部分182A(和基础体接触件区)没有设置在器件单元180的中心。作为补充或替代,这些特征可描述为是不对称的,因为器件布局72G的器件单元180、SSBC 182和基础SSBC区(未示出)具有少于对称的两个镜平面,其与半导体表面的平面垂直设置(即,沿z轴设置)。实际上,所示器件单元180各仅包括对称的一个镜平面,其沿以对角线对分器件单元180的每个的z轴定向。

可以理解,所公开的SSBC蜂窝器件布局实施例72A-G实现优于其他器件布局和器件单元设计的性能优点。为了进行比较,另一种器件布局的示例在图12中示出,其是带状器件布局194(即,非蜂窝布局)的俯视图或平面图。图12A的所示带状布局194包括:沟道区195、n+区196、源接触件区197、体接触件区198和JFET区199。可以理解,源接触件区197和体接触件区198形成为沿图12A的所示带状布局194的半导体的表面的连续带。另一种器件布局的示例在图12B中示出,其是具有分段源/体接触件的带状阶梯器件布局200(即,非蜂窝布局)的俯视图或平面图。所示布局200包括:沟道区202、n+区204、分段源/体接触件206(包括体接触件部分206A和源接触件部分206B)和JFET区210。图12B还示出带状阶梯器件布局200的尺寸,包括:沟道长度(L

有鉴于以上所述,SSBC蜂窝器件布局72A-G的当前所公开实施例通过提供比其他器件布局要大的沟道宽度(例如更大沟道周边),来实现优于器件布局和器件单元设计的性能优点。例如,等式1描述由图3A和图3C所示的当前所公开SSBC蜂窝器件布局72A(通过“SSBC”下标所示)所提供的沟道宽度(W

作为另一示例,等式3描述由当前所公开SSBC蜂窝器件布局72A(通过“SSBC”下标所示)所提供的沟道宽度(W

等式1

等式2

等式3

等式4

当前所公开的蜂窝器件布局实施例72A-G还可通过提供比其他器件布局要大的JFET区密度,来实现优于其他器件布局和器件单元设计的性能优点。例如,等式5描述由当前所公开SSBC蜂窝器件布局72A(通过“SSBC”下标所表示)所提供的JFET区密度(例如,图3C中示为A

通过另一示例,等式7描述由当前所公开SSBC蜂窝器件布局72A(通过“SSBC”下标所表示)所提供的JFET区密度(例如,图3C中示为A

等式5

等式6

等式7

等式8

图13是示出具有三个不同沟道长度的器件的等式1(即,图3C的SSBC蜂窝器件布局72A的沟道宽度(W

图14是示出具有三个不同沟道长度的器件的等式5(即,图3C的SSBC蜂窝器件布局72A的JFET密度,其归一化成图12B的带状阶梯器件布局200的JFET密度)的图表290。具体来说,图14所示的图表290包括表示具有0.3 μm的沟道长度(L

图15是示出具有三个不同沟道长度的器件的等式3(即,图3C的SSBC蜂窝器件布局72A的沟道宽度(W

图16是示出具有三个不同沟道长度的器件的等式7(即,图3C的SSBC蜂窝器件布局72A的JFET密度,其归一化成图12C的正方形蜂窝布局240的JFET密度)的图表310。具体来说,图16所示的图表310包括表示具有0.3 μm的沟道长度(L

本发明的技术效果包括蜂窝器件设计和布局,其实现改进的半导体器件性能。具体来说,当前实施例通过提供增加的沟道宽度和/或增加的沟道密度以降低通道电阻,并且通过提供增加的JFET密度以降低JFET区组件的电阻,来降低器件传导损耗(例如使R

本书面描述使用包括最佳模式的示例来公开本发明,并且还使本领域的技术人员能够实施本发明,包括制作和使用任何装置或系统,以及执行任何结合方法。本发明的专利范围由权利要求书来定义,并且可包括本领域的技术人员想到的其他示例。如果这类其他示例具有与权利要求书的文字语言完全相同的结构元件,或者如果它们包括具有与权利要求书的文字语言的非实质差异的等效结构元件,则它们意在落入权利要求书的范围之内。