一种肖特基二极管、制备方法及芯片

文献发布时间:2023-06-19 18:29:06

技术领域

本申请属于半导体技术领域,尤其涉及一种肖特基二极管、制备方法及芯片。

背景技术

电子信息产业作为高新技术产业,在扩大社会就业、推动经济转型升级、增强国际竞争力和维护国家安全等方面扮演着更加重要的角色。功率二极管是电路系统的关键部件,现已经被广泛应用在高频逆变器、数码产品、发电机、电视机等民用产品和卫星接收装置、导弹及飞机等各种先进武器控制系统以及仪器仪表设备的军用场合。

通常应用的有普通整流二极管、肖特基二极管、PN二极管等,其中,肖特基整流管由于具有较低的通态压降、较大的漏电流、反向恢复时间几乎为零等优点,应用非常广泛。

肖特基二极管是利用金属与半导体接触形成的金属-半导体结原理制作的一种二极管。肖特基二极管比PN结二极管具有更低的功耗、更大的电流以及超高速的优点,因此,在电子学器件中受到青睐。

但是,现有的肖特基二极管存在击穿电压较低的问题。

发明内容

为了解决上述技术问题,本申请实施例提供了一种肖特基二极管、制备方法及芯片,旨在解决现有的肖特基二极管存在击穿电压较低的问题。

本申请实施例的第一方面提供了一种肖特基二极管,所述肖特基二极管包括:

半导体衬底;

沟道层,设于所述半导体衬底上;

第一势垒层,设于所述半导体衬底上,且与所述沟道层的第一面接触;

第二势垒层,设于所述半导体衬底上,且与所述沟道层的第二面接触;

第一P柱,设于所述半导体衬底上,且所述第一势垒层设于所述第一P柱和所述沟道层之间;

第二P柱,设于所述半导体衬底上,且所述第二势垒层设于所述第二P柱和所述沟道层之间;

阴极电极单元,设于所述半导体衬底上,且所述阴极电极单元分别与所述沟道层的第一端、所述第一势垒层的第一端以及所述第二势垒层的第一端接触;

阳极电极单元,所述阳极电极单元的形状为“L”形;其中,所述阳极电极单元的垂直部设于所述半导体衬底上,且所述垂直部分别与所述沟道层的第二端、所述第一势垒层的第二端、所述第二势垒层的第二端接触,所述阳极电极单元的的水平部设于所述第一P柱、所述第二P柱、所述沟道层、所述第一势垒层以及所述第二势垒层上。

在一个实施例中,所述阳极电极单元包括:

第一阳极子单元,设于所述半导体衬底上,且分别与所述沟道层的第二端、所述第一势垒层的第二端、所述第二势垒层的第二端接触;

金属场板子单元,设于所述第一P柱、所述第二P柱、所述沟道层、所述第一势垒层以及所述第二势垒层上。

在一个实施例中,所述阳极电极单元为肖特基金属,所述阴极电极单元为欧姆金属。

在一个实施例中,所述阴极电极单元的高度与所述第一阳极子单元和所述金属场板子单元的高度之和相等。

在一个实施例中,所述第一P柱和所述第二P柱相对设置。

在一个实施例中,所述第一P柱到所述阴极电极单元的距离与所述第一P柱到所述第一阳极子单元的距离相同。

在一个实施例中,所述第一P柱的长度小于所述第一势垒层的长度。

在一个实施例中,所述第一P柱的长度为所述第一势垒层的长度的1/3。

本申请实施的第二方面提供了一种芯片,包括多个如上述任一项所述的肖特基二极管,多个所述肖特基二极管共设于同一半导体衬底上,且多个所述肖特基二极管的阴极电极单元共接,多个所述肖特基二极管的阳极电极单元共接。

本申请实施的第三方面提供了一种肖特基二极管的制备方法,包括:

在半导体衬底上依次间隔形成第一P柱、沟道层以及第二P柱;

在所述半导体衬底上形成第一势垒层;其中,所述第一势垒层位于所述第一P柱和所述沟道层之间;

在所述半导体衬底上形成第二势垒层;其中,所述第二势垒层位于所述第二P柱和所述沟道层之间;

在所述半导体衬底上形成阴极电极单元;其中,所述阴极电极单元分别与所述沟道层的第一端、所述第一势垒层的第一端以及所述第二势垒层的第一端接触;

形成阳极电极单元;其中,所述阳极电极单元的形状为“L”形;所述阳极电极单元的垂直部设于所述半导体衬底上,且所述垂直部分别与所述沟道层的第二端、所述第一势垒层的第二端、所述第二势垒层的第二端接触,所述阳极电极单元的的水平部设于所述第一P柱、所述第二P柱、所述沟道层、所述第一势垒层以及所述第二势垒层上。

本申请实施例与现有技术相比存在的有益效果是:在本实施例中,通过设置阳极电极单元为肖特基金属,且阳极电极单元与第一P柱、第二P柱接触,使得是阳极电极单元与第一P柱之间为肖特基接触,阳极电极单元与第二P柱之间为肖特基接触,可以使得阳极电极单元与第一P柱、第二P柱之间存在较高的肖特基势垒高度,进而减小阳极电极单元的泄漏电流,提供较高的正向阈值电压,从而提升肖特基二极管的击穿电压电压。

附图说明

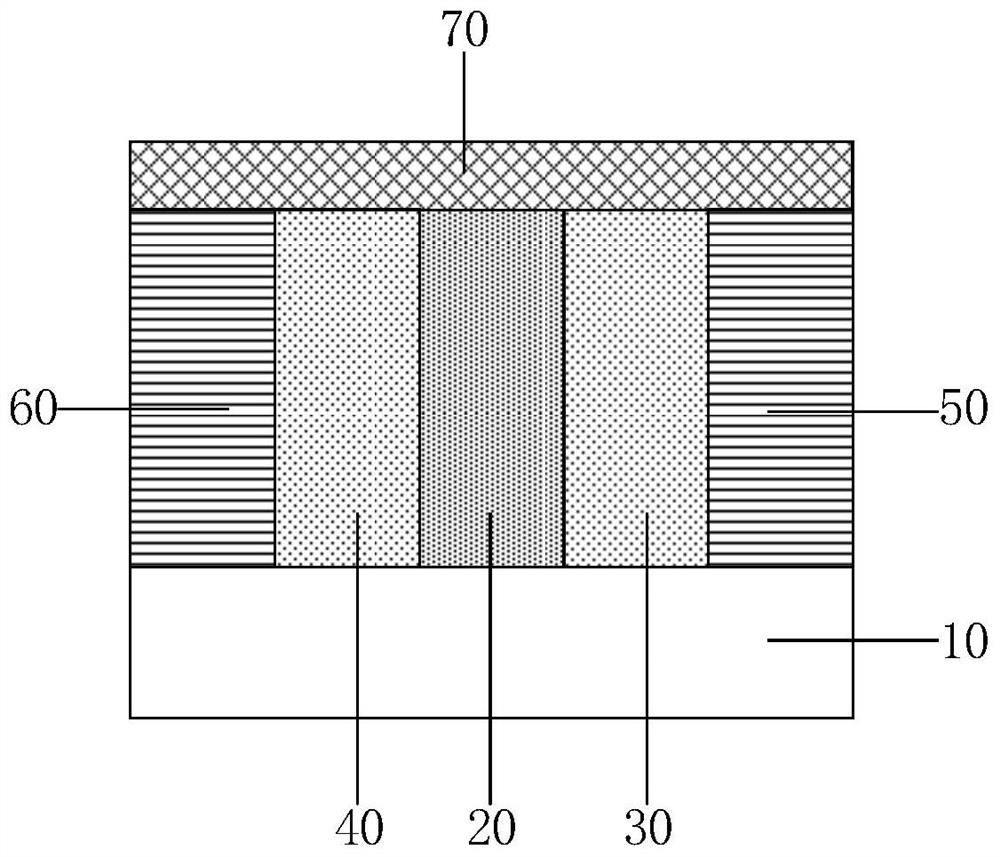

图1是本申请一个实施例提供的肖特基二极管沿着阳极电极单元的垂直切面结构示意图;

图2是本申请一个实施例提供的肖特基二极管俯视结构示意图;

图3是本申请一个实施例提供的肖特基二极管的正视结构示意图;

图4是本申请一个实施例提供的肖特基二极管的结构示意图;

图5是本申请一个实施例提供的芯片的结构示意图;

图6是本申请一个实施例提供的肖特基二极管的制备方法步骤示意图;

图7是本申请一个实施例提供的形成第一P柱、沟道层以及第二P柱后的示意图;

图8是本申请一个实施例提供的形成第一势垒层和第二势垒层后的示意图;

图9是本申请一个实施例提供的形成阴极电极单元后的示意图;

图10是本申请一个实施例提供的形成阳极电极单元后的示意图。

具体实施方式

为了使本申请所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本申请,并不用于限定本申请。

需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本申请的描述中,“多个”的含义是一个或一个以上,除非另有明确具体的限定。

在本申请说明书中描述的参考“一个实施例”、“一些实施例”或“实施例”意味着在本申请的一个或多个实施例中包括结合该实施例描述的特定特征、结构或特点。由此,在本说明书中的不同之处出现的语句“在一个实施例中”、“在一些实施例中”、“在其他一些实施例中”、“在另外一些实施例中”、“在一个具体实施例中”、“在一个具体应用中”等不是必然都参考相同的实施例,而是意味着“一个或多个但不是所有的实施例”,除非是以其他方式另外特别强调。此外,在一个或多个实施例中,可以以任何合适的方式组合特定的特征、结构或特性。

电子信息产业作为高新技术产业,在扩大社会就业、推动经济转型升级、增强国际竞争力和维护国家安全等方面扮演着更加重要的角色。功率二极管是电路系统的关键部件,现已经被广泛应用在高频逆变器、数码产品、发电机、电视机等民用产品和卫星接收装置、导弹及飞机等各种先进武器控制系统以及仪器仪表设备的军用场合。

通常应用的有普通整流二极管、肖特基二极管、PN二极管等,其中,肖特基整流管由于具有较低的通态压降、较大的漏电流、反向恢复时间几乎为零等优点,应用非常广泛。

肖特基二极管是利用金属与半导体接触形成的金属-半导体结原理制作的一种二极管。肖特基二极管比PN结二极管具有更低的功耗、更大的电流以及超高速的优点,因此,在电子学器件中受到青睐。

但是,现有的肖特基二极管存在击穿电压较低的问题。

为了解决上述技术问题,本申请实施例提供了一种肖特基二极管,参考图1、图2、图3所示,图1为肖特基二极管从第一P柱50、第二P柱60的垂直切面结构示意图,图2为肖特基二极管的俯视结构示意图,图3为肖特基二极管的正视结构示意图,肖特基二极管包括:半导体衬底10、沟道层20、第一势垒层30、第二势垒层40、第一P柱50、第二P柱60、阳极电极单元70以及阴极电极单元80。

具体的,沟道层20设于半导体衬底10上。第一势垒层30设于半导体衬底10上,且第一势垒层30与沟道层20的第一面接触。第二势垒层40设于半导体衬底10上,且第二势垒层40与沟道层20的第二面接触。第一P柱50设于半导体衬底10上,且第一势垒层30设于第一P柱50和沟道层20之间。第二P柱60设于半导体衬底10上,且第二势垒层40设于第二P柱60和沟道层20之间。阴极电极单元80设于半导体衬底10上,且阴极电极单元80分别与沟道层20的第一端、第一势垒层30的第一端以及第二势垒层40的第一端接触。阳极电极单元70的形状为“L”形;其中,阳极电极单元70的垂直部设于半导体衬底10上,且垂直部分别与沟道层20的第二端、第一势垒层30的第二端、第二势垒层40的第二端接触,阳极电极单元70的水平部设于第一P柱50、第二P柱60、沟道层20、第一势垒层30以及第二势垒层40上。

在本实施例中,第一势垒层30与沟道层20的第一面接触;第二势垒层40与沟道层20的第二面接触。可以理解的是,沟道层20设于第一势垒层30和第二势垒层40之间,第一势垒层30和第二势垒层40设于沟道层20的两侧,第一势垒层30和第二势垒层40相对设置。在本实施例中,通过设置第一势垒层30和第二势垒层40设于沟道层20的两侧,可以在沟道层20的两侧形成双层的二维电子气(Two-Dimensional Electron Gas,2DEG),实现阴极电极单元80和阳极电极单元70之间的沟通。

在本实施例中,第一势垒层30设于第一P柱50和沟道层20之间,可以理解的是,第一P柱50与第一势垒层30接触,第二势垒层40设于第二P柱60和沟道层20之间,第二P柱60与第二势垒层40接触。在本实施例中,通过设置第一P柱50和第二P柱60分别与第一势垒层30和第二势垒层40接触,可以利用第一P柱50和第二P柱60抵消掉双层的二维电子气,使得肖特基二极管在关断时具有较小的二维电子气,避免了漏电流的产生,如此实现对器件的完全控制,提供较高的正向阈值电压。

在本实施例中,阴极电极单元80分别与沟道层20的第一端、第一势垒层30的第一端以及第二势垒层40的第一端接触。阳极电极单元70的形状为“L”形;其中,阳极电极单元70的水平部设于第一P柱50、第二P柱60、沟道层20、第一势垒层30以及第二势垒层40上。可以理解的是,第一P柱50和第二P柱60设于半导体衬底10上,且第一P柱50和第二P柱60设于阴极电极单元80和阳极电极单元70的垂直部之间,阳极电极单元70的水平部用于连接阳极电极单元70的垂直部和第一P柱50以及第二P柱60,并且阳极电极单元70的水平部仅与第一P柱50、第二P柱60与阳极电极单元70的垂直部之间的沟道层20、第一势垒层30以及第二势垒层40接触,换言之,其并不与第一P柱50、第二P柱60与阴极电极单元80之间的沟道层20、第一势垒层30以及第二势垒层40接触。

在本实施例中,沟道层20、第一势垒层30以及第二势垒层40均垂直设于半导体衬底10上,并且阳极电极单元70的水平部设于沟道层20、第一势垒层30、第二势垒层40、第一P柱50以及第二P柱60上,阳极电极单元70的水平部为肖特基金属,如此形成一个金属场板,可以在肖特基二极管工作时,对肖特基二极管内部的电场进行调节,使得内部电场更加均匀,进而提升肖特基二级管的击穿电压。相对于传统半导体器件中的沟道层20和势垒层平行设置于半导体衬底10上而言,如此可以提供较高的肖特基势垒高度,具有较高的导通电流,进而减小阳极电极单元70的泄漏电流,提供较高的正向阈值电压。

在一个实施例中,参考图3所示,阳极电极单元70包括:第一阳极子单元71和金属场板子单元72。

具体的,第一阳极子单元71设于半导体衬底10上,且第一阳极子单元71分别与沟道层20的第二端、第一势垒层30的第二端、第二势垒层40的第二端接触。金属场板子单元72设于第一P柱50、第二P柱60、沟道层20、第一势垒层30以及第二势垒层40上。

在本实施例中,金属场板子单元72用于连接第一阳极子单元71和第一P柱50以及第二P柱60,并且金属场板子单元72仅与第一P柱50、第二P柱60与阳极电极单元70的垂直部之间的沟道层20、第一势垒层30以及第二势垒层40接触,换言之,金属场板子单元72并不与第一P柱50、第二P柱60与阴极电极单元80之间的沟道层20、第一势垒层30以及第二势垒层40接触。因为金属场板子单元72为肖特基金属,如此形成一个金属场板,可以在肖特基二极管工作时,对肖特基二极管内部的电场进行调节,使得内部电场更加均匀,进而提升肖特基二级管的击穿电压。

在一个实施例中,沟道层20为GaN。

在本实施例中,沟道层20可以由氮化镓材料制备,例如通过在半导体衬底10上沉积氮化镓材料或者外延生长氮化镓材料形成。

在一个实施例中,第一势垒层30和第二势垒层40均为AlGaN。

在本实施例中,第一势垒层30和第二势垒层40可以均由氮镓化铝材料制备,例如通过在半导体衬底10上沉积氮镓化铝材料或者外延生长氮镓化铝材料形成第一势垒层30和第二势垒层40。

在一个实施例中,第一P柱50和第二P柱60为P-GaN。

在本实施例中,通过在GaN中掺杂p型掺杂剂就形成了P-GaN,其中,P型掺杂剂可以为硼、镓、铝等。

在一个实施例中,半导体衬底10为蓝宝石衬底。

在一个实施例中,阳极电极单元70为肖特基金属,阴极电极单元80为欧姆金属。

具体的,肖特基金属可以是铂、金、银的层或者导电的半导体层等。欧姆金属为Ti、Al、Ti、Au材料的组合。

在一个具体应用中,肖特基金属为Ni、Au材料的组合。

在一个实施例中,欧姆金属的Ti、Al、Ti、Au材料的厚度分别为15nm、250nm、50nm、150nm,肖特基金属的Ni、Au的厚度分别为70nm、30nm。

在本实施例中,通过设置阳极电极单元70为肖特基金属,使得阳极为肖特基接触,如此可以提供较高的肖特基势垒高度,通过设置肖特基金属的Ni、Au的厚度分别为70nm、30nm,进而减小阳极电极单元70的泄漏电流,提供较高的正向阈值电压,进而提升肖特基二极管的整体性能。

在一个实施例中,参考图3所示,阴极电极单元80的高度与第一阳极子单元71和金属场板子单元72的高度之和相等。具体的,通过设置阴极电极单元80的高度与第一阳极子单元71和金属场板子单元72的高度之和相等,可以使得形成的肖特基二极管的最终处于同一水平位置,可以提升功率器件的稳定性,进而导致功率器件在工作时,性能更加稳定,进而延长肖特基二极管的使用寿命。

在一个实施例中,参考图1所示,第一P柱50和第二P柱60相对设置。

具体的,第一P柱50和第二P柱60分别设于第一势垒层30和第二势垒层40的两侧,如此可以更好的抵消沟道层20的两侧的二维电子气,并且通过设置第一P柱50和第二P柱60相对设置,可以使得沟道层20的两侧的二维电子气被抵消的区域也相同,可以提升功率器件的稳定性,因为若第一P柱50和第二P柱60不相对设置,例如,交错设置会使得沟道层20的两侧的二维电子气被抵消的区域不相同,进而导致功率器件在工作时,性能不稳定,进而缩短肖特基二极管的使用寿命。

在一个实施例中,参考图4所示,为方便观察,图4为肖特基二极管去掉阳极电极单元70的水平部的结构示意图,第一P柱50到阴极电极单元80的距离L1与第一P柱50到第一阳极子单元71(或者说阳极电极单元70的垂直部)的距离L2相同。第二P柱60到阴极电极单元80的距离与第二P柱60到第一阳极子单元71的距离相同。具体的,第一P柱50和第二P柱60均设于阴极电极单元80和第一阳极子单元71之间的中间位置。如此可以可以使得沟道层20的两侧的二维电子气被抵消的区域也相同,可以提升功率器件的稳定性。

在一个实施例中,因为阳极电极单元70为肖特基金属,阳极电极单元70与第二P柱60接触,使得是阳极电极单元70与第二P柱60之间为肖特基接触,可以使得阳极电极单元70与第二P柱60之间存在较高的肖特基势垒高度,进而减小阳极电极单元70的泄漏电流,提供较高的正向阈值电压,从而提升肖特基二极管的性能,拓展肖特基二极管应用范围。

在一个实施例中,参考图4所示,第一P柱50和第二P柱60的长度相同,均用L3表示。沟道层20的长度与第一势垒层30的长度以及第二势垒层40的长度相同,均用L4表示。具体的,沟道层20的长度等于第一势垒层30的长度等于第二势垒层40的长度,通过设置第一P柱50和第二P柱60的长度相同,可以使得沟道层20的两侧的二维电子气被抵消的区域相同,可以提升功率器件的稳定性,使得肖特基二极管更加稳定的工作,拓展肖特基二极管应用范围。

在一个实施例中,参考图4所示,第一P柱50的长度L3小于第一势垒层30的长度L4。具体的,第一P柱50的长度L3小于第一势垒层30的长度L4,因为第一P柱50和第二P柱60都是用于抵消二维电子气的,二维电子气用于实现阴极电极单元80和阳极电极单元70之间的沟通,通过设置第一P柱50的长度小于第一势垒层30的长度,第二P柱60的长度小于第二势垒层40的长度,可以使得二维电子气不会被抵消完,不仅能实现肖特基二极管的功能,还能实现对器件的完全控制,提供较高的正向阈值电压。

在一个实施例中,第一P柱50的长度为第一势垒层30的长度的1/3。具体的,第二P柱60的长度为第二势垒层40的长度的1/3。因为第一P柱50和第二P柱60都是用于抵消二维电子气的,二维电子气用于实现阴极电极单元80和阳极电极单元70之间的沟通,通过设置第一P柱50的长度为第一势垒层30的长度的1/3,第二P柱60的长度为第二势垒层40的长度的1/3,可以使得二维电子气不会被抵消完,不仅能实现肖特基二极管的功能,还能实现对器件的完全控制,提供较高的正向阈值电压。

在一个实施例中,第一P柱50的高度、第二P柱60的高度、沟道层20的高度、第一势垒层30的高度以及第二势垒层40的高度均相同。在本实施例中,通过设置第一P柱50的高度、第二P柱60的高度、沟道层20的高度、第一势垒层30的高度以及第二势垒层40的高度均相同,可以使得肖特基二极管的性能更加稳定,延长肖特基二极管的使用寿命,拓展肖特基二极管应用范围。

在一个实施例中,参考图2所示,第一P柱50的宽度W2大于第一势垒层30的宽度W1,第二P柱60的宽度与第一P柱50的宽度相同。因为第一P柱50和第二P柱60可以抵消二维电子气,通过设置第一P柱50的宽度大于第一势垒层30的宽度,可以利用第一P柱50和第二P柱60更好的抵消掉双层的二维电子气,使得肖特基二极管在关断时具有较小的二维电子气,避免了有漏电流的产生,如此实现对器件的完全控制,提供较高的正向阈值电压。

在一个实施例中,第一P柱50的宽度与第一势垒层30的宽度相同。具体的,第二P柱60的宽度与第一势垒层30的宽度相同,第一势垒层30的宽度与第二势垒层40的宽度相同。在本实施例中,通过设置第一P柱50的宽度与第一势垒层30的宽度相同,可以使得肖特基二极管的性能更加稳定,延长肖特基二极管的使用寿命。

本申请实施例的第二方面提供了一种芯片,参考图5所示,包括多个如上述任一项的肖特基二极管100,多个肖特基二极管100共设于同一半导体衬底10上,且多个肖特基二极管100的阴极电极单元80共接,多个肖特基二极管100的阳极电极单元70共接。

具体的,多个肖特基二极管100分别通过相邻的第一P柱50和第二P柱60接触连接在一起。例如,第一个肖特基二极管100的第一P柱50与第二个肖特基二极管100的第二P柱60接触连接,第二个肖特基二极管100的第一P柱50与第三个肖特基二极管100的第二P柱60,以此类推,形成芯片。芯片最大的优势就是可以通过阳极电极单元70、第一P柱50、第二P柱60之间的高肖特基势垒高度而减小阳极的泄漏电流,提供较高的正向阈值电压。通过设置多个肖特基二极管100共设于同一半导体衬底10上,且多个肖特基二极管100的阴极电极单元80共接,多个肖特基二极管100的阳极电极单元70共接,如此使得多个肖特基二极管100并联使用,其中第一P柱50和第二P柱60可以作为相邻两个肖特基二极管100的连接,可以实现对多个器件产生控制作用,并有效避免了有漏电流的产生,可以产生更高的正向导通电流。

本申请实施例还提供了一种肖特基二极管的制备方法,参考图6所示,包括:步骤S10至步骤S40。

步骤S10:参考图7所示,在半导体衬底10上依次间隔形成第一P柱50、沟道层20以及第二P柱60。

在一个具体应用中,在半导体衬底10上进行进行选择性刻蚀,分别刻蚀出第一P柱50、沟道层20以及第二P柱60的位置,然后分别对应的在第一P柱50、沟道层20以及第二P柱60的位置区域中填充相应的半导体材料,例如,在第一P柱50和第二P柱60区域填充P-GaN材料,在沟道层20区域填充GaN材料。

在一个具体应用中,半导体衬底10为蓝宝石衬底。

步骤S20:参考图8所示,在半导体衬底10上形成第一势垒层30;其中,第一势垒层30位于第一P柱50和沟道层20之间,在半导体衬底10上形成第二势垒层40;其中,第二势垒层40位于第二P柱60和沟道层20之间。

在一个具体应用中,在半导体衬底10上进行进行选择性刻蚀,分别刻蚀出第一势垒层30和第二势垒层40的位置,然后分别对应的在第一势垒层30和第二势垒层40的位置区域中填充相应的半导体材料,例如,在第一势垒层30和第二势垒层40区域填充AlGaN材料。

在一个实施例中,可以通过多次外延第一P柱50、沟道层20、第二P柱60、第一势垒层30和第二势垒层40,可以决定第一P柱50、沟道层20、第二P柱60、第一势垒层30和第二势垒层40的高度。

步骤S30:参考图9所示,在半导体衬底10上形成阴极电极单元80;其中,阴极电极单元80分别与沟道层20的第一端、第一势垒层30的第一端以及第二势垒层40的第一端接触。

在一个实施例中,采用掩膜确定阴极电极单元80的形状,并在掩膜上淀积金属形成阴极电极单元80。

步骤S40:参考图10所示,形成阳极电极单元70;其中,阳极电极单元70的形状为“L”形;阳极电极单元70的垂直部设于半导体衬底上,且垂直部分别与沟道层20的第二端、第一势垒层30的第二端、第二势垒层40的第二端接触,阳极电极单元70的的水平部设于第一P柱50、第二P柱60、沟道层20、第一势垒层30以及第二势垒层40上,阳极电极单元70为肖特基金属。

在一个实施例中,采用掩膜确定阳极电极单元70的形状,并在掩膜上淀积金属形成阳极电极单元70。因为阳极电极单元70为肖特基金属,阳极电极单元70与第一P柱50接触,使得阳极电极单元70与第一P柱50之间为肖特基接触,可以使得阳极电极单元70与第一P柱50之间存在较高的肖特基势垒高度,进而减小阳极电极单元70的泄漏电流,提供较高的正向阈值电压,从而提升肖特基二极管的性能,拓展肖特基二极管应用范围。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述或记载的部分,可以参见其它实施例的相关描述。

以上实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例技术方案的精神和范围,均应包含在本申请的保护范围之内。

- 一种无注入型终结端结构的SiC肖特基二极管及其制备方法

- 一种抗浪涌能力增强型的4H-SiC肖特基二极管及其制备方法

- 一种带场板的肖特基结金刚石二极管器件的制备方法

- 一种基于肖特基二极管的毫米波过保护电路及其制备方法

- 肖特基二极管、肖特基二极管阵列及肖特基二极管的制备方法

- 肖特基二极管、肖特基二极管阵列及肖特基二极管的制备方法