低功耗紧凑型Relu激活函数神经元电路

文献发布时间:2023-06-19 18:32:25

技术领域

本发明涉及CMOS电路领域,尤其涉及一种低功耗紧凑型Relu激活函数神经元电路。

背景技术

人工神经网络是在受生物学的启发后创建的。由于生物大脑是由相互连接的多个神经元组成的极其复杂的网络,人们仿照生物神经网络的结构,使用简单运算单元模拟神经元,并将大量运算单元按某种形式密集连接,便构成了人工神经网络。

在人工神经网络的众多形式中,卷积神经网络(Convolutional Neural Network,CNN)是一种前馈神经网络,其在众多人工神经网络形式中最贴近人脑神经元运行方式。卷积神经网络的基本结构由输入层、卷积层、激活层、池化层、全连接层及输出层构成。激活层负责对卷积层抽取的特征进行激活。由于卷积操作是由输入矩阵与卷积核矩阵进行相乘加的线性变化关系,需要激活层对其进行非线性映射,这样神经网络拟合出来的函数也就能适应复杂函数起伏。

在卷积神经网络中,通常采用Relu函数(即线性整流函数,英文全称Linearrectification function Relu)来充当激活函数。作为激活函数的Relu函数能够限制小于0的值为0,同时令大于或者等于0的值保存输出,计算速度很快,可以更好地解决较为复杂的问题,更加符合实际生物学对模拟神经网络的期望。其中,卷积神经网络的理念已经应用到CMOS电路中。

现有的CMOS电路通常采用4个晶体管做布局连接以实现Relu函数神经元单元,参见图1所示,4个晶体管分别是NM1、NM2、PM1和PM2,并且再由多个该神经元单元形成神经元电路。由于卷积神经网络由数百层组成,每层的输出要分别连接到具有加权和非线性激活函数的人工神经元上实现运算。但是,面对大数据时代产生的海量数据,基于多个上述Relu函数神经元单元而形成的Relu函数神经元电路需要频繁地访问存储器,不仅增大功耗,而且也会造成数据冗余以及较低的有效传输速率,限制神经网络加速芯片的发展。

为了降低现有Relu函数神经元电路的计算量和功耗,以满足集成电路向高密度集成及微型化的发展趋势,“存内计算”的概念被提出。存内计算就是直接在存储阵列内完成计算。在存储阵列需要执行“存内计算”时,主处理模块只需要给存储阵列发送输入数据,然后经过若干时钟周期后,存储阵列就会把计算好的结果返回给主处理模块。其中,在处理人工智能相关任务的时候,会把神经网络权重存储到上述的存储阵列中,主处理模块直接把神经网络的输入信息发送给存储阵列后,即可开始执行存内计算。但大多数基于非易失性存储器的存内计算仍然依赖于通用处理器来计算和传播每个层的激活函数,并且用于实现非线性激活功能的模拟互补金属氧化物半导体(CMOS)电路和具有可重构功能映射的模/数转换器(ADC)均需要大量加法器、乘法器以及数模转化器等,导致神经元电路规模庞大、体积巨大且功耗大幅度提高,难以适应低功耗紧凑型神经元电路的发展需要。

发明内容

本发明所要解决的技术问题是针对上述现有技术提供一种结构简单紧凑且功耗低的低功耗紧凑型Relu激活函数神经元电路。

本发明解决上述技术问题所采用的技术方案为:低功耗紧凑型Relu激活函数神经元电路,其特征在于,包括:

第一层突触阵列,具有至少一个电压输出端;

神经元晶体管,为具有阈值电压可调性能的MOS晶体管,该神经元晶体管具有栅极、源极和漏极,栅极连接第一层突触阵列的各电压输出端;其中,单个神经元晶体管作为一个神经元;

第二层突触阵列,具有至少一个电压输入端,各电压输入端连接神经元晶体管的漏极;

其中,第一层突触阵列的电压输出端的电压输出值标记为X,神经元晶体管的阈值电压标记为Vth,神经元晶体管的栅极电压标记为Vg,Vg=X;

当电压输出值X小于阈值电压Vth时,MOS晶体管未导通,神经元未被激活,神经元的输出恒定为0;

当电压输出值X大于或者等于阈值电压Vth时,MOS晶体管导通,神经元被激活,神经元的输出为X-Vth。

可选择地,在所述低功耗紧凑型Relu激活函数神经元电路中,所述神经元晶体管为NMOS晶体管或者PMOS晶体管。

再改进,在所述低功耗紧凑型Relu激活函数神经元电路中,所述MOS晶体管的阈值电压可调性能通过铁电极化MOS晶体管栅极的铁电翻转或者改变沟道掺杂浓度或者掺杂处理沟道离子注入浓度或者调节栅氧化层厚度或者具有易失性阈值开关特性的栅极实现。

进一步地,在所述低功耗紧凑型Relu激活函数神经元电路中,所述神经元晶体管为铁电极化MOS晶体管。

进一步地,在所述低功耗紧凑型Relu激活函数神经元电路中,通过在制备MOS晶体管的漏极过程中调整漏极掺杂浓度而实现漏极的阻值调整。

更进一步地,在所述低功耗紧凑型Relu激活函数神经元电路中,所述铁电极化MOS晶体管采用如下方式制备得到:

采用常规的CMOS晶体管制备前端工艺,在衬底上形成浅沟槽隔离区且由浅沟槽隔离区隔离出有源区;

通过离子注入形成对应各有源区的阱;其中,NMOS阱为P阱,PMOS为N阱;

通过光刻显影形成栅极图案,在衬底的上表面先沉积SiO

基于该栅极图案对多晶硅层、铁电材料层和SiO

对栅极结构进行侧墙隔离保护,并对栅极结构的两端进行离子掺杂以形成源漏两端,再采用常规的CMOS后端工艺制备得到MOS晶体管;其中,通过在制备漏极过程中调整掺杂浓度以调整漏极的阻值,制备得到的该MOS晶体管即为所述铁电极化MOS晶体管。

可选择地,在所述低功耗紧凑型Relu激活函数神经元电路中,所述铁电材料层为HfZrO层或者BTO层。

再改进,在所述低功耗紧凑型Relu激活函数神经元电路中,所述漏极的阻值标记为R;其中:

R=(Vg-Vth-Vd)/[β·Vd(Vg-Vth-0.5Vd)];

β=(μ·W·C

其中,Vg为所述神经元晶体管的栅极电压,Vth为所述神经元晶体管的阈值电压,Vd为所述神经元晶体管的漏源电压,μ为所述神经元晶体管的沟道内的载流子迁移率,W为所述神经元晶体管的沟道宽度,C

再进一步地,在所述低功耗紧凑型Relu激活函数神经元电路中,所述阻值R=1/(β·Vd),Vd=0.1V。

与现有技术相比,本发明的优点在于:

首先,在该发明的低功耗紧凑型Relu激活函数神经元电路中,神经元晶体管采用具有阈值电压可调性能的MOS晶体管,并且令该神经元晶体管的栅极连接第一层突触阵列的各电压输出端,令该神经元晶体管的漏极连接第二层突触阵列的各电压输入端。由于神经元晶体管的阈值电压可调,这样就可以通过调节晶体管阈值电压的大小,来满足对不同突触阵列输出值的判断运算以及输出。因该神经元电路的一个神经元只需要采用一个晶体管与第一层突触阵列和第二层突触阵列的配合连接,就可以实现Relu激活函数,这样在能效、延迟和占用面积方面实现显著的增益提高;

其次,该发明的低功耗紧凑型Relu激活函数神经元电路设计简单且工艺并不复杂,采用常规CMOS工艺就可以制备得到作为神经元的神经元晶体管,更加具有实用性。

附图说明

图1为现有的Relu函数神经元单元示意图;

图2为本发明实施例中的低功耗紧凑型Relu激活函数神经元电路示意图;

图3为本发明实施例中的神经元所实现的Relu函数示意图;

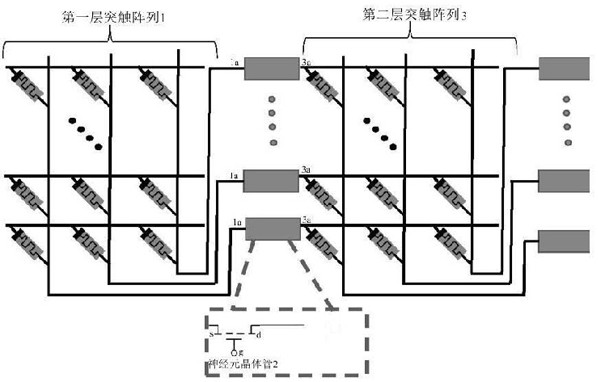

图4为本发明实施例中的低功耗紧凑型Relu激活函数神经元电路在应用场景时的示意图;

图5为本发明实施例制备铁电极化MOS晶体管过程中,在衬底上形成浅沟槽隔离区时的结构示意图;

图6为在图5所示结构基础上先后沉积完毕SiO

图7为在图6所示结构基础上形成栅极结构后的示意图;

图8为制备得到的铁电极化MOS晶体管示意图。

具体实施方式

以下结合附图实施例对本发明作进一步详细描述。

本实施例提供一种低功耗紧凑型Relu激活函数神经元电路。具体地,参见图2所示,该实施例的低功耗紧凑型Relu激活函数神经元电路包括第一层突触阵列1、神经元晶体管2和第二层突触阵列3,第一层突触阵列1具有多个电压输出端1a,第二层突触阵列3具有多个电压输入端3a,神经元晶体管2为具有阈值电压可调性能的MOS晶体管,该神经元晶体管2具有栅极g、源极s和漏极d,栅极g连接第一层突触阵列1的各电压输出端1a,神经元晶体管2的漏极d连接第二层突触阵列3的各电压输入端3a。其中,单个神经元晶体管2作为一个神经元;例如,此处的神经元晶体管2可以是NMOS晶体管或者PMOS晶体管。在该实施例中,第一层突触阵列1的各电压输出端1a的电压输出值标记为X,神经元晶体管2的阈值电压标记为Vth,神经元晶体管2的栅极电压标记为Vg,Vg=X,第二层突触阵列3的各电压输入端3a的电压输入值标记为Y;

当电压输出值X小于阈值电压Vth时,也即Vg 当电压输出值X大于或者等于阈值电压Vth时,也即Vg≥Vth时,MOS晶体管导通,神经元被激活,神经元的输出为X-Vth。 也就是说,针对每一个神经元,位于上一层的突触阵列每输出一个大于阈值电压Vth的电压值X,该神经元的输出对应值为X-Vth,并且神经元的该输出值X-Vth传递到下一层的突触阵列中,神经元的输入及输出过程满足Relu函数关系(参见图3所示)。通过调节晶体管阈值电压(Vth)的大小,就可以满足对不同突触阵列输出值的判断运算以及输出。其中,Relu函数关系如下所示:

作为上述MOS晶体管的阈值电压可调性能的实现方式,根据需要,可以通过铁电极化MOS晶体管栅极的铁电翻转或者改变沟道掺杂浓度或者掺杂处理沟道离子注入浓度或者调节栅氧化层厚度或者具有易失性阈值开关特性的栅极实现。 其中,上述低功耗紧凑型Relu激活函数神经元电路在应用场景时的情况参见图4所示。突触阵列采用4×4阵列,并且每一列的四个突触分别连接一个神经元晶体管。其中,该4×4阵列的突触阵列位于字线解码与位线解码之间。 例如,在该实施例中,上述低功耗紧凑型Relu激活函数神经元电路中所采用的神经元晶体管2也可以采用铁电极化MOS晶体管。其中,该铁电极化MOS晶体管可以采用如下方式制备得到: 步骤S1,采用常规的CMOS晶体管制备前端工艺,在衬底21上形成浅沟槽隔离区22且由浅沟槽隔离区22隔离出有源区;其中,衬底21采用硅衬底;此处所形成的结构参见图5所示; 步骤S2,通过离子注入形成对应各有源区的阱;其中,NMOS阱为P阱,PMOS为N阱; 步骤S3,通过光刻显影形成栅极图案,在衬底21的上表面先沉积SiO 步骤S4,基于该栅极图案对多晶硅层25、铁电材料层24和SiO 步骤S5,对栅极结构进行侧墙隔离保护,并对栅极结构的两端进行离子掺杂以形成源漏两端,再采用常规的CMOS晶体管制备后端工艺制备得到MOS晶体管;其中,制备得到的MOS晶体管即为所述铁电极化MOS晶体管,铁电极化MOS晶体管的结构参见图8所示。其中,标号26所指结构为栅极保护墙,标号27所指区域为源漏掺杂区。 需要说明的是,在神经元晶体管2采用铁电极化MOS晶体管时,上述低功耗紧凑型Relu激活函数神经元电路中神经元晶体管漏极的阻值计算方式如下:假设神经元晶体管漏极的阻值标记为R: R=(Vg-Vth-Vd)/[β·Vd(Vg-Vth-0.5Vd)]; β=(μ·W·C 其中,Vg为神经元晶体管的栅极电压,Vth为神经元晶体管的阈值电压,Vd为神经元晶体管的漏源电压,μ为神经元晶体管的沟道内的载流子迁移率,W为神经元晶体管的沟道宽度,C 本领域技术人员熟知,此处的栅氧化层就是晶体管的栅极与硅衬底之间的绝缘介质,一般用二氧化硅等,就是用来绝缘和防止漏电的。其中,在该实施例中,神经元晶体管2的漏源电压Vd=0.1V,神经元晶体管漏极的阻值R=1/(β·Vd)。 尽管以上详细地描述了本发明的优选实施例,但是应该清楚地理解,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 基于CMOS的神经元激活函数电路及神经元电路

- 一种基于忆阻器的VFL-RELU脉冲神经元的电路