读出电路架构

文献发布时间:2023-06-19 19:00:17

技术领域

本申请涉及半导体电路版图领域,特别涉及一种读出电路架构。

背景技术

动态随机存取存储存储器(Dynamic Random Access Memory,DRAM)通过单元电容中的电荷来写入数据;单元电容连接至位线和互补位线,在DRAM中,当执行读取操作或刷新操作时,读出放大器读出并放大位线和互补位线之间的电压差。

构成读出放大器的半导体器件可能由于工艺变化、温度等因素的影响从而具有不同的器件特性(例如,阈值电压)。不同的器件特性会导致读出放大器中的产生偏移噪声,而偏移噪声会降低读出放大器的有效读出裕度,并且会降低DRAM的性能。

申请人发现,目前对DRAM的偏移噪声的消除过程中,需专门设计用于偏移消除的MOS管,从而增大感测放大电路所需的版图面积,不利于DRAM集成度的提高。

因此,如何在不多引入偏移消除MOS管的前提下,以消除读出电路中的偏移噪声,是当下亟待解决的问题。

发明内容

本申请实施例提供一种读出电路架构,在不多引入偏移消除MOS管的前提下,以消除读出电路中的偏移噪声,有利于DRAM集成度的提高。

本申请实施例提供了一种读出电路架构,包括:第一NMOS版图,包括在第一方向上分立排布的第一N型有源层,以及设置在第一N型有源层上分立排布的第一栅极层;第二NMOS版图,包括在第一方向上分立排布的第二N型有源层,以及设置在第二N型有源层上分立排布的第二栅极层;第一PMOS版图,包括在第一方向上分立排布的第一P型有源层,以及设置在第一P型有源层上分立排布的第三栅极层;第二PMOS版图,包括在第一方向上分立排布的第二P型有源层,以及设置在第二P型有源层上分立排布的第四栅极层;第一处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第一有源层,以及设置在第一有源层上,且在第二方向上延伸的第一隔离栅极;第二处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第二有源层,以及设置在第一有源层上,且在第二方向上延伸的第二隔离栅极;第一方向和第二方向相交。

在偏移消除过程中,第一PMOS管的栅极连接互补读出位线,漏极连接读出位线,第一PMOS管导通后第一信号端与读出位线电连接,且第一信号端用于接收对应逻辑“1”的高电平,即第一信号端接收芯片内部电源电压;此时导通后的第一PMOS管基于互补读出位线的电平和阈值电压影响读出位线的电平;第二PMOS管的栅极连接读出位线,漏极连接互补读出位线,第二PMOS管导通后第一信号端与读出位线电连接,且第一信号端用于接收对应逻辑“1”的高电平,即第一信号端芯片内部电源电压;此时导通后的第二PMOS管基于读出位线的电平和阈值电压影响互补读出位线的电平,第一PMOS管和第二PMOS管的阈值电压差异会导致读出位线和互补读出位线的电平差异,即通过读出位线和互补读出位线的电平,反应出第一PMOS管和第二PMOS管的偏移噪声。第一NMOS管的栅极连接至互补读出位线,漏极连接位线;第二NMOS管的栅极连接至读出位线,漏极互补位线;由于第一隔离MOS管<11>和第二隔离MOS管<12>的连接方式,在偏移消除进行时,第一隔离MOS管<11>和第二隔离MOS管<12>不导通,且第二信号端也用于接收对应逻辑“1”的高电平,即第一信号端接收芯片内部电源电压;使得第一NMOS管和第二NMOS管的导通差异并不影响读出位线和互补读出位线,而是直接调整位线电压和互补位线电压。另外,由于读出位线和互补读出位线的电平已反应出第一PMOS管和第二PMOS管的偏移噪声,且第一NMOS管的导通程度基于互补读出位线的电平和第一NMOS管的阈值电压确定,第二NMOS管的导通程度基于读出位线的电平和第二NMOS管的阈值电压确定;此时,第一NMOS管和第二NMOS管分别基于互补读出位线和读出位线导通后,使调整后的位线电压和互补位线反应出第一PMOS管和第二PMOS管的偏移噪声,并同时反应出第一NMOS管和第二NMOS管的偏移噪声,即完成读出电路的偏移消除操作。因此,本申请实施例提供的读出电路的版图可以避免布局偏移消除MOS管,从而减小了读出电路的版图面积。

附图说明

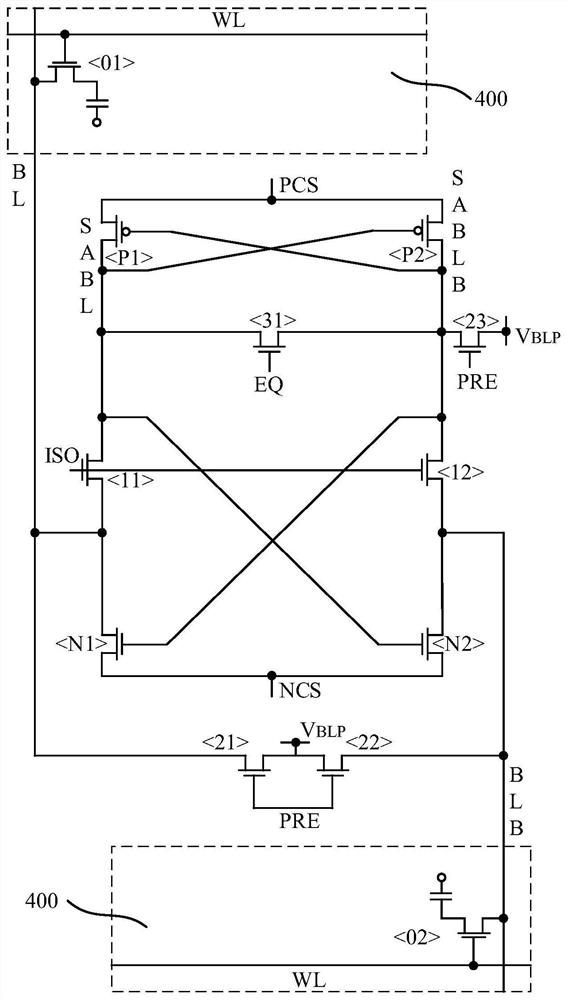

图1为本申请实施例提供的读出电路的电路结构示意图;

图2~图15为本申请实施例提供的读出电路的版图结构示意图。

具体实施方式

构成读出放大器的半导体器件可能由于工艺变化、温度等因素的影响从而具有不同的器件特性(例如,阈值电压)。不同的器件特性会导致读出放大器中的产生偏移噪声,而偏移噪声会降低读出放大器的有效读出裕度,并且会降低DRAM的性能。

目前对DRAM的偏移噪声的消除过程中,需专门设计用于偏移消除的MOS管,从而增大感测放大电路所需的版图面积,不利于DRAM集成度的提高。

本申请实施例提供了一种读出电路架构,包括:第一NMOS版图,包括在第一方向上分立排布的第一N型有源层,以及设置在第一N型有源层上分立排布的第一栅极层;第二NMOS版图,包括在第一方向上分立排布的第二N型有源层,以及设置在第二N型有源层上分立排布的第二栅极层;第一PMOS版图,包括在第一方向上分立排布的第一P型有源层,以及设置在第一P型有源层上分立排布的第三栅极层;第二PMOS版图,包括在第一方向上分立排布的第二P型有源层,以及设置在第二P型有源层上分立排布的第四栅极层;第一处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第一有源层,以及设置在第一有源层上,且在第二方向上延伸的第一隔离栅极;第二处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第二有源层,以及设置在第一有源层上,且在第二方向上延伸的第二隔离栅极;第一方向和第二方向相交。

本领域的普通技术人员可以理解,在本申请各实施例中,为了使读者更好地理解本申请而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本申请所要求保护的技术方案。

图1为本实施例提供的读出电路的电路结构示意图,图2~图15为本实施例提供的读出电路的版图结构示意图,以下结合附图对本申请各实施例提供的读出电路架构作进一步详细说明,具体如下:

需要说明的是,在本实施例中,以第一方向与第二方向垂直进行举例说明,第一方向为横向(存储阵列间隙的延伸方向),第二方向为纵向(存储阵列间隙的宽度方向);由于垂直是相交的一种特殊情况,在其他实施例中,本领域技术人员可以根据任意角度设置第一方向和第二方向的相交的方式,本实施例依然适用。

参考图1和图2,读出电路架构,包括:

第一NMOS版图,包括在第一方向上分立排布的第一N型有源层101,以及设置在第一N型有源层101上分立排布的第一栅极层102;其中,第一栅极层102电连接互补读出位线SABLB,位于所述第一栅极层102两侧的第一N型有源层101分别电连接位线BL和第二信号端。

第一NMOS版图用于形成第一NMOS管

第二NMOS版图,包括在第一方向上分立排布的第二N型有源层103,以及设置在第二N型有源层103上分立排布的第二栅极层104;其中,第二栅极层104电连接读出位线SABL,位于第二栅极层104两侧的第二N型有源层103分别电连接互补位线BLB和第二信号端。

第二NMOS版图用于形成第二NMOS管

第一PMOS版图,包括在第一方向上分立排布的第一P型有源层201,以及设置在第一P型有源层201上分立排布的第三栅极层202;其中,第三栅极层202电连接互补读出位线SABLB,位于第三栅极层202两侧的第一P型有源层201分别电连接读出位线SABL和第一信号端。

第一PMOS版图用于形成第一PMOS管

第二PMOS版图,包括在第一方向上分立排布的第二P型有源层203,以及设置在第二P型有源层203上分立排布的第四栅极层204;其中,第四栅极层204电连接读出位线SABL,位于第四栅极层204两侧的第二P型有源层203分别电连接互补读出位线SABLB和第一信号端。

第二PMOS版图用于形成第二PMOS管

第一处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第一有源层301,以及设置在第一有源层301上,且在第二方向上延伸的第一隔离栅极311;其中,第一隔离栅极311由于接收隔离信号(Isolation Signal,ISO),位于第一隔离栅极311两侧的第一有源层301分别电连接位线BL和读出位线SABL。

第一有源层301和第一隔离栅极311用于形成第一隔离MOS管<11>,第一隔离MOS管<11>源极连接位线BL,漏极连接读出位线SABL,栅极用于接收隔离信号ISO,第一隔离MOS管<11>用于根据隔离信号导通,使位线BL与读出位线SABL电连接。

第二处理结构版图,包括在第一方向上分立排布且在第二方向上延伸的第二有源层302,以及设置在第二有源层302上,且在第二方向上延伸的第二隔离栅极312;其中,第二隔离栅极312用于接收隔离信号ISO,位于第二隔离栅极312两侧的第二有源层302分别电连接互补位线BLB和互补读出位线SABLB。

第二有源层302和第二隔离栅极312用于形成第二隔离MOS管<12>,第二隔离MOS管<12>源极连接互补位线BLB,漏极连接互补读出位线SABLB,栅极用于接收隔离信号ISO,第二隔离MOS管<12>用于根据隔离信号导通,使互补位线BLB与互补读出位线SABLB电连接。

对于位线BL和互补位线BLB,位线BL连接相邻存储阵列400中一存储阵列400的存储单元<01>,互补位线BLB连接相邻存储阵列400中另一存储阵列400的存储单元<02>。

在偏移消除过程中,第一信号端和第二信号端都用于接收对应逻辑“1”的高电平;在数据读出过程中,第一信号端用于接收对应逻辑“1”的高电平,第二信号端用于接收对应逻辑“0”的低电平。在本实施例中,第一电平信号(Positive Cell Storing Signal,PCS)的电压大于第二电平信号(Negative Cell Storing Signal,NCS)的电压,即第一电平信号PCS为对应逻辑“1”的高电平,第二电平信号NCS为对应逻辑“0”的低电平;在其他实施例中,同样可以设置为,第一电平信号的电压小于第二电平信号的电压,即第一电平信号为对应逻辑“0”的低电平,第二电平信号为对应逻辑“1”的高电平。

对于存储器而言,在数据读出之前,存储器会将位线BL、互补位线BLB、读出位线SABL和互补读出位线SABLB预充电至预设电压。

对于本实施例的读出电路而言,在第一读出阶段,即存储器的偏移消除阶段,向第一信号端和第二信号端提供第一电平信号PCS;第一PMOS管

读出位线SABL和互补读出位线SABLB的电平拉高后,第一PMOS管

读出位线SABL和互补读出位线SABLB的电平拉高后,由于第一NMOS管

由于构成读出放大器的半导体器件可能由于工艺变化、温度等因素的影响从而具有不同的器件特性(例如,阈值电压),即由于外部因素或形成工艺的影响,导致第一NMOS管

在数据共享阶段,将目标存储单元的电压分享至位线BL上,将目标存储单元的电压分享至互补位线BLB上,此时,由于偏移消除过程的执行,位线BL的实际电压比理论电压偏小,从而实现在第二读出阶段,即实际读出放大阶段中,第一隔离MOS管<11>和第二隔离MOS管<12>导通,位线BL与读出位线SABL电连接,互补位线BLB与互补读出位线SABLB电连接,使得原本阈值电压较小的第二PMOS管

综上所述,本实施例提供的读出电路的版图可以避免布局偏移消除MOS管,从而减小了读出电路的版图面积。

在一个实施例中,参考图2,读出电路架构,还包括:

第一处理结构版图还包括:第一预充栅极321,设置在第一有源层301上,在第一方向上延伸,且第一预充栅极321和第一隔离栅极311在第二方向上依次排布;其中,第一预充栅极321用于接收预充电信号(Precharge Signal,PRE),位于第一预充栅极321两侧且远离第一隔离栅极311的第一有源层301用于接收预设电压V

第一预充栅极321和第一有源层301用于形成第一预充电MOS管<21>,第一预充电MOS管<21>的一端子连接位线BL,另一端子用于接收预设电压V

在本实施例中,预设电压V

第二处理结构版图还包括:第二预充栅极322和第三预充栅极323,设置在第二有源层302上,在第一方向上延伸,且第二预充栅极322、第二隔离栅极312和第三预充栅极323在第二方向上依次排布;其中,第二预充栅极322用于接收预充电信号(Precharge Signal,PRE);位于第二预充栅极322两侧且远离第二隔离栅极312的第二有源层302用于接收预设电压V

第二预充栅极322和第二有源层302用于形成第二预充电MOS管<22>,第二预充电MOS管<22>的一端子连接互补位线BLB,另一端子用于接收预设电压V

在一个具体的例子中,第一预充电MOS管<21>接收预设电压V

在一个具体的例子中,第一预充电MOS管<21>的控制端子和第二预充电MOS管<22>的控制端子相连接,即第一预充电MOS管<21>的栅极和第二预充电MOS管<22>的栅极相连接,用于接收预充电信号PRE。

第三预充栅极323和第二有源层302用于形成第三预充电MOS管<23>,第三预充电MOS管<23>的一端子连接读出位线SABL或互补读出位线SABLB,另一端子用于接收预设电压V

进一步地,第一处理结构版图还包括:均衡栅极331,设置在第一有源层301上,在第一方向上延伸,且第一预充栅极321、第一隔离栅极311和均衡栅极331在第二方向上依次排布;其中,均衡栅极331用于接收均衡信号(Equalizing Signal,EQ);位于均衡栅极331两侧且远离第一隔离栅极311的第一有源层301连接互补读出位线SABLB;位于均衡栅极331两侧且与第一隔离栅极311共用的第一有源层301连接SABL。

均衡栅极331和第一有源层301用于形成均衡MOS管<31>,均衡MOS管<31>连接在读出位线SABL和互补读出位线SABLB之间,且具有接收均衡信号EQ的控制端子。具体地,在本实施例中,均衡MOS管<31>的源极连接读出位线SABL,漏极连接互补读出位线SABLB,栅极用于接收均衡信号EQ。

在偏移消除过程中,位线BL和读出位线BLB的电平仅受第一NMOS管

在另一个实施例中,参考图3和图4,读出电路架构,还包括:

参考图3,第一处理结构版图还包括:第一预充栅极321和第三预充栅极323,设置在在第一有源层301上,在第一方向上延伸,且第一预充栅极321、第一隔离栅极311和第三预充栅极323在第二方向上依次排布;其中,第一预充栅极321用于接收预充电信号PRE,位于第一预充栅极321两侧且远离第一隔离栅极311的第一有源层301用于接收预设电压V

进一步地,第一处理结构版图还包括:均衡栅极331,设置在第一有源层301上,在第一方向上延伸,且第一预充栅极321、第一隔离栅极311、均衡栅极331和第三预充栅极323在第二方向上依次排布;其中,均衡栅极331用于接收均衡信号EQ;位于均衡栅极331两侧且与第三预充栅极323共用的第一有源层301连接读出位线SABL;位于均衡栅极331两侧且与第一隔离栅极311共用的第一有源层301连接互补读出位线SABLB。均衡栅极331和第一有源层301用于形成均衡MOS管<31>。

第二处理结构版图还包括:第二预充栅极322,设置在第二有源层302上,在第一方向上延伸,且第二预充栅极322和第二隔离栅极312在第二方向上依次排布;其中,第二预充栅极322用于接收预充电信号PRE;位于第二预充栅极322两侧且远离第二隔离栅极312的第二有源层302用于接收预设电压V

参考图4,第一处理结构版图可以设置为第一隔离栅极311、第一预充栅极321、第三预充栅极323和均衡栅极331在第二方向上依次排布,第二处理结构板图可以设置为,第二隔离栅极312和第二预充栅极322在第二方向上依次排布。

在一个例子中,参考图5~图7,在第一方向上,用于电连接预设电压V

具体地,参考图5,在第一有源层中301中,在第一方向上排列的多个第一预充电MOS管<21>中,用于连接预设电压V

具体地,参考图6,在第一有源层中301中,在第一方向上排列的多个第一预充电MOS管<21>中,用于连接预设电压V

具体地,参考图7,在第一有源层中301中,在第一方向上排列的多个第一预充电MOS管<21>和多个第三预充电MOS管<23>中,用于连接预设电压V

另外,本实施例还给出了多种第一处理结构版图、第二处理结构版图、第一NMOS版图、第二NMOS版图、第一PMOS版图和第二PMOS版图的排布方式。

参考图2~图7,第一布局方式即在第二方向上,第一处理结构版图、第一NMOS版图、第一PMOS版图、第二PMOS版图、第二NMOS版图和第二处理结构版图依次排列。

参考图8~图10,第二布局方式即在第二方向上,第一处理结构版图、第一PMOS版图、第一NMOS版图、第二NMOS版图、第二PMOS版图和第二处理结构版图依次排列。

需要说明的是,本方式同样适用于用于电连接预设电压V

参考图11和图12,第三布局方式即在第二方向上,第一NMOS版图、第一处理结构版图、第一PMOS版图、第二PMOS版图、第二处理结构版图和第二NMOS版图依次排列。

第四布局方式即在第二方向上,第一PMOS版图、第一处理结构版图、第一NMOS版图、第二NMOS版图、第二处理结构版图和第二PMOS版图依次排列。

参考图13,第五布局方式即在第二方向上,第一PMOS版图、第一NMOS版图、第一处理结构、第二处理结构、第二NMOS版图和第二PMOS版图依次排列。

参考图14,第六布局方式即在第二方向上,第一NMOS版图、第一PMOS版图、第一处理结构、第二处理结构、第二PMOS版图和第二NMOS版图依次排列。

需要说明的是,在第五布局方式和第六布局方式中,第一有源层和第二有源层相连接。进一步地,参考图15,第五布局方式和第六布局方式依然适用于用于电连接预设电压V

需要说明的是,上述各个晶体管定义的具体“源极”和“漏极”的连接方式,并不构成对本实施例的限定,在其他实施例中,可以采用“漏极”替换“源极”,“源极”替换“漏极”的连接方式。

在偏移消除过程中,第一PMOS管的栅极连接互补读出位线,漏极连接读出位线,第一PMOS管导通后第一信号端与读出位线电连接,且第一信号端用于接收对应逻辑“1”的高电平,即第一信号端接收芯片内部电源电压;此时导通后的第一PMOS管基于互补读出位线的电平和阈值电压影响读出位线的电平;第二PMOS管的栅极连接读出位线,漏极连接互补读出位线,第二PMOS管导通后第一信号端与读出位线电连接,且第一信号端用于接收对应逻辑“1”的高电平,即第一信号端芯片内部电源电压;此时导通后的第二PMOS管基于读出位线的电平和阈值电压影响互补读出位线的电平,第一PMOS管和第二PMOS管的阈值电压差异会导致读出位线和互补读出位线的电平差异,即通过读出位线和互补读出位线的电平,反应出第一PMOS管和第二PMOS管的偏移噪声。第一NMOS管的栅极连接至互补读出位线,漏极连接位线;第二NMOS管的栅极连接至读出位线,漏极互补位线;由于第一隔离MOS管<11>和第二隔离MOS管<12>的连接方式,在偏移消除进行时,第一隔离MOS管<11>和第二隔离MOS管<12>不导通,且第二信号端也用于接收对应逻辑“1”的高电平,即第一信号端接收芯片内部电源电压;使得第一NMOS管和第二NMOS管的导通差异并不影响读出位线和互补读出位线,而是直接调整位线电压和互补位线电压。另外,由于读出位线和互补读出位线的电平已反应出第一PMOS管和第二PMOS管的偏移噪声,且第一NMOS管的导通程度基于互补读出位线的电平和第一NMOS管的阈值电压确定,第二NMOS管的导通程度基于读出位线的电平和第二NMOS管的阈值电压确定;此时,第一NMOS管和第二NMOS管分别基于互补读出位线和读出位线导通后,使调整后的位线电压和互补位线反应出第一PMOS管和第二PMOS管的偏移噪声,并同时反应出第一NMOS管和第二NMOS管的偏移噪声,即完成读出电路的偏移消除操作。因此,本实施例提供的读出电路的版图可以避免布局偏移消除MOS管,从而减小了读出电路的版图面积。

需要说明的是,为了突出本申请的创新部分,本实施例中并没有将与解决本申请所提出的技术问题关系不太密切的单元引入,但这并不表明本实施例中不存在其它的单元;本领域的普通技术人员可以理解,上述各实施例是实现本申请的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本申请的精神和范围。

本领域的普通技术人员可以理解,上述各实施例是实现本申请的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本申请的精神和范围。