硬掩膜的制作方法、图形的制作方法及半导体结构

文献发布时间:2023-06-19 19:00:17

技术领域

本申请涉及半导体制造领域,尤其涉及一种硬掩膜的制作方法、图形的制作方法及半导体结构。

背景技术

在半导体制造过程中,特征尺寸越来越小,并趋近于曝光系统的理论极限,光刻后硅片表面的成像将产生严重的畸变,即产生光学邻近效应。由此,发展了自对准双重成像技术,其原理是经过一次光刻后,在第一次光刻图形周围淀积侧墙,再通过刻蚀实现对空间图形的倍频。

但是,在第一次光刻图形周围淀积侧墙的过程中,一般在硬遮罩上采用离子式原子堆叠氧化硅,会破坏硬遮罩的形状,从而无法精准控制硬遮罩破坏程度导致后续关键尺寸大小不均,最后影响半导体器件的良率。

因此如何减小硬遮罩的破坏程度是需要解决的技术问题。

发明内容

本申请所要解决的技术问题是提供一种硬掩膜的制作方法、图形的制作方法及半导体结构,以减小硬遮罩的破坏程度。

为了解决上述问题,本申请提供了一种硬掩膜的制作方法。所述硬掩膜的制作方法,包括:提供基底,所述基底上形成有图形化的牺牲层;形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁;形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁;去除所述牺牲层;去除所述第一掩膜层侧壁处的所述第一保护层。

在一些实施例中,所述形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁的步骤中,所述第一保护层还覆盖所述牺牲层的上表面及所述基底暴露的表面;所述形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁的步骤包括:形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层表面;去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,暴露出所述牺牲层顶部及部分基底表面。

在一些实施例中,所述去除所述第一掩膜层侧壁处的所述第一保护层包括:沿所述第一掩膜层的侧壁向下刻蚀第一保护层。

在一些实施例中,所述基底包括衬底及设置在所述衬底上的第二掩膜层的步骤包括:以所述第一掩膜层为掩膜,在所述第二掩膜层上形成初始图案。

在一些实施例中,所述衬底包括半导体衬底及设置在所述半导体衬底上的氧化物层及多晶硅层。

在一些实施例中,所述第一保护层为氮化物层。

在一些实施例中,所述第一掩膜层为氧化物层。

在一些实施例中,所述形成第一保护层的制程中温度为600~700摄氏度。

在一些实施例中,所述形成第一掩膜层的制程中压力为0.1~50托,温度为25~600摄氏度。

在一些实施例中,所述形成第一掩膜层的原料为二(异丙氨基)硅烷、双(叔丁基氨基)硅烷、或双(二乙基氨基)硅烷。

在一些实施例中,所述形成第一掩膜层的方式为等离子体增强型原子沉积、热原子沉积、或触媒原子沉积中的一种。

在一些实施例中,所述去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,采用六氟化硫、四氟化碳、氯气、或氩气中的一种或多种气体对所述第一掩膜层进行刻蚀。

本申请还提供了一种图形的制作方法。所述图形的制作方法,包括:提供基底,所述基底上形成有图形化的牺牲层;形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁;形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁;去除所述牺牲层;去除所述第一掩膜层侧壁处的所述第一保护层;以所述第一掩膜层为掩膜,在所述基底上形成目标图形。

在一些实施例中,所述形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁的步骤中,所述第一保护层还覆盖所述牺牲层的上表面及所述基底暴露的表面;所述形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁的步骤包括:形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层表面;去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,暴露出所述牺牲层顶部及部分基底表面。

在一些实施例中,所述去除所述第一掩膜层侧壁处的所述第一保护层包括:沿所述第一掩膜层的侧壁向下刻蚀第一保护层。

在一些实施例中,所述基底包括衬底及设置在所述衬底上的第二掩膜层,以所述第一掩膜层为掩膜,在所述基底上形成目标图形的步骤包括:以所述第一掩膜层为掩膜,在所述第二掩膜层上形成初始图案;以所述第二掩膜层为掩膜,将所述初始图案转移到所述衬底上,形成所述目标图案。

在一些实施例中,所述衬底包括半导体衬底及设置在所述半导体衬底上的氧化物层及多晶硅层,所述目标图案贯穿所述氧化物层及多晶硅层,并延伸至所述半导体衬底内。

本申请还提供了一种半导体结构。所述半导体结构,包括:基底;图形化的第一保护层,形成于所述基底表面;图形化的第一掩膜层,覆盖所述第一保护层,所述第一保护层与所述第一掩膜层重叠。

在一些实施例中,在所述基底内具有以所述第一保护层与所述第一掩膜层作为掩膜形成的目标图案。

在一些实施例中,所述基底还包括半导体衬底及设置在所述半导体衬底上的氧化物层及多晶硅层,所述目标图案贯穿所述氧化物层及多晶硅层,并延伸至所述半导体衬底内。

上述技术方案,通过在所述基底上形成有图形化的牺牲层;形成至少覆盖所述牺牲层侧壁的第一保护层;形成覆盖所述第一保护层侧壁的第一掩膜层,保留了完整的牺牲层。因此在去除所述牺牲层后,通过去除所述第一掩膜层侧壁处的所述第一保护层形成的硬掩膜位置准确无偏移,在往下转移图形时,避免因硬掩膜的位置偏差导致的后续关键尺寸大小不均,提高了半导体器件的良率。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

为了更清楚地说明本申请实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

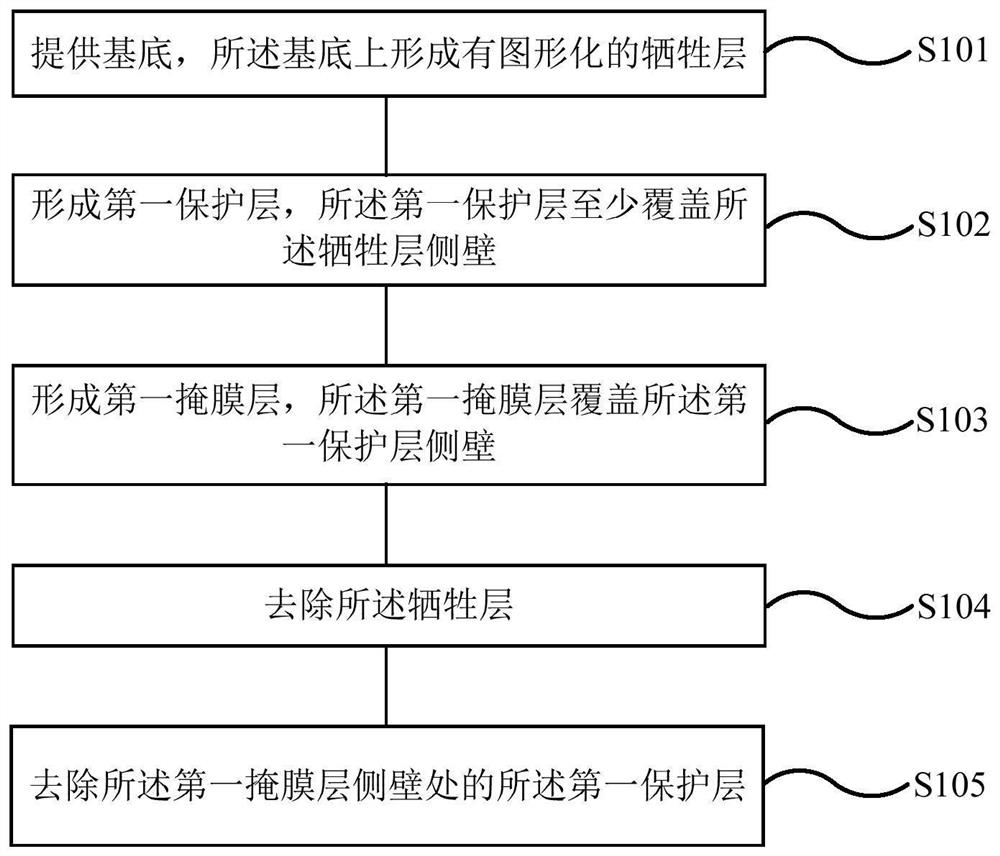

图1是本申请一实施例中硬掩膜的制作方法的示意图。

图2是本申请一实施例中基底的示意图。

图3是本申请一实施例中第一保护层的示意图。

图4是本申请另一实施例中第一保护层的示意图。

图5是本申请一实施例中形成第一掩膜层的示意图。

图6是本申请一实施例中第一掩膜层的示意图。

图7是本申请一实施例中第一掩膜层的示意图。

图8是本申请一实施例中去除所述牺牲层的示意图。

图9是本申请一实施例中硬掩膜的示意图。

图10是本申请一实施例中基底的示意图。

图11本申请一实施例中初始图案的示意图。

图12是本申请一实施例中图形的制作方法的示意图。

图13是本申请一实施例中衬底的示意图。

图14是本申请一实施例中目标图案的示意图。

图15是本申请一实施例中半导体结构的示意图。

图16是本申请一实施例中目标图案的示意图。

具体实施方式

下面结合附图对本申请提供的的具体实施方式做详细说明。

图1是本申请一实施例中硬掩膜的制作方法的示意图。所述硬掩膜的制作方法,包括:步骤S101,提供基底,所述基底上形成有图形化的牺牲层;步骤S102,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁;步骤S103,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁;步骤S104,去除所述牺牲层;步骤S105,去除所述第一掩膜层侧壁处的所述第一保护层。

下面请继续参阅图1,步骤S101,提供基底,所述基底上形成有图形化的牺牲层。图2是本申请一实施例中基底的示意图。下面请参阅图2,提供基底1,所述基底1上形成有图形化的牺牲层2。在本实施例中,所述牺牲层2包括第一牺牲层21及第二牺牲层22,所述第一牺牲层为氮化硅层,所述第二牺牲层为旋涂硬掩膜层。

下面请继续参阅图1,步骤S102,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁。在本实施例中,所述第一保护层为氮化物层。所述形成第一保护层的制程中温度为600~700摄氏度。

图3是本申请一实施例中第一保护层的示意图。下面请参阅图3,在本实施例中,形成第一保护层3,所述第一保护层3至少覆盖所述第一牺牲层21及第二牺牲层22的侧壁。图4是本申请另一实施例中第一保护层的示意图。下面请参阅图4,在本实施例中,所述形成第一保护层3,所述第一保护层3至少覆盖所述牺牲层2侧壁的步骤中,所述第一保护层3还覆盖所述牺牲层2的上表面及所述基底1暴露的表面。

下面请继续参阅图1,步骤S103,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁。在本实施例中,所述第一掩膜层为氧化物层。在一些实施例中,所述形成第一掩膜层的制程中压力为0.1~50托,温度为25~600摄氏度。在一些实施例中,所述形成第一掩膜层的原料为二(异丙氨基)硅烷(diisopropylaminosilane,LTO)、双(叔丁基氨基)硅烷(bis(t-butylamino)silane,2NTE)、或双(二乙基氨基)硅烷(bis(diethylamino)silane,SAM-24)。在一些实施例中,所述形成第一掩膜层的方式为等离子体增强型原子沉积、热原子沉积、或触媒原子沉积中的一种。

图5是本申请一实施例中形成第一掩膜层的示意图。下面请参阅图5,在本实施例中,所述形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁的步骤包括:步骤S501,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层表面;步骤S502,去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,暴露出所述牺牲层顶部及部分基底表面。在一些实施例中,所述去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,采用六氟化硫、四氟化碳、氯气、或氩气中的一种或多种气体对所述第一掩膜层进行刻蚀。

图6是本申请一实施例中第一掩膜层的示意图。下面请参阅图6,形成第一掩膜层4,所述第一掩膜层4覆盖所述第一保护层3表面。图7是本申请一实施例中第一掩膜层的示意图。下面请参阅图7,去除所述牺牲层2顶部的第一掩膜层4、第一保护层3及牺牲层2之间的部分第一掩膜层4及第一保护层3,暴露出所述牺牲层2顶部及部分基底1表面。在牺牲层2的侧壁上形成了第一保护层3,避免在形成第一掩膜层4时对牺牲层2造成的破坏。

下面请继续参阅图1,步骤S104,去除所述牺牲层。图8是本申请一实施例中去除所述牺牲层的示意图。在本实施例中,所述牺牲层包括第一牺牲层及第二牺牲层,去除所述第一牺牲层及第二牺牲层后,在所述基底1上保留了部分第一掩膜层4及第一保护层3。

下面请继续参阅图1,步骤S105,去除所述第一掩膜层侧壁处的所述第一保护层。所述去除所述第一掩膜层侧壁处的所述第一保护层包括:沿所述第一掩膜层的侧壁向下刻蚀第一保护层。图9是本申请一实施例中硬掩膜的示意图。下面请参阅图9,沿所述第一掩膜层4的侧壁向下刻蚀第一保护层3,在基底1上保留的第一保护层3及第一掩膜层4重叠,形成硬掩膜。

图10是本申请一实施例中基底的示意图。下面请参阅图10,所述基底1包括衬底11及设置在所述衬底11上的第二掩膜层12,以所述第一掩膜层4为掩膜,在所述第二掩膜层12上形成初始图案。图11本申请一实施例中初始图案的示意图。下面请参阅图11,以所述第一掩膜层为掩膜,在所述第二掩膜层12上形成初始图案。在一些实施例中,所述衬底包括半导体衬底及设置在所述半导体衬底上的氧化物层及多晶硅层。

上述技术方案,通过步骤S101,在所述基底1上形成有图形化的牺牲层2;步骤S102,形成至少覆盖所述牺牲层2侧壁的第一保护层3;步骤S103,形成覆盖所述第一保护层3侧壁的第一掩膜层4,保留了完整的牺牲层2。因此在去除所述牺牲层2后,通过去除所述第一掩膜层侧壁处的所述第一保护层形成的硬掩膜位置准确无偏移,在往下转移图形时,避免因硬掩膜的位置偏差导致的后续关键尺寸大小不均,提高了半导体器件的良率。

本申请还提供了一种图形的制作方法。图12是本申请一实施例中图形的制作方法的示意图。下面请参阅图12,所述图形的制作方法,包括:步骤S121,提供基底,所述基底上形成有图形化的牺牲层;步骤S122,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁;步骤S123,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁;步骤S124,去除所述牺牲层;步骤S125,去除所述第一掩膜层侧壁处的所述第一保护层;步骤S126,以所述第一掩膜层为掩膜,在所述基底上形成目标图形。

下面请继续参阅图12,步骤S121,提供基底,所述基底上形成有图形化的牺牲层。图2是本申请一实施例中基底的示意图。下面请参阅图2,提供基底1,所述基底1上形成有图形化的牺牲层2。在本实施例中,所述牺牲层2包括第一牺牲层21及第二牺牲层22,所述第一牺牲层为氮化硅层,所述第二牺牲层为旋涂硬掩膜层。

下面请继续参阅图12,步骤S122,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁。在本实施例中,所述第一保护层为氮化物层。所述形成第一保护层的制程中温度为600~700摄氏度。

图3是本申请一实施例中第一保护层的示意图。下面请参阅图3,在本实施例中,形成第一保护层3,所述第一保护层3至少覆盖所述第一牺牲层21及第二牺牲层22的侧壁。图4是本申请另一实施例中第一保护层的示意图。下面请参阅图4,在本实施例中,所述形成第一保护层3,所述第一保护层3至少覆盖所述牺牲层2侧壁的步骤中,所述第一保护层3还覆盖所述牺牲层2的上表面及所述基底1暴露的表面。

下面请继续参阅图12,步骤S123,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁。在本实施例中,所述第一掩膜层为氧化物层。在一些实施例中,所述形成第一掩膜层的制程中压力为0.1~50托,温度为25~600摄氏度。在一些实施例中,所述形成第一掩膜层的原料为二(异丙氨基)硅烷、双(叔丁基氨基)硅烷、或双(二乙基氨基)硅烷。在一些实施例中,所述形成第一掩膜层的方式为等离子体增强型原子沉积、热原子沉积、或触媒原子沉积中的一种。

图5是本申请一实施例中形成第一掩膜层的示意图。下面请参阅图5,在本实施例中,所述形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁的步骤包括:步骤S501,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层表面;步骤S502,去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,暴露出所述牺牲层顶部及部分基底表面。在一些实施例中,所述去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,采用六氟化硫、四氟化碳、氯气或氩气中的一种或多种气体对所述第一掩膜层进行刻蚀。

图6是本申请一实施例中第一掩膜层的示意图。下面请参阅图6,形成第一掩膜层4,所述第一掩膜层4覆盖所述第一保护层3表面。图7是本申请一实施例中第一掩膜层的示意图。下面请参阅图7,去除所述牺牲层顶部的第一掩膜层4、第一保护层3及牺牲层2之间的部分第一掩膜层4及第一保护层3,暴露出所述牺牲层2顶部及部分基底1表面。在牺牲层2的侧壁上形成了第一保护层3,避免在形成第一掩膜层4时对牺牲层造成的破坏。

下面请继续参阅图12,步骤S124,去除所述牺牲层。图8是本申请一实施例中去除所述牺牲层的示意图。在本实施例中,所述牺牲层包括第一牺牲层及第二牺牲层,去除所述第一牺牲层及第二牺牲层后,在所述基底1上保留了部分第一掩膜层4及第一保护层3。

下面请继续参阅图12,步骤S125,去除所述第一掩膜层侧壁处的所述第一保护层。所述去除所述第一掩膜层侧壁处的所述第一保护层包括:沿所述第一掩膜层的侧壁向下刻蚀第一保护层。图9是本申请一实施例中硬掩膜的示意图。下面请参阅图9,沿所述第一掩膜层4的侧壁向下刻蚀第一保护层3,在基底1上保留的第一保护层3及第一掩膜层4重叠,形成硬掩膜。

下面请继续参阅图12,步骤S126,以所述第一掩膜层为掩膜,在所述基底上形成目标图形。在一些实施例中,所述基底包括衬底及设置在所述衬底上的第二掩膜层,以所述第一掩膜层为掩膜,在所述基底上形成目标图形的步骤包括:以所述第一掩膜层为掩膜,在所述第二掩膜层上形成初始图案;以所述第二掩膜层为掩膜,将所述初始图案转移到所述衬底上,形成所述目标图案。

图10是本申请一实施例中基底的示意图。下面请参阅图10,所述基底1包括衬底11及设置在所述衬底11上的第二掩膜层12,以所述第一掩膜层4为掩膜,在所述第二掩膜层12上形成初始图案。图11本申请一实施例中初图案的示意图。下面请参阅图11,以所述第一掩膜层为掩膜,在所述第二掩膜层12上形成初始图案。图13是本申请一实施例中衬底的示意图。在本实施例中,所述衬底11包括半导体衬底111及设置在所述半导体衬底111上的氧化物层113及多晶硅层112。以形成所述初始图案后的第二掩膜层为掩膜,将所述初始图案转移到所述衬底上,形成所述目标图案。图14是本申请一实施例中目标图案的示意图。下面请参阅图14,所述目标图案贯穿所述氧化物层113及多晶硅层112,并延伸至所述半导体衬底111内。

上述技术方案,通过步骤S101,在所述基底上形成有图形化的牺牲层2;步骤S102,形成至少覆盖所述牺牲层2侧壁的第一保护层3;步骤S103,形成覆盖所述第一保护层3侧壁的第一掩膜层4,保留了完整的牺牲层2。因此在去除所述牺牲层2后,通过去除所述第一掩膜层侧壁处的所述第一保护层形成的硬掩膜位置准确无偏移,在往下转移图形以形成所述目标图案时,避免因硬掩膜的位置偏差导致的后续关键尺寸大小不均,提高了半导体器件的良率。

本申请还提供了一种半导体结构。图15是本申请一实施例中半导体结构的示意图。下面请参阅图15,所述半导体结构,包括:基底1;图形化的第一保护层3,形成于所述基底1表面;图形化的第一掩膜层4,覆盖所述第一保护层3,所述第一保护层3与所述第一掩膜层4重叠。

在一些实施例中,所述基底还包括半导体衬底及设置在所述半导体衬底上的氧化物层及多晶硅层,所述目标图案贯穿所述氧化物层及多晶硅层,并延伸至所述半导体衬底内。在所述基底内具有以所述第一保护层与所述第一掩膜层作为掩膜形成的目标图案。图16是本申请一实施例中目标图案的示意图。下面请参阅图16,所述目标图案5贯穿所述氧化物层113及多晶硅层112,并延伸至所述半导体衬底111内。

图12是本申请一实施例中图形的制作方法的示意图。下面请参阅图12,所述图形的制作方法,包括:步骤S121,提供基底,所述基底上形成有图形化的牺牲层;步骤S122,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁;步骤S123,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁;步骤S124,去除所述牺牲层;步骤S125,去除所述第一掩膜层侧壁处的所述第一保护层;步骤S126,以所述第一掩膜层为掩膜,在所述基底上形成目标图形。

下面请继续参阅图12,步骤S121,提供基底,所述基底上形成有图形化的牺牲层。图2是本申请一实施例中基底的示意图。下面请参阅图2,提供基底1,所述基底包括图形化的牺牲层2。在本实施例中,所述牺牲层2包括第一牺牲层21及第二牺牲层22,所述第一牺牲层为氮化硅层,所述第二牺牲层为旋涂硬掩膜层。

下面请继续参阅图12,步骤S122,形成第一保护层,所述第一保护层至少覆盖所述牺牲层侧壁。在本实施例中,所述第一保护层为氮化物层。所述形成第一保护层的制程中温度为600~700摄氏度。

图3是本申请一实施例中第一保护层的示意图。下面请参阅图3,在本实施例中,形成第一保护层3,所述第一保护层3至少覆盖所述第一牺牲层21及第二牺牲层22的侧壁。图4是本申请另一实施例中第一保护层的示意图。下面请参阅图4,在本实施例中,所述形成第一保护层3,所述第一保护层3至少覆盖所述牺牲层2侧壁的步骤中,所述第一保护层3还覆盖所述牺牲层2的上表面及所述基底1暴露的表面。

下面请继续参阅图12,步骤S123,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁。在本实施例中,所述第一掩膜层为氧化物层。在一些实施例中,所述形成第一掩膜层的制程中压力为0.1~50托,温度为25~600摄氏度。在一些实施例中,所述形成第一掩膜层的原料为二(异丙氨基)硅烷、双(叔丁基氨基)硅烷、或双(二乙基氨基)硅烷。在一些实施例中,所述形成第一掩膜层的方式为等离子体增强型原子沉积、热原子沉积、或触媒原子沉积中的一种。

图5是本申请一实施例中形成第一掩膜层的示意图。下面请参阅图5,在本实施例中,所述形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层侧壁的步骤包括:步骤S501,形成第一掩膜层,所述第一掩膜层覆盖所述第一保护层表面;步骤S502,去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,暴露出所述牺牲层顶部及部分基底表面。在一些实施例中,所述去除所述牺牲层顶部的第一掩膜层、第一保护层及牺牲层之间的部分第一掩膜层及第一保护层,采用六氟化硫、四氟化碳、氯气、或氩气中的一种或多种气体对所述第一掩膜层进行刻蚀。

图6是本申请一实施例中第一掩膜层的示意图。下面请参阅图6,形成第一掩膜层4,所述第一掩膜层4覆盖所述第一保护层3表面。图7是本申请一实施例中第一掩膜层的示意图。下面请参阅图7,去除所述牺牲层顶部的第一掩膜层4、第一保护层3及牺牲层2之间的部分第一掩膜层4及第一保护层3,暴露出所述牺牲层2顶部及部分基底1表面。在牺牲层2的侧壁上形成了第一保护层3,避免在形成第一掩膜层4时对牺牲层造成的破坏。

下面请继续参阅图12,步骤S124,去除所述牺牲层。图8是本申请一实施例中去除所述牺牲层的示意图。在本实施例中,所述牺牲层包括第一牺牲层及第二牺牲层,去除所述第一牺牲层及第二牺牲层后,在所述基底1上保留了部分第一掩膜层4及第一保护层3。

下面请继续参阅图12,步骤S125,去除所述第一掩膜层侧壁处的所述第一保护层。所述去除所述第一掩膜层侧壁处的所述第一保护层包括:沿所述第一掩膜层的侧壁向下刻蚀第一保护层。图9是本申请一实施例中硬掩膜的示意图。下面请参阅图9,沿所述第一掩膜层4的侧壁向下刻蚀第一保护层3,在基底1上保留的第一保护层3及第一掩膜层4重叠,形成硬掩膜。

下面请继续参阅图12,步骤S126,以所述第一掩膜层为掩膜,在所述基底上形成目标图形。在一些实施例中,所述基底包括衬底及设置在所述衬底上的第二掩膜层,以所述第一掩膜层为掩膜,在所述基底上形成目标图形的步骤包括:以所述第一掩膜层为掩膜,在所述第二掩膜层上形成初始图案;以所述第二掩膜层为掩膜,将所述初始图案转移到所述衬底上,形成所述目标图案。

上述技术方案,通过在所述基底上形成有图形化的牺牲层2;形成至少覆盖所述牺牲层2侧壁的第一保护层3;形成覆盖所述第一保护层3侧壁的第一掩膜层4,保留了完整的牺牲层2。因此在去除所述牺牲层2后,通过去除所述第一掩膜层侧壁处的所述第一保护层形成的硬掩膜位置准确无偏移,在往下转移图形以形成所述目标图案时,避免因硬掩膜的位置偏差导致的后续关键尺寸大小不均,提高了半导体器件的良率。

以上所述仅是本申请的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 掩膜版及其制作方法、半导体器件的形成方法

- 一种掩膜单元及其制作方法、掩膜版

- 掩膜版组合和使用掩膜版组合将半导体薄膜图形化的方法

- 硬掩膜层的制作方法、层间介质层的制作方法及半导体器件

- 硬掩膜层的制作方法、层间介质层的制作方法及半导体器件