基片处理系统、基片处理方法和基片处理装置

文献发布时间:2023-06-19 19:18:24

本申请是申请号为201780031969.7、申请日为2017年5月22日的发明名称为“处理被处理体的方法”的申请的分案申请。

技术领域

本发明的实施方式涉及处理被处理体的方法。

背景技术

在半导体器件这样的电子器件的制造工艺中,在被处理层上形成掩模,并为了将该掩模的图案转印到该被处理层而进行蚀刻。作为掩模,通常使用抗蚀剂掩模。抗蚀剂掩模通过光刻技术形成。因此,形成在被蚀刻层的图案的极限尺寸受到通过光刻技术形成的抗蚀剂掩模的分辨率极限、图案密度等影响,近年来,伴随着电子器件的高集成化,要求形成比抗蚀剂掩模的分辨率极限更小尺寸的图案。因此,如专利文献1记载的那样,提案有通过在抗蚀剂掩模上形成氧化硅膜,调整该抗蚀剂掩模的尺寸,并利用该抗蚀剂掩模缩小能够提供的开口的宽度的技术。

在专利文献1公开的精细图案形成方法中,在要形成精细图案的物质膜上形成光致抗蚀剂图案,在其上蒸镀氧化硅膜,但必须对下部的光致抗蚀剂图案不施加损伤保形地较薄地形成。并且,之后要对下部膜实施干蚀刻,起初在光致抗蚀剂图案的侧壁形成间隔部,接着在光致抗蚀剂图案上形成聚合物膜。

现有技术文献

专利文献

专利文献1:日本特开2004-80033号公报

发明内容

发明想要解决的技术问题

在形成具有比抗蚀剂掩模的分辨率极限小的尺寸的图案时,要求图案的槽的高精细的最小线宽(CD:Critical Dimension)的控制。图案越精细,最小线宽的不均的影响越大。因此,在被处理体上的图案形成中,为了伴随着高集成化的细微化,必须实现抑制高精度的最小线宽的不均的方法。

用于解决技术问题的技术方案

在一种方式中,提供一种处理被处理体的方法,被处理体包括被处理层和设置在该被处理层的主面的掩模。该方法包括:包括:调节掩模的图案的槽宽度的第一步骤;和在执行第一步骤之后,利用掩模蚀刻被处理层的第二步骤。主面在该方法中被划分为多个区域,第一步骤包括:按在该方法中所划分的多个区域的每一区域测定槽宽度的值的第三步骤;第四步骤,在执行第三步骤之后,按多个区域的每一区域计算从通过该第三步骤测定得到的槽宽度的值减去该槽宽度的基准值而得到的正的差值;第五步骤,在执行第四步骤之后,在被送入到等离子体处理装置的处理容器内的被处理体的掩模的表面,形成通过该第四步骤计算出的多个区域的每一区域的差值的膜厚的膜。第五步骤包括第十步骤和第十一步骤,其中,第十步骤,在膜形成处理中,利用预先取得的对应数据和与在第四步骤中按多个区域的每一区域计算出的差值对应的膜厚,按该多个区域的每一区域调节被送入到处理容器内的被处理体的该被处理层的温度,其中,膜形成处理反复执行包括以下步骤的流程:向处理容器内供给第一气体的第六步骤;在执行第六步骤之后,对处理容器内进行吹扫的第七步骤;在执行第七步骤之后,在处理容器内生成第二气体的等离子体的第八步骤;和在执行第八步骤之后,对处理容器内进行吹扫的第九步骤,对应数据表示被处理层的温度与沉积在该被处理层上的掩模的表面的膜的膜厚的对应,第十一步骤,在执行第十步骤之后,执行膜形成处理,在被处理层上的掩模的表面形成膜。第六步骤所需要的处理时间为,在第六步骤中沉积在被处理层上的掩模的表面的膜的膜厚成为根据该被处理层的温度的高低而增减的状态的时间以内,第一气体包含氨基硅烷类气体,第二气体包含含有氧原子和碳原子的气体。

在上述方法中,在蚀刻被处理层的第二步骤之前,实施调节掩模的图案的槽宽度的第一步骤。在第一步骤中,将被处理层的主面划分为多个区域,在第三步骤和第四步骤中按多个区域的每一区域计算出掩模的槽宽度与该槽宽度的基准值的差值,在第五步骤中,在掩模形成与该差值对应的膜厚的膜,按多个区域的每一区域将掩模的槽宽度修正为该基准值。在第五步骤中,利用反复执行第六步骤~第九步骤的膜形成处理,通过与ALD(AtomicLayer Deposition)法同样的方法在掩模按每一原子层高精细地形成膜。在膜形成处理中形成的膜的膜厚根据被处理层的温度而不同,所以,在第十步骤中,利用表示被处理层的温度与形成的膜的膜厚的对应的对应数据,按多个区域的每一区域,调节被处理层的温度,以使其成为与在第四步骤计算出的差值对应的膜厚的膜的形成所需要的温度。像这样,在第二步骤进行的蚀刻之前,在被处理层的主面的多个区域的每一区域,决定与掩模的槽的修正量对应的膜厚,利用对应数据决定该膜厚的形成所需要的被处理层的温度,以按多个区域的每一区域所决定的温度调节了被处理层的温度之后的状态下,进行与ALD法同样的膜形成处理,所以能够按被处理层的主面的多个区域的每一区域高精细地且充分地抑制掩模的图案的不均。

在一个实施方式中,第十步骤按该多个区域的每一区域基于对应数据调节该被处理层的温度,以使得被送入到处理容器内的被处理体的被处理层中的多个区域的每一区域的温度,成为与在第四步骤中按该多个区域的每一区域计算出的差值的膜厚对应的温度。

在一个实施方式中,第五步骤包括不依赖于多个区域地对掩模的表面保形地形成膜的第十二步骤,第十步骤按该多个区域的每一区域基于对应数据调节该被处理层的温度,以使得被送入到处理容器内的被处理体的被处理层中的多个区域的每一区域的温度,成为与从在第四步骤中按该多个区域的每一区域计算出的差值的膜厚减去在第十二步骤中保形地形成的膜的膜厚而得到的值对应的温度,第十二步骤在第十步骤之前或者膜形成处理之后进行。像这样,关于多个区域的每一区域的膜厚中共同的膜厚,能够不经由按多个区域的每一区域进行的被处理层的温度的调节地、局部地形成膜。

在一个实施方式中,第一步骤在执行第五步骤之后再次执行第三步骤和第四步骤,在通过该再次执行在该第四步骤计算出的差值没有满足预先设定的基准范围的情况下,再次执行第五步骤。这样,通过第五步骤进行了膜的形成之后,再次计算出掩模的槽宽度的差值,判断差值是否在基准范围中,当差值不在基准范围中时,再次进行膜的形成,因此能够进一步充分地抑制掩模的槽宽度的不均。

在一个实施方式中,第一气体的氨基硅烷类气体能够包含含有1~3个硅原子的氨基硅烷。第一气体的氨基硅烷类气体能够包含含有1~3个氨基的氨基硅烷。像这样,在第一气体的氨基硅烷类气体中,能够使用含有1~3个硅原子的氨基硅烷。另外,在第一气体的氨基硅烷类气体中,能够使用含有1~3个氨基的氨基硅烷。

发明效果

如以上所说明,提供一种方法,在被处理体上的图案形成中,抑制高精度的最小线宽的不均。

附图说明

图1是表示一该实施方式的处理被处理体的方法的流程图。

图2是例示图1所示的方法的适用对象即被处理体的截面图。

图3是表示图1所示的方法的执行中能够使用的处理系统的一例的图。

图4是表示图3所示的处理系统能够具有的等离子体处理装置的一例的图。

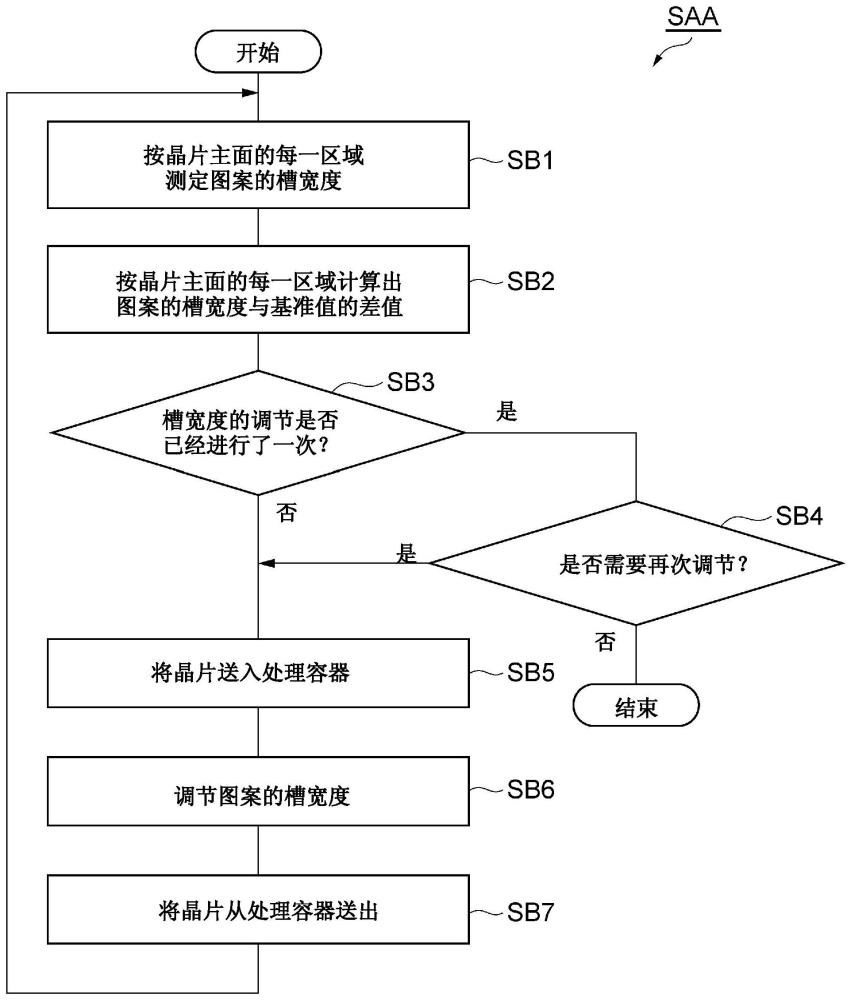

图5是表示图1所示的方法能够包括的步骤、即在蚀刻前的图案的槽宽度的调节处理的步骤的一例的图。

图6包括(a)部分和(b)部分,图6的(a)部分是表示执行图5所示的步骤前的被处理体的状态的截面图,图6的(b)部分是表示执行图5所示的步骤后的被处理体的状态的截面图。

图7是将在一个实施方式的处理被处理体的方法中所划分的被处理体的主面的多个区域的一部分作为一例示意性地表示的图。

图8是表示图5所示的步骤的一部分的步骤、即调节图案的槽宽度的步骤的一例的流程图。

图9是表示图8所示的步骤中能够包括的步骤、即在被处理体的主面形成均匀的膜的步骤的一例的流程图。

图10包括(a)部分、(b)部分和(c)部分,图10的(a)部分例如是示意性地表示执行图8和图9各自所示的流程前的被处理体的状态的图,图10的(b)部分是示意性地表示执行图8和图9各自所示的流程中的被处理体的状态,图10的(c)部分是示意性地表示执行图8和图9的各自中所示的流程后的被处理体的状态的图。

具体实施方式

以下,参照附图对各种实施方式进行详细地说明。其中,在各图中,对相同或者相应的部分标注相同的附图标记。

图1是表示一个实施方式的处理被处理体的方法的流程图。图1所示的方法MT是处理被处理体的方法的一个实施方式。图2是例示作为图1所示的方法MT的适用对象的被处理体(以下称为晶片W)的截面图。图2所示的晶片W具有基片BA、被蚀刻层EL2、被蚀刻层EL1、有机膜OL、防反射膜AL和掩模MK。

被蚀刻层EL2设置在基片BA上。被蚀刻层EL1设置在被蚀刻层EL2上。被蚀刻层EL1和被蚀刻层EL2是含有硅的层,例如非晶硅层或者多晶硅层。有机膜OL是由有机材料构成的膜,设置在被蚀刻层EL1上。防反射膜AL是含Si防反射膜,设置在有机膜OL上。掩模MK设置在防反射膜AL上,并且是在晶片W的主面FW。掩模MK是由有机材料构成的掩模,例如是抗蚀剂掩模。在掩模MK中,提供开口的图案通过光刻而形成。

方法MT(处理被处理体的方法)由具有等离子体处理装置的处理系统执行。图3是表示能够用于图1所述的方法MT的实施的处理系统的一个例子的图。图3所示的处理系统1包括:控制部Cnt、台122a、台122b、台122c、台122d、收纳容器124a、收纳容器124b、收纳容器124c、收纳容器124d、装载组件LM、装载锁定室LL1、装载锁定室LL2、传送室121、等离子体处理装置10。

控制部Cnt包括处理器、存储部、输入装置、显示装置等的计算机,控制处理系统1的后述的各部。控制部Cnt与运送机械臂Rb1、运送机械臂Rb2、光学观察装置OC、等离子体处理装置10等连接,并且在后述的图4所示的等离子体处理装置10中,与阀组42、流量控制器组44、排气装置50、第一高频电源62、匹配器66、第二高频电源64、匹配器68、电源70、加热器电源HP、冷却单元等连接。

控制部Cnt根据在方法MT的各步骤中用于控制处理系统1的各部的计算机程序(基于所输入的方案的程序)工作,输出控制信号。通过来自控制部Cnt的控制信号控制处理系统1的各部、例如运送机械臂Rb1、Rb2、光学观察装置OC和等离子体处理装置10的各部。在图4所示的等离子体处理装置10中,通过来自控制部Cnt的控制信号能够控制从气体源组40供给的气体的选择和流量、排气装置50的排气、来自第一高频电源62和第二高频电源64的电功率供给、来自电源70的电压施加、加热器电源HP的电功率供给、来自冷却单元的致冷剂流量和致冷剂温度。而且,本说明书中所公开的处理被处理体的方法MT的各步骤,通过基于控制部Cnt的控制使处理系统1的各部工作而能够执行。在控制部Cnt的存储部中,用于执行方法MT的计算机程序和方法MT的执行中所使用的各种数据(例如,后述的对应数据DT)以能够读取的方式被保存。

台122a~122d沿着装载组件LM的一边缘排列。在台122a~122d的各自上,分别设置有收纳容器124a~124d。晶片W能够被收纳在收纳容器124a~124d内。

在装载组件LM内设置有运送机械臂Rb1。运送机械臂Rb1将被收纳在收纳容器124a~124d的任一者中的晶片W取出,并将晶片W运送到装载锁定室LL1或者LL2。

装载锁定室LL1和LL2沿着装载组件LM的另一边缘设置,与装载组件LM连接。装载锁定室LL1和LL2构成预备减压室。装载锁定室LL1和LL2分别与传送室121连接。

传送室121是能减压的腔室,在传送室121内设置有运送机械臂Rb2。在传送室121连接有等离子体处理装置10。运送机械臂Rb2从装载锁定室LL1或者装载锁定室LL2取出晶片W,将该晶片W运送到等离子体处理装置10。

处理系统1具有光学观察装置OC。晶片W能够通过运送机械臂Rb1和运送机械臂Rb2在光学观察装置OC与等离子体处理装置10之间移动。通过运送机械臂Rb1将晶片W收纳在光学观察装置OC内,在光学观察装置OC内进行了晶片W的对位之后,光学观察装置OC测定晶片W的掩模(例如掩模MK等)的图案的槽宽度,并将测定结果发送到控制部Cnt。光学观察装置OC能够按主面FW的多个区域ER(后述)的每一区域测定掩模的图案的槽宽度。

图4是表示图3所示的处理系统能够具有的等离子体处理装置的一例的图。在图4中,概略地表示在处理被处理体的方法MT的各种实施方式中能够利用的等离子体处理装置10的截面结构。

如图4所示,等离子体处理装置10是具有平行平板的电极的等离子体蚀刻装置,包括处理容器12。处理容器12具有大致圆筒形状,区划出处理空间Sp。处理容器12例如由铝构成,其内壁面被执行了阳极氧化处理。处理容器12被安全接地。

在处理容器12的底部上,设置有大致圆筒状的支承部14。支承部14例如由绝缘材料构成。构成支承部14的绝缘材料如石英那样能够含有氧。支承部14在处理容器12内从处理容器12的底部沿着铅垂方向延伸。在处理容器12内设置有载置台PD。载置台PD由支承部14支承。

载置台PD在载置台PD的上表面保持晶片W。晶片W的主面FW是与载置台PD的上表面接触的晶片W的背面的相反侧,与上部电极30相对。载置台PD具有下部电极LE和静电吸盘ESC。下部电极LE包括第一板18a和第二板18b。第一板18a和第二板18b例如由铝之类的金属构成,形成大致圆盘形状。第二板18b设置在第一板18a上,与第一板18a电连接。

在第二板18b上设置有静电吸盘ESC。静电吸盘ESC具有将由导电膜构成的电极配置在一对绝缘层之间或者一对绝缘片之间的结构。静电吸盘ESC的电极经由开关23与直流电源22电连接。晶片W载置在载置台PD的情况下与静电吸盘ESC接触。晶片W的背面(主面FW的相反侧的面)与静电吸盘ESC接触。静电吸盘ESC利用由来自直流电源22的直流电压产生的库仑力等的静电功率吸附晶片W。由此,静电吸盘ESC能够保持晶片W。

在第二板18b的周缘部上,以包围晶片W的边缘和静电吸盘ESC的方式配置有聚焦环FR。聚焦环FR是为了提高蚀刻的均匀性而设置的。聚焦环FR由根据蚀刻对象的膜的材料适当选择的材料构成,例如能够由石英构成。

在第二板18b的内部设置有致冷剂流路24。致冷剂流路24构成温度控制机构。从设置在处理容器12的外部的冷却单元(省略图示)经由配管26a对致冷剂流路24供给致冷剂。对致冷剂流路24供给的致冷剂经由配管26b返回到冷却单元。像这样,致冷剂被循环地供给到致冷剂流路24。通过控制该致冷剂的温度,能够控制由静电吸盘ESC支承的晶片W的温度。

在等离子体处理装置10设置有气体供给管路28。气体供给管路28将来自导热气体供给机构的导热气体、例如He气体供给到静电吸盘ESC的上表面与晶片W的背面之间。

在等离子体处理装置10设置有调节晶片W的温度的温度调节部HT。温度调节部HT内置于静电吸盘ESC。在温度调节部HT连接有加热器电源HP。通过从加热器电源HP对温度调节部HT供给电功率,能够调整静电吸盘ESC的温度,从而能够调整载置在静电吸盘ESC上的晶片W的温度。而且,温度调节部HT也能够埋入在第二板18b内。温度调节部HT包括:发热的多个加热元件;和分别检测该多个加热元件各自的周围的温度的多个温度传感器。多个加热元件的各自,在晶片W与静电吸盘ESC对位而载置在该静电吸盘ESC上的情况下,按晶片W的主面FW的多个区域ER(后述)的每一区域而设置。控制部Cnt在晶片W与静电吸盘ESC对位而载置在该静电吸盘ESC上的情况下,将与晶片W的主面FW的多个区域ER的各个区域对应的加热元件以及温度传感器和区域ER相关联地进行识别。控制部Cnt能够按多个区域的每一区域(多个区域ER的每一区域)将区域ER和与该区域ER对应的加热元件以及温度传感器根据例如数字或者文字等的序号等来识别。控制部Cnt通过在与该一个区域ER对应的部位所设置的温度传感器检测一个区域ER的温度,利用在与该一个区域ER对应的部位所设置的加热元件进行对该一个区域ER的温度调节。其中,在晶片W载置在静电吸盘ESC上的情况下,由一个温度传感器检测的温度与晶片W中该温度传感器上的区域ER的温度(更具体而言,后述的被处理层J1中的区域ER的温度)相同。

等离子体处理装置10具有上部电极30。上部电极30在载置台PD的上方与载置台PD相对配置。下部电极LE与上部电极30彼此大致平行地设置,构成平行平板电极。在上部电极30与下部电极LE之间,提供用于对晶片W进行等离子体处理的处理空间Sp。

上部电极30经由绝缘性屏蔽部件32被支承在处理容器12的上部。绝缘性屏蔽部件32由绝缘材料构成,例如如石英那样能够含有氧。上部电极30能够包括电极板34和电极支承体36。电极板34面向处理空间Sp,在电极板34设置有多个气体排出孔34a。电极板34在一个实施方式中含有硅。在另一实施方式中,电极板34能够含有氧化硅。

电极支承体36将电极板34以能够装卸的方式支承,例如能够由铝之类的导电性材料构成。电极支承体36能够具有水冷构造。在电极支承体36的内部设置有气体扩散室36a。与气体排出孔34连通的多个气体流通孔36b从气体扩散室36a向下方延伸。在电极支承体36形成有对气体扩散室36a导入处理气体的气体导入口36c,在气体导入口36c连接有气体供给管38。

气体供给管38经由阀组42和流量控制器组44与气体源组40连接。气体源组40具有多个气体源。多个气体源可以包括:含有机基团的氨基硅烷类气体源、碳氟化合物类气体源(C

阀组42包括多个阀,流量控制器组44包括质量流量控制器之类的多个流量控制器。气体源组40的多个气体源各自经由阀组42的对应的阀和流量控制器组44的对应的流量控制器与气体供给管38连接。因此,等离子体处理装置10能够将来自选自气体源组40的多个气体源中的一个以上的气体源的气体以独立地调整了的流量供给到处理容器12内。

在等离子体处理装置10中,沉积防护件46沿着处理容器12的内壁以能够装卸的方式设置。沉积防护件46也设置在支承部14的外周。沉积防护件46是防止蚀刻副产物(沉积物)附着于处理容器12的部件,能够通过在铝材覆盖Y

在处理容器12的底部侧、且在支承部14与处理容器12的侧壁之间设置有排气板48。排气板48例如通过在铝材覆盖Y

等离子体处理装置10还具有第一高频电源62和第二高频电源64。第一高频电源62是产生等离子体生成用的第一高频电功率的电源,产生27~100[MHz]的频率,在一个例子中产生60[MHz]的高频电功率。另外,第一高频电源62具有脉冲规格,能够按频率5~10[kHz]、占空比50~100%进行控制。第一高频电源62经由匹配器66与上部电极30连接。匹配器66是用于使第一高频电源62的输出阻抗与负载侧(下部电极LE侧)的输入阻抗匹配的电路。而且,第一高频电源62可以经由匹配器66与下部电极LE连接。

第二高频电源64是产生用于将离子引入到晶片W的第二高频电功率、即高频偏置电功率的电源,产生400[kHz]~40.68[MHz]的范围内的频率,在一个例子中产生13.56[MHz]的频率的高频偏置电功率。另外,第二高频电源64具有脉冲规格,能够按频率5~40[kHz]、Duty20~100%进行控制。第二高频电源64经由匹配器68与下部电极LE连接。匹配器68是用于使第二高频电源64的输出阻抗与负载侧(下部电极LE側)的输入阻抗匹配的电路。

等离子体处理装置10还具有电源70。电源70与上部电极30连接。电源70对上部电极30施加用于将存在于处理空间Sp内的正离子引入到电极板34的电压。在一个例子中,电源70是产生负的直流电压的直流电源。这样的电压从电源70施加到上部电极30时,存在于处理空间Sp中的正离子与电极板34碰撞。由此,从电极板34释放二次电子和/或者硅。

以下,参照图1、图5、图8、图9以具有等离子体处理装置10的处理系统1中实施的方式为例,详细说明方法MT。其中,方法MT也能够在与处理系统1不同的处理系统中实施,这样的处理系统能够具有等离子体处理装置10以外的等离子体处理装置。

首先,图1所示的方法MT包括步骤SA1~SA4。步骤SA1包括使用图2所示的掩模MK蚀刻防反射膜AL的步骤SA11(第二步骤)。接着步骤SA1的步骤SA2包括使用通过在步骤SA11中进行的蚀刻由防反射膜AL形成的掩模来蚀刻有机膜OL的步骤SA21(第二步骤)。接着步骤SA2的步骤SA3包括:使用通过在步骤SA21中进行的蚀刻由有机膜OL形成的掩模来蚀刻被蚀刻层EL1的步骤SA31;和在步骤SA31之后,对由有机膜OL形成的掩模进行灰化而除去的步骤SA32。接着步骤SA3的步骤SA4,包括使用通过在步骤SA31中进行的蚀刻由被蚀刻层EL1形成的掩模来蚀刻被蚀刻层EL2的步骤SA41。

在步骤SA11中,蚀刻防反射膜AL。具体而言,从选自气体源组40的多个气体源中的气体源,将包含碳氟化合物气体的处理气体供给到处理容器12内。并且,从第一高频电源62供给高频电功率。从第二高频电源64供给高频偏置电功率。通过使排气装置50工作,将处理容器12内的压力设定为规定的压力。如以上所述,在处理容器12的处理空间Sp内生成碳氟化合物气体的等离子体。所生成的等离子体中的含氟的活性种对防反射膜AL的整个区域中从掩模MK露出的区域进行蚀刻。通过该防反射膜AL的蚀刻,由防反射膜AL形成在对有机膜OL的蚀刻中使用的掩模。

在步骤SA21中蚀刻有机膜OL。具体而言,从选自气体源组40的多个气体源中的气体源,将含有氮气和氢气的处理气体供给到处理容器12内。并且,从第一高频电源62供给高频电功率。从第二高频电源64供给高频偏置电功率。通过使排气装置50工作,将处理容器12内的压力设定为规定的压力。如以上所述那样,在处理容器12的处理空间Sp内生成含有氮气和氢气的处理气体的等离子体。所生成的等离子体中的氢的活性种即氢自由基,对有机膜OL的整个区域中的、从在步骤SA11由防反射膜AL形成的掩模露出的区域进行蚀刻。通过该有机膜OL的蚀刻,由有机膜OL形成在对被蚀刻层EL1的蚀刻中使用的掩模。其中,作为蚀刻有机膜OL的气体,可以使用含氧的处理气体。

在接着步骤SA2的步骤SA3的步骤SA31中,蚀刻被蚀刻层EL1。具体而言,从选自气体源组40的多个气体源中的气体源,将处理气体供给到处理容器12内。处理气体能够给根据构成被蚀刻层EL1的材料适当选择。例如,在被蚀刻层EL1由氧化硅构成的情况下,处理气体可以包含碳氟化合物气体。并且,从第一高频电源62供给高频电功率。从第二高频电源64供给高频偏置电功率。通过使排气装置50工作,将处理容器12内的压力设定为所定的压力。由此,生成等离子体。所生成的等离子体中的活性种,对被蚀刻层EL1的整个区域中的、从通过在步骤SA21进行的蚀刻由有机膜OL形成的掩模露出的区域进行蚀刻。在步骤SA31之后,在步骤SA32中,将由有机膜OL在步骤SA21中所形成的掩模灰化。具体而言,从选自气体源组40的多个气体源中的气体源将处理气体供给到处理容器12内。处理气体可以包含氧气和氧原子。并且,从第一高频电源62供给高频电功率。从第二高频电源64供给高频偏置电功率。通过使排气装置50工作,将处理容器12内的压力设定为规定的压力。由此,生成等离子体。所生成的等离子体中的活性种,将由有机膜OL在步骤SA21所形成的掩模灰化。其中,作为将由有机膜OL在步骤SA21所形成的掩模灰化的气体,能够使用含有氮气和氢气的处理气体。

在接着步骤SA3的步骤SA4的步骤SA41中,蚀刻被蚀刻层EL2。具体而言,从选自气体源组40的多个气体源中的气体源,将处理气体供给到处理容器12内。处理气体能够根据构成被蚀刻层EL2的材料适当选择。例如,在被蚀刻层EL2由非晶硅构成的情况下,处理气体能够含有卤素类的气体。并且,从第一高频电源62供给高频电功率。从第二高频电源64供给高频偏置电功率。通过使排气装置50工作,将处理容器12内的压力设定为所定的压力。由此,生成等离子体。所生成的等离子体中的活性种,对被蚀刻层EL2的整个区域中的、从通过在步骤SA31、SA32中进行的蚀刻和灰化而由被蚀刻层EL1形成的掩模露出的区域进行蚀刻。

步骤SA1、步骤SA2、步骤SA3和步骤SA4能够包括进行蚀刻前的图案的槽宽度的调节处理的步骤SAA(第一步骤)。在步骤SAA中,在蚀刻前,调节在蚀刻中使用的掩模的图案的槽宽度。步骤SAA在步骤SA1中进行的情况下,在步骤SA11之前进行。步骤SAA在步骤SA2中进行的情况下,在步骤SA21之前进行。步骤SAA在步骤SA3中进行的情况下,在步骤SA31之前进行。步骤SAA在步骤SA4中进行的情况下,在步骤SA41之前进行。

图6的(a)部分表示作为步骤SAA的处理对象(即,后述的图5所示的步骤的处理对象)的晶片W的状态。图6的(a)部分是表示图5所示的步骤(步骤SAA)的实施前的晶片W的状态的截面图。图6的(a)部分表示的晶片W包括被处理层J1和掩模J2。掩模J2设置在被处理层J1的主面J11(在掩模J2与掩模MK对应的情况下,主面J11与晶片W的主面FW对应)。

在蚀刻防反射膜AL的步骤SA1中执行图1所示的步骤SAA的情况下,被处理层J1为防反射膜AL,掩模J2为掩模MK。步骤SA11在步骤SAA的执行之后使用进行了槽宽度的调节处理的掩模来蚀刻被处理层J1。

在图1所示的步骤SAA在蚀刻有机膜OL的步骤SA2中被执行的情况下,被处理层J1为有机膜OL,掩模J2为通过在步骤SA11中进行的蚀刻而由防反射膜AL形成的掩模。步骤SA21在步骤SAA的执行之后,使用被进行了槽宽度的调节处理的掩模来蚀刻被处理层J1。

在蚀刻被蚀刻层EL1的步骤SA3中执行图1所示的步骤SAA的情况下,被处理层J1为被蚀刻层EL1,掩模J2为通过在步骤SA21中进行的蚀刻而由有机膜OL形成的掩模。步骤SA31在步骤SAA的执行之后,使用被进行了槽宽度的调节处理的掩模来蚀刻被处理层J1。

在蚀刻被蚀刻层EL2的步骤SA4中执行图1所示的步骤SAA的情况下,被处理层J1为被蚀刻层EL2,掩模J2是通过在步骤SA31、SA32中进行的蚀刻和灰化而由被蚀刻层EL1形成的掩模。步骤SA41在步骤SAA的执行之后,使用进行了槽宽度的调节处理的掩模蚀刻被处理层J1。

接着,参照图5,详细说明图1所示的步骤SAA的详细内容。图5是表示能够包含在图1所示的方法中的步骤(步骤SAA)、即蚀刻前的图案的槽宽度的调节处理的步骤的一例的流程图。

在步骤SAA中(在控制部Cnt进行的处理中),晶片W的被处理层J1的主面J11被划分为多个区域(区域ER)。图7是将一个实施方式的方法MT中被划分的晶片W的被处理层J1的主面J11的多个区域ER的一部分作为一例示意性地表示的图。多个区域ER彼此不重叠。多个区域ER覆盖被处理层J1的主面J11(晶片W的主面FW)。区域ER的形状例如能够是相对于被处理层J1的主面J11的中心点(主面FW的中心点)同心圆地延展的区域或者格子状的区域等,但并不限定于此。

如图5所示,步骤SAA包括步骤SB1~SB7,步骤SB5~SB7根据步骤SB3和步骤SB4的判断结果,能够完成多次(反复)的执行。首先,在步骤SB1(第三步骤)中,通过处理系统1的光学观察装置OC按被处理层J1的主面J11的多个区域ER的每一区域测定掩模J2的图案的槽宽度的值。

在接着步骤SB1的步骤SB2(第四步骤)中,按被处理层J1的主面J11的多个区域ER的每一区域,计算从由步骤SB1测定得到的掩模J2的图案的槽宽度的值减去该槽宽度的基准值而得到的正的差值。

在接着步骤SB2的步骤SB3中,判断图案的槽宽度的调节是否已经进行过一次(图案的槽宽度的调节已经进行了一次的情况,是指图案的槽宽度的调节通过后述的步骤SB5~SB7已经进行过至少一次的情况),图案的槽宽度的调节一次还未进行的情况下(图案的槽宽度的调节初次进行的情况)(步骤SB3:否),移动到步骤SB5。在步骤SB3中,图案的槽宽度的调节已经进行了一次的情况下(步骤SB3:是),移动到步骤SB4。

在步骤SB4中,基于在步骤SB2中计算出的图案的槽宽度的差值,判断是否需要图案的槽宽度的再次调节。在步骤SB4中,需要图案的槽宽度的再次调节的情况下(步骤SB4:是),再次执行步骤SB5~SB7。即,在执行步骤SB5~SB7之后再次执行步骤SB1和步骤SB2,通过该再次执行,当在步骤SB2计算出的差值没有满足预先设定的基准范围的情况下(步骤SB4:是),再次执行步骤SB5~SB7。该基准范围是包含在步骤SB2中使用的槽宽度的基准值的范围。在步骤SB4中,不需要图案的槽宽度的再次调节的情况下(步骤SB4:否)、即,在步骤SB2中计算出的差值满足了预先设定的基准范围的情况下,结束步骤SAA的处理。

在接着步骤SB3:“是”以及步骤SB4:“是”的步骤SB5中,晶片W通过运送机械臂Rb1和运送机械臂Rb2被从光学观察装置OC移动到等离子体处理装置10,晶片W被送入等离子体处理装置10的处理容器12内。

在接着步骤SB5的步骤SB6(第五步骤)中,在被送入到处理容器12内的晶片W的掩模J2的表面J21,形成在步骤SB2中计算出的多个区域ER的每一区域的差值的膜厚的膜J3(多个区域ER的每一区域的膜厚成为在步骤SB2按多个区域ER的每一区域计算出的差值的膜)。膜J3为氧化硅的膜。图6的(b)部分是表示图5所示的步骤(步骤SB6)的实施后的晶片W的状态的截面图。在图6的(b)部分所示的晶片W中,在掩模J2的表面J21形成有膜J3。其中,在步骤SB6中进行的处理内容的详情在后文中说明。

在接着步骤SB6的步骤SB7中,晶片W通过运送机械臂Rb1和运送机械臂Rb2被从等离子体处理装置10移动到光学观察装置OC,晶片W被送入到光学观察装置OC内。在步骤SB7之后,再次执行步骤SB1、步骤SB2和步骤SB3。

参照图8和图9,说明步骤SB6的详细内容。图8是表示图5所示的步骤的一部分步骤(步骤SB6)、即调节图案的槽宽度的步骤的一例的流程图。图9是图8所示的步骤中能够包含的步骤(步骤SCC),是表示在被处理层J1的主面J11形成均匀的膜的步骤的一例的流程图。

如图8所示,步骤SB6包括步骤SC1~SC9。步骤SC5~SC8构成流程SQ1。流程SQ1和步骤SC9是在晶片W的掩模J2的表面J21形成膜J3的膜形成处理。步骤SC1~SC4是为了执行由流程SQ1和步骤SC9构成的膜形成处理的必要的准备处理。

在步骤SC1中,被送入到等离子体处理装置10的处理容器12内的晶片W与静电吸盘ESC相对位地被载置在静电吸盘ESC上。接着步骤SC1的步骤SC2中,与步骤SB3同样地判断是否已经进行了一次图案的槽宽度的调节(已经进行了一次图案的槽宽度的调节的情况,是指图案的槽宽度的调节在后述的步骤SB5~SB7中已经至少进行了一次的情况),在图案的槽宽度的调节一次还未进行的情况下(图案的槽宽度的调节初次进行的情况)(步骤SC2:否),移动到步骤SC3。其中,步骤SC2的判断结果与图5所示的步骤SB3的判断结果对应。另外,步骤SC3,在包含该步骤SC3的步骤SAA在蚀刻有机膜的步骤SA2中进行的情况下(在步骤SA1之后且在步骤SA21之前进行的情况下),有时不被执行。

在步骤SC2中,在已经进行了一次图案的槽宽度的调节的情况下(步骤SC2:是),移动到步骤SC4或者步骤SCC(第十二步骤)。其中,步骤SC2的判断结果与步骤SB3的判断结果相同,所以步骤SC2的判断的处理能够通过参照步骤SB3的判断结果来完成。

在步骤SCC中,不依赖于多个区域ER地对掩模J2的表面J21保形地形成膜。关于步骤SCC的详细内容参照图9在后文说明。此外,如图8所示,步骤SB6可以是不包括步骤SCC的构成,在包括步骤SCC的情况下,可以是当步骤SC3或者步骤SC2为:“否”时,在与步骤SC4之间(即,步骤SC4之前)或者后述的步骤SC9为:“是”之后(即、膜形成处理之后),能够执行步骤SCC的构成。

在接着步骤SC2为:“是”的步骤SC3中,对晶片W照射二次电子。步骤SC3是,在执行对掩模J2的表面J21形成膜J3的流程SQ1和步骤SC9之前,使处理容器12的处理空间Sp内产生等离子体,对上部电极30施加负的直流电压,由此对掩模J2照射二次电子的步骤。

如上所述,因为在执行对掩模J2的表面J21形成膜J3的流程SQ1~步骤SC9的一系列的步骤之前,对掩模J2照射次电子,所以在膜J3的形成前能够将掩模J2改性,能够抑制由后述的步骤导致的对掩模J2的损伤。

对步骤SC3的处理内容进行具体的说明。首先,向处理容器12内供给氢气体和稀有气体,从第一高频电源62供给高频电功率,由此在处理空间Sp内能够生成等离子体。从选自气体源组40的多个气体源中的气体源向处理容器12内供给氢气和稀有气体。因此,处理空间Sp中的正离子被引入到上部电极30,该正离子与上部电极30碰撞。通过正离子与上部电极30碰撞,从上部电极30释放出二次电子。通过被释放出的二次电子照射晶片W,掩模J2被改性。并且,通过正离子碰撞电极板34,作为电极板34的构成材料的硅与二次电子一同被释放。所释放出的硅,与被暴露在等离子体中的等离子体处理装置10的构成部件所释放出的氧结合。该氧例如从支承部14、绝缘性屏蔽部件32和沉积防护件46之类的部件释放出来。通过硅与氧的结合,生成氧化硅化合物,该氧化硅化合物沉积在晶片W上覆盖掩模J2来保护该掩模J2。像这样,在对掩模J2照射二次电子的步骤SC3中,在处理空间Sp内使等离子体产生对上部电极30施加负的直流电压,由此对掩模J2照射二次电子,并且使从电极板34释放硅,用含该硅的氧化硅化合物覆盖掩模J2。并且,对掩模J2照射二次电子,并用氧化硅化合物覆盖掩模J2之后对处理容器12内进行吹扫,移动到步骤SC4或者步骤SCC。如以上所述,在步骤SC3中,氧化硅化合物覆盖掩模J2的情况下,能够进一步抑制后述的步骤导致的对掩模J2的损伤。

此外,在步骤SC3中,为了基于二次电子的照射进行的改性和保护膜的形成,可以使第二高频电源64的偏置电功率为最小限度抑制硅的释放。另外,在方法MT中能够除去步骤SC3。

在步骤SC3之后,或者在步骤SC2为:“否”之后,经过步骤SCC或者不经过步骤SCC,移动到步骤SC4(第十步骤)。在步骤SC4中,按晶片W的被处理层J1的主面J11的多个区域ER的每一区域,利用温度调节部HT调节晶片W的被处理层J1的温度。在步骤SC4中,利用预先取得的对应数据DT和与在步骤SB2中按多个区域ER的每一区域计算出的差值对应的膜厚,调节多个区域ER的每一区域中被处理层J1的温度,其中,对应数据DT表示被处理层J1的温度与在被处理层J1上的掩模J2的表面J21沉积的膜(后述的膜形成处理(流程SQ1和步骤SC9)中形成的膜)的膜厚的对应。对应数据DT是通过按被处理层J1的每一温度基于与由流程SQ1和步骤SC9构成的膜形成处理相同的条件(被处理层J1的除了温度以外的条件)在掩模J2的表面J21沉积膜J3而预先取得的数据,该数据以能够读取的方式保存在控制部Cnt的存储部中。

在步骤SC4中,步骤SB6不包含步骤SCC的情况下,基于对应数据DT按多个区域ER的每一区域调节被处理层J1的温度,以使得被送入到处理容器12内的晶片W的被处理层J1中的多个区域ER的每一区域的温度成为与在步骤SB2中按多个区域ER的每一区域计算出的差值的膜厚对应的温度。

在步骤SC4中,在步骤SB6包含步骤的情况下,即步骤SCC在步骤SC4之前且在步骤SC3之后或步骤SC2为:“否”之后被执行的情况下,或者在由步骤SQ1和步骤SC9构成的膜形成处理之后被执行的情况下,基于对应数据DT按多个区域ER的每一区域调节被处理层J1的温度,以使得被送入到处理容器12内的晶片W的被处理层J1中的多个区域ER的每一区域的温度,成为与从在步骤SB2中按多个区域ER的每一区域计算出的差值的膜厚减去在步骤SCC中保形地形成的膜的膜厚的值对应的温度。

由接着步骤SC4的流程SQ1和步骤SC9构成的膜形成处理(第11步骤)中,在被送入到处理容器12内的晶片W的被处理层J1上的掩模J2的表面J21形成膜(膜J3、或者在步骤SB6中执行步骤SCC的情况下膜J3的一部分)。由流程SQ1和步骤SC9构成的膜形成处理是通过与ALD(Atomic Layer Deposition)法同样的方法在晶片W的掩模J2的表面J21上按多个区域ER的每一区域以均匀的厚度保形地形成氧化硅的膜的步骤。在执行流程SQ1的步骤SC5中,维持在步骤SC4中按多个区域ER的每一区域所调节的晶片W的被处理层J1的温度。因此,通过膜形成处理形成的膜的膜厚在多个区域ER的每一区域成为不同的膜厚,包括通过膜形成处理形成的膜在内的膜J3形成在掩模J2的表面J21之后(步骤SB4:否),且在步骤SAA之后,掩模J2的槽宽度成为所希望的值(在步骤SB2中用于差值的计算的多个区域ER的每一区域的槽宽度的基准值)。

说明膜形成处理(流程SQ1和步骤SC9)的详细内容。流程SQ1包括步骤SC5~SC8。在步骤SC5(第六步骤)中,向处理容器12内供给第一气体G1。具体而言,在步骤SC5中,如图10的(a)部分所示,向处理容器12内导入含硅的第一气体G1。第一气体G1包含含有机基团的氨基硅烷类气体。第一气体G1作为氨基硅烷类气体能够使用氨基的数量比较少的分子构造的气体,例如单氨基硅烷(H

在步骤SC5所需要的处理时间,在步骤SC5中沉积在被处理层J1上的掩模J2的表面J21的膜的膜厚成为根据被处理层J1的温度的高低而增减的状态的时间内。这样的处理时间可以说是比ALD法中的成为自限性(self-limited)区域(不依赖于被处理层J1的温度的膜厚的膜能够形成在被处理层J1上的掩模J2的表面J21的处理时间)的处理时间短的时间。

第一气体G1的分子如图10的(b)部分所示,作为反应前体(层Ly1)附着在被处理层J1的主面J11(具体而言,主面J11上的掩模J2的表面J21)。第一气体G1的分子通过基于化学键合的化学吸附附着在掩模J2的表面J21,不能利用等离子体。此外,作为第一气体G1,在步骤SC4中基于按多个区域ER的每一区域所调节的被处理层J1的温度通过化学键合能够附着在掩模J2的表面J21,且只要是含有硅的气体就能够利用。

另一方面,例如对于第一气体G1选择单氨基硅烷的情况下,作为选择单氨基硅烷的理由,原因是单氨基硅烷具有比较高的电负性并且具备具有极性的分子构造,因此化学吸附能够比较容易进行。通过第一气体G1的分子附着在掩模J2的表面J21形成的反应前体的层Ly1,由于该附着是化学吸附而成为接近但分子层(单层)的状态。单氨基硅烷的氨基(R)越小,吸附在掩模J2的表面J21的分子的分子构造也越小,因此能够降低因分子的大小造成的立体障碍,由此,第一气体G1的分子能够在掩模J2的表面J21按多个区域ER的每一区域均匀地吸附,层Ly1对于掩模J2的表面J21能够按多个区域ER的每一区域以均匀的膜厚形成。

如上所述,因为第一气体G1包含含有机基团的氨基硅烷类气体,所以通过步骤SC5,硅的反应前体(层Ly1)沿着掩模J2的表面J21的原子层形成在掩模J2上。

在接着步骤SC5的步骤SC6(第七步骤)中,对处理容器12内进行吹扫。具体而言,在步骤SC5中所供给的第一气体G1被排气。在步骤SC6中,作为吹扫气体可以将氮气或者稀有气体(例如Ar等)之类的不活泼气体供给到处理容器12内。即,步骤SC6的吹扫可以是使不活泼气体在处理容器12内流通的气体吹扫、或者基于抽真空进行的吹扫的任意者。在步骤SC6中,也能够除去在掩模J2的表面J21上过度附着的分子。通过以上内容,反应前体的层Ly1成为极薄的单分子层。

在接着步骤SC6的步骤SC7(第八步骤)中,如图10的(b)部分所示,在处理容器12的处理空间Sp内生成第二气体的等离子体P1。第二气体能够包含含有氧原子和碳原子的气体,例如包含二氧化碳气体。在步骤SC7中,生成第二气体的等离子体P1时的晶片W的被处理层J1的温度可以是例如摄氏0度以上且摄氏200度以下。从选自气体源组40的多个气体源中的气体源向处理容器12内供给包含含有氧原子和碳原子的气体的第二气体。并且,从第一高频电源62供给高频电功率。这时,也能够施加第二高频电源64的偏置电功率,另外,也能够仅用第二高频电源64生成等离子体。从第二高频电源64供给高频偏置电功率,使排气装置50工作,由此将处理容器12内的空间的压力设定为预先设定的压力。如此一来,在处理空间Sp内生成第二气体的等离子体P1。

如图10的(b)部分所示,当生成第二气体的等离子体P1时,能够生成氧的活性种和碳的活性种、例如氧自由基、碳自由基,如图10的(c)部分所示,由氧化硅膜形成的层Ly2(在膜J3中包含的层)作为单分子层形成。碳自由基能够起到抑制对掩模J2的氧侵蚀的功能,所以氧化硅膜作为保护膜能够在掩模J2的表面J21稳定地形成。氧化硅膜的Si-O键的键能为192[kcal]程度,形成掩模的有机膜的各种各样的键种即C-C键、C-H键、C-F键各自的键能(50-110[kcal]程度、70-110[kcal]程度、100-120[kcal]程度)更高,因此氧化硅膜能够作为保护膜发挥作用。

如以上所述,因为第二气体含有氧原子,所以在步骤SC7中,该氧原子与设置在掩模J2上的硅的反应前体(层Ly1)键合,由此在掩模J2上氧化硅膜的层Ly2能够按多个区域ER的每一区域以不同的膜厚保形地形成。另外,因为第二气体包含碳原子,由氧原子导致的对掩模J2的侵蚀能够被该碳原子抑制。因此,在流程SQ1中,通过与ALD法同样的方法,能够将氧化硅膜的层Ly2在掩模J2的表面J21上以与多个区域ER的各自的温度相应的均匀的膜厚在多个区域ER的每一区域中保形地形成。

在接着步骤SC7的步骤SC8(第九步骤)中,对处理容器12内进行吹扫。具体而言,在步骤SC7中所供给的第二气体被排气。在步骤SC8中,作为吹扫气体可以将氮气或者稀有气体(例如Ar等)之类的不活泼气体供给到处理容器12内。即,步骤SC8的吹扫,可以是使不活泼气体在处理容器12内流通的气体吹扫、或者是基于抽真空进行的吹扫的任意者。

在接着流程SQ1的步骤SC9中,判断流程SQ1的反复次数是否达到了预先设定的次数(例如50次等),当判断为没有达到该次数时(步骤SC9:否),再次执行流程SQ1,当判断为已达到了该次数时(步骤SC9:是),结束步骤SB6。即,在步骤SC9中,直至流程SQ1的反复次数达到了预先设定的次数为止,反复执行流程SQ1,对掩模J2的表面J21按多个区域ER的每一区域形成与多个区域ER的各自的温度对应的膜厚的膜。通过步骤SC9控制的流程SQ1的反复次数根据在步骤SC5的处理时间和通过由流程SQ1和步骤SC9构成的膜形成处理形成的膜(膜J3或者在步骤SB6中执行步骤SCC的情况下膜J3的一部分)的膜厚而决定。

在此,参照图9说明步骤SCC的详细内容。步骤SCC由流程SQ2和步骤SD5构成。流程SQ2由步骤SD1~SD4构成。流程SQ2的步骤SD1与图8所示的流程SQ1的步骤SC5对应,步骤SD1与步骤SC5的不同点在于:步骤SD1中的被处理层J1的温度与步骤SC5中的被处理层J1的温度不同;和在步骤SD1需要的处理时间与在步骤SC5需要的处理时间不同。流程SQ2的步骤SD2~SD4的各步骤与图8所示的流程SQ1的步骤SC6~SC8的各步骤进行相同的处理。

由步骤SD5控制的流程SQ2的反复次数,根据由步骤SCC形成的膜(膜J3的一部分)的膜厚决定。在步骤SB6形成的膜J3由在步骤SCC形成的膜和在膜形成处理(流程SQ1和步骤SC9)形成的膜构成。在步骤SB6形成的膜J3的膜厚是在步骤SCC形成的膜的膜厚与在膜形成处理(流程SQ1和步骤SC9)形成的膜的膜厚的合计值。

在流程SQ2的步骤SD1的处理时间,成为ALD法中的成为自限性(self-limited)区域(与被处理层J1的温度无关的膜厚能够形成在被处理层J1上的掩模J2的表面J21的处理时间)的处理时间,比流程SQ1的步骤SC5的处理时间长。在步骤SD1中,晶片W的处理层J1的温度能够是例如摄氏0度以上且摄氏200度以下。

对于一个实施方式的对应数据DT的制作方法的具体例进行说明。对应数据DT是表示被处理层J1的温度与在被处理层J1上的掩模J2的表面J21沉积的膜(由膜形成处理(流程SQ1和步骤SC9)形成的膜)的膜厚的对应的数据,并且是按被处理层J1的每一温度基于与由流程SQ1和步骤SC9构成的膜形成处理相同的条件(除了被处理层J1的温度之外的条件)使膜J3沉积在掩模J2的表面J21,由此能够在方法MT的执行前预先得到的数据。

首先,按被处理层J1的多个温度(以下将该温度的值称为KR)的每一温度,测定在步骤SC5的处理时间(以下将该处理时间的值称为TM)与在膜形成处理形成的膜的膜厚(以下将该膜厚的值称为VL)的关系(以下将该关系作为处理时间(TM)和温度(KR)的函数,称为F1)。按每一温度(KR),处理时间(TM)与膜厚(VL)的关系(VL=F1(TM;KR))能够以对数函数:VL=α1(KR)×ln(TM)+β1(KR)…(式1)良好地近似。α1(KR)是按每一KR决定的常数,ln(TM)是相对TM的自然对数,β1(KR)是按每一KR决定的常数。在式1(近似式)中,在膜形成处理形成的膜的膜厚(VL),根据相对温度(KR)的阿累尼乌斯方程式(阿累尼乌斯曲线图)可知,温度(KR)越高变得越大,在ALD法中的自己控制区域中,不依赖于KR收敛于大致一定的值。

式1中包含的α1(KR)和β1(KR)能够如以下所示近似。α1(KR)的倒数(1/α1(KR))能够用一次函数:1/α1(KR)=α2×KR+β2…(式2)良好地近似。α2、β2是式2(近似式)的计算时决定的常数。β1(KR)作为KR的函数,能够用对数函数:β1(KR)=α3×ln(KR)+β3…(式3)良好地近似。α3、β3是式3(近似式)的计算时决定的常数。ln(KR)是相对KR的自然对数。

对式1中包含的α1(KR)和β1(KR)的各自,分别适用式2和式3,由此,式1表示为VL=ln(TM)/(α2×KR+β2)+α3×ln(KR)+β3…(式4)。即,膜厚(VL)是如果将处理时间(TM)固定为一定的值(ALD法中的与自己控制区域对应的处理时间段的步骤SC需要的处理时间,膜厚(VL)根据温度(KR)能够充分地变化的处理时间),能够根据温度(KR)唯一计算出的。如以上所说明,对应数据DT通过式4能够制作。此外,用上述式1~式4的方法以外的方法也能够制作对应数据DT。

在以上所说明的一个实施方式的方法MT中,在蚀刻被处理层J1的步骤SA11(或者步骤SA21、步骤SA31、步骤SA41)之前,执行调节掩模J2的图案的槽宽度的步骤SAA。在步骤SAA中,将被处理层J1的主面J11划分为多个区域ER,在步骤SB1和步骤SB2中按多个区域ER的每一区域计算掩模J2的槽宽度与该槽宽度的基准值的差值,在步骤SB6中在掩模J2形成与该差值对应的膜厚的膜J3,按多个区域ER的每一区域将掩模的槽宽度修正为该基准值。在步骤SB6中,利用反复执行步骤SC5~SC8的膜形成处理通过与ALD法同样的方法在掩模J2将膜按每一原子层高精细地形成。在膜形成处理中形成的膜的膜厚根据被处理层J1的温度而不同,所以在步骤SC4中,利用表示被处理层J1的温度与要形成的膜的膜厚的对应的对应数据DT,按多个区域ER的每一区域,调节被处理层J1的温度,以成为与在步骤SB2计算出的差值对应的膜厚的膜的形成所需要的温度。像这样,在步骤SA11(或者步骤SA21、步骤SA31、步骤SA41)进行的蚀刻之前,按被处理层J1的主面J11的多个区域ER的每一区域,决定与掩模J2的槽的修正量对应的膜厚,利用对应数据DT决定该膜厚的形成需要的被处理层J1的温度,以按多个区域ER的每一区域所决定的温度调节了被处理层J1的温度的状态下,进行与ALD法同样的膜形成处理,所以掩模J2的图案的不均能够按被处理层J1的主面J11的多个区域ER的每一区域精细且充分地得以抑制。

另外,不依赖于多个区域ER对掩模J2的表面J21保形地形成膜的步骤SCC用于方法MT的情况下,关于多个区域ER的每一区域的膜厚中共同的膜厚,能够不经由在步骤SC4按多个区域ER的每一区域进行的被处理层J1的温度的调节,而通过步骤SCC局部地进行膜的形成。

另外,在步骤SB6进行了膜J3的形成之后,在此计算掩模J2的槽宽度的差值,判断差值是否在基准范围中(步骤SB1~SB4),当差值不在基准范围时,再次进行膜J3的形成,因此掩模J2的槽宽度的不均匀能够进一步被充分地抑制。

以上,在适当的实施方式中图示了本发明的原理并进行了说明,本发明只要不脱离这样的原理,其配置和详细内容能够进行改变,这一点作为本领域技术人员是能够知晓的。本发明并不限于本实施方式中所公开的特定的结构。因此,对于根据权利要求的范围及其精神的范围得到的全部的修正和变更请求权利。

附图标记说明

1…处理系统;10…等离子体处理装置;12…处理容器;121…传送室;122a…台;122b…台;122c…台;122d…台;124a…收纳容器;124b…收纳容器;124c…收纳容器;124d…收纳容器;12e…排气口;12g…运入运出口;14…支承部;18a…第一板;18b…第二板;22…直流电源;23…开关;24…致冷剂流路;26a…配管;26b…配管;28…气体供给管路;30…上部电极;32…绝缘性屏蔽部件;34…电极板;34a…气体排出孔;36…电极支承体;36a…气体扩散室;36b…气体流通孔;36c…气体导入口;38…气体供给管;40…气体源组;42…阀组;44…流量控制器组;46…沉积防护件;48…排气板;50…排气装置;52…排气管;54…闸阀;62…第一高频电源;64…第二高频电源;66…匹配器;68…匹配器;70…电源;AL…防反射膜;Cnt…控制部;DT…对应数据;EL1…被蚀刻层;EL2…被蚀刻层;ER…区域;ESC…静电吸盘;FR…聚焦环;FW…主面;G1…第一气体;HP…加热器电源;HT…温度调节部;J1…被处理层;J11…主面;J2…掩模;J21…表面;J3…膜;LE…下部电极;LL1…装载锁定室;LL2…装载锁定室;LM…装载组件;Ly1…层;Ly2…层;MK…掩模;OC…光学观察装置;OL…有机膜;P1…等离子体;PD…载置台;Rb1…运送机械臂;Rb2…运送机械臂;BA…基片;Sp…处理空间;W…晶片。

- 基片处理装置、基片处理方法和存储介质

- 基片处理装置、基片处理方法和存储介质

- 基片处理装置和基片处理装置的运用方法

- 基片位置调整方法、存储介质和基片处理系统

- 具有制冷剂用的流路的部件及其控制方法和基片处理装置

- 基片处理装置、基片处理系统和基片处理方法

- 基片处理装置、基片处理系统和基片处理方法