基片处理方法和基片处理装置

文献发布时间:2023-06-19 19:23:34

技术领域

本发明涉及基片处理方法和基片处理装置。

背景技术

基片在带有较多电荷时,存在该基片的器件发生损伤(静电破坏),或在利用静电力使基片从载置台脱离时发生破损的情况。为此,一直以来需要进行减少基片上的电荷的除静电处理。例如,专利文献1公开了一种技术,在将基片送入基片处理系统时对带电的基片进行除静电处理,降低基片的带电状态。

现有技术文献

专利文献

专利文献1:日本特开2018-107077号公报

发明内容

发明要解决的技术问题

本发明提供一种能够使基片的除静电处理优化的技术。

解决问题的技术手段

根据本发明的一个方面,提供一种基片处理装置的基片处理方法,其包括:从对基片实施等离子体处理和除静电处理的处理模块(Process module)中将所述基片送出,并将该基片输送到能够在大气气氛与真空气氛之间切换的负载锁定部的步骤;在所述负载锁定部测量所述基片的带电状态的步骤;和对所述基片的带电状态的测量结果进行分析来使所述除静电处理优化的步骤。

发明效果

根据一个方面,能够使基片的除静电处理优化。

附图说明

图1是概略地表示一个实施方式的基片处理装置的俯视图。

图2是示意地表示负载锁定部和输送装置的一部分的侧视截面图。

图3是表示伴随负载锁定部中的基片的输送过程发生的带电状态的变化的图。

图4是示例说明表示除静电处理的方案的一部分的表。

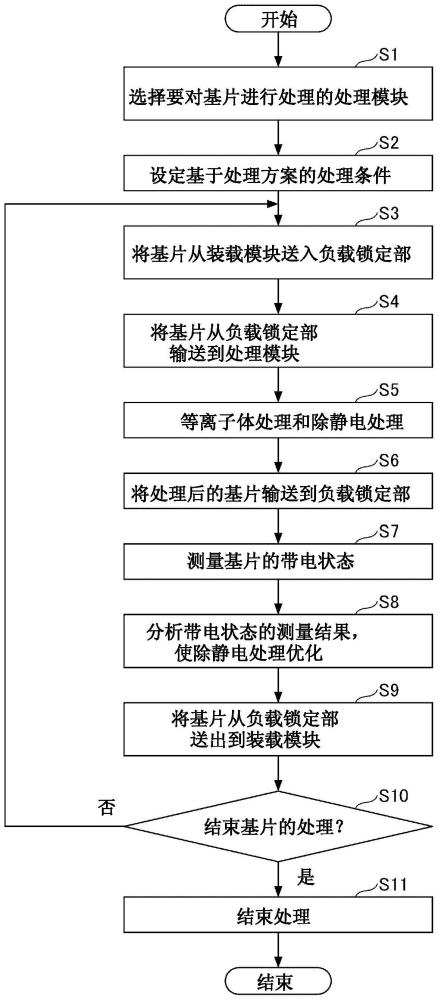

图5是第一实施方式的基片处理方法的流程图。

图6是第二实施方式的基片处理方法的流程图。

图7是第四实施方式的基片处理方法的流程图。

附图标记的说明

1 基片处理装置

10、11、12 处理模块

20 真空输送模块

21 输送装置

27 接触件

30 负载锁定部

37 缓冲部

39 支承销

40 带电测量部

60 控制部

S 基片

具体实施方式

下面参照附图对本发明的实施方式进行说明。对于各图中相同的构成部分标注同一标记,有时会省略重复的说明。

图1是概略地表示一个实施方式的基片处理装置1的俯视图。如图1所示,基片处理装置1构成为多腔室系统,具有对基片S实施等离子体处理的多个(本实施方式为3个)处理模块10、11、12。基片处理装置1在俯视时将方形的真空输送模块20配置于中央位置。并且,基片处理装置1在真空输送模块20的三个侧面分别配置处理模块10、11、12,并在真空输送模块20的剩余一个侧面配置负载锁定部30。处理模块10、11、12、真空输送模块20和负载锁定部30均是能够在减压气氛(真空气氛)下工作的腔室容器。另外,基片处理装置1还包括对各部分的动作进行控制的控制部60。

作为基片处理装置1所处理的基片S,例如可列举液晶显示器、有机EL显示器等FPD(Flat Panel Display,平板显示器)用基片。在此情况下,作为基片S的材料能够应用玻璃或合成树脂等。基片S可以包括表面图案形成有电路的基片,或者不具有电路的支承基片等。基片S的平面尺寸没有特别的限定,但例如能够列举长边为1800mm~3400mm左右的范围、短边为1500mm~3000mm左右的范围或其他尺寸的矩形基片。

在真空输送模块20与各处理模块10、11、12之间,分别设置有基片S可通过的开口部10a、11a、12a。另外,各基片处理装置1包括分别对各开口部10a、11a、12a进行开闭的闸阀13、14、15。各闸阀13、14、15能够在闭状态下将真空输送模块20与各处理模块10、11、12之间气密地密封,在开状态下使真空输送模块20与各处理模块10、11、12之间连通而输送基片S。

各处理模块10、11、12是能够将各自的内部空间10s、11s、12s(基片处理室:处理腔室)保持为规定的减压气氛(真空气氛)的容器,对输送到内部空间10s、11s、12s的基片S实施等离子体处理。在各处理模块10、11、12内设置有用于载置基片S的载置台16。载置台16例如具有利用静电力保持基片S的静电吸盘(未图示)。各处理模块10、11、12对固定于载置台16的基片S进行蚀刻处理、灰化处理、成膜处理这样的等离子体处理。另外,载置台16对基片的固定方法并不特别限定于静电吸盘,也可以应用机械夹具等。基片处理装置1中的各处理模块10、11、12可以进行同种类的等离子体处理,也可以按每个处理模块10、11、12进行不同种类的等离子体处理。

另外,各处理模块10、11、12对因等离子体处理等而带电的基片S进行除静电处理。例如,作为除静电处理,各处理模块10、11、12能够采用这样的方法,即,对埋设于静电吸盘中的吸附电极(未图示)施加与原本施加于吸附电极的电压正负相反、大小相同的直流电压,来消除基片S的电荷。或者,各处理模块10、11、12也可以采用产生除静电处理用的等离子体来消除基片S的电荷的方法。

真空输送模块20构成为能够保持规定的真空气氛的容器。真空输送模块20在容器的内部空间(输送室)具有输送装置21。输送装置21在真空输送模块20与各处理模块10、11、12之间以及该真空输送模块20与负载锁定部30之间输送基片S。

输送装置21包括基座部22、支承于该基座部22的输送臂23、和用于使输送臂23旋转、上下移动以及进退的动作部24,其中,输送臂23在末端执行器具有能够保持基片S的下表面的叉件25。动作部24与控制部60连接,基于控制部60的动作指令使输送臂23动作。叉件25在输送臂23的动作中进入各处理模块10、11、12的内部或负载锁定部30的内部,进行基片S的递交或接收。进而,叉件25能够在递交了基片S的状态下或接收了基片S的状态下,从各处理模块10、11、12或负载锁定部30后退。

图2是示意地表示负载锁定部30和输送装置21的一部分的侧视截面图。如图1和图2所示,叉件25包括多个支承拾取部26,和设置在各支承拾取部26的上表面的与基片S直接接触的多个接触件27。各接触件27由比支承拾取部26软、具有摩擦力且具有导电性的材料形成。作为该接触件27例如能够应用由导电性橡胶形成的环状部件。另外接触件27也可以是突起状部件。输送装置21与接地电位连接,在输送基片S时能够经由各接触件27、支承拾取部26和输送臂23,使基片S带有的电荷移动。若接触件27未发生劣化、处于具有足够导电性的状态,则即使是在各处理模块10、11、12的内部的除静电处理中未完全除去而残留在基片S上的电荷,也能够在输送基片S时补充地除静电至足够低的带电量。

回到图1,基片处理装置1在真空输送模块20与负载锁定部30之间具有供基片S通过的开口部30a,并且具有用于开闭该开口部30a的闸阀31。闸阀31在闭状态下将真空输送模块20与负载锁定部30之间气密地密封,在开状态下使真空输送模块20与负载锁定部30之间连通使得能够输送基片S。另外,基片处理装置1在负载锁定部30与该负载锁定部30的外侧之间具有开口部30b和闸阀32。闸阀32在闭状态下维持负载锁定部30的气密性,在开状态下使负载锁定部30与外侧之间连通使得能够输送基片S。

在负载锁定部30的外侧,为了能够与该负载锁定部30之间进行基片S的送入和送出,连接有相对于基片处理装置1另外设置的装载模块50。装载模块50在大气气氛下进行基片S的待机、输送等。装载模块50没有特别的限定,例如能够应用这样的结构,其包括收纳了多个基片S的载具、空的载具(均未图示)和能够相对于各载具放入/取出基片S的输送机构51。或者,装载模块50也可以是从设置于基片处理装置1周边的其他处理装置接收基片S、且将基片S送至其他处理装置的机构(未图示)。

基片处理装置1的负载锁定部30(负载锁定模块)在位于大气气氛的装载模块50与真空气氛的真空输送模块20之间进行基片S的交接。因此,负载锁定部30构成为能够保持规定的真空气氛的容器。该负载锁定部30为了能够反复地切换至大气气氛和真空气氛,形成为较小的容积。

如图1和图2所示,负载锁定部30的容器包括设置于箭头A方向的多个侧壁部33、设置于箭头B方向的开口部30a和开口部30b、各侧壁部33连结的底部34、被各侧壁部33支承的顶部35,且与接地电位连接。在沿箭头B方向彼此相对的一对开口部30a和开口部30b中,开口部30a具有闸阀31,开口部30b具有闸阀32。

在负载锁定部30的底部34,设置有在该负载锁定部30的空间部30s(负载锁定室)内支承基片S的基片支承部36。基片支承部36的上表面形成为沿箭头A方向交替设置了缓冲部37(支承部)和凹槽38而得到的凹凸。多个凹槽38为了能够使输送装置21(叉件25)的各支承拾取部26进入而呈直线状。

另外,在多个缓冲部37的上表面,设置有当叉件25下降时与基片S接触来支承基片S的多个支承销39(支承件)。支承销39由具有导电性的材料形成。由此,负载锁定部30能够使残留在基片S上带电的电荷经由支承销39、基片支承部36和底部34移动到负载锁定部30的外部。

另外,负载锁定部30在顶部35具有测量基片S的带电状态的带电测量部40。本实施方式中,基片S的“带电状态”作为基片S上产生的静电力的电压(表面电位)而被测量。其中,带电测量部40测量的“带电状态”不限于表面电位,例如也可以测量基片S的电荷量、电位差、电场、其他的物理应力(压电等)。

带电测量部40设置于比箭头B方向的中间位置靠真空输送模块20一侧(闸阀31的附近位置)。另外,图2中表示了1个带电测量部40,但负载锁定部30也可以采用具有多个带电测量部40的结构。例如,基片处理装置1通过沿图1所示的箭头A方向排列配置多个带电测量部40,能够随着基片S沿箭头B方向的输送而获得整个面的带电状态的分布。

带电测量部40可应用能够在空间部30s为真空气氛的状态下测量基片S的带电状态的传感器。这是因为,在空间部30s为大气气氛的状态下,基片S的带电状态会发生变化。该带电测量部40利用静电感应现象,通过测量当传感器靠近带电物体时因带电物体形成的电场而在传感器上引发的感应电荷,来取得表面电位。例如,带电测量部40具有:固定在顶部35上的具有放大电路的测量主体41,和从测量主体41经配线42垂下的、配置在负载锁定部30内部的探头43。测量主体41与控制部60可通信地连接,将测量结果(带电状态的信息)发送给控制部60。探头43配置在顶部35内或比顶部35靠下侧,靠近所输送的基片S。由此,带电测量部40能够提高基片S的表面电位的检测精度。

图3是表示伴随负载锁定部30中的基片S的输送过程发生的带电状态的变化的图。该图中,横轴是时间,纵轴是对基片S测得的表面电位。如图3所示,带电测量部40能够在将基片S从真空输送模块20送入负载锁定部30并利用基片支承部36支承基片S的整个输送过程中,测量基片S的表面电位。

详细而言,基片S的输送过程包括:利用叉件25送入基片S的送入步骤,使叉件25下降的下降步骤,将基片S从叉件25交接给缓冲部37的交接步骤,和抽离叉件25来利用缓冲部37支承基片S的支承步骤。在该基片S的输送过程中,负载锁定部30的内部被减压至与各处理模块10、11、12和真空输送模块20的真空气氛相同的真空气氛。带电测量部40在输送过程的每个步骤(送入步骤、下降步骤、交接步骤、支承步骤)测量变动的基片S的带电状态。

尤其是,在通过基片支承部36支承基片S的支承步骤中测得的基片S的带电状态,表示的是基片处理装置1中处理后的基片S经过各步骤除静电后的结果即最终的带电状态。即,在对基片S实施下一个处理时,将在该带电状态下实施处理。不过,支承步骤初期的带电状态可能不稳定,因此控制部60可以使用支承步骤开始后经过规定时间之后的测量结果。另外,如图3中所示,带电测量部40测得的表面电位(基片S的带电状态)随时间经过反复出现微小的振幅。因此,控制部60优选对带电状态的测量波形计算振幅的平均值(移动平均等)或中位值作为带电状态的值。

另外,控制部60通过在送入步骤中输送基片S时持续利用带电测量部40进行测量,能够识别基片S的沿输送方向的带电状态的分布。于是,控制部60通过使用输送过程的各步骤中的带电测量部40的测量结果(基片S的带电状态),能够适当地识别由各处理模块10、11、12的除静电处理的状态、输送基片S时接触件27除静电的状态、以及通过基片支承部36支承基片S时支承销39除静电的状态得到的除静电的结果,从而能够使除静电处理优化。

另外,负载锁定部30的结构也可以是,分别具有用于从装载模块50送入未处理的基片S的空间部,和用于从真空输送模块20送入处理后的基片S的空间部(例如是具有上下两层的空间部的结构)。在此情况下,将带电测量部40适当地设置在包围各空间部的壁部即可。

回到图1,基片处理装置1的控制部60具有控制器主体61和与控制器主体61连接的用户接口65。控制器主体61可应用具有1个以上的处理器62、存储器63、未图示的输入输出接口以及电子电路的控制用计算机。处理器62是CPU、ASIC、FPGA、由多个半导体分立器件构成的电路等中的一个或多个的组合。存储器63包括易失性存储器、非易失性存储器(例如光盘、DVD、硬盘、闪存等),存储用于使基片处理装置1动作的程序、等离子体处理的处理条件等处理方案R(还参照图4)。

用户接口65可应用供用户为了管理基片处理装置1而进行指令输入操作等的键盘、将基片处理装置1的运行状况可视化显示的显示器、或者具有显示和输入这两个功能的触摸面板等。

本实施方式的基片处理装置1基本上按照以上所述构成,下面对其动作(基片处理方法)进行说明。

基片处理装置1通过在负载锁定部30具有带电测量部40,能够基于带电测量部40的测量结果(基片S的带电状态)使各处理模块10、11、12的除静电处理优化。另外,以下对在各处理模块10、11、12之中有代表性的处理模块10进行处理的情形进行说明,但当然通过其他处理模块11、12也能够实施相同的处理。

具体而言,控制部60通过执行以下(a)~(d)的处理内容来使除静电处理优化。

(a)基于从处理模块10送入负载锁定部30后的基片S的带电状态,重新设定除静电处理的时间(下文也称除静电期间)。

(b)基于基片S在负载锁定部30内部的输送过程中的基片S的带电状态,推算(推断)输送装置21的接触件27或负载锁定部30的支承销39的劣化,在推算为发生了劣化的情况下延长除静电期间。

(c)基于基片S在负载锁定部30内部的输送过程中的基片S的带电状态,识别基片S的带电状态的分布。

(d)基于从装载模块50送入到负载锁定部30中的未处理的基片S的带电状态,和在处理模块处理后从处理模块送入到负载锁定部30中的处理后的基片S的带电状态,重新设定除静电期间。

下面针对基片处理方法的(a)~(d)的处理内容,分成第一~第四实施方式进行说明。另外,基片处理装置1可以构成为实施(a)~(d)的处理内容中的任一个,也可以构成为组合地实施(a)~(d)的处理内容中的多个或全部。

〔第一实施方式〕

(a)的处理内容是,按照经处理模块10进行了等离子体处理和除静电处理的处理后的基片S的带电状态,使通过该处理模块10进行除静电处理的除静电期间缩短或延长。例如,以下对经处理模块10处理后的基片S的带电极性为正(表面电位为正值)的情况进行说明。

当基片S带正电时,基片处理装置1通过除静电处理使表面电位向负侧降低。于是,在除静电处理后的基片S的带电状态比目标带电状态小的情况下,可以说除静电期间过长。因而,控制部60缩短下一个处理的基片S的除静电期间。反之,在除静电处理后的基片S的带电状态比目标带电状态大的情况下,可以说除静电期间过短。因而,控制部60延长下一个处理的基片S的除静电期间。另外,为简单起见,视作接触件27和支承销39不存在导电性劣化,对基片支承部36上最终的基片S的带电状态进行了说明,但如后所述,即使接触件27和支承销39发生了劣化,结果上也是进行同样的处理。

图4是示例说明表示除静电处理的方案R的一部分的表。为简单起见,省略了除静电处理以外的处理步骤。因此,空栏部分视作不相关,未记载数值。如图4所示,在记载了基片S的处理条件的方案R中,描述了处理模块10的除静电处理中的目标表面电位(带电状态)和初始除静电期间。控制部60在对从装载模块50输送的第一片基片S通过处理模块10最初进行除静电处理的情况下,按照遵从方案R的目标带电状态和除静电期间进行处理。另外,目标带电状态、初始除静电期间也可以构成为能够由用户经由用户接口65设定。

接着,如图2所示,控制部60将除静电处理后的基片S从处理模块10输送到负载锁定部30,利用负载锁定部30的带电测量部40测量基片S的带电状态,并基于其测量结果变更除静电期间。在(a)的处理内容中,控制部60优选使用通过基片支承部36支承基片S的支承步骤的带电测量部40的测量结果(还参照图3)。由此,能够利用基片S的最终带电状态的测量结果。

例如,若方案R中目标带电状态为100V且除静电期间为40秒,而除静电处理后的基片S的带电状态(测量结果)为80V,在此情况下可以说除静电期间过长。因此控制部60缩短除静电期间。

除静电期间的缩短可以是,计算测得的基片S的带电状态与目标带电状态之差(带电差),根据带电差来设定缩短的期间。作为一例可以是,控制部60按照带电差每增大1V则缩短1秒的方式重新设定除静电期间。即,上例中,基于带电差为20V这一结果,控制部60将40秒的除静电期间缩短20秒。或者,除静电期间的缩短也可以采用每进行一次基片S的处理就缩短规定期间的方法。

反之,若目标带电状态为100V且除静电期间为20秒,而除静电处理后的基片S的带电状态(测量结果)为110V,在此情况下可以说除静电期间过短。因此控制部60延长除静电期间。除静电期间的延长同样可以是,计算测得的基片S的带电状态与目标带电状态之差(带电差),根据带电差来设定延长的期间。或者,除静电期间的延长也可以采用每进行一次基片S的处理就延长规定期间的方法。

另外,在带电差为规定范围(例如数V)以内的情况下,控制部60也可以不重新设定除静电期间。由此,控制部60能够抑制除静电期间在每次处理模块10的处理中发生变化的情况,能够避免因带电测量部40的测量误差等的影响导致的变动。

再反之,在经处理模块10处理后的基片S的带电极性为负(表面电位为负值)的情况下,基片处理装置1通过除静电处理使表面电位向正侧降低。于是,在除静电处理后的基片S的带电状态比目标带电状态大(接近0)的情况下,可以说除静电期间过长。因而,控制部60缩短下一个处理的基片S的除静电期间。反之,在除静电处理后的基片S的带电状态比目标带电状态小(位于负侧)的情况下,可以说除静电期间过短。因而,控制部60延长下一个处理的基片S的除静电期间。

图5是第一实施方式(对应于(a)的处理内容)的基片处理方法的流程图。如图5所示,控制部60在基片处理装置1开始基片S的处理时,从各处理模块10、11、12中选择要对基片S进行处理的处理模块10(步骤S1)。之后,控制部60针对选中的处理模块10的等离子体处理和除静电处理,设定基于方案R的处理条件(步骤S2)。由此,设定了作为除静电处理的条件的目标带电状态和初始除静电期间。

接着,控制部60将基片S从装载模块50送入负载锁定部30(步骤S3),进而控制输送装置21,将负载锁定部30的基片S输送到选中的处理模块10(步骤S4)。在输送了基片S后,控制部60对基片S实施等离子体处理和除静电处理(步骤S5)。此时,控制部60按照设定的目标带电状态和除静电期间执行除静电处理。例如,在通过处理模块10最初进行除静电处理的情况下,进行方案R的除静电期间的除静电处理。

在基片S处理后,控制部60将处理后的基片S从处理模块10送出,并将该基片S输送到负载锁定部30(步骤S6)。并且,控制部60利用负载锁定部30的带电测量部40测量被基片支承部36支承的基片S的带电状态(步骤S7)。由此,控制部60从带电测量部40接收测量结果。

之后,控制部60通过分析带电状态的测量结果,进行除静电处理的优化(步骤S8)。即,控制部60在测量结果的分析中,对按之前设定的除静电期间进行除静电处理后的基片S的带电状态与目标带电状态进行比较。根据该比较的结果,在基片S的带电状态的绝对值比目标带电状态的绝对值大的情况下,延长下一个除静电处理的时间,在基片S的带电状态的绝对值比目标带电状态的绝对值小的情况下,缩短下一个除静电处理的时间。另外,如上所述,在进行除静电处理的优化时,控制部60也可以计算按之前设定的除静电期间进行除静电处理后的基片S的带电状态与目标带电状态之间的带电差,基于带电差重新设定除静电期间。

在测量基片S的带电状态后,控制部60将负载锁定部30的基片S从负载锁定部30送出至装载模块50(步骤S9)。由此,基片处理装置1能够对之前进行过处理的处理模块10新输送未处理的基片S。然后,处理模块10判断是否结束基片S的处理(步骤S10),在继续基片S的处理的情况下(步骤S10:“否”),回到步骤S3反复其后同样的处理流程。

如上所述,在步骤S8中,控制部60重新设定了对下一个基片S进行除静电处理时的除静电期间。因此,在步骤S5中,控制部60按照重新设定了的除静电期间进行除静电处理。其结果是,在除静电期间过长的情况下,能够减少除静电期间来缩短整个处理的时间,并且能够抑制因除静电处理而产生的颗粒。反之,在除静电期间不足的情况下,能够延长除静电期间来降低带电状态,减少形成在基片S上的器件受到的损伤。

另一方面,在要结束基片S的处理的情况下(步骤S10:“是”),控制部60前进至步骤S11进行结束处理。在该结束处理中,控制部60优选存储经过步骤S8进行了优化的除静电处理的信息。由此,控制部60在重新开始基片S的处理时,能够使用所存储的除静电处理的信息(优化的信息)来从最初开始进行除静电处理。

如上所述,第一实施方式的基片处理方法在负载锁定部30对处理模块10处理后的基片S测量带电状态,实现除静电处理的优化。因此,基片处理方法能够使基片S的带电状态为所希望的带电状态,并且能够将处理模块10的处理期间调节为合适的长度。另外,基片处理装置1无需在各处理模块10设置带电测量部40,能够降低制造成本。

〔第二实施方式〕

(b)的处理内容是,使用基片S在负载锁定部30内部的输送过程中的基片S的带电状态的变化,推算(推定)与基片S接触的导电性部件(输送装置21的接触件27、基片支承部36的支承销39)的劣化。另外,第二实施方式对经处理模块10处理后的基片S的带电极性为正(表面电位为正值)的情况进行说明,但带电极性为负的情况当然也与为正的情况同样,能够抑制导电性部件的劣化。

如图3所示可知,在负载锁定部30的内部,当输送基片S时基片S的带电状态也发生变化。这是因为,带电测量部40是利用了静电感应的部件,因此若对象物与传感器的距离变化则传感器所引发的电荷变化,测量结果发生变化。因而,伴随输送臂23下降而出现的带电状态的变化是表面上的。因此,通过与其他输送处理之间对送入步骤彼此的带电状态进行比较,以及支承步骤彼此的带电状态进行比较,能够分别判断接触件27的(关于导电性的)劣化、支承销39的(关于导电性的)劣化。

此处,在支承步骤中,在基片支承部36的具有导电性的各支承销39支承着基片S的状态下,基片S上带有的电子经由各支承销39被释放到接地电位。从而,基片S的带电状态随支承步骤的实施而降低。在因长时间使用等导致支承销39发生了劣化的情况下,在支承步骤中,基片S的带电状态的降低变弱(或者不再变化)。

因此,控制部60能够基于支承步骤中基片S的带电状态推算支承销39的劣化。例如,控制部60对支承步骤中过去实施过相同处理条件(目标带电状态、除静电期间等)的除静电处理时的基片S的带电状态(多个的情况下可以取平均值)与当前的基片S的带电状态进行比较。然后,在基片S的带电状态的降低变小规定以上的情况下,判断为支承销39发生劣化。或者也可以是,控制部60计算通过支承步骤支承基片S时的带电状态随时间经过的降低率,在计算出的降低率小于降低率阈值(未图示)的情况下,判断为支承销39发生劣化。

接着,控制部60在判断为支承销39发生劣化时,作为除静电处理的优化方式,将各处理模块10、11、12的除静电期间重新设定得较长。例如,控制部60基于支承销39的劣化判断,使除静电期间延长预先设定的期间。另外,控制部60也可以构成为,计算支承销39的劣化程度,随着劣化程度变得越大而将除静电期间设定得越长。

另外,在送入步骤中,在输送装置21(叉件25)的具有导电性的各接触件27支承着基片S的状态下,基片S带有的电荷也会经由各接触件27被释放到接地电位。从而,基片S的带电状态在实施送入步骤的期间降低。在因长时间使用等导致接触件27发生了劣化的情况下,在送入步骤中,基片S的带电状态的降低变弱(或者不再变化)。不过,送入步骤中带电测量部40检测出的电位除了基片S的带电状态之外,还包括基片支承部36带有的电荷。

因此,控制部60通过使用送入步骤中的基片S的带电状态和支承步骤中的基片S的带电状态这两者,来推算接触件27的劣化。例如,控制部60从当前的送入步骤中的基片S的带电状态减去当前的支承步骤中的基片S的带电状态,来除去基片支承部36带电的影响。然后,将当前的减法结果与过去实施相同处理条件(目标带电状态、除静电期间等)的除静电处理时的减法结果比较,在减法结果变小了规定以上的量的情况下,判断为接触件27发生劣化。

控制部60在判断为接触件27发生劣化时,与支承销39同样地,将各处理模块10、11、12中的除静电处理的时间重新设定得较长。例如,控制部60基于接触件27的劣化判断,使除静电期间延长预先设定的期间。接触件27发生了劣化时的除静电期间的延长量和支承销39发生了劣化时的除静电期间的延长量可以相同也可以彼此不同。另外,控制部60也可以构成为,计算接触件27的劣化程度,随着劣化程度越增大而将除静电期间设定得越长。

图6是第二实施方式(对应于(b)的处理内容)的基片处理方法的流程图。如图6所示,控制部60在步骤S21~S26进行与上述对应于(a)的处理内容的基片处理方法的步骤S1~S6相同的处理。然后,控制部60在将基片S于负载锁定部30内部输送的输送过程中,利用带电测量部40持续测量基片S的带电状态(步骤S27)。控制部60接收该基片S的带电状态的测量结果,将其存储在存储器63中。

之后,控制部60通过分析带电状态的测量结果,进行除静电处理的优化(步骤S28)。即,控制部60在测量结果的分析中,如上所述根据送入步骤、支承步骤中的基片S的带电状态,提取表示接触件27的状态的指标和表示支承销39的劣化的指标。

进一步,控制部60基于提取出的各指标分别判断接触件27的劣化和支承销39的劣化(步骤S29)。在判断为接触件27或支承销39未发生劣化的情况下(步骤S29:“否”),控制部60不实施与劣化对应的除静电期间校正(步骤S30)。因此,控制部60在不基于其他的判断而重新设定除静电期间的情况下,维持目前的除静电期间。

另一方面,在判断为接触件27或支承销39发生了劣化的情况下(步骤S29:“是”),控制部60进行使下一个除静电处理的时间延长的校正(步骤S31)。

另外,在测量基片S的带电状态后,控制部60将负载锁定部30的基片S从负载锁定部30送出至装载模块50(步骤S32)。由此,基片处理装置1能够对之前进行了处理的处理模块10新输送未处理的基片S。然后,处理模块10判断是否结束基片S的处理(步骤S33),在继续基片S的处理的情况下(步骤S33:“否”),回到步骤S23反复其后同样的处理流程。

在接触件27或支承销39发生了劣化的情况下,控制部60将除静电期间重新设定得较长。因此,在步骤S25中,控制部60按照延长了的除静电期间进行除静电处理。基片处理装置1通过随着接触件27或支承销39的劣化而增长除静电期间,从整个处理来看能够将基片S的带电状态维持为一定,即使不立即进行维护或部件更换也能够以同样的质量对基片S进行处理。

另一方面,在要结束基片S的处理的情况下(步骤S33:“是”),控制部60前进至步骤S34进行结束处理。在该结束处理中,控制部60优选存储优化了的除静电处理的信息。由此,控制部60在重新开始基片S的处理时,能够使用优化了的信息来从最初开始进行除静电处理。

如上所述,在第二实施方式的基片处理方法中,推算接触件27的劣化和支承销39的劣化。基片处理装置1通过将该劣化的信息经由用户接口65通知用户,能够提醒用户进行基片处理装置1的维护。另外,在基片处理方法中,即使不立即进行维护,也由于延长了除静电期间,所以能够通过处理模块10降低基片S的带电状态。于是,基片处理方法能够推迟输送装置21或负载锁定部30的维护,能够在下一次定期维护的时机一并进行维护或部件更换,能够抑制装置的停工期。

〔第三实施方式〕

(c)的处理内容是,识别经处理模块10进行了等离子体处理和除静电处理的基片S的带电状态的分布,监视带电状态的均匀性。另外,第三实施方式也是对经处理模块10处理后的基片S的带电极性为正(表面电位为正值)的情况进行说明,但带电极性为负的情况当然也与为正的情况同样地,能够监视带电状态的分布。

在此情况下,控制部60使用在基片S的输送过程的送入步骤中测得的基片S的带电状态,基于基片S的输送速度和带电测量部40的位置,提取沿基片S的延伸方向的带电状态的分布。并且,例如控制部60在基片S的带电状态沿基片S的面方向处于规定的允许误差内(可视作均匀的范围)的情况下,判断为确保了处理后的基片S的质量。反之,控制部60在基片S的带电状态沿基片S的面方向超过了规定的允许误差的情况下,判断为处理后的基片S的带电状态存在不均匀(质量降低)。

另外,控制部60可以对判断为带电状态存在不均匀的基片S再次进行除静电处理。此时,基片处理装置1可以将基片S再次输送到处理模块10在处理模块10进行除静电处理,也可以采用使基片S在负载锁定部30中长时间待机来经由支承销39使电荷移动的除静电处理。或者,控制部60也可以在装载模块50中拣选确保了质量的基片S和质量降低的基片S。

〔第四实施方式〕

(d)的处理内容是,测量从装载模块50送入负载锁定部30中的基片S的带电状态,使用该测量结果(下文也称未处理带电状态)监视经处理模块10处理后的基片S的带电状态。即,供给到基片处理装置1中的基片S有的情况下已经带电(存在引入带电)。在存在引入(带入)带电的情况下,若原样进行分析并将基于分析结果的除静电期间的调节应用于下个除静电处理,可能无法正确地进行除静电处理,因此,在第四实施方式的基片处理方法中,排除该引入带电的影响,能够准确地捕获各处理模块10、11、12处理后的基片S的带电状态。此处,能够考虑到引入带电为正且通过等离子体处理带正电的情况、引入带电为正且通过等离子体处理带负电的情况、引入带电为负且通过等离子体处理带正电的情况、以及引入带电为负且通过等离子体处理带负电的情况。

详细而言,控制部60计算从处理后的基片S的带电状态减去未处理带电状态得到的差(下面称为处理前后差)。控制部60对该处理前后差与预先保存的阈值进行比较。阈值被设定成,对于不存在引入带电的情况下的基片S能够正确地进行除静电期间的调节。处理前后差和阈值优选以绝对值进行比较。此处,处理前后差小于阈值的情况指的是,包括基片S的表面电位带正电的状态和基片S的表面电位带负电的状态在内,可以说除静电处理过长。因而,控制部60缩短下一个处理的基片S的除静电期间。反之,处理前后差大于阈值的情况指的是,包括基片S的表面电位带正电的状态和基片S的表面电位带负电的状态在内,可以说除静电处理过短。因而,控制部60延长下一个处理的基片S的除静电期间。

图7是第四实施方式(对应于(d)的处理内容)的基片处理方法的流程图。如图7所示,控制部60在步骤S41~S43进行与上述对应于(a)的处理内容的基片处理方法的步骤S1~S3相同的处理。

然后,控制部60对送入负载锁定部30中的基片S利用带电测量部40测量带电状态(未处理带电状态)(步骤S44)。接着,控制部60接收带电测量部40测得的测量结果(未处理带电状态),将其存储在存储器63中。

之后,控制部60控制输送装置21,将负载锁定部30的基片S输送到选中的处理模块10(步骤S45)。在输送了基片S后,控制部60对基片S实施等离子体处理和除静电处理(步骤S46)。此时,控制部60按照设定的目标带电状态和除静电期间执行除静电处理。

在基片S处理后,控制部60将处理后的基片S从处理模块10送出,并将该基片S输送到负载锁定部30(步骤S47)。并且,控制部60利用负载锁定部30的带电测量部40测量输送来的处理后的基片S的带电状态(步骤S48)。由此,控制部60接收带电测量部40测得的测量结果,将其存储在存储器63中。

接着,控制部60分析处理后的基片S的带电状态和未处理带电状态,进行除静电处理的优化(步骤S49)。控制部60在测量结果的分析中,从处理后的基片S的带电状态减去未处理带电状态,计算处理前后差。控制部60在该处理前后差的绝对值比预先保存的阈值小的情况下,在进行优化时缩短下一个除静电处理的时间,在处理前后差的绝对值比阈值大的情况下,在进行优化时延长下一个除静电处理的时间。

另外,在测量基片S的带电状态后,控制部60将负载锁定部30的基片S从负载锁定部30送出至装载模块50(步骤S50)。由此,基片处理装置1能够对之前进行了处理的处理模块10新输送未处理的基片S。为此,处理模块10判断是否结束基片S的处理(步骤S51),在继续基片S的处理的情况下(步骤S51:“否”),回到步骤S43反复其后同样的处理流程。

如上所述,在步骤S49中,控制部60重新设定对下一个基片S进行除静电处理时的除静电期间。因此,在步骤S46中,控制部60按照重新设定了的除静电期间进行除静电处理。其结果是,能够减少过长的除静电期间来缩短整个处理的时间,并且能够抑制因除静电处理而产生的颗粒,而在除静电期间不足的情况下,能够延长除静电期间来降低带电状态,减少形成在基片S上的器件受到的损伤。

另一方面,在要结束基片S的处理的情况下(步骤S51:“是”),控制部60前进至步骤S52进行结束处理。在该结束处理中,控制部60优选存储经过步骤S49进行了优化的除静电处理的信息。由此,控制部60在重新开始基片S的处理时,能够使用所存储的除静电处理的信息(优化了的信息)来从最初开始进行除静电处理。

如上所述,第四实施方式的基片处理方法在考虑了未处理带电状态的基础上识别处理后的基片S的带电状态,由此能够更高精度地监视处理模块10的除静电处理能力,能够适当地调节除静电期间。另外,在基片处理方法中,在推算具有导电性的部件的劣化时(即(b)的处理内容),也可以利用从装载模块50送入基片S时的未处理带电状态。进而,在基片处理方法中,在监视基片S的带电状态的分布时(即(c)的处理内容),也可以利用从装载模块50送入基片S时的未处理带电状态。

另外,在基片处理方法中,在从装载模块50将基片S送入负载锁定部30时的未处理带电状态原本就为规定以上的情况下,可以停止将基片S输送到处理模块10。或者,在基片处理方法中,在未处理带电状态原本就为规定以上的情况下,也可以在将基片输送到处理模块10后立即实施除静电处理。

将在以上实施方式中说明了的本发明的技术思想和效果记载如下。

本发明的第一方案是一种基片处理装置1的基片处理方法,包括:从对基片S实施等离子体处理和除静电处理的处理模块10、11、12中将基片S送出,并将该基片S输送到能够切换成大气气氛和真空气氛的负载锁定部30的步骤;在负载锁定部30测量基片S的带电状态的步骤;和对基片S的带电状态的测量结果进行分析来使除静电处理优化的步骤。

根据上述方案,基片处理方法能够在负载锁定部30中稳定地测量基片S的带电状态,通过使用该测量结果,能够使基片S的除静电处理优化。例如,基片处理方法通过根据基片S的带电状态调节除静电处理的时间,能够促进缩短基片S的整个处理的时间,并且抑制颗粒的产生。另外,除静电处理的优化不限于调节除静电期间,也可以调节除静电处理中供给的电力。例如可以是,在带电状态的绝对值大的情况下,增大电力供给量来提高除静电能力,而在带电状态的绝对值小的情况下,减小电力供给量来降低除静电能力。

另外,在测量基片S的带电状态的步骤中,使负载锁定部30内部为真空气氛。由此,基片处理方法能够抑制因大气气氛导致基片S的带电状态发生变化,能够更高精度地测量基片S的带电状态。

另外,负载锁定部30包括对输送来的基片S进行支承的支承部(缓冲部37),在测量基片S的带电状态的步骤中,利用设置于负载锁定部30的带电测量部40测量被支承部支承的基片S的表面电位。由此,基片处理方法能够简单地测量基片S的带电状态即表面电位。

另外,包括在处理模块10、11、12与负载锁定部30之间输送基片S的输送装置21,输送装置21中与基片S接触的接触件27和在支承部(缓冲部37)与基片S接触的支承件(支承销39)分别具有导电性,在使除静电处理优化的步骤中,基于支承在支承部上的基片S的带电状态、和通过输送装置21在负载锁定部30内部输送的基片S的带电状态的测量结果,推算接触件27和支承件的导电性的劣化。由此,基片处理方法能够稳定地推算输送装置21的接触件27和负载锁定部30(缓冲部37)的支承件的导电性的劣化。

另外,在推算接触件27或支承件(支承销39)的导电性发生了劣化的情况下,使除静电处理的时间优化。由此,在基片处理方法中,即使接触件27或支承件的导电性劣化了,也通过延长时间进行除静电处理,能够确保基片S的质量,将基片处理装置1的维护推迟。

另外,在使除静电处理优化的步骤中,对按之前设定的除静电处理的时间进行除静电处理后的基片S的带电状态与目标带电状态进行比较,基于该比较(结果)调节下一个除静电处理的时间。由此,基片处理方法能够适当地调节除静电处理的时间。

另外,在使除静电处理优化的步骤中,计算按之前设定的除静电期间进行除静电处理后的基片S的带电状态与目标带电状态之间的带电差,基于带电差重新设定除静电处理的时间。由此,基片处理方法能够更加顺畅地调节除静电处理的时间。

另外,在测量基片S的带电状态的步骤中,持续测量在负载锁定部30内部输送的基片S的带电状态,在使除静电处理优化的步骤中,提取基片的带电状态的分布。由此,基片处理方法能够识别整个基片S的带电状态的分布,能够抑制带电状态的不均匀等。

另外,还包括:将被处理模块10、11、12处理前的基片S输送到负载锁定部30的步骤;和在负载锁定部30中测量处理前的基片S的带电状态的步骤,在使除静电处理优化的步骤中,基于被处理模块10、11、12处理后的基片S的带电状态和处理前的基片S的带电状态,使除静电处理优化。由此,基片处理方法能够更高精度地使除静电处理优化。

另外,在使除静电处理优化的步骤中,计算输送到负载锁定部30的处理后的基片S的带电状态与输送到负载锁定部的处理前的带电状态之间的差量,对差量与预先设定的阈值进行比较,在差量为阈值以上的情况下延长除静电处理的时间。由此,基片处理方法基于差量较大这一情况延长除静电处理的时间,能够抑制基片S的除静电不足。

另外,在差量小于阈值的情况下缩短除静电处理的时间。由此,基片处理方法基于差量较小这一情况缩短除静电处理的时间,能够进一步提高基片处理的作业效率。

另外,本发明的第二方案是一种基片处理装置1,包括:对基片S实施等离子体处理和除静电处理的处理模块10、11、12;能够切换成大气气氛和真空气氛的负载锁定部30;将处理模块10、11、12处理后的基片S从处理模块10、11、12输送到负载锁定部30的真空输送模块20;设置于负载锁定部30的、用于测量基片S的带电状态的带电测量部40;和对带电测量部40的测量结果进行处理的控制部60,控制部60对基片S的带电状态的测量结果进行分析来使除静电处理优化。由此,基片处理装置1能够使基片S的处理中的除静电处理优化。

本发明的实施方式的基片处理方法和基片处理装置1在所有方面都只是例示而不是限制性的。实施方式可以在不脱离本发明技术方案的范围及其思想的基础上,以各种方式实现变形和改进。上述多个实施方式中记载的内容在不产生矛盾的范围内能够采用其他结构,或能够在不产生矛盾的范围内相互组合。例如,基片处理方法和基片处理装置1所处理的基片S的种类不限于FPD用基片,能够以圆盘形状的晶片等各种部件为对象。

本发明的基片处理装置1能够应用于Atomic Layer Deposition(ALD,原子层沉积)装置、Capacitively Coupled Plasma(CCP,电容耦合等离子体)、Inductively CoupledPlasma(ICP,电感耦合等离子体)、Radial Line Slot Antenna(RLSA,径向线缝隙天线)、Electron Cyclotron Resonance Plasma(ECR,微波电子回旋共振等离子体)、HeliconWave Plasma(HWP,螺旋波等离子体)中的任一类型的装置。

- 基片处理装置、基片处理方法和存储介质

- 基片处理装置、基片处理方法和存储介质

- 基片处理装置和基片处理装置的运用方法

- 具有制冷剂用的流路的部件及其控制方法和基片处理装置

- 一种基片刻蚀方法及相应的处理装置

- 基片处理装置,基片支承装置,基片处理方法和基片制造方法

- 基片处理系统、基片处理方法和基片处理装置