显示装置及包括该显示装置的瓦片形显示装置

文献发布时间:2024-01-17 01:18:42

技术领域

本发明涉及一种显示装置及包括该显示装置的瓦片形显示装置。

背景技术

随着信息化社会的发展,对用于显示图像的显示装置的需求正以多样的形态增加。显示装置可以是诸如液晶显示装置(Liquid Crystal Display Device)、场发射显示装置(Field Emission Display Device)、发光显示装置(Light Emitting Display Device)等之类的平板显示装置。

发光显示装置可以包括包含有机发光二极管元件而作为发光元件的有机发光显示装置,或者包含诸如发光二极管(LED:Light Emitting Diode)之类的无机发光二极管元件而作为发光元件的发光二极管显示装置。在有机发光显示装置的情况下,通过调节施加到有机发光二极管元件的驱动电流的大小来调节有机发光二极管元件的光的亮度或灰度。但是,无机发光二极管元件发出的光的波长根据驱动电流而变化,因此在无机发光二极管元件以与有机发光二极管元件相同的方法被驱动的情况下,图像的品质可能会降低。

发明内容

本发明所要解决的技术问题在于提供一种能够防止与基板的边缘相邻地布置的布线的短路不良的显示装置及包括该显示装置的瓦片形显示装置。

本发明的技术问题并不限于以上提及的技术问题,本领域技术人员可以通过以下记载明确理解未提及的其他技术问题。

用于解决上述技术问题的根据一实施例的一种显示装置包括:基板,包含排列多个子像素的显示区域和作为所述显示区域的周围的非显示区域;晶体管阵列层,布置在所述基板的第一面上;以及多个发光元件,布置在所述晶体管阵列层上的所述显示区域中并且分别对应于所述多个子像素。所述晶体管阵列层包括:多个像素驱动部,布置在利用所述显示区域的一部分构成的电路区域中,并且分别对应于所述多个子像素且分别包括至少一个晶体管;两个以上的栅极驱动部,布置在所述电路区域中,沿一方向彼此隔开,并且向连接到所述多个像素驱动部的栅极布线供应各自的信号;第一栅极电压供应布线,布置在所述显示区域中的所述电路区域的周围并沿所述一方向延伸;以及两条以上的第一栅极电压辅助布线,沿与所述一方向交叉的另一方向延伸,并且分别连接在所述两个以上的栅极驱动部与所述第一栅极电压供应布线之间。而且,所述两条个以上的第一栅极电压辅助布线中的每一条的一端通过至少一个第一栅极电压布线接触孔而连接到所述第一栅极电压供应布线,并且,所述两条以上的第一栅极电压辅助布线中的每一条的所述一端相比于所述第一栅极电压供应布线而更远离所述基板的与所述第一栅极电压供应布线邻近的边缘。

所述多个发光元件中的每一个可以是倒装芯片型的微型发光二极管元件。

所述显示装置可以配备有分别利用所述多个子像素中的沿所述一方向或所述另一方向相邻的两个以上的子像素构成的多个像素。所述显示装置还可以包括:防静电图案,布置在所述基板的所述第一面中的所述非显示区域的一部分。所述防静电图案可以包括与所述显示区域的边缘平行地布置的主图案和从所述主图案朝向所述显示区域侧突出的多个子图案。所述多个子图案可以分别布置于所述多个像素中的与所述主图案相邻的像素之间,所述多个子图案中的至少一个可以与所述第一栅极电压布线接触孔重叠。

所述第一栅极电压供应布线可以与所述防静电图案的所述主图案邻近地布置。

所述非显示区域可以包括:至少一个垫区域,布置有与所述晶体管阵列层连接的垫。所述防静电图案可以与所述垫区域隔开。

所述显示装置还可以包括:连接布线,布置在与所述基板的所述第一面相反的所述基板的第二面;以及侧面布线,布置在所述基板中的所述第一面与所述第二面之间的一侧面,并分别连接在所述垫与所述连接布线之间。所述连接布线可以通过导电性粘合部件而连接到柔性膜。

所述两条以上的第一栅极电压辅助布线中的每一条的所述一端可以沿所述一方向延伸并且与所述第一栅极电压供应布线重叠。

所述晶体管阵列层还可以包括:第二栅极电压供应布线,布置在所述显示区域中的所述电路区域的周围,沿所述一方向延伸,并且相比于所述第一栅极电压供应布线而更远离所述基板的边缘;以及两条以上的第二栅极电压辅助布线,沿所述另一方向延伸并且分别连接在所述两个以上的栅极驱动部与所述第二栅极电压供应布线之间。所述第一栅极电压供应布线和所述两条以上的第一栅极电压辅助布线可以将预定的第一栅极电平电压传输到所述两个以上的栅极驱动部。所述第二栅极电压供应布线和所述两条以上的第二栅极电压辅助布线可以将与所述第一栅极电平电压不同的电压电平的第二栅极电平电压传输到所述两个以上的栅极驱动部。

所述晶体管阵列层还可以包括:栅极绝缘膜,覆盖所述基板的所述第一面上的半导体层;第一层间绝缘膜,覆盖所述栅极绝缘膜上的第一导电层;第二层间绝缘膜,覆盖所述第一层间绝缘膜上的第二导电层;第一平坦化膜,覆盖所述第二层间绝缘膜上的第三导电层;第二平坦化膜,覆盖所述第一平坦化膜上的第四导电层;以及第三平坦化膜,覆盖所述第二平坦化膜上的第五导电层。所述第一栅极电压供应布线可以利用所述第三导电层构成,所述两条以上的第一栅极电压辅助布线可以利用所述第四导电层构成。

所述晶体管阵列层还可以包括:多个阳极电极,分别对应于所述多个子像素,并利用所述第三平坦化膜上的第六导电层构成;多个阴极电极,分别对应于所述多个子像素,分别与所述多个阳极电极相邻,并利用所述第六导电层构成;多个阳极垫,分别覆盖所述多个阳极电极,利用所述第六导电层上的第七导电层构成;以及多个阴极垫,分别覆盖所述多个阴极电极并利用所述第七导电层构成。所述第七导电层可以利用透明导电性物质构成。所述多个发光元件可以分别布置在所述多个阳极垫和所述多个阴极垫上。

所述防静电图案可以利用所述第七导电层构成。所述第二平坦化膜的与所述基板的边缘邻近的边缘一部分可以暴露到所述第三平坦化膜的外部,所述第一平坦化膜的与所述基板的边缘邻近的边缘一部分可以暴露到所述第二平坦化膜的外部。所述防静电图案的所述多个子图案可以与所述第一平坦化膜、所述第二平坦化膜及所述第三平坦化膜相接。

所述晶体管阵列层还可以包括:扫描写入布线,从所述两个以上的栅极驱动部中的一个被施加扫描写入信号;扫描初始化布线,从所述两个以上的栅极驱动部中的一个被施加扫描初始化信号;扫频信号布线,从所述两个以上的栅极驱动部中的一个被施加扫频信号;第一数据布线,被施加第一数据电压;以及第二数据布线,被施加第二数据电压。所述多个子像素中的每一个的所述像素驱动部可以连接到所述扫描写入布线、所述扫描初始化布线、所述扫频信号布线、所述第一数据布线和所述第二数据布线。所述多个子像素中的每一个的所述像素驱动部可以包括:第一像素驱动电路部,根据所述第一数据布线的所述第一数据电压而生成控制电流;第二像素驱动电路部,根据所述第二数据布线的所述第二数据电压而生成施加到所述阳极电极的驱动电流;以及第三像素驱动电路部,根据所述第一像素驱动电路部的所述控制电流来控制将所述驱动电流施加到所述发光元件的时段。所述第一像素驱动电路部可以包括:第一晶体管,根据所述第一数据电压而生成所述控制电流;第二晶体管,根据所述扫描写入信号而向所述第一晶体管的第一电极施加所述第一数据布线的所述第一数据电压;第三晶体管,根据所述扫描初始化信号向所述第一晶体管的栅极电极施加初始化电压布线的初始化电压;第四晶体管,根据所述扫描写入信号而连接所述第一晶体管的栅极电极与第二电极;以及第一电容器,布置于所述扫频信号布线与所述第一晶体管的栅极电极之间。

所述晶体管阵列层还可以包括:第一电源布线,被施加第一电源电压;第二电源布线,被施加第二电源电压;第一发光布线,从所述两个以上的栅极驱动部中的一个被施加第一发光信号;以及扫描控制布线,从所述两个以上的栅极驱动部中的一个被施加扫描控制信号。所述两条以上的第一栅极电压辅助布线还可以连接到所述多个子像素中的每一个的所述像素驱动部。所述第一像素驱动电路部还可以包括:第五晶体管,根据所述第一发光信号而将所述第一电源布线连接到所述第一晶体管的第一电极;第六晶体管,根据所述第一发光信号而将所述第一晶体管的第二电极连接到所述第三像素驱动电路部;以及第七晶体管,根据所述扫描控制信号而将所述扫频信号布线与所述第一电容器之间的第一节点连接到所述第一栅极电压辅助布线。

所述第二像素驱动电路部可以包括:第八晶体管,根据所述第二数据电压而生成所述驱动电流;第九晶体管,根据所述扫描写入信号而向所述第八晶体管的第一电极施加所述第二数据布线的所述第二数据电压;第十晶体管,根据所述扫描初始化信号而向所述第八晶体管的栅极电极施加所述初始化电压布线的初始化电压;以及第十一晶体管,根据所述扫描写入信号而连接所述第八晶体管的栅极电极与所述第八晶体管的第二电极。

所述第二像素驱动电路部还可以包括:第十二晶体管,根据所述第一发光信号而将所述第二电源布线连接到所述第八晶体管的第一电极;第十三晶体管,根据所述扫描控制信号而将所述第一电源布线连接到第二节点;第十四晶体管,根据所述第一发光信号而将所述第二电源布线连接到所述第二节点;以及第二电容器,布置在所述第八晶体管的栅极电极与所述第二节点之间。

所述第三像素驱动电路部可以在第三节点与所述第一像素驱动电路部的所述第六晶体管连接。所述第三像素驱动电路部可以包括:第十五晶体管,包括连接到所述第三节点的栅极电极;第十六晶体管,根据所述扫描控制信号而将所述第三节点连接到所述初始化电压布线;第十七晶体管,根据所述第二发光信号而将所述第十五晶体管的第二电极连接到所述阳极电极;第十八晶体管,根据所述扫描控制信号而将所述阳极电极连接到所述初始化电压布线;以及第三电容器,布置在所述第三节点与所述初始化电压布线之间。

所述晶体管阵列层还可以包括:第三电源布线,与所述多个阴极电极连接,并被施加第三电源电压;多个第一阳极连接电极,分别对应于所述多个子像素;以及多个第二阳极连接电极,分别对应于所述多个子像素,并分别与所述多个第一阳极连接电极连接。所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管、所述第八晶体管、所述第九晶体管、所述第十晶体管、所述第十一晶体管、所述第十二晶体管、所述第十三晶体管、所述第十四晶体管、所述第十五晶体管、所述第十六晶体管、所述第十七晶体管和所述第十八晶体管中的每一个的沟道、源极电极和漏极电极可以利用所述半导体层构成。所述第一晶体管、所述第二晶体管、所述第三晶体管、所述第四晶体管、所述第五晶体管、所述第六晶体管、所述第七晶体管、所述第八晶体管、所述第九晶体管、所述第十晶体管、所述第十一晶体管、所述第十二晶体管、所述第十三晶体管、所述第十四晶体管、所述第十五晶体管、所述第十六晶体管、所述第十七晶体管和所述第十八晶体管中的每一个的栅极电极及分别作为所述第一电容器、所述第二电容器及所述第三电容器的一端的第一电容器电极、第三电容器电极及第五电容器电极可以利用所述第一导电层构成。分别作为所述第一电容器、所述第二电容器及所述第三电容器的另一端的第二电容器电极、第四电容器电极及第六电容器电极可以利用所述第二导电层构成。所述初始化电压布线、所述扫描初始化布线、所述扫描写入布线、所述第一发光布线、第二发光布线、被施加所述第一电源电压的第一电源水平布线、所述扫频信号布线、所述第一栅极电压辅助布线、所述扫描控制布线以及被施加所述第三电源电压的第三电源辅助布线可以利用所述第三导电层构成。所述第一数据布线、被施加所述第一电源电压的第一电源垂直布线、所述第二数据布线以及所述多个第一阳极连接电极可以利用所述第四导电层构成。所述第二电源布线及所述多个第二阳极连接电极可以利用所述第五导电层构成。所述第三电源布线可以与所述第二电源布线隔开,并可以利用所述第五导电层或所述第六导电层构成。

用于解决上述技术问题的一种瓦片形显示装置包括:彼此并排排列的多个显示装置和布置于所述多个显示装置之间的连接部。所述多个显示装置中的一个包括:基板,包含排列多个子像素的显示区域和作为所述显示区域的周围的非显示区域;晶体管阵列层,布置在所述基板的第一面上;以及多个发光元件,布置在所述晶体管阵列层上的所述显示区域中并且分别对应于所述多个子像素。所述晶体管阵列层还包括:多个像素驱动部,布置在利用所述显示区域的一部分构成的电路区域中,并且分别对应于所述多个子像素且分别包括至少一个晶体管;第一栅极电压供应布线,布置在作为所述电路区域的周围的所述显示区域的边缘一部分并沿一方向延伸;两个以上的栅极驱动部,布置在所述电路区域中,沿所述一方向彼此隔开,并且向连接到所述多个像素驱动部的栅极布线供应栅极信号;以及两条以上的第一栅极电压辅助布线,沿与所述一方向交叉的另一方向延伸,并且分别连接在所述两个以上的栅极驱动部与所述第一栅极电压供应布线之间。所述两条以上的第一栅极电压辅助布线中的每一条的一端通过至少一个第一栅极电压布线接触孔而连接到所述第一栅极电压供应布线,并且,所述两条以上的第一栅极电压辅助布线中的每一条的所述一端相比于所述第一栅极电压供应布线而更远离所述基板的与所述第一栅极电压供应布线邻近的边缘。

所述多个发光元件中的每一个可以是倒装芯片型的微型发光二极管元件。

在所述多个显示装置中的所述一个中,可以配备有分别利用所述多个子像素中的沿所述一方向或所述另一方向相邻的两个以上的子像素构成的多个像素。所述多个显示装置中的所述一个还可以包括:防静电图案,布置在所述基板的所述第一面中的所述非显示区域的一部分。所述防静电图案可以包括与所述显示区域的边缘平行地布置的主图案和从所述主图案朝向所述显示区域侧突出的多个子图案。所述多个子图案可以分别布置于所述多个像素中的与所述主图案相邻的像素之间。所述多个子图案中的至少一个可以与所述第一栅极电压布线接触孔重叠。

所述第一栅极电压供应布线可以与所述防静电图案的所述主图案邻近地布置。

所述非显示区域可以包括:至少一个垫区域,布置有与所述晶体管阵列层连接的垫。所述防静电图案可以与所述垫区域隔开。

所述显示装置中的所述一个还可以包括:连接布线,布置在与所述基板的所述第一面相反的所述基板的第二面;以及侧面布线,布置在所述基板中的所述第一面与所述第二面之间的一侧面,并分别连接在所述垫与所述连接布线之间。所述连接布线可以通过导电性粘合部件而连接到柔性膜。

所述两条以上的第一栅极电压辅助布线中的每一条的所述一端可以沿所述一方向延伸并且与所述第一栅极电压供应布线重叠。

所述晶体管阵列层还可以包括:第二栅极电压供应布线,布置在所述显示区域的边缘一部分,沿所述一方向延伸,并且相比于所述第一栅极电压供应布线更远离所述基板的边缘;以及两条以上的第二栅极电压辅助布线,沿所述另一方向延伸并且分别连接在所述两个以上的栅极驱动部与所述第二栅极电压供应布线之间。所述第一栅极电压供应布线和所述两条以上的第一栅极电压辅助布线可以将预定的第一栅极电平电压传输到所述两个以上的栅极驱动部。所述第二栅极电压供应布线和所述两条以上的第二栅极电压辅助布线可以将与所述第一栅极电平电压不同的电压电平的第二栅极电平电压传输到所述两个以上的栅极驱动部。

所述晶体管阵列层可以包括:栅极绝缘膜,覆盖所述基板的所述第一面上的半导体层;第一层间绝缘膜,覆盖所述栅极绝缘膜上的第一导电层;第二层间绝缘膜,覆盖所述第一层间绝缘膜上的第二导电层;第一平坦化膜,覆盖所述第二层间绝缘膜上的第三导电层;第二平坦化膜,覆盖所述第一平坦化膜上的第四导电层;以及第三平坦化膜,覆盖所述第二平坦化膜上的第五导电层。所述第一栅极电压供应布线可以利用所述第三导电层构成。所述两个以上的第一栅极电压辅助布线可以利用所述第四导电层构成。

所述晶体管阵列层还可以包括:多个阳极电极,分别对应于所述多个子像素,并利用所述第三平坦化膜上的第六导电层构成;多个阴极电极,分别对应于所述多个子像素,分别与所述多个阳极电极相邻,并利用所述第六导电层构成;多个阳极垫,分别覆盖所述多个阳极电极,利用所述第六导电层上的第七导电层构成;以及多个阴极垫,分别覆盖所述多个阴极电极并利用所述第七导电层构成。所述第七导电层可以利用透明导电性物质构成。所述多个发光元件可以分别布置在所述多个阳极垫和所述多个阴极垫上。

所述防静电图案可以利用所述第七导电层构成。所述第二平坦化膜的与所述基板的边缘邻近的边缘一部分可以暴露到所述第三平坦化膜的外部,所述第一平坦化膜的与所述基板的边缘邻近的边缘一部分可以暴露到在所述第二平坦化膜的外部。所述防静电图案的所述多个子图案可以与所述第一平坦化膜、所述第二平坦化膜及所述第三平坦化膜相接。

所述多个显示装置可以以M个行和N个列的矩阵形态排列,其中,M和N为1以上的自然数。

其他实施例的具体事项包含在详细说明及附图中。

根据实施例的显示装置及包括该显示装置的瓦片形显示装置包括布置在电路区域中的两个以上的栅极驱动部、布置在电路区域的周围的第一栅极电压供应布线以及分别连接在两个以上的栅极驱动部与第一栅极电压供应布线之间的两条以上的第一栅极电压辅助布线。在此,两条以上的第一栅极电压辅助布线中的每一条的一端比所述第一栅极电压供应布线更远离所述基板的边缘。如此,可以防止与邻近于基板的边缘而布置的第一栅极电压供应布线重叠的两条以上的栅极电压辅助布线中的每一条的一端暴露到覆盖第一栅极电压辅助布线的平坦化膜的外部。因此,可以防止与基板的边缘邻近地布置的第一栅极电压供应布线的短路不良。

根据实施例的效果不受以上示例性内容的限制,在本说明书中包括更加多样的效果。

附图说明

图1是示出根据一实施例的瓦片形显示装置的立体图。

图2是详细示出图1的A区域的放大布局图。

图3是示出沿图2的C-C'剖切的面的一示例的剖面图。

图4是详细示出图1的B区域的放大布局图。

图5是示出沿图4的D-D'剖切的面的一示例的剖面图。

图6是示出根据一实施例的瓦片形显示装置的框图。

图7是示出根据一实施例的显示装置的显示面板的平面图。

图8及图9是示出关于图7的像素的示例的图。

图10是示出沿图8的E-E'剖切的面的一示例的剖面图。

图11是示出图1的显示装置中的一个显示装置的框图。

图12是示出针对图11的多个子像素中的一个子像素的像素驱动部的一示例的电路图。

图13是示出根据一实施例的第一子像素的半导体层、第一导电层、第二导电层、第三导电层和第四导电层的布局图。

图14是详细示出图13的I区域的放大布局图。

图15是详细示出图13的II区域的放大布局图。

图16是详细示出图13的III区域的放大布局图。

图17是示出图13所示的第一子像素的第五导电层、第六导电层和第七导电层的一示例的布局图。

图18是示出沿图13及图14的F-F'剖切的面的一示例的剖面图。

图19是示出沿图13及图14的G-G'剖切的面的一示例的剖面图。

图20是示出沿图13及图14的H-H'剖切的面的一示例的剖面图。

图21是示出沿图13及图14的I-I'剖切的面的一示例的剖面图。

图22是示出沿图13及图14的J-J'剖切的面的一示例的剖面图。

图23是示出沿图13及图14的K-K'剖切的面的一示例的剖面图。

图24是示出沿图13、图14、图15及图16的L-L'剖切的面的一示例的剖面图。

图25是示出沿图13、图14及图15的M-M'剖切的面的一示例的剖面图。

图26是示出沿图13及图16的N-N'剖切的面的一示例的剖面图。

图27是示出沿图13、图16及图17的O-O'剖切的面的一示例的剖面图。

图28是示出根据一实施例的显示装置的显示面板的布局图。

图29是示出针对图28的P区域的一示例的布局图。

图30是示出针对布置在图29的Q区域中的第三导电层和第四导电层的一示例的布局图。

图31是示出针对布置在图29的Q区域中的第三导电层、第四导电层、第五导电层和第六导电层的一示例的布局图。

图32是示出针对布置在图29的Q区域中的第三导电层、第四导电层、第五导电层、第六导电层和第七导电层的一示例的布局图。

图33是示出短路不良的比较例的剖面图。

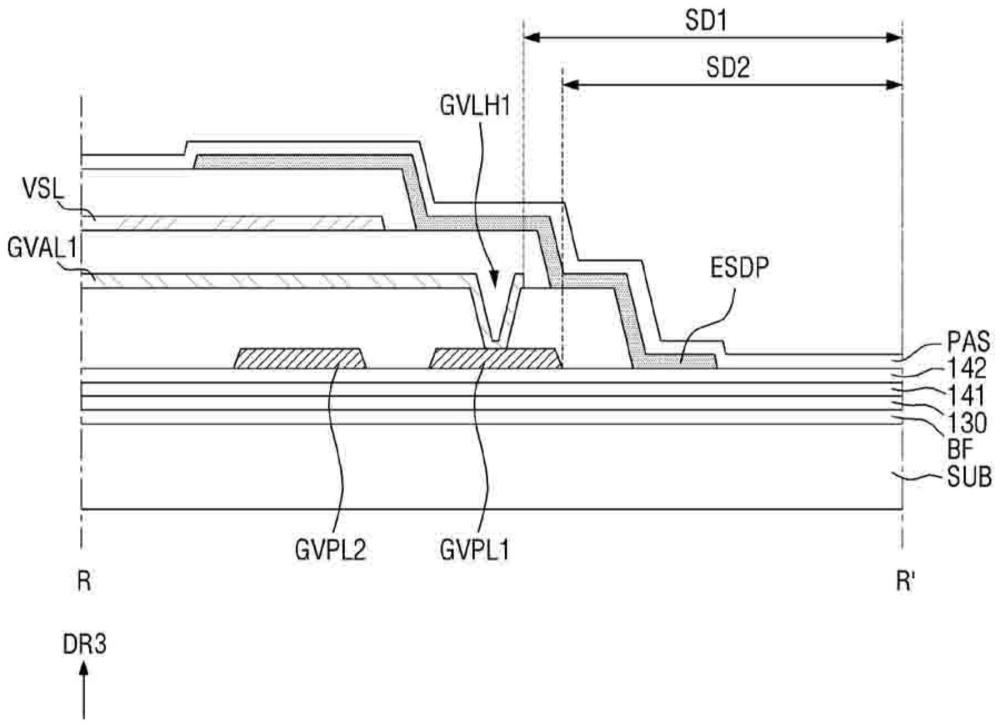

图34是示出沿图32的R-R'剖切的面的一示例的剖面图。

图35是示出沿图32的S-S'剖切的面的一示例的剖面图。

图36是示出图34的另一示例的剖面图。

附图标记的说明

TD:瓦片形显示装置 10:显示装置

11、12、13、14:第一显示装置、第二显示装置、第三显示装置、第四显示装置

SM:连接部

PX1、PX2、PX3、PX4:第一像素、第二像素、第三像素、第四像素

SUB:基板 TFTL:晶体管阵列层

130:栅极绝缘膜 141、142:第一层间绝缘膜、第二层间绝缘膜

160:第一平坦化膜 170:第二平坦化膜

180:第三平坦化膜 PAS:保护膜

LE:发光元件 PAD:垫

100:显示面板 PX:像素

RP、GP、BP:第一子像素、第二子像素、第三子像素

AND:阳极电极 CSD:阴极电极

ANDP:阳极垫 CSS:阴极垫

ANDC:阳极接触电极 CSDC:阴极接触电极

BSUB:基材基板 NSEM:n型半导体

MQW:活性层 PSEM:p型半导体

CTE1、CTE2:第一接触电极、第二接触电极

GDR:栅极驱动部 200:源极驱动部

300:时序控制部 400:电源供应部

GWL:扫描写入布线 GIL:扫描初始化布线

GCL:扫描控制布线 SWPL:扫频信号布线

PWEL:PWM发光布线 PAEL:PAM发光布线

DL:PWM数据布线

RDL、GDL、BDL:第一PAM数据布线、第二PAM数据布线、第三PAM数据布线

DATA:数字视频数据 TS:时序信号

DCS:PWM控制信号 VDD1、VDD2:第一电源、第二电源

VSS:第三电源 VI:初始化电压

VGH、VGL:第一栅极电压和第二栅极电压

PD:像素驱动部

PDU1、PDU2、PDU3:第一像素驱动电路部、第二像素驱动电路部和第三像素驱动电路部

GVPL1、GVPL2:第一栅极电压供应布线和第二栅极电压供应布线

GVAL1、GVAL2:第一栅极电压辅助布线和第二栅极电压辅助布线

GVLH1、GVLH2:第一栅极电压布线接触孔和第二栅极电压布线接触孔

ESDP:防静电图案

ESDM:主图案 ESDS:子图案

具体实施方式

参照与附图一起详细后述的实施例,可以明确本发明的优点和特征以及达成这些的方法。然而本发明可以实现为彼此不同的多样的形态,而不限于以下公开的实施例,并且提供本实施例的目的仅在于使本发明的公开完整并向本发明所属技术领域中具有普通知识的人员完整地告知本发明的范围,本发明仅由权利要求书的范围所定义。

当元件(elements)或层被称为位于其他元件或层“上(on)”时,包括元件(elements)或层在其他元件或层的紧邻的上方或中间夹设有其他层或其他元件的全部情况。在整个说明书中,相同的附图标记指代相同的构成要素。在用于说明实施例的附图中所示出的形状、尺寸、比率、角度、数量等是示例性的,因此本发明并不限于所示出的事项。

虽然“第一”、“第二”等用于叙述多样的构成要素,但这些构成要素显然不受限于这些术语。这些术语仅用于将一个构成要素与其他构成要素进行区分。因此,以下提及的第一构成要素在本发明的技术思想内,显然也可以是第二构成要素。

本发明的多个实施例的各个特征可部分或整体地彼此结合或组合,在技术上可进行多样的联动及驱动,各个实施例可以相对于彼此独立实施,也可通过相关关系而一起实施。

以下,参照附图对实施例进行说明。

图1是示出根据一实施例的瓦片形显示装置的立体图。

参照图1,根据一实施例的瓦片形显示装置TD可以包括在第一方向DR1和第二方向DR2上并排地排列的多个显示装置10以及多个显示装置10之间的连接部SM。

多个显示装置10可以以网格形态排列。多个显示装置10可以以包括M(M为1以上的自然数)个行和N(N为1以上的自然数)个列的矩阵形态排列。

例如,配备于瓦片形显示装置TD的多个显示装置10可以包括以2×2矩阵排列的第一显示装置11、第二显示装置12、第三显示装置13和第四显示装置14。

在这种情况下,第一显示装置11和第二显示装置12可以在第一方向DR1上彼此相邻。第一显示装置11和第三显示装置13可以在第二方向DR2上彼此相邻。第三显示装置13和第四显示装置14可以在第一方向DR1上彼此相邻。第二显示装置12和第四显示装置14可以在第二方向DR2上彼此相邻。

然而,根据一实施例的多个显示装置10的数量和布置形态不限于图1的图示。即,配备于瓦片形显示装置TD的多个显示装置10的数量和布置形态可以根据显示装置10和瓦片形显示装置TD中的每一个的尺寸和形状而改变。

对多个显示装置10中的每一个的详细说明进行后述。

连接部SM可以包括结合部件或粘合部件。即,多个显示装置10可以通过连接部SM的结合部件或粘合部件而彼此连接。

根据图1的示例,连接部SM可以布置于第一显示装置11与第二显示装置12之间、第一显示装置11与第三显示装置13之间、第二显示装置12与第四显示装置14之间、第三显示装置13与第四显示装置14之间。

图2是详细示出图1的A区域的放大布局图。

参照图2,在第一显示装置11、第二显示装置12、第三显示装置13及第四显示装置14彼此邻近的瓦片形显示装置TD的中心区域中,连接部SM可以具有十字形、十字架或加法符号的平面形态。

多个显示装置10中的每一个可以包括在第一方向DR1和第二方向DR2上以矩阵形态排列的多个像素以显示图像。

即,为了显示图像,第一显示装置11可以包括在第一方向DR1和第二方向DR2上以矩阵形态排列的第一像素PX1。为了显示图像,第二显示装置12可以包括在第一方向DR1和第二方向DR2上以矩阵形态排列的第二像素PX2。为了显示图像,第三显示装置13可以包括在第一方向DR1和第二方向DR2上以矩阵形态排列的第三像素PX3。为了显示图像,第四显示装置14可以包括在第一方向DR1和第二方向DR2上以矩阵形态排列的第四像素PX4。

在第一方向DR1上相邻的第一像素PX1之间的最小距离可以被定义为第一水平隔开距离GH1,在第一方向DR1上相邻的第二像素PX2之间的最小距离可以被定义为第二水平隔开距离GH2。第一水平隔开距离GH1和第二水平隔开距离GH2可以实质上相同。

在第一方向DR1上相邻的第一像素PX1与第二像素PX2之间可以布置有连接部SM。在第一方向DR1上相邻的第一像素PX1与第二像素PX2之间的最小距离G12可以是在第一方向DR1上的第一像素PX1与连接部SM之间的最小距离GHS1、在第一方向DR1上的第二像素PX2与连接部SM之间的最小距离GHS2以及连接部SM在第一方向DR1上的宽度GSM1之和。

在第一方向DR1上相邻的第一像素PX1与第二像素PX2之间的最小距离G12、第一水平隔开距离GH1和第二水平隔开距离GH2可以实质上相同。为此,在第一方向DR1上的第一像素PX1与连接部SM之间的最小距离GHS1可以小于第一水平隔开距离GH1,在第一方向DR1上的第二像素PX2与连接部SM之间的最小距离GHS2可以小于第二水平隔开距离GH2。并且,连接部SM在第一方向DR1上的宽度GSM1可以小于第一水平隔开距离GH1或第二水平隔开距离GH2。

在第一方向DR1上相邻的第三像素PX3之间的最小距离可以被定义为第三水平隔开距离GH3,在第一方向DR1上相邻的第四像素PX4之间的最小距离可以被定义为第四水平隔开距离GH4。第三水平隔开距离GH3和第四水平隔开距离GH4可以实质上相同。

在第一方向DR1上相邻的第三像素PX3与第四像素PX4之间可以布置有连接部SM。在第一方向DR1上相邻的第三像素PX3与第四像素PX4之间的最小距离G34可以是在第一方向DR1上的第三像素PX3与连接部SM之间的最小距离GHS3、在第一方向DR1上的第四像素PX4与连接部SM之间的最小距离GHS4以及连接部SM在第一方向DR1上的宽度GSM1之和。

在第一方向DR1上相邻的第三像素PX3与第四像素PX4之间的最小距离G34、第三水平隔开距离GH3和第四水平隔开距离GH4可以实质上相同。为此,在第一方向DR1上的第三像素PX3与连接部SM之间的最小距离GHS3可以小于第三水平隔开距离GH3,在第一方向DR1上的第四像素PX4与连接部SM之间的最小距离GHS4可以小于第四水平隔开距离GH4。并且,连接部SM在第一方向DR1上的宽度GSM1可以小于第三水平隔开距离GH3或第四水平隔开距离GH4。

在第二方向DR2上相邻的第一像素PX1之间的最小距离可以被定义为第一垂直隔开距离GV1,在第二方向DR2上相邻的第三像素PX3之间的最小距离可以被定义为第三垂直隔开距离GV3。第一垂直隔开距离GV1和第三垂直隔开距离GV3可以实质上相同。

在第二方向DR2上相邻的第一像素PX1与第三像素PX3之间可以布置有连接部SM。在第二方向DR2上相邻的第一像素PX1与第三像素PX3之间的最小距离G13可以是在第二方向DR2上的第一像素PX1与连接部SM之间的最小距离GVS1、在第二方向DR2上的第三像素PX3与连接部SM之间的最小距离GVS3以及连接部SM在第二方向DR2上的宽度GSM2之和。

在第二方向DR2上相邻的第一像素PX1与第三像素PX3之间的最小距离G13、第一垂直隔开距离GV1和第三垂直隔开距离GV3可以实质上相同。为此,在第二方向DR2上的第一像素PX1与连接部SM之间的最小距离GVS1可以小于第一垂直隔开距离GV1,在第二方向DR2上的第三像素PX3与连接部SM之间的最小距离GVS3可以小于第三垂直隔开距离GV3。并且,连接部SM在第二方向DR2上的宽度GSM2可以小于第一垂直隔开距离GV1或第三垂直隔开距离GV3。

在第二方向DR2上相邻的第二像素PX2之间的最小距离可以被定义为第二垂直隔开距离GV2,在第二方向DR2上相邻的第四像素PX4之间的最小距离可以被定义为第四垂直隔开距离GV4。第二垂直隔开距离GV2和第四垂直隔开距离GV4可以实质上相同。

在第二方向DR2上相邻的第二像素PX2与第四像素PX4之间可以布置有连接部SM。在第二方向DR2上相邻的第二像素PX2与第四像素PX4之间的最小距离G24可以是在第二方向DR2上的第二像素PX2与连接部SM之间的最小距离GVS2、在第二方向DR2上的第四像素PX4与连接部SM之间的最小距离GVS4以及连接部SM在第二方向DR2上的宽度GSM2之和。

在第二方向DR2上相邻的第二像素PX2与第四像素PX4之间的最小距离G24、第二垂直隔开距离GV2和第四垂直隔开距离GV4可以实质上相同。为此,在第二方向DR2上的第二像素PX2与连接部SM之间的最小距离GVS2可以小于第二垂直隔开距离GV2,在第二方向DR2上的第四像素PX4与连接部SM之间的最小距离GVS4可以小于第四垂直隔开距离GV4。并且,连接部SM在第二方向DR2上的宽度GSM2可以小于第二垂直隔开距离GV2或第四垂直隔开距离GV4。

如上所述,根据一实施例,为了防止在基于多个显示装置10的图像中识别出连接部SM,彼此相邻的显示装置的像素之间的最小距离可以与显示装置中的每一个显示装置的像素之间的最小距离实质上相同。

图3是示出沿图2的C-C'剖切的面的一示例的剖面图。

多个显示装置10中的每一个可以包括发出用于显示图像的光的显示模块和布置在显示模块的发光面上的前盖。

即,参照图3,第一显示装置11包括第一显示模块DPM1和第一前盖COV1。第二显示装置12包括第二显示模块DPM2和第二前盖COV2。

第一显示模块DPM1和第二显示模块DPM2中的每一个包括基板SUB、晶体管阵列层TFTL及发光元件LE。

晶体管阵列层TFTL包括布置在基板SUB上的缓冲膜BF、覆盖缓冲膜BF上的半导体层CH、S、D的栅极绝缘膜130、覆盖栅极绝缘膜130上的栅极电极G和第一电容器电极CAE1的第一层间绝缘膜141、覆盖第一层间绝缘膜141上的第二电容器电极CAE2的第二层间绝缘膜142、覆盖第二层间绝缘膜142上的连接电极CCE的第一平坦化膜160、覆盖第一平坦化膜160上的第一阳极连接电极ANDE1的第二平坦化膜170、覆盖第二平坦化膜170上的第二阳极连接电极ANDE2和第三电源布线VSL的第三平坦化膜180、第三平坦化膜180上的阴极电极CSD和阳极电极AND、覆盖阴极电极CSD的阴极垫CSDP以及覆盖阳极电极AND的阳极垫ANDP。

缓冲膜BF上的半导体层CH、S、D可以包括沟道CH和与沟道CH的两侧接触的源极电极S和漏极电极D。

栅极绝缘膜130上的栅极电极G可以与半导体层的沟道CH重叠。

晶体管TR可以借由这种沟道CH、源极电极S、漏极电极D和栅极电极G而配备。

电容器Cst可以借由第一电容器电极CAE1与第二电容器电极CAE2彼此重叠的区域而配备。

阳极电极AND可以通过连接电极CCE、第一阳极连接电极ANDE1及第二阳极连接电极ANDE2而与晶体管TR的漏极电极D连接。

阴极电极CSD可以连接到第三电源布线VSL。

发光元件LE可以布置在阳极垫ANDP和阴极垫CSDP上。在阳极垫ANDP和阴极垫CSDP与发光元件LE之间分别可以布置有阳极接触电极ANDC和阴极接触电极CSDC。

发光元件LE可以配备为倒装型发光二极管,但一实施例不限于图3的图示。

对这种晶体管阵列层TFTL和发光元件LE的详细说明进行后述。

基板SUB可以包括彼此相反的第一面和第二面以及第一面与第二面之间的第一侧面。晶体管阵列层TFTL可以布置在基板SUB的第一面上。第一面可以是基板SUB的前表面(front side)或上表面(top side),第二面可以是基板SUB的背表面(rear side)或下表面(bottom side)。

基板SUB还可以包括布置在第一面与第一侧面之间以及第二面与第一侧面之间并利用倾斜面构成的倒角(chamfer)面。

在倒角面上可以不布置晶体管阵列层TFTL和发光元件LE。由于第一侧面的宽度因倒角面而减小,因此可以减轻第一显示装置11的基板SUB与第二显示装置12的基板SUB碰撞而破损的情况。

倒角面还可以布置在第一面与除了第一侧面之外的其他侧面中的每一个侧面之间以及第二面与除了第一侧面之外的侧面中的每一个侧面之间。例如,在第一显示装置11和第二显示装置12如图1所示地具有矩形的平面形态的情况下,基板SUB可以包括布置在第一面与第二侧面、第三侧面和第四侧面中的每一个侧面之间以及布置在第二面与第二侧面、第三侧面和第四侧面中的每一个侧面之间的倒角面。

第一前盖COV1可以与基板SUB的倒角面重叠。作为一示例,第一前盖COV1可以在第一方向DR1和第二方向DR2上比基板SUB突出。因此,第一显示装置11的基板SUB与第二显示装置12的基板SUB之间的距离GSUB可以大于第一前盖COV1与第二前盖COV2之间的距离GCOV。

第一前盖COV1和第二前盖COV2中的每一个可以包括粘合部件51、布置在粘合部件51上的光透射率调节层52以及布置在光透射率调节层52上的防眩光层(Anti-GlareLayer)53。

第一前盖COV1的粘合部件51附着到第一显示模块DPM1上。

第二前盖COV2的粘合部件51附着到第二显示模块DPM2上。

粘合部件51可以是能够透射光的透明粘合部件。例如,粘合部件51可以是光学粘合膜(optically clear adhesive film)或光学粘合树脂(optically clear resin)。

防眩光层53可以设计为使外部光漫反射,以防止由于外部光被直接反射而降低图像的可识别性。据此,由于防眩光层53,可以提高由第一显示装置11和第二显示装置12显示的图像的对比度。

光透射率调节层52可以设计为降低外部光或从第一显示模块DPM1和第二显示模块DPM2反射的光的透射率。因此,可以防止第一显示模块DPM1的基板SUB与第二显示模块DPM2的基板SUB之间的间隔区域被外部识别。

防眩光层53可以实现为偏光板,光透射率调节层52可以实现为相位延迟层,但是一实施例不限于此。

图4是详细示出图1的B区域的放大布局图。

参照图4,第一显示装置11还可以包括布置在第一显示装置11的上侧边缘的垫PAD。

作为一示例,第一显示装置11还可以包括与垫PAD连接并沿第二方向DR2延伸的数据布线。在此,垫PAD可以布置在第一显示装置11的基板SUB的第一面中的第二方向DR2的至少一侧边缘。例如,垫PAD可以布置在第一显示装置11的基板SUB的第一面中的上侧边缘和下侧边缘。

图5是示出沿图4的D-D'剖切的面的一示例的剖面图。

参照图5,第一显示装置11还可以包括布置在第二层间绝缘膜142上的数据布线DL、连接到垫PAD并从基板SUB的侧面延伸到第二面的侧面布线SSL以及布置在基板SUB的第二面并连接到侧面布线SSL的连接布线CCL。

连接到数据布线DL的一端的垫PAD可以布置在数据布线DL的一端上。

作为一示例,垫PAD可以包括利用与第一阳极连接电极ANDE1相同的层构成的第一垫层PAD1以及覆盖第一垫层PAD1并利用与阳极垫ANDP及阴极垫CSDP相同的层构成的第二垫层PAD2。

作为另一示例,虽然未单独示出,但连接到数据布线DL的一端的垫PAD可以利用数据布线DL的一部分构成。

作为又一示例,虽然未单独示出,但是连接到数据布线DL的一端的垫PAD布置于覆盖数据布线DL的绝缘膜(未示出)上,并且可以利用通过贯通绝缘膜的孔而接触到数据布线DL的一部分上的导电性图案构成。

然而,这仅是示例,一实施例的垫PAD不限于图5的图示。

在垫PAD为包括第一垫层PAD1及第二垫层PAD2的结构的情况下,垫PAD中的一部分可以不被平坦化膜或其他绝缘膜覆盖而暴露。

第一垫层PAD1可以包括诸如铝和钛的堆叠结构(Ti/Al/Ti)、铝和ITO的堆叠结构(ITO/Al/ITO)、APC合金以及APC合金和ITO的堆叠结构(ITO/APC/ITO)之类的反射率高的金属物质。

第二垫层PAD2可以利用诸如ITO、IZO之类的透明的金属物质(TCO,TransparentConductive Material)构成。

布置在基板SUB的第二面的连接布线CCL可以是利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)和铜(Cu)中的一种或它们的合金构成的单层或多层。

第一显示装置11还可以包括布置于基板SUB的第二面并覆盖连接布线CCL的一部分的下部平坦化膜INS1和覆盖下部平坦化膜INS1的下部绝缘膜INS2。

下部平坦化膜INS1可以利用丙烯酸树脂(acryl resin)、环氧树脂(epoxyresin)、酚醛树脂(phenolic resin)、聚酰胺树脂(polyamide resin)、聚酰亚胺树脂(polyimide resin)等有机膜形成。

下部绝缘膜INS2可以利用无机膜(例如,硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或铝氧化物层)形成。

连接布线CCL可以连接到布置在下部绝缘膜INS2下方的柔性膜FPCB。

柔性膜FPCB可以通过贯通下部平坦化膜INS1和下部绝缘膜INS2的孔以及导电性粘合部件CAM而连接到连接布线CCL。在柔性膜FPCB的下表面上可以布置有用于向数据布线DL供应数据电压的源极驱动电路等。导电性粘合部件CAM可以是各向异性导电膜或各向异性导电膏。

侧面布线SSL可以跨过基板SUB中的第二面的边缘、侧面及第一面的边缘而布置。侧面布线SSL的一端可以布置在第二面,并且可以连接到连接布线CCL。侧面布线SSL的另一端可以布置在第一面,并且可以连接到垫PAD。在侧面布线SSL布置在保护膜PAS上的情况下,侧面布线SSL的另一端可以通过贯通保护膜PAS的接触孔而连接到垫PAD。

侧面布线SSL可以布置在基板SUB的侧面、缓冲膜BF的侧面、栅极绝缘膜130的侧面、第一层间绝缘膜141的侧面、第二层间绝缘膜142的侧面以及保护膜PAS的侧面上。

如上所述,配备于根据一实施例的瓦片形显示装置TD的第一显示装置11包括用于将布置在基板SUB的第一面上的数据布线DL与布置在基板SUB的第二面下方的柔性膜FPCB的源极驱动电路连接的连接布线CCL和侧面布线SSL。即,由于源极驱动电路布置在基板SUB的第二面下方,因此可以最小化基板SUB的第一面中的除了布置有像素的显示区域之外的剩余的非显示区域。

图6是示出根据一实施例的瓦片形显示装置的框图。

参照图6,瓦片形显示装置TD与主机系统HOST连接。

主机系统HOST可以实现为电视系统、家庭影院系统、机顶盒、导航系统、DVD播放器、蓝光播放器、个人计算机(PC)、移动电话系统(mobile phone system)和平板计算机中的一个。

用户的命令可以以多样的形式输入到主机系统HOST。例如,主机系统HOST可以被输入基于用户的触摸输入的命令。或者,主机系统HOST可以被输入基于键盘输入或远程控制器的按钮输入的用户的命令。

主机系统HOST可从外部接收与原始图像对应的原始视频数据ODATA。主机系统HOST可以将原始视频数据ODATA划分为与显示装置的数量相同的数量的程度。例如,主机系统HOST可以对应于第一显示装置11、第二显示装置12、第三显示装置13和第四显示装置14而将原始视频数据ODATA划分为与第一图像对应的第一视频数据DATA1、与第二图像对应的第二视频数据DATA2、与第三图像对应的第三视频数据DATA3和与第四图像对应的第四视频数据DATA4。主机系统HOST可以将第一视频数据DATA1传输到第一显示装置11,将第二视频数据DATA2传输到第二显示装置12,将第三视频数据DATA3传输到第三显示装置13,并且将第四视频数据DATA4传输到第四显示装置14。

第一显示装置11可以根据第一视频数据DATA1来显示第一图像,第二显示装置12可以根据第二视频数据DATA2来显示第二图像,第三显示装置13可以根据第三视频数据DATA3来显示第三图像,并且第四显示装置14可以根据第四视频数据DATA4来显示第四图像。据此,用户可以观看通过组合显示在第一显示装置11、第二显示装置12、第三显示装置13和第四显示装置14中的第一图像至第四图像而获得的原始图像。

第一显示装置11可以包括广播调谐部510、信号处理部520、显示部530、扬声器540、用户输入部550、存储部(例如,硬盘驱动器(HDD:Hard disk Driver))560、网络通信部570、用户界面(UI:User Interface)生成部580和控制部590。

广播调谐部510可以根据控制部590的控制而调谐预定信道频率,并且利用天线接收相应信道的广播信号。广播调谐部510可以包括信道检测模块和RF解调模块。

借由广播调谐部510而解调的广播信号由信号处理部520处理并输出到显示部530和扬声器540。在此,信号处理部520可以包括解复用器521、视频解码器522、视频处理部523、音频解码器524和附加数据处理部525。

解复用器521将解调的广播信号分离为视频信号、音频信号和附加数据。分离的视频信号、音频信号和附加数据分别由视频解码器522、音频解码器524和附加数据处理部525恢复。此时,视频解码器522、音频解码器524和附加数据处理部525以与传输广播信号时的编码格式相对应的解码格式进行恢复。

另外,经解码的视频信号被视频处理部523转换为适合于显示部530的输出标准的垂直频率、分辨率、画面比率等,并且经解码的音频信号输出到扬声器540。

显示部530包括显示图像的显示面板100(参照图7)和控制显示面板100的驱动的面板驱动部。针对显示面板100和面板驱动部的详细的框图已经在图4等中叙述,因此省略重复的说明。

用户输入部550可以接收由主机系统HOST传输的信号。用户输入部550可以配备为不仅能够接收关于由主机系统HOST传输的频道的选择和用户界面(UI:User Interface)菜单的选择和操作的数据,还能够接收允许用户选择和输入关于与其他显示装置12~14通信的命令的数据。

存储部560用于存储包括操作系统(OS:Operataion System)程序在内的多样的软件程序、录制的广播节目、视频、照片、其他数据,可以利用硬盘或非易失性存储器等存储介质构成。

网络通信部570用于与主机系统HOST及其他显示装置12~14进行近距离通信,可以利用包括能够实现移动通信、数据通信、蓝牙、RF、以太网等的天线图案的通信模块来实现。

网络通信部570也可以通过后述的天线图案而在根据用于移动通信的技术标准或通信方案(例如,全球移动通信系统(GSM:Global System for Mobile communication)、码分多址(CDMA:Code Division Multi Access)、码分多址2000(CDMA2000:Code DivisionMulti Access 2000)、增强型语音数据优化或仅增强型语音数据(EV-DO:Enhanced Voice-Data Optimized or Enhanced Voice-Data Only)、宽带码分多址(WCDMA:WidebandCDMA)、高速下行链路分组接入(HSDPA:High Speed Downlink Packet Access)、高速上行链路分组接入(HSUPA:High Speed Uplink Packet Access)、长期演进(LTE:Long TermEvolution)、高级长期演进(LTE-A:Long Term Evolution-Advanced)、5G等)构建的移动通信网络上与基站、外部终端和服务器中的至少一个收发无线信号。

网络通信部570可以通过后述的天线图案在根据无线互联网技术的通信网中收发无线信号。作为无线互联网技术,例如包括无线局域网(WLAN:Wireless LAN)、无线保真(Wi-Fi:Wireless-Fidelity)、无线保真直连(Wi-Fi(Wireless Fidelity)Direct)、数字生活网络联盟(DLNA:Digital Living Network Alliance)、无线宽带接入(WiBro:WirelessBroadband)、全球微波接入互操作性(WiMAX:World Inter operability for MicrowaveAccess)、高速下行链路分组接入(HSDPA:HighSpeedDownlinkPacketAccess)、高速上行链路分组接入(HSUPA:HighSpeedUplinkPacketAccess)、长期演进(LTE:Long TermEvolution)、高级长期演进(LTE-A:Long Term Evolution-Advanced)等,天线图案在还包括上述未列出的互联网技术的范围内,根据至少一种无线互联网技术收发数据。

UI生成部580生成用于与主机系统HOST和其他显示装置12~14进行通信的UI菜单,并且可以通过算法代码和OSD IC来实现。用于与主机系统HOST和其他显示装置12~14进行通信的UI菜单可以是用于指定期望通信的对方数字TV并选择期望功能的菜单。

控制部590负责第一显示装置11的整体控制,并且负责主机系统HOST和第二显示装置12、第三显示装置13及第四显示装置14的通信控制,并存储有用于控制的相应算法代码,并且可以利用运行所存储的算法代码的微控制部单元(MCU:Micro Controller Unit)来实现。

控制部590根据用户输入部550的输入和选择来控制相应控制命令和数据通过网络通信部570传输到主机系统HOST和第二显示装置12、第三显示装置13及第四显示装置14。当然,在从主机系统HOST和第二显示装置12、第三显示装置13及第四显示装置14输入预定的控制命令和数据的情况下,根据相应控制命令执行操作。

另外,第二显示装置12的框图、第三显示装置13的框图和第四显示装置14的框图与图6所示的第一显示装置11的框图实质上相同,因此省略对其的说明。

接着,对根据一实施例的显示装置进行说明。作为参考,一实施例的显示装置可以配备为图1的瓦片形显示装置TD的一部分。但是,一实施例的显示装置不限于配备为瓦片形显示装置TD的一部分的情形,也可以配备为单个装置。

图7是示出根据一实施例的显示装置的显示面板的平面图。图8及图9是示出关于图7的像素的示例的图。

参照图7,显示装置10包括平板的显示面板100,并且显示面板100包括在第一方向DR1和第二方向DR2上以矩阵形态排列的多个像素PX。

这种显示装置10是显示运动图像或静止图像的装置,不仅可以用作诸如移动电话(mobile phone)、智能电话(smart phone)、平板个人计算机(tablet PC(personalcomputer))、智能手表(smart watch)、手表电话(watch phone)、移动通信终端、电子记事本、电子书、便携式多媒体播放器(PMP:portable multimedia player)、导航仪、超移动个人计算机(UMPC:Ultra Mobile PC)等的便携式电子设备的显示画面,而且可以用作诸如电视、笔记本计算机、监视器、广告牌、物联网(IOT:internet of things)装置等的多样的产品的显示画面。

显示面板100可以形成为具有第一方向DR1上的长边和与第一方向DR1交叉的第二方向DR2上的短边的矩形形态的平面。第一方向DR1上的长边与第二方向DR2上的短边相遇的边角(corner)可以以具有预定曲率的方式弧形地形成或形成为直角。显示面板100的平面形状不限于四边形,并且可以形成为其他多边形、圆形或椭圆形。显示面板100可以平坦地形成,但不限于此。例如,显示面板100可以包括形成在左右侧末端并且具有恒定曲率或变化曲率的曲面部。此外,显示面板100可以以能够弯曲、弯折、折弯、折叠或卷曲的方式柔软地形成。

如图8和图9所示,多个像素PX中的每一个可以包括多个子像素RP、GP、BP。图8和图9示出了多个像素PX中的每一个包括对应于彼此不同的颜色的三个子像素RP、GP、BP,即包括第一子像素RP、第二子像素GP和第三子像素BP的情形,但是本说明书的实施例不限于此。

第一子像素RP、第二子像素GP和第三子像素BP中的每一个可以具有矩形、正方形或菱形的平面形态。

例如,如图8所示,第一子像素RP、第二子像素GP和第三子像素BP中的每一个可以具有包括第一方向DR1上的短边和第二方向DR2上的长边的矩形形态。而且,第一子像素RP、第二子像素GP和第三子像素BP可以沿第一方向DR1排列。

或者,如图9所示,第一子像素RP、第二子像素GP和第三子像素BP中的每一个可以具有包括在第一方向DR1和第二方向DR2上具有相同长度的边的正方形或菱形的形态。

第二子像素GP和第三子像素BP中的一个和第一子像素RP可以沿第一方向DR1排列,第二子像素GP和第三子像素BP中的另一个和第一子像素RP可以沿第二方向DR2排列。

作为一示例,第一子像素RP和第二子像素GP可以沿第一方向DR1排列,并且第一子像素RP和第三子像素BP可以沿第二方向DR2排列。

作为另一示例,第一子像素RP和第三子像素BP中的一个和第二子像素GP可以沿第一方向DR1排列,第一子像素RP和第三子像素BP中的另一个和第二子像素GP可以沿第二方向DR2排列。或者,第一子像素RP和第二子像素GP中的一个和第三子像素BP可以沿第一方向DR1排列,第一子像素RP和第二子像素BP中的另一个和第三子像素BP可以沿第二方向DR2排列。

第一子像素RP可以发出第一光,第二子像素GP可以发出与第一光不同颜色的第二光,第三子像素BP可以发出与第一光和第二光不同颜色的第三光。

作为一示例,第一光可以是红色波长带的光,第二光可以是绿色波长带的光,第三光可以是蓝色波长带的光。在此,红色波长带可以是大约600nm至750nm的波长带,绿色波长带可以是大约480nm至560nm的波长带,蓝色波长带可以是大约370nm至460nm的波长带,但本说明书的实施例不限于此。

第一子像素RP、第二子像素GP和第三子像素BP中的每一个可以包括具有无机半导体的无机发光元件作为发出光的发光元件。例如,无机发光元件可以是倒装芯片(flipchip)类型的微型发光二极管(LED:Light Emitting Diode),但本说明书的实施例不限于此。

第一子像素RP的面积、第二子像素GP的面积和第三子像素BP的面积可以实质上相同,但是一实施例不限于此。

作为一示例,第一子像素RP的面积、第二子像素GP的面积和第三子像素BP的面积中的至少一个可以与另一个不同。

即,第一子像素RP的面积、第二子像素GP的面积和第三子像素BP的面积中的两个可以实质上相同,且另一个可以与所述两个面积不同。或者,第一子像素RP的面积、第二子像素GP的面积和第三子像素BP的面积可以彼此不同。

图10是示出沿图8的E-E'剖切的面的一示例的剖面图。

参照图10,显示装置10可以包括基板SUB、布置于基板SUB上的晶体管阵列层TFTL以及布置于晶体管阵列层TFTL上的多个发光元件LE。

基板SUB可以是用于支撑晶体管阵列层TFTL及多个发光元件LE的部件。

基板SUB可以是玻璃材质的刚性(rigid)基板。或者,基板SUB可以是能够弯曲(Bending)、折叠(Folding)、卷曲(Rolling)等的柔性(Flexible)基板。在这种情况下,基板SUB可以包括诸如聚酰亚胺(PI)之类的高分子树脂等绝缘物质。

晶体管阵列层TFTL可以包括阳极电极AND、阴极电极CSD、阳极垫ANDP和阴极垫CSDP。

在阳极垫ANDP与发光元件LE之间可以布置有阳极接触电极ANDC,并且在阴极垫CSDP与发光元件LE之间可以布置有阴极接触电极CSDC。

多个发光元件LE中的每一个可以包括基材基板BSUB、n型半导体NSEM、活性层MQW、p型半导体PSEM、第一接触电极CTE1以及第二接触电极CTE2。

基材基板BSUB可以是蓝宝石基板,但一实施例不限于此。

n型半导体NSEM可以布置在基材基板BSUB的一表面上。例如,n型半导体NSEM可以布置在基材基板BSUB的下表面上。

n型半导体NSEM可以利用掺杂有诸如Si、Ge、Se、Sn等之类的n型导电型掺杂剂的GaN构成。

活性层MQW可以布置在n型半导体NSEM的一部分上。

活性层MQW可以包括单量子阱结构或多量子阱结构的物质。在活性层MQW包括多量子阱结构的物质的情况下,也可以是多个阱层(well layer)和势垒层(barrier layer)彼此交替堆叠的结构。此时,阱层可以利用InGaN形成,势垒层可以利用GaN或AlGaN形成,但不限于此。

或者,活性层MQW也可以是能带隙(Band gap)大的类型的半导体物质和能带隙(Band gap)小的半导体物质彼此交替堆叠的结构,或者也可以根据发出的光的波长带而包括不同的III族至V族半导体物质。

p型半导体PSEM可以布置在活性层MQW上。p型半导体PSEM可以利用掺杂有诸如Mg、Zn、Ca、Ba等之类的p型导电型掺杂剂的GaN构成。

第一接触电极CTE1可以布置在p型半导体PSEM上。

第二接触电极CTE2可以布置在n型半导体NSEM中除了布置有活性层MQW的一部分之外的其他一部分上。n型半导体NSEM的布置有第二接触电极CTE2的另一部分可以与n型半导体NSEM的布置有活性层MQW的一部分隔开而布置。

第一接触电极CTE1和阳极电极AND可以通过阳极接触电极ANDC而彼此粘合。

第二接触电极CTE2和阴极电极CSD可以通过阴极接触电极CSDC而彼此粘合。

阳极接触电极ANDC及阴极接触电极CSDC可以是诸如各向异性导电膜(ACF:Anisotropic Conductive Film)或各向异性导电膏(ACP:Anisotropic ConductivePaste)之类的导电性粘合部件。

或者,发光元件LE也可以不包括阳极接触电极ANDC和阴极接触电极CSDC。在这种情况下,第一接触电极CTE1与阳极电极AND之间以及第二接触电极CTE2与阴极电极CSD之间可以通过焊接(soldering)工艺而粘合。

发光元件LE可以是倒装芯片型微型LED。

这种倒装芯片型的发光元件LE包括布置在p型半导体PSEM上的第一接触电极CTE1以及去除活性层MQW和p型半导体PSEM的一部分而被暴露的n型半导体NSEM上的第二接触电极CTE2。即,倒装芯片型的发光元件LE构成第一接触电极CTE1比第二接触电极CTE2突出的台面(MESA)结构。

第一子像素RP、第二子像素GP和第三子像素BP中的每一个子像素包括连接到阳极电极AND和阴极电极CSD的发光元件LE。由于阳极电极AND分别对应于多个子像素RP、GP、BP,因此阳极电极AND可以被称为像素电极。而且,由于阴极电极CSD共同对应于多个子像素RP、GP、BP,因此阴极电极CSD可以被称为公共电极。

阳极电极AND和阴极电极CSD可以包括诸如铝和钛的堆叠结构(Ti/Al/Ti)、铝和ITO的堆叠结构(ITO/Al/ITO)、APC合金及APC合金和ITO的堆叠结构(ITO/APC/ITO)之类的反射率高的金属物质。APC合金是银(Ag)、钯(Pd)和铜(Cu)的合金。

在发光元件LE中,第一方向DR1的长度、第二方向DR2的长度和第三方向DR3的长度可以分别是几μm至几百μm。例如,发光元件LE在第一方向DR1上的长度、发光元件LE在第二方向DR2上的长度和发光元件LE在第三方向DR3上的长度中的每一个可以是大约100μm以下。

发光元件LE可以在诸如硅晶片之类的半导体基板上生长而形成。发光元件LE中的每一个可以从硅晶片直接转移到基板SUB的阳极垫ANDP和阴极垫CSDP上。或者,发光元件LE中的每一个可以通过使用静电头(Electrostatic Head)的静电方式或将PDMS或硅等具有弹性的高分子物质用作转印基板的印模方式而转移到基板SUB的阳极垫ANDP和阴极垫CSDP上。

显示面板100还可以包括覆盖阳极垫ANDP和阴极垫CSDP中的每一个的边缘的保护膜PAS。

作为一示例,保护膜PAS可以利用硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层及铝氧化物层等无机膜形成。

图11是示出图1的显示装置中的一个的框图。

参照图11,根据一实施例的显示装置10可以包括显示面板100、栅极驱动部GDR、源极驱动部200、时序控制部300和电源供应部400。

显示面板100可以包括发出用于显示图像的各个光的子像素RP、GP、BP以及连接到子像素RP、GP、BP的栅极布线、数据布线和电压布线。

栅极布线可以沿第一方向DR1延伸,并且可以包括扫描写入布线GWL、扫描初始化布线GIL、扫描控制布线GCL、扫频信号布线SWPL、PWM发光布线PWEL和PAM发光布线PAEL。

数据布线可以沿第二方向DR2延伸,并且可以包括PWM数据布线DL、第一PAM数据布线RDL、第二PAM数据布线GDL和第三PAM数据布线BDL。第一PAM数据布线RDL可以彼此电连接,第二PAM数据布线GDL可以彼此电连接,并且第三PAM数据布线BDL可以彼此电连接。

电压布线可以分别对应于第一电源电压VDD1、第二电源电压VDD2、第三电源电压VSS、初始化电压VI及栅极电平电压VGH、VGL。

子像素RP、GP、BP可以包括发出第一光的第一子像素RP、发出第二光的第二子像素GP和发出第三光的第三子像素BP。第一光表示红色波长带的光,第二光表示绿色波长带的光,第三光表示蓝色波长带的光。例如,第一光的主峰值波长可以位于大约600nm至750nm,第二光的主峰值波长可以位于大约480nm至560nm,并且第三光的主峰值波长可以位于大约370nm至460nm。

子像素RP、GP、BP中的每一个可以与扫描写入布线GWL中的一个、扫描初始化布线GIL中的一个、扫描控制布线GCL中的一个、扫频信号布线SWPL的一个、PWM发光布线PWEL中的一个以及PAM发光布线PAEL中的一个连接。并且,第一子像素RP中的每一个可以与PWM数据布线DL中的一个和第一PAM数据布线RDL中的一个连接。并且,第二子像素GP中的每一个可以与PWM数据布线DL中的一个和第二PAM数据布线GDL中的一个连接。并且,第三子像素BP中的每一个可以与PWM数据布线DL中的一个和第三PAM数据布线BDL中的一个连接。

显示面板100可以包括用于向包括扫描写入布线GWL、扫描初始化布线GIL、扫描控制布线GCL、扫频信号布线SWPL、PWM发光布线PWEL以及PAM发光布线PAEL的栅极布线施加各自的信号的栅极驱动部GDR。为了便于说明,在图11示出了栅极驱动部GDR布置在显示面板100的第一方向DR1上的一侧边缘的情形,但是根据一实施例的栅极驱动部GDR可以配备为在子像素RP、GP、BP之间以沿第一方向DR1彼此隔开的方式划分布置的多个栅极驱动部GDR。

栅极驱动部GDR可以包括第一扫描信号驱动部SCDR1、第二扫描信号驱动部SCDR2、扫频信号驱动部SWDR及发光信号驱动部EMDR。

第一扫描信号驱动部SCDR1可以根据从时序控制部300输入的第一扫描驱动控制信号而向扫描初始化布线GIL输出扫描初始化信号,并向扫描写入布线GWL输出扫描写入信号。即,第一扫描信号驱动部SCDR1可以输出扫描初始化信号和扫描写入信号。

第二扫描信号驱动部SCDR2可以根据从时序控制部300输入的第二扫描驱动控制信号而向扫描控制布线GCL输出扫描控制信号。

扫频信号驱动部SWDR可以从时序控制部300接收第一发光控制信号及扫频控制信号。

扫频信号驱动部SWDR可以根据第一发光控制信号而向PWM发光布线PWEL输出PWM发光信号,且根据扫频控制信号而向扫频信号布线SWPL输出扫频信号。即,扫频信号驱动部SWDR可以输出PWM发光信号和扫频信号。

发光信号输出部EMDR可以根据从时序控制部300输入的第二发光控制信号而向PAM发光布线PAEL输出PAM发光信号。

时序控制部300接收数字视频数据DATA和时序信号TS。时序控制部300可以根据时序信号TS而生成用于控制栅极驱动部GDR的操作时序的扫描时序控制信号。扫描时序控制信号可以生成第一扫描驱动控制信号、第二扫描驱动控制信号、第一发光控制信号、第二发光控制信号及扫频控制信号。并且,时序控制部300可以生成用于控制源极驱动部200的操作时序的源极控制信号DCS。

时序控制部300将第一扫描驱动控制信号、第二扫描驱动控制信号、第一发光控制信号、第二发光控制信号及扫频控制信号输出至栅极驱动部GDR。时序控制部300将数字视频数据DATA和源极控制信号DCS输出到源极驱动部200。

源极驱动部200将数字视频数据DATA转换为模拟PWM数据电压并输出到PWM数据布线DL。据此,可以借由栅极驱动部GDR的扫描写入信号来选择子像素RP、GP、BP,并且PWM数据电压可以被供应到所选择的子像素RP、GP、BP。

此外,如上面参照图5所述,源极驱动部200可以实现为安装于布置在基板SUB的第二面下方的柔性膜FPCB的源极驱动部电路的集成电路芯片。

电源供应部400可以将第一PAM数据电压共同输出到第一PAM数据布线RDL,将第二PAM数据电压共同输出到第二PAM数据布线GDL,并且将第三PAM数据电压共同输出到第三PAM数据布线BDL。并且,电源供应部400可以生成多个电压并将多个电压输出到显示面板100。

电源供应部400可以将第一电源电压VDD1、第二电源电压VDD2、第三电源电压VSS、初始化电压VI和栅极电平电压VGL、VGH输出到显示面板100。第一电源电压VDD1和第二电源电压VDD2可以是用于驱动子像素RP、GP、BP中的每一个的发光元件的高电位驱动电压。第三电源电压VSS可以是用于驱动子像素RP、GP、BP中的每一个的发光元件的低电位驱动电压。初始化电压VI可以被施加到子像素RP、GP、BP中的每一个,并且栅极电平电压VGL、VGH可以被施加到栅极驱动部GDR。

源极驱动部200、时序控制部300及电源供应部400中的每一个可以形成为集成电路(integrated circuit)。并且,源极驱动部200可以利用多个集成电路形成。

这种集成电路可以安装于布置在基板SUB的第二面下方的柔性膜FPCB(图5)。

图12是示出针对图11的多个子像素中的一个的像素驱动部的一示例的电路图。

参照图12,配备于一实施例的显示面板100的多个子像素RP、GP、BP中的一个的像素驱动部PD可以与第k(k是正整数)扫描写入布线GWLk、第k扫描初始化布线GILk、第k扫描控制布线GCLk、第k扫频信号布线SWPLk、第k PWM发光布线PWELk和第k PAM发光布线PAELk连接。而且,像素驱动部PD可以连接到第j PWM数据布线DLj和第一PAM数据布线RDL。而且,像素驱动部PD可以与被施加第一电源电压VDD1的第一电源布线VDL1、被施加第二电源电压VDD2的第二电源布线VDL2、被施加第三电源电压VSS的第三电源布线VSL、被施加初始化电压VI的初始化电压布线VIL以及被施加第一栅极电平电压VGH的第一栅极电压辅助布线GVAL1连接。

另外,为了便于说明,第j PWM数据布线DLj可以被称为第一数据布线,并且第一PAM数据布线RDL可以被称为第二数据布线。

像素驱动部PD可以包括发光元件(Light Emitting Element)LE、第一像素驱动电路部PDU1、第二像素驱动电路部PDU2和第三像素驱动电路部PDU3。

第一像素驱动电路部PDU1、第二像素驱动电路部PDU2和第三像素驱动电路部PDU3彼此连接,并且发光元件LE可以基于借由第二像素驱动电路部PDU2生成的驱动电流而发光。

发光元件LE可以布置在第十七晶体管T17与第三电源布线VSL之间。

发光元件LE的第一电极可以与第十七晶体管T17的第二电极连接,发光元件LE的第二电极可以与第三电源布线VSL连接。

发光元件LE的第一电极可以是阳极电极(即,像素电极),发光元件LE的第二电极可以是阴极电极(即,公共电极)。

发光元件LE可以是包括第一电极、第二电极及布置于第一电极与第二电极之间的无机半导体的无机发光元件。例如,发光元件LE可以是利用无机半导体构成的微型发光二极管(micro light emitting diode),但不限于此。

第一像素驱动电路部PDU1通过根据第j PWM数据布线DLj的第j PWM数据电压生成控制电流来控制第三像素驱动电路部PDU3的第三节点N3的电压。由于可以借由第一像素驱动电路部PDU1的控制电流来调节在发光元件EL中流动的驱动电流的脉冲宽度,因此第一像素驱动电路部PDU1可以是执行在发光元件EL中流动的驱动电流的脉冲宽度调制(pulsewidth modulation)的脉冲宽度调制部(PWM部)。

第一像素驱动电路部PDU1可以包括第一晶体管T1至第七晶体管T7和第一电容器PC1。

第一晶体管T1根据施加到栅极电极的PWM数据电压来控制在第二电极与第一电极之间流动的控制电流。

第二晶体管T2借由第k扫描写入布线GWLk的第k扫描写入信号而导通,以将第jPWM数据布线DLj的PWM数据电压供应到第一晶体管T1的第一电极。第二晶体管T2的栅极电极可以连接到第k扫描写入布线GWLk,第一电极可以连接到第j PWM数据布线DLj,并且第二电极可以连接到第一晶体管T1的第一电极。

第三晶体管T3借由第k扫描初始化布线GILk的第k扫描初始化信号而导通,以将初始化电压布线VIL与第一晶体管T1的栅极电极连接。据此,在第三晶体管T3导通的时段期间,第一晶体管T1的栅极电极可以放电为初始化电压布线VIL的初始化电压VI。

此时,第k扫描初始化信号的第二栅极电平电压VGL可以与初始化电压布线VIL的初始化电压VI不同。尤其,由于第二栅极电平电压VGL与初始化电压VI之间的差电压大于第三晶体管T3的阈值电压,因此即使在初始化电压VI施加到第一晶体管T1的栅极电极之后,第三晶体管T3也可以稳定地导通。因此,在第三晶体管T3导通的情况下,初始化电压VI可以与第三晶体管T3的阈值电压无关地稳定地施加到第一晶体管T1的栅极电极。

第三晶体管T3可以包括串联连接的多个晶体管。例如,第三晶体管T3可以包括第一子晶体管T31和第二子晶体管T32。据此,可以防止第一晶体管T1的栅极电极的电压通过第三晶体管T3泄漏。第一子晶体管T31的栅极电极可以连接到第k扫描初始化布线GILk,第一电极可以连接到第一晶体管T1的栅极电极,第二电极可以连接到第二子晶体管T32的第一电极。第二子晶体管T32的栅极电极可以连接到第k扫描初始化布线GILk,第一电极可以连接到第一子晶体管T31的第二电极,第二电极可以连接到初始化电压布线VIL。

第四晶体管T4借由第k扫描写入布线GWLk的第k扫描写入信号而导通,以连接第一晶体管T1的栅极电极和第二电极。据此,在第四晶体管T4导通的时段期间,第一晶体管T1可以作为二极管操作。

第四晶体管T4可以包括串联连接的多个晶体管。例如,第四晶体管T4可以包括第三子晶体管T41和第四子晶体管T42。据此,可以防止第一晶体管T1的栅极电极的电压通过第四晶体管T4泄漏。第三子晶体管T41的栅极电极可以连接到第k扫描写入布线GWLk,第一电极可以连接到第一晶体管T1的第二电极,第二电极可以连接到第四子晶体管T42的第一电极。第四子晶体管T42的栅极电极可以连接到第k扫描写入布线GWLk,第一电极可以连接到第三子晶体管T41的第二电极,第二电极可以连接到第一晶体管T1的栅极电极。

第五晶体管T5借由第k PWM发光布线PWELk的第k PWM发光信号而导通,以将第一晶体管T1的第一电极连接到第一电源布线VDL1。第五晶体管T5的栅极电极可以连接到第kPWM发光布线PWELk,第五晶体管T5的第一电极可以连接到第一电源布线VDL1,第五晶体管T5的第二电极可以连接到第一晶体管T1的第一电极。

第六晶体管T6借由第k PWM发光布线PWELk的第k PWM发光信号而导通,以将第一晶体管T1的第二电极连接到第三像素驱动电路部PDU3的第三节点N3。第六晶体管T6的栅极电极可以连接到第k PWM发光布线PWELk,第六晶体管T6的第一电极可以连接到第一晶体管T1的第二电极,第六晶体管T6的第二电极可以连接到第三像素驱动电路部PDU3的第三节点N3。

第七晶体管T7借由第k扫描控制布线GCLk的第k扫描控制信号而导通,以将第一栅极电压辅助布线GVAL1的第一栅极电平电压VGH供应到与第k扫频信号布线SWPLk连接的第一节点N1。据此,在第一晶体管T1的栅极电极被施加初始化电压VI的期间和对第j PWM数据布线DLj的PWM数据电压和第一晶体管T1的阈值电压Vth1进行编程的期间,可以防止因第一电容器PC1导致第一晶体管T1的栅极电极的电压变化反映到第k扫频信号布线SWPLk的第k扫频信号。第七晶体管T7的栅极电极可以连接到第k扫描控制布线GCLk,第七晶体管T7的第一电极可以连接到第一栅极电压辅助布线GVAL1,第七晶体管T7的第二电极可以连接到第一节点N1。

第一电容器PC1可以布置在第一晶体管T1的栅极电极与第一节点N1之间。第一电容器PC1的一电极可以连接到第一晶体管T1的栅极电极,并且第一电容器PC1的另一电极可以连接到第一节点N1。

第一节点N1可以是第k扫频信号布线SWPLk、第七晶体管T7的第二电极及第一电容器PC1的另一电极的接点。

第二像素驱动电路部PDU2根据第一PAM数据布线RDL的第一PAM数据电压生成施加到发光元件LE的驱动电流。第二像素驱动电路部PDU2可以是执行脉冲幅度调制(pulseamplitude modulation)的脉冲幅度调制部(PAM部)。第二像素驱动电路部PDU2可以是根据第一PAM数据电压生成恒定的驱动电流的恒定电流生成部。

并且,第一子像素RP中的每一个的第二像素驱动电路部PDU2可以与第一子像素RP的亮度无关地接收相同的第一PAM数据电压来生成相同的驱动电流。与此相同地,第二子像素GP中的每一个的第二像素驱动电路部PDU2可以与第二子像素GP的亮度无关地接收相同的第二PAM数据电压来生成相同的驱动电流。第三子像素BP中的每一个的第三像素驱动电路部PDU3可以与第三子像素BP的亮度无关地接收相同的第三PAM数据电压来生成相同的驱动电流。

第二像素驱动电路部PDU2可以包括第八晶体管T8至第十四晶体管T14和第二电容器PC2。

第八晶体管T8根据施加到栅极电极的电压来控制流向发光元件LE的驱动电流。

第九晶体管T9借由第k扫描写入布线GWLk的第k扫描写入信号而导通,以将第一PAM数据布线RDL的第一PAM数据电压供应到第八晶体管T8的第一电极。第九晶体管T9的栅极电极可以连接到第k扫描写入布线GWLk,第九晶体管T9的第一电极可以连接到第一PAM数据布线RDL,第九晶体管T9的第二电极可以连接到第八晶体管T8的第一电极。

第十晶体管T10借由第k扫描初始化布线GILk的第k扫描初始化信号而导通,以将初始化电压布线VIL连接到第八晶体管T8的栅极电极。据此,在第十晶体管T10导通的时段期间,第八晶体管T8的栅极电极可以放电为初始化电压布线VIL的初始化电压VI。此时,第k扫描初始化信号的第二栅极电平电压VGL可以与初始化电压布线VIL的初始化电压VI不同。尤其,由于第二栅极电平电压VGL与初始化电压VI之间的差电压大于第十晶体管T10的阈值电压,因此即使在初始化电压VI被施加到第八晶体管T8的栅极电极之后,第十晶体管T10也可以稳定地导通。因此,在第十晶体管T10导通的情况下,初始化电压VI可以与第十晶体管T10的阈值电压无关地稳定地施加到第八晶体管T8的栅极电极。

第十晶体管T10可以包括串联连接的多个晶体管。例如,第十晶体管T10可以包括第五子晶体管T101和第六子晶体管T102。据此,可以防止第八晶体管T8的栅极电极的电压通过第十晶体管T10泄漏。第五子晶体管T101的栅极电极可以与第k扫描初始化布线GILk连接,第五子晶体管T101的第一电极可以与第八晶体管T8的栅极电极连接,第五子晶体管T101的第二电极可以与第六子晶体管T102的第一电极连接。第六子晶体管T102的栅极电极可以与第k扫描初始化布线GILk连接,第六子晶体管T102的第一电极可以与第五子晶体管T101的第二电极连接,第六子晶体管T102的第二电极可以与初始化电压布线VIL连接。

第十一晶体管T11借由第k扫描写入布线GWLk的第k扫描写入信号而导通,从而连接第八晶体管T8的栅极电极与第二电极。据此,在第十一晶体管T11导通的时段期间,第八晶体管T8可以作为二极管操作。

第十一晶体管T11可以包括串联连接的多个晶体管。例如,第十一晶体管T11可以包括第七子晶体管T111和第八子晶体管T112。据此,可以防止第八晶体管T8的栅极电极的电压通过第十一晶体管T11泄漏。第七子晶体管T111的栅极电极可以连接到第k扫描写入布线GWLk,第七子晶体管T111的第一电极可以连接到第八晶体管T8的第二电极,第七子晶体管T111的第二电极可以连接到第八子晶体管T112的第一电极。第八子晶体管T112的栅极电极可以连接到第k扫描写入布线GWLk,第八子晶体管T112的第一电极可以连接到第七子晶体管T111的第二电极,第八子晶体管T112的第二电极可以连接到第八晶体管T8的栅极电极。

第十二晶体管T12借由第k PWM发光布线PWELk的第k PWM发光信号而导通,以将第八晶体管T8的第一电极连接到第二电源布线VDL2。第十二晶体管T12的栅极电极可以连接到第k PWM发光布线PWELk,第十二晶体管T12的第一电极可以连接到第一电源布线VDL1,第十二晶体管T12的第二电极可以连接到第八晶体管T8的第一电极。

第十三晶体管T13借由第k扫描控制布线GCLk的第k扫描控制信号而导通,以将第一电源布线VDL1连接到第二节点N2。第十三晶体管T13的栅极电极可以连接到第k扫描控制布线GCLk,第十三晶体管T13的第一电极可以连接到第一电源布线VDL1,第十三晶体管T13的第二电极可以连接到第二节点N2。

第十四晶体管T14借由第k PWM发光布线PWELk的第k PWM发光信号而导通,以将第二电源布线VDL2连接到第二节点N2。因此,在第十四晶体管T14导通的情况下,第二电源布线VDL2的第二电源电压VDD2可以供应到第二节点N2。第十四晶体管T14的栅极电极可以连接到第k PWM发光布线PWELk,第十四晶体管T14的第一电极可以连接到第二电源布线VDL2,第十四晶体管T14的第二电极可以连接到第二节点N2。

第二电容器PC2可以布置在第八晶体管T8的栅极电极与第二节点N2之间。第二电容器PC2的一电极可以连接到第八晶体管T8的栅极电极,第二电容器PC2的另一电极可以连接到第二节点N2。

第二节点N2可以是第十三晶体管T13的第二电极、第十四晶体管T14的第二电极和第二电容器PC2的另一电极的接点。

第三像素驱动电路部PDU3根据第三节点N3的电压调节驱动电流施加到发光元件LE的时段。

第三像素驱动电路部PDU3可以包括第十五晶体管T15至第十九晶体管T19和第三电容器PC3。

第十五晶体管T15根据第三节点N3的电压而导通或截止。在第十五晶体管T15导通的情况下,第八晶体管T8的驱动电流可以供应到发光元件LE,在第十五晶体管T15截止的情况下,第八晶体管T8的驱动电流可以不供应到发光元件LE。因此,第十五晶体管T15的导通时段可以与发光元件LE的发光时段实质上相同。第十五晶体管T15的栅极电极可以连接到第三节点N3,第十五晶体管T15的第一电极可以连接到第八晶体管T8的第二电极,第十五晶体管T15的第二电极可以连接到第十七晶体管T17的第一电极。

第十六晶体管T16借由第k扫描控制布线GCLk的第k扫描控制信号而导通,以将初始化电压布线VIL连接到第三节点N3。据此,在第十六晶体管T16导通的时段期间,第三节点N3可以放电为初始化电压布线VIL的初始化电压VI。

第十六晶体管T16可以包括串联连接的多个晶体管。例如,第十六晶体管T16可以包括第九子晶体管T161和第十子晶体管T162。据此,可以防止第三节点N3的电压通过第十六晶体管T16泄漏。第九子晶体管T161的栅极电极可以连接到第k扫描控制布线GCLk,第九子晶体管T161的第一电极可以连接到第三节点N3,第九子晶体管T161的第二电极可以连接到第十子晶体管T162的第一电极。第十子晶体管T162的栅极电极可以连接到第k扫描控制布线GCLk,第十子晶体管T162的第一电极可以连接到第九子晶体管T161的第二电极,第十子晶体管T162的第二电极可以连接到初始化电压布线VIL。

第十七晶体管T17借由第k PAM发光布线PAELk的第k PAM发光信号而导通,以将第十五晶体管T15的第二电极连接到发光元件LE的第一电极。第十七晶体管T17的栅极电极可以连接到第k PAM发光布线PAELk,第十七晶体管T17的第一电极可以连接到第十五晶体管T15的第二电极,第十七晶体管T17的第二电极可以连接到发光元件LE的第一电极。

第十八晶体管T18借由第k扫描控制布线GCLk的第k扫描控制信号而导通,以将初始化电压布线VIL连接到发光元件LE的第一电极。据此,在第十八晶体管T18导通的时段期间,发光元件LE的第一电极可以放电为初始化电压布线VIL的初始化电压VI。第十八晶体管T18的栅极电极可以连接到第k扫描控制布线GCLk,第十八晶体管T18的第一电极可以连接到发光元件LE的第一电极,第十八晶体管T18的第二电极可以连接到初始化电压布线VIL。

第十九晶体管T19借由测试信号布线TSTL的测试信号而导通,以将发光元件LE的第一电极连接到第三电源布线VSL。第十九晶体管T19的栅极电极可以连接到测试信号布线TSTL,第十九晶体管T19的第一电极可以连接到发光元件EL的第一电极,第十九晶体管T19的第二电极可以连接到第三电源布线VSL。

第三电容器PC3可以布置在第三节点N3与初始化电压布线VIL之间。第三电容器PC3的一电极可以连接到第三节点N3,第三电容器PC3的另一电极可以连接到初始化电压布线VIL。

第三节点N3可以是第六晶体管T6的第二电极、第十五晶体管T15的栅极电极、第九子晶体管T161的第一电极和第三电容器PC3的一电极的接点。

第一晶体管T1至第十九晶体管T19中的每一个的第一电极和第二电极中的一个可以是源极电极,并且另一个可以是漏极电极。第一晶体管T1至第十九晶体管T19中的每一个的沟道可以利用多晶硅(Poly Silicon)、非晶硅以及氧化物半导体中的一种形成。在第一晶体管T1至第十九晶体管T19中的每一个的沟道为多晶硅的情况下,第一晶体管T1至第十九晶体管T19可以通过低温多晶硅(LTPS:Low Temperature Poly Silicon)工艺形成。

在图12中,以第一晶体管T1至第十九晶体管T19中的每一个利用P型MOSFET形成的情形为中心进行了说明,但一实施例不限于此。例如,第一晶体管T1至第十九晶体管T19中的至少一个也可以利用N型MOSFET形成。

作为一示例,为了通过阻断漏电流来提高发光元件EL的黑色表现能力,在第一子像素RP中,第三晶体管T3的第一子晶体管T31和第二子晶体管T32、第四晶体管T4的第三子晶体管T41和第四子晶体管T42、第十晶体管T10的第五子晶体管T101和第六子晶体管T102以及第十一晶体管T11的第七子晶体管T111和第八子晶体管T112可以利用N型MOSFET形成。

在这种情况下,第四晶体管T4的第三子晶体管T41的栅极电极和第四子晶体管T42的栅极电极以及第十一晶体管T11的第七子晶体管T111的栅极电极和第八子晶体管T112的栅极电极可以连接到第k控制信号GNLk。第k扫描初始化信号GILk和第k控制信号GNLk可以具有由第一栅极电平电压VGH产生的脉冲。

并且,第三晶体管T3的第一子晶体管T31和第二子晶体管T32、第四晶体管T4的第三子晶体管T41和第四子晶体管T42、第十晶体管T10的第五子晶体管T101和第六子晶体管T102以及第十一晶体管T11的第七子晶体管T111和第八子晶体管T112的沟道可以利用氧化物半导体形成,并且其余晶体管的沟道可以利用多晶硅形成。

或者,第三晶体管T3的第一子晶体管T31和第二子晶体管T32中的一个可以利用N型MOSFET形成,并且另一个可以利用P型MOSFET形成。在这种情况下,在第三晶体管T3的第一子晶体管T31和第二子晶体管T32中,利用N型MOSFET形成的晶体管的沟道可以利用氧化物半导体形成,利用P型MOSFET形成的晶体管的沟道可以利用多晶硅形成。

或者,第四晶体管T4的第三子晶体管T41和第四子晶体管T42中的一个可以利用N型MOSFET形成,并且另一个可以利用P型MOSFET形成。在这种情况下,在第四晶体管T4的第三子晶体管T41和第四子晶体管T42中,利用N型MOSFET形成的晶体管的沟道可以利用氧化物半导体形成,利用P型MOSFET形成的晶体管的沟道可以利用多晶硅形成。

或者,第十晶体管T10的第五子晶体管T101和第六子晶体管T102中的一个可以利用N型MOSFET形成,并且另一个可以利用P型MOSFET形成。在这种情况下,在第十晶体管T10的第五子晶体管T101和第六子晶体管T102中,利用N型MOSFET形成的晶体管的沟道可以利用氧化物半导体形成,利用P型MOSFET形成的晶体管的沟道可以利用多晶硅形成。

或者,第十一晶体管T11的第七子晶体管T111和第八子晶体管T112中的一个可以利用N型MOSFET形成,并且另一个可以利用P型MOSFET形成。在这种情况下,在第十一晶体管T11的第七子晶体管T111和第八子晶体管T112中,利用N型MOSFET形成的晶体管的沟道可以利用氧化物半导体形成,利用P型MOSFET形成的晶体管的沟道可以利用多晶硅形成。

图13是示出根据一实施例的第一子像素的半导体层、第一导电层、第二导电层、第三导电层和第四导电层的布局图。图14是详细示出图13的I区域的放大布局图。图15是详细示出图13的II区域的放大布局图。图16是详细示出图13的III区域的放大布局图。图17是示出图13所示的第一子像素的第五导电层、第六导电层和第七导电层的一示例的布局图。

参照图13、图14、图15及图16,初始化电压布线VIL、第k扫描初始化布线GILk、第k扫描写入布线GWLk、第k PWM发光布线PWELk、第一电源水平布线VDL1、第一栅极电压辅助布线GVAL1、第k扫频信号布线SWPLk、第k扫描控制布线GCLk、第k PAM发光布线PAELk、测试信号布线TSTL及第三电源辅助布线AVSL可以分别沿第一方向DR1延伸,并可以沿第二方向DR2彼此隔开。

第j数据布线DLj、第一电源垂直布线VVDL1及第一PAM数据布线RDL可以沿第二方向DR2延伸。

此外,图11所示的第二PAM数据布线GDL和第三PAM数据布线BDL也可以沿第二方向DR2延伸。

第j数据布线DLj、第一电源垂直布线VVDL1、第一PAM数据布线RDL、第二PAM数据布线GDL和第三PAM数据布线BDL可以沿第一方向DR1彼此隔开。

如图13的图示,第一子像素RP可以包括第一晶体管T1至第十九晶体管T19、第一电容器电极CE1至第六电容器电极CE6、第一栅极连接电极GCE1至第六栅极连接电极GCE6、第一数据连接电极DCE1和第二数据连接电极DCE2、第一连接电极CCE1至第八连接电极CCE8以及第一阳极连接电极ANDE1。

参照图14,第一晶体管T1可以包括第一沟道CH1、第一栅极电极G1、第一源极电极S1以及第一漏极电极D1。

第一沟道CH1可以沿第一方向DR1延伸。

第一栅极电极G1可以在第三方向DR3上与第一沟道CH1重叠。第一栅极电极G1可以通过第一接触孔CT1而连接到第一连接电极CCE1。

第一电容器电极CE1可以与第一栅极电极G1配备为一体。

第一源极电极S1可以布置于第一沟道CH1的一侧,并连接到第二漏极电极D2和第五漏极电极D5。

第一漏极电极D1可以布置在第一沟道CH1的另一侧,并且可以连接到第三子源极电极S41和第六源极电极S6。

第一栅极电极G1可以在第三方向DR3上仅与第一沟道CH1重叠,而不与第一源极电极S1和第一漏极电极D1重叠。

第一源极电极S1和第一漏极电极D1可以在第三方向DR3上与第二电容器电极CE2重叠。

第二晶体管T2包括第二沟道CH2、第二栅极电极G2、第二源极电极S2和第二漏极电极D2。

第二栅极电极G2可以在第三方向DR3上与第二沟道CH2重叠。

第二栅极电极G2可以与第一栅极连接电极GCE1形成为一体。

第二源极电极S2可以布置在第二沟道CH2的一侧,并且可以通过第一数据接触孔DCT1而连接到第一数据连接电极DCE1。

第二漏极电极D2可以布置在第二沟道CH2的另一侧,并且可以连接到第一源极电极S1。第二漏极电极D2可以沿第二方向DR2延伸。

第三晶体管T3可以利用第一子晶体管T31和第二子晶体管T32构成。

第三晶体管T3的第一子晶体管T31包括第一子沟道CH31、第一子栅极电极G31、第一子源极电极S31和第一子漏极电极D31。

第一子栅极电极G31可以与第二栅极连接电极GCE2形成为一体。

第一子沟道CH31可以在第三方向DR3上与第一子栅极电极G31重叠。

第一子源极电极S31可以布置在第一子沟道CH31的一侧,并且可以连接到第四子漏极电极D42。

第一子漏极电极D31可以布置在第一子沟道CH31的另一侧,并且可以连接到第二子源极电极S32。

第一子源极电极S31可以在第三方向DR3上与第k扫描写入布线GWLk重叠。第一子漏极电极S32可以在第三方向DR3上与初始化电压布线VIL重叠。

第三晶体管T3的第二子晶体管T32包括第二子沟道CH32、第二子栅极电极G32、第二子源极电极S32和第二子漏极电极D32。

第二子栅极电极G32可以与第二栅极连接电极GCE2形成为一体。

第二子沟道CH32可以在第三方向DR3上与第二子栅极电极G32重叠。

第二子源极电极S32可以布置在第二子沟道CH32的一侧,并且可以连接到第一子漏极电极D31。

第二子漏极电极D32可以布置在第二子沟道CH32的另一侧,并且可以通过第一电源接触孔VCT1而连接到初始化电压布线VIL。

第二子源极电极S32和第二子漏极电极D32可以在第三方向DR3上与初始化电压布线VIL重叠。

第四晶体管T4可以利用第三子晶体管T41和第四子晶体管T42构成。

第四晶体管T4的第三子晶体管T41包括第三子沟道CH41、第三子栅极电极G41、第三子源极电极S41和第三子漏极电极D41。

第三子栅极电极G41可以与第一栅极连接电极GCE1形成为一体。

第三子沟道CH41可以在第三方向DR3上与第三子栅极电极G41重叠。

第三子源极电极S41可以布置在第三子沟道CH41的一侧,并且可以连接到第一漏极电极D1。

第三子漏极电极D31可以布置在第三子沟道CH41的另一侧,并且可以连接到第四子源极电极S42。

第四晶体管T4的第四子晶体管T42包括第四子沟道CH42、第四子栅极电极G42、第四子源极电极S42和第四子漏极电极D42。

第四子栅极电极G42可以与第一栅极连接电极GCE1形成为一体。

第四子沟道CH42可以在第三方向DR3上与第四子栅极电极G42重叠。

第四子源极电极S42可以布置在第四子沟道CH42的一侧,并且可以连接到第三子漏极电极D32。

第四子漏极电极D42可以布置在第四子沟道CH42的另一侧,并且可以连接到第一子源极电极S31。

第五晶体管T5包括第五沟道CH5、第五栅极电极G5、第五源极电极S5和第五漏极电极D5。

第五栅极电极G5可以与第六栅极连接电极GCE6形成为一体。

第五沟道CH5可以在第三方向DR3上与第五栅极电极G5重叠。

第五源极电极S5可以布置在第五沟道CH5的一侧,并且可以通过第二电源接触孔VCT2而连接到第一电源水平布线HVDL1。

第五漏极电极D5可以布置在第五沟道CH5的另一侧,并且可以连接到第一源极电极S1。第五漏极电极D5可以在第三方向DR3上与第二电容器电极CE2的延伸部EX重叠。

第六晶体管T6包括第六沟道CH6、第六栅极电极G6、第六源极电极S6和第六漏极电极D6。

第六栅极电极G6可以与第六栅极连接电极GCE6形成为一体。

第六沟道CH6可以在第三方向DR3上与第六栅极电极G6重叠。

第六源极电极S6可以布置在第六沟道CH6的一侧,并且可以连接到第一漏极电极D1。

第六漏极电极D6可以布置在第六沟道CH6的另一侧,并且可以通过第十接触孔CT10而连接到第四连接电极CCE4。第六漏极电极D6可以在第三方向DR3上与第二连接电极CCE2和第一电源水平布线HVDL1重叠。

第七晶体管T7包括第七沟道CH7、第七栅极电极G7、第七源极电极S7和第七漏极电极D7。

第七栅极电极G7可以与第三栅极连接电极GCE3形成为一体。第七栅极电极G7可以在第三方向DR3上与初始化电压布线VIL重叠。

第七沟道CH7可以在第三方向DR3上与第七栅极电极G7重叠。

第七源极电极S7可以布置在第七沟道CH7的一侧,并且可以通过第七接触孔CT7而连接到第一栅极电压辅助布线GVAL1。

第七漏极电极D7可以布置在第七沟道CH7的另一侧,并且可以通过第六接触孔CT6而连接到第k扫频信号布线SWPLk。

第八晶体管T8包括第八沟道CH8、第八栅极电极G8、第八源极电极S8和第八漏极电极D8。

第八栅极电极G8可以沿第二方向DR2延伸。第八栅极电极G8可以与第三电容器电极CE3形成为一体。

第八沟道CH8可以在第三方向DR3上与第八栅极电极G8重叠。

第八源极电极S8可以布置在第八沟道CH8的一侧,并且可以连接到第九漏极电极D9和第十二漏极电极D12。

第八漏极电极D8可以布置在第八沟道CH8的另一侧,并且可以连接到第七子源极电极S111。

第九晶体管T9包括第九沟道CH9、第九栅极电极G9、第九源极电极S9和第九漏极电极D9。

第九栅极电极G9可以沿第二方向DR2延伸。第九栅极电极G9可以与第一栅极连接电极GCE1形成为一体。

第九沟道CH9可以在第三方向DR3上与第九栅极电极G9重叠。

第九源极电极S9可以布置在第九沟道CH9的一侧,并可以通过第三数据接触孔DCT3而连接到第二数据连接电极DCE2。

第九漏极电极D9可以布置在第九沟道CH9的另一侧,并且可以连接到第八源极电极D8。

第十晶体管T10可以包括第五子晶体管T101和第六子晶体管T102。

第十晶体管T10的第五子晶体管T101包括第五子沟道CH101、第五子栅极电极G101、第五子源极电极S101和第五子漏极电极D101。

第五子栅极电极G101可以与第二栅极连接电极GCE2形成为一体。

第五子沟道CH101可以在第三方向DR3上与第五子栅极电极G101重叠。

第五子源极电极S101可以布置在第五子沟道CH101的一侧,并可以连接到第八子漏极电极D112。

第五子漏极电极D101可以布置在第五子沟道CH101的另一侧,并且可以连接到第六子源极电极S102。

第五子源极电极S101可以在第三方向DR3上与第k扫描写入布线GWLk重叠。第五子漏极电极S102可以在第三方向DR3上与初始化电压布线VIL重叠。

第十晶体管T10的第六子晶体管T102包括第六子沟道CH102、第六子栅极电极G102、第六子源极电极S102和第六子漏极电极D102。

第六子栅极电极G102可以与第二栅极连接电极GCE2形成为一体。

第六子沟道CH102可以在第三方向DR3上与第六子栅极电极G102重叠。

第六子源极电极S102可以布置在第六子沟道CH102的一侧,并可以连接到第五子漏极电极D101。

第六子漏极电极D102可以布置在第六子沟道CH102的另一侧,并且可以通过第一电源接触孔VCT1而连接到初始化电压布线VIL。

第六子源极电极S102和第六子漏极电极D102可以在第三方向DR3上与初始化电压布线VIL重叠。

第十一晶体管T11可以利用第七子晶体管T111和第八子晶体管T112构成。

第十一晶体管T11的第七子晶体管T111包括第七子沟道CH111、第七子栅极电极G111、第七子源极电极S111和第七子漏极电极D111。

第七子栅极电极G111可以与第一栅极连接电极GCE1形成为一体。

第七子沟道CH111可以在第三方向DR3上与第七子栅极电极G111重叠。

第七子源极电极S111可以布置在第七子沟道CH111的一侧,并可以连接到第八漏极电极D8。

第七子漏极电极D111可以布置在第七子沟道CH111的另一侧,并且可以连接到第八子源极电极S112。

第十一晶体管T11的第八子晶体管T112包括第八子沟道CH112、第八子栅极电极G112、第八子源极电极S112和第八子漏极电极D112。

第八子栅极电极G112可以与第一栅极连接电极GCE1形成为一体。

第八子沟道CH112可以在第三方向DR3上与第八子栅极电极G112重叠。

第八子源极电极S112可以布置在第八子沟道CH112的一侧,并且可以连接到第七子漏极电极D111。

第八子漏极电极D112可以布置在第八子沟道CH112的另一侧,并且可以连接到第五子源极电极S101。

第十二晶体管T12包括第十二沟道CH12、第十二栅极电极G12、第十二源极电极S12和第十二漏极电极D12。

第十二栅极电极G12可以与第六栅极连接电极GCE6形成为一体。

第十二沟道CH12可以在第三方向DR3上与第十二栅极电极G12重叠。

第十二源极电极S12可以布置在第十二沟道CH12的一侧,并可以通过第十一接触孔CT11而连接到第五连接电极CCE5。

第十二漏极电极D12可以布置在第十二沟道CH12的另一侧。

第十三晶体管T13包括第十三沟道CH13、第十三栅极电极G13、第十三源极电极S13和第十三漏极电极D13。

第十三栅极电极G13可以与第三栅极连接电极GCE3形成为一体。

第十三沟道CH13可以在第三方向DR3上与第十三栅极电极G13重叠。

第十三源极电极S13可以布置在第十三沟道CH13的一侧,并且可以通过第二电源接触孔VCT2连接到第一电源水平布线HVDL1。

第十三漏极电极D13可以布置在第十三沟道CH13的另一侧,并且可以通过第三接触孔CT3而连接到第二连接电极CCE2。

第十四晶体管T14包括第十四沟道CH14、第十四栅极电极G14、第十四源极电极S14和第十四漏极电极D14。

第十四栅极电极G14可以与第六栅极连接电极GCE6形成为一体。

第十四沟道CH14可以在第三方向DR3上与第十四栅极电极G14重叠。

第十四源极电极S14布置在第十四沟道CH14的一侧,并可以通过第十一接触孔CT11而连接到第五连接电极CCE5。

第十四漏极电极D14可以布置在第十四沟道CH14的另一侧,并且可以通过第四接触孔CT4而连接到第二连接电极CCE2。

第十五晶体管T15包括第十五沟道CH15、第十五栅极电极G15、第十五源极电极S15和第十五漏极电极D15。

第十五栅极电极G15可以与第五电容器电极CE5形成为一体。

第十五沟道CH15可以在第三方向DR3上与第十五栅极电极G15重叠。

第十五源极电极S15可以布置在第十五沟道CH15的一侧,并可以连接到第八漏极电极D8。

第十五漏极电极D15可以布置在第十五沟道CH15的另一侧,并可以连接到第十七源极电极S17。

第十六晶体管T16可以利用第九子晶体管T161和第十子晶体管T162构成。

第十六晶体管T16的第九子晶体管T161包括第九子沟道CH161、第九子栅极电极G161、第九子源极电极S161和第九子漏极电极D161。

第九子栅极电极G161可以与第三栅极连接电极GCE3形成为一体。

第九子沟道CH161可以在第三方向DR3上与第九子栅极电极G161重叠。

第九子源极电极S161可以布置在第九子沟道CH161的一侧,并且可以通过第十接触孔CT10而连接到第四连接电极CCE4。

第九子漏极电极D161可以布置在第九子沟道CH161的另一侧,并且可以连接到第十子源极电极S162。

第十六晶体管T16的第十子晶体管T162包括第十子沟道CH162、第十子栅极电极G162、第十子源极电极S162和第十子漏极电极D162。

第十子栅极电极G162可以与第三栅极连接电极GCE3形成为一体。

第十子沟道CH162可以在第三方向DR3上与第十子栅极电极G162重叠。

第十子源极电极S162可以布置在第十子沟道CH162的一侧,并且可以连接到第九子漏极电极D161。

第十子漏极电极D162可以布置在第十子沟道CH162的另一侧,并且可以通过第九接触孔CT9连接到初始化电压布线VIL。

第十七晶体管T17包括第十七沟道CH17、第十七栅极电极G17、第十七源极电极S17和第十七漏极电极D17。

第十七栅极电极G17可以与第五栅极连接电极GCE5形成为一体。

第十七沟道CH17可以在第三方向DR3上与第十七栅极电极G17重叠。

第十七源极电极S17可以布置在第十七沟道CH17的一侧,并且可以连接到第十五漏极电极D15。

第十七漏极电极D17可以布置在第十七沟道CH17的另一侧,并且可以通过第十六接触孔CT16而连接到第七连接电极CCE7。

第十八晶体管T18包括第十八沟道CH18、第十八栅极电极G18、第十八源极电极S18和第十八漏极电极D18。

第十八栅极电极G18可以与第三栅极连接电极GCE3形成为一体。

第十八沟道CH18可以在第三方向DR3上与第十八栅极电极G18重叠。

第十八源极电极S18可以布置在第十八沟道CH18的一侧,并且可以通过第九接触孔CT9而连接到初始化电压布线VIL。

第十八漏极电极D18可以布置在第十八沟道CH18的另一侧,并且可以通过第十六接触孔CT16而连接到第七连接电极CCE7。

第十九晶体管T19包括第十九沟道CH19、第十九栅极电极G19、第十九源极电极S19和第十九漏极电极D19。

第十九栅极电极G19可以通过第二十三接触孔CT23而连接到测试信号布线TSTL。

第十九沟道CH19可以在第三方向DR3上与第十九栅极电极G19重叠。

第十九源极电极S19可以布置在第十九沟道CH19的一侧,并且可以通过第二十一接触孔CT21而连接到第八连接电极CCE8。

第十九漏极电极D19可以布置在第十九沟道CH19的另一侧,并且可以通过第二十四接触孔CT24而连接到第三电源辅助布线AVSL。

第一电容器电极CE1可以与第一栅极电极G1形成为一体。

第一连接电极CCE1可以通过第一接触孔CT1而连接到第一栅极电极G1。

第二电容器电极CE2可以在第三方向DR3上与第一栅极电极G1或第一电容器电极CE1重叠。

第二电容器电极CE2可以包括沿第二方向DR2延伸的延伸部EX。第二电容器电极CE2的延伸部EX可以与第k PWM发光布线PWELk和第一电源水平布线HVDL1交叉。

第二电容器电极CE2的延伸部EX可以通过第五接触孔CT5而连接到第k扫频信号布线SWPLk。

可以通过这种第一电容器电极CE1与第二电容器电极CE2之间的重叠区域来配备第一电容器PC1(图12)。

第三电容器电极CE3可以与第八栅极电极G8形成为一体。

第六连接电极CCE6可以通过第十二接触孔CT12而连接到第八栅极电极G8。

第四电容器电极CE4可以在第三方向DR3上与第三电容器电极CE3重叠。

可以通过这种第三电容器电极CE3与第四电容器电极CE4之间的重叠区域来配备第二电容器PC2(图12)。

第五电容器电极CE5可以与第四栅极连接电极GCE4和第十五栅极电极G15形成为一体。

第六电容器电极CE6可以在第三方向DR3上与第五电容器电极CE5重叠。第六电容器电极CE6可以通过第十八接触孔CT18而连接到初始化电压布线VIL。

可以通过这种第五电容器电极CE5与第六电容器电极CE6之间的重叠区域来配备第三电容器PC3(图12)。

第一栅极连接电极GCE1可以与第二栅极电极G2、第三子栅极电极G41、第四子栅极电极G42、第九栅极电极G9、第七子栅极电极G111和第八子栅极电极G112形成为一体,并且可以通过第一栅极接触孔GCT1和第三栅极接触孔GCT3而连接到第k扫描写入布线GWLk。

第二栅极连接电极GCE2可以与第一子栅极电极G31、第二子栅极电极G32、第五子栅极电极G101和第六子栅极电极G102形成为一体,并且可以通过第二栅极接触孔GCT2而连接到第k扫描初始化布线GILk。

第三栅极连接电极GCE3可以与第七栅极电极G7、第十三栅极电极G13、第九子栅极电极G161、第十子栅极电极G162和第十八栅极电极G18形成为一体,并且可以通过第八接触孔CT8而连接到第k扫描控制布线GCLk。

第四栅极连接电极GCE4可以与第五电容器电极CE5及第十五栅极电极G15形成为一体,并可以通过第十七接触孔CT17而连接到第四连接电极CCE4。

第五栅极连接电极GCE5可以与第十七栅极电极G17形成为一体,并且可以通过第十九接触孔CT19而连接到第k PAM发光布线PAELk。

第六栅极连接电极GCE6可以与第五栅极电极G5、第六栅极电极G6、第十二栅极电极G12和第十四栅极电极G14形成为一体,并且可以通过第十四接触孔CT14而连接到第kPWM发光布线PWELk。

第一数据连接电极DCE1可以通过第一数据接触孔DCT1而连接到第二源极电极S2,并可以通过第二数据接触孔DCT2而连接到第j数据布线DLj。

第二数据连接电极DCE2可以通过第三数据接触孔DCT3而连接到第九源极电极S9,并且可以通过第四数据接触孔DCT4而连接到第一PAM数据布线RDL。

第一连接电极CCE1可以沿第二方向DR2延伸。第一连接电极CCE1可以通过第一接触孔CT1而连接到第一栅极电极G1,并且可以通过第二接触孔CT2而连接到第一子源极电极S31和第四子漏极电极D42。

第二连接电极CCE2可以沿第一方向DR1延伸。第二连接电极CCE2可以通过第三接触孔CT3而连接到第十三漏极电极D13,并可以通过第四接触孔CT4而连接到第十四漏极电极D14,并且可以通过第十五接触孔CT15而连接到第四电容器电极CE4。

第四连接电极CCE4可以沿第一方向DR1延伸。第四连接电极CCE4可以通过第十接触孔CT10而连接到第六漏极电极D6和第九子源极电极S161,并且可以通过第十七接触孔CT17而连接到与第十五栅极电极G15形成为一体的第四栅极连接电极GCE4。

第五连接电极CCE5可以沿第一方向DR1延伸。第五连接电极CCE5可以通过第十一接触孔CT11而连接到第十二源极电极S12和第十四源极电极S14。

第六连接电极CCE6可以沿第二方向DR2延伸。第六连接电极CCE6可以通过第十二接触孔CT12而连接到第三电容器电极CE3,并且可以通过第十三接触孔CT13而连接到第五子源极电极S101和第八子漏极电极D112。

第七连接电极CCE7可以通过第十六接触孔CT16而连接到第十七漏极电极D17和第十八漏极电极D18。第七连接电极CCE7可以通过第二十接触孔CT20而连接到第一阳极连接电极ANDE1。

第八连接电极CCE8可以通过第二十一接触孔CT21而连接到第十九源极电极S19,并可以通过第二十二接触孔CT22而连接到第一阳极连接电极ANDE1。

第一阳极连接电极ANDE1可以沿第二方向DR2延伸。第一阳极连接电极ANDE1可以通过第二十接触孔CT20而连接到第七连接电极CCE7,并可以通过第二十二接触孔CT22而连接到第八连接电极CCE8。

第二电源连接电极VDCE可以沿第二方向DR2延伸,并且可以通过第四电源接触孔VCT4而连接到第五连接电极CCE5。

参照图17,第一子像素RP还可以包括第二阳极连接电极ANDE2、阳极电极AND、阴极电极CSD、阳极垫ANDP及阴极垫CSDP。

第二阳极连接电极ANDE2与第一阳极连接电极ANDE1(图16)的一部分重叠。

阳极电极AND与第二阳极连接电极ANDE2重叠,并被阳极垫ANDP覆盖。

阴极电极CSD沿第一方向DR1与阳极电极AND隔开,并且被阴极垫CSDP覆盖。

并且,第二电源布线VDL2可以沿第一方向DR1或第二方向DR2延伸,并在第三方向DR3上与第一晶体管T1至第十八晶体管T18重叠。或者,第二电源布线VSL2可以在第三方向DR3上与第二电源连接电极VDCE的至少一部分重叠。

第三电源布线VSL可以与第二电源布线VDL2隔开,并沿第一方向DR1或第二方向DR2延伸,并且在第三方向DR3上与阴极电极CSD部分重叠。或者,第三电源布线VSL可以在第三方向DR3上与第三电源辅助布线AVSL的至少一部分重叠。

作为一示例,第二电源布线VDL2及第三电源布线VSL可以沿第一方向DR1延伸,并可以沿第二方向DR2彼此隔开。

图18是示出沿图13及图14的F-F'剖切的面的一示例的剖面图。图19是示出沿图13及图14的G-G'剖切的面的一示例的剖面图。图20是示出沿图13及图14的H-H'剖切的面的一示例的剖面图。图21是示出沿图13及图14的I-I'剖切的面的一示例的剖面图。图22是示出沿图13及图14的J-J'剖切的面的一示例的剖面图。图23是示出沿图13及图14的K-K'剖切的面的一示例的剖面图。图24是示出沿图13、图14、图15及图16的L-L'剖切的面的一示例的剖面图。图25是示出沿图13、图14及图15的M-M'剖切的面的一示例的剖面图。图26是示出沿图13及图16的N-N'剖切的面的一示例的剖面图。图27是示出沿图13、图16及图17的O-O'剖切的面的一示例的剖面图。

参照图18至图25,根据一实施例的显示装置10的显示面板100包括基板SUB和布置在基板上的晶体管阵列层TFTL。

而且,参照图26和图27,显示面板100还包括布置在晶体管阵列层TFTL上的发光元件LE。

显示面板100还可以包括布置在晶体管阵列层TFTL与发光元件LE之间的阳极接触电极ANDC和阴极接触电极CSDC。

基板SUB可以利用聚酰亚胺(polyimide)的高分子树脂构成。基板SUB可以是能够进行弯曲(bending)、折叠(folding)、卷曲(rolling)等的柔性(flexible)基板。

如图18至图27所示,晶体管阵列层TFTL包括覆盖基板SUB的第一面上的半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19的栅极绝缘膜130、覆盖栅极绝缘膜130上的第一导电层G1、G2、G31、G32、G41、G42、G5~G9、G101、G102、G111、G112、G12~G15、G161、G162、G17~19、CE1、CE3、CE5、GCE1~GCE5的第一层间绝缘膜141、覆盖第一层间绝缘膜141上的第二导电层CE2、CE4、CE6的第二层间绝缘膜142、覆盖第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8的第一平坦化膜160、覆盖第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE的第二平坦化膜170以及覆盖第二平坦化膜170上的第五导电层VDL2、VSL、ANDE2的第三平坦化膜180。

而且,晶体管阵列层TFTL还可以包括布置在第三平坦化膜180上的第六导电层AND、CSD以及布置在第六导电层AND、CSD的一部分上的第七导电层ANDP、CSDP。

并且,晶体管阵列层TFTL还可以包括覆盖基板SUB的第一面的缓冲膜BF。在这种情况下,半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19和覆盖它们的栅极绝缘膜130布置在缓冲膜BF上。

缓冲膜BF可以利用交替堆叠的多个无机膜构成。例如,缓冲膜BF可以利用硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层及铝氧化物层中的一种以上的无机膜交替堆叠的多膜形成。

缓冲膜BF上的半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19可以包括配备于各子像素的像素驱动部PD的晶体管T1~T19中的每一个的沟道CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、源极电极S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19和漏极电极D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19。

半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19可以包括多晶硅、单晶硅、低温多晶硅、非晶硅或氧化物半导体。

半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19中除晶体管T1~T19中的每一个的沟道CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19之外的剩余半导体层可以是在硅半导体或氧化物半导体中掺杂离子或杂质而具有导电性的区域。

覆盖缓冲膜BF上的半导体层CH1、CH2、CH31、CH32、CH41、CH42、CH5~CH9、CH101、CH102、CH111、CH112、CH12~CH15、CH161、CH162、CH17~CH19、S1、S2、S31、S32、S41、S42、S5~S9、S101、S102、S111、S112、S12~S15、S161、S162、S17~S19、D1、D2、D31、D32、D41、D42、D5~D9、D101、D102、D111、D112、D12~D15、D161、D162、D17~D19的栅极绝缘膜130可以利用无机膜(例如,硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或铝氧化物层)形成。栅极绝缘膜130可以被称为第一绝缘膜。

栅极绝缘膜130上的第一导电层G1、G2、G31、G32、G41、G42、G5~G9、G101、G102、G111、G112、G12~G15、G161、G162、G17~G19、CE1、CE3、CE5、GCE1~GCE5可以包括配备于各子像素的像素驱动部PD的晶体管T1~T19的各个栅极电极G1、G2、G31、G32、G41、G42、G5~G9、G101、G102、G111、G112、G12~G15、G161、G162、G17~G19、第一栅极连接电极GCE1至第五栅极连接电极GCE5、第一电容器电极CE1、第三电容器电极CE3和第五电容器电极CE5。

栅极绝缘膜130上的第一导电层G1、G2、G31、G32、G41、G42、G5~G9、G101、G102、G111、G112、G12~G15、G161、G162、G17~G19、CE1、CE3、CE5、GCE1~GCE5可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金构成的单层或多层。

覆盖栅极绝缘膜130上的第一导电层G1、G2、G31、G32、G41、G42、G5~G9、G101、G102、G111、G112、G12~G15、G161、G162、G17~G19、CE1、CE3、CE5、GCE1~GCE5的第一层间绝缘膜141可以利用无机膜(例如,硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或铝氧化物层)形成。第一层间绝缘膜141可以被称为第二绝缘膜。

第一层间绝缘膜141上的第二导电层CE2、CE4、CE6可以包括第二电容器电极CE2、第四电容器电极CE4和第六电容器电极CE6。

第二电容器电极CE2在第三方向DR3上以将第一层间绝缘膜141置于之间的状态与第一电容器电极CE1重叠,从而可以配备第一电容器PC1。

第四电容器电极CE4在第三方向DR3上以将第一层间绝缘膜141置于之间的状态与第三电容器电极CE3重叠,从而可以配备第二电容器PC2。

第六电容器电极CE6在第三方向DR3上以将第一层间绝缘膜141置于之间的状态与第五电容器电极CE5重叠,从而可以配备第三电容器PC3。

第一层间绝缘膜141上的第二导电层CE2、CE4、CE6可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金形成的单层或多层。

覆盖第一层间绝缘膜141上的第二导电层CE2、CE4、CE6的第二层间绝缘膜142可以利用无机膜(例如,硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或铝氧化物层)形成。第二层间绝缘膜142可以被称为第三绝缘膜。

第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8可以包括沿第一方向DR1延伸的栅极布线,即,初始化电压布线VIL、第k扫描初始化布线GILk、第k扫描写入布线GWLk、第k PWM发光布线PWELk、第k扫频信号布线SWPLk、第k扫描控制布线GCLk以及第k PAM发光布线PAELk。

并且,第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8还可以包括沿第一方向DR1延伸的第一栅极电压辅助布线GVAL1、第一电源水平布线HVDL1、测试信号布线TSTL及第三电源辅助布线AVSL。

并且,第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8还可以包括第一数据连接电极DCE1、第二数据连接电极DCE2和第一连接电极CCE1至第八连接电极CCE8。

第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金构成的单层或多层。

如图18所示,第k扫描写入布线GWLk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第一栅极接触孔GCT1而连接到与第一栅极连接电极GCE1形成为一体的第四子栅极电极G42。

如图22所示,第k扫描写入布线GWLk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第三栅极接触孔GCT3而连接到与第一栅极连接电极GCE1形成为一体的第八子栅极电极G112。

如上所述,第一栅极连接电极GCE1与第二栅极电极G2、第三子栅极电极G41、第四子栅极电极G42、第九栅极电极G9、第七子栅极电极G111和第八子栅极电极G112形成为一体。由此,如图12所示,第二晶体管T2、第四晶体管T4的第三子晶体管T41及第四子晶体管T42、第九晶体管T9、第十一晶体管T11的第七子晶体管T111及第八子晶体管T112可以基于第k扫描写入布线GWLk的扫描写入信号而导通。

如图19所示,第k扫描初始化布线GILk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第二栅极接触孔GCT2而连接到第二栅极连接电极GCE2。在此,第二栅极连接电极GCE2与第一子栅极电极G31、第二子栅极电极G32、第五子栅极电极G101和第六子栅极电极G102形成为一体。由此,如图12所示,第三晶体管T3的第一子晶体管T31和第二子晶体管T32以及第十晶体管T10的第五子晶体管T101和第六子晶体管T102可以基于第k扫描初始化布线GILk的扫描初始化信号而导通。

如图25所示,第k PWM发光布线PWELk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第十四接触孔CT14而连接到第六栅极连接电极GCE6。在此,第六栅极连接电极GCE6与第五栅极电极G5、第六栅极电极G6、第十二栅极电极G12和第十四栅极电极G14形成为一体。由此,如图12所示,第五晶体管T5、第六晶体管T6、第十二晶体管T12及第十四晶体管T14可以基于第k PWM发光布线PWELk的PWM发光信号而导通。

如图21所示,第k扫描控制布线GCLk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第八接触孔CT8连接到第三栅极连接电极GCE3。在此,第三栅极连接电极GCE3与第七栅极电极G7、第十三栅极电极G13、第九子栅极电极G161、第十子栅极电极G162及第十八栅极电极G18形成为一体。由此,如图12所示,第七晶体管T7、第十三晶体管T13、第十六晶体管T16的第九子晶体管T161、第十子晶体管T162及第十八晶体管T18可以基于第k扫描控制布线GCLk的扫描控制信号而导通。

如图25所示,第k PAM发光布线PAELk可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第十九接触孔CT19而连接到第五栅极连接电极GCE5。第五栅极连接电极GCE5与第十七栅极电极G17形成为一体。由此,如图12所示,第十七晶体管T17可以基于第kPAM发光布线PAELk的PAM发光信号而导通。

如图19所示,初始化电压布线VIL可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第一电源接触孔VCT1而连接到第二子漏极电极D32。在此,第二子漏极电极D32与第六子漏极电极D102形成为一体。

如图21所示,初始化电压布线VIL可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第九接触孔CT9而连接到第十子漏极电极D162和第十八漏极电极D18。

如图25所示,初始化电压布线VIL可以通过贯通第二层间绝缘膜142的第十八接触孔CT18而连接到第六电容器电极CE6。

由此,如图12所示,第三晶体管T3、第十六晶体管T16、第三电容器PC3及第十八晶体管T18可以与供应初始化电压的初始化电压布线VIL连接。

如图20所示,第一电源水平布线HVDL1可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第二电源接触孔VCT2而连接到第五源极电极S5和第十三源极电极S13。由此,如图12所示,第五晶体管T5及第十三晶体管T13可以通过第一电源水平布线HVDL1而连接到供应第一电源VDD1的第一电源布线VDL1。

如图21所示,第一栅极电压辅助布线GVAL1可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第七接触孔CT7而连接到第七源极电极S7。由此,如图12所示,第七晶体管T7可以通过第一栅极电压辅助布线GVAL1接收第一栅极电平电压。

如图26所示,测试信号布线TSTL可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第二十三接触孔CT23而连接到第十九栅极电极G19。由此,如图12所示,第十九晶体管T19可以基于测试信号布线TSTL的测试信号而导通。

并且,第三电源辅助布线AVSL可以通过贯通栅极绝缘膜130、第一层间绝缘膜141及第二层间绝缘膜142的第二十四接触孔CT24而连接到第十九漏极电极D19。由此,第十九晶体管T19可以通过第三电源辅助布线AVSL接收第三电源VSS。

如图18所示,第一数据连接电极DCE1可以通过贯通栅极绝缘膜130、第一层间绝缘膜141及第二层间绝缘膜142的第一数据接触孔DCT1而连接到第二源极电极S2。

如图22所示,第二数据连接电极DCE2可以通过贯通栅极绝缘膜130、第一层间绝缘膜141以及第二层间绝缘膜142的第三数据接触孔DCT3而连接到第九源极电极S9。

如图19所示,第一连接电极CCE1可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第一接触孔CT1而连接到第一栅极电极G1。而且,第一连接电极CCE1可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第二接触孔CT2而连接到第一子源极电极S31和第四子漏极电极D42。由此,如图12所示,第一晶体管T1的栅极电极G1可以连接到第三晶体管T3和第四晶体管T4。

如图20所示,第二连接电极CCE2的一侧可以通过贯通栅极绝缘膜130、第一层间绝缘膜141以及第二层间绝缘膜142的第三接触孔CT3而连接到第十三漏极电极D13。

如图24所示,第二连接电极CCE2的一部分可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第四接触孔CT4而连接到第十四漏极电极D14。而且,第二连接电极CCE2的另一侧可以通过贯通第二层间绝缘膜142的第十五接触孔CT15而连接到第四电容器电极CE4。

由此,如图12所示,可以配备有使第十三晶体管T13、第十四晶体管T14和第二电容器PC2彼此连接的第二节点N2。

如图21所示,第四连接电极CCE4可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第十接触孔CT10而连接到第十六漏极电极D16。

并且,如图25所示,第四连接电极CCE4可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第十七接触孔CT17而连接到第四栅极连接电极GCE4。在此,第四栅极连接电极GCE4与第五电容器电极CE5和第十五栅极电极G15形成为一体。

由此,如图12所示,可以配备有使第十六晶体管T16、第三电容器PC3和第十五晶体管T15彼此连接的第三节点N3。

如图14和图23所示,第五连接电极CCE5可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第十一接触孔CT11而连接到第十二源极电极S12。在此,第十二源极电极S12配备为与第十四源极电极S14相连的图案。

如图23所示,第六连接电极CCE6可以通过贯通第一层间绝缘膜141和第二层间绝缘膜142的第十二接触孔CT12而连接到第三电容器电极CE3。在此,第三电容器电极CE3与第八栅极电极G8形成为一体。

而且,第六连接电极CCE6可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第十三接触孔CT13而连接到第五子源极电极S101和第八子漏极电极D112。在此,第五子源极电极S101和第八子漏极电极D112配备为彼此连接的图案。

由此,如图12所示,第二电容器PC2、第八晶体管T8的栅极电极G8、第十晶体管T10和第十一晶体管T11可以彼此连接。

如图15和图24所示,第七连接电极CCE7可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第十六接触孔CT16而连接到第十七漏极电极D17和第十八漏极电极D18。在此,第十七漏极电极D17和第十八漏极电极D18配备为彼此连接的图案。

由此,如图12所示,第十七晶体管T17和第十八晶体管T18可以彼此连接。

如图26所示,第八连接电极CCE8可以通过贯通栅极绝缘膜130、第一层间绝缘膜141和第二层间绝缘膜142的第二十一接触孔CT21而连接到第十九源极电极S19。

覆盖第二层间绝缘膜142上的第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1~CCE8的第一平坦化膜160可以利用丙烯酸树脂(acryl resin)、环氧树脂(epoxy resin)、酚醛树脂(phenolic resin)、聚酰胺树脂(polyamide resin)、聚酰亚胺树脂(polyimide resin)等有机膜形成。第一平坦化膜160可以被称为第四绝缘膜。

第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE可以包括第j数据布线DLj、第一电源垂直布线VVDL1和第一PAM数据布线RDL。

并且,第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE还可以包括第一阳极连接电极ANDE1和第二电源连接电极VDCE。

第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金形成的单层或多层。

如图18所示,第j数据布线DLj可以通过贯通第一平坦化膜160的第二数据接触孔DCT2而连接到第一数据连接电极DCE1。第一数据连接电极DCE1可以通过第一数据接触孔DCT1而连接到第二源极电极S2。由此,如图12所示,第二晶体管T2可以与第j数据布线DLj连接。

如图22所示,第一PAM数据布线RDL可以通过贯通第一平坦化膜160的第四数据接触孔DCT4而连接到第二数据连接电极DCE2。第二数据连接电极DCE2可以通过第三数据接触孔DCT3而连接到第九源极电极S9。由此,如图12所示,第九晶体管T9可以连接到第一PAM数据布线RDL。

如图20所示,第一电源垂直布线VVDL1可以通过贯通第一平坦化膜160的第三电源接触孔VCT3而连接到第一电源水平布线HVDL1。第一电源水平布线HVDL1可以通过第二电源接触孔VCT2而连接到第五源极电极S5和第十三源极电极S13。由此,如图12所示,第五晶体管T5及第十三晶体管T13可以连接到第一电源布线VDL1。

在此,第三电源接触孔VCT3可以在第三方向DR3上与第二电源接触孔VCT2重叠。作为一示例,第三电源接触孔VCT3的面积可以大于第二电源接触孔VCT2的面积。

如图26所示,第一阳极连接电极ANDE1可以通过贯通第一平坦化膜160的第二十接触孔CT20而连接到第七连接电极CCE7。第七连接电极CCE7可以通过第十六接触孔CT16(参照图24)而连接到第十七漏极电极D17。如图15所示,第十七漏极电极D17可以配备为连接到第十八漏极电极D18的图案。

并且,第一阳极连接电极ANDE1可以通过贯通第一平坦化膜160的第二十二接触孔CT22而连接到第八连接电极CCE8。第八连接电极CCE8可以通过第二十一接触孔CT21而连接到第十九源极电极S19。

由此,如图12所示,第十七晶体管T17、第十八晶体管T18、第十九晶体管T19可以相互连接。

如图22所示,第二电源连接电极VDCE可以通过贯通第一平坦化膜160的第四电源接触孔VCT4而连接到第五连接电极CCE5。如图14所示,第五连接电极CCE5可以通过第十一接触孔CT11而连接到第十二源极电极S12和第十四源极电极S14。

因此,如图12所示,第十二晶体管T12和第十四晶体管T14可以彼此连接。

覆盖第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE的第二平坦化膜170可以利用丙烯酸树脂(acryl resin)、环氧树脂(epoxy resin)、酚醛树脂(phenolicresin)、聚酰胺树脂(polyamide resin)、聚酰亚胺树脂(polyimide resin)等有机膜形成。第二平坦化膜170可以被称为第五绝缘膜。

第二平坦化膜170上的第五导电层VDL2、VSL、ANDE2可以包括第二电源布线VDL2、第三电源布线VSL及第二阳极连接电极ANDE2。

如图23所示,第二电源布线VDL2可以通过贯通第二平坦化膜170的第五电源接触孔VCT5而连接到第二电源连接电极VDCE。第二电源连接电极VDCE可以通过第四电源接触孔VCT4而连接到第五连接电极CCE5,第五连接电极CCE5可以通过第十一接触孔CT11而连接到第十二源极电极S12和第十四源极电极S14。

由此,如图12所示,第十二晶体管T12及第十四晶体管T14可以连接到第二电源布线VDL2。

此外,虽然未单独示出,但是第三电源布线VSL可以利用与第二电源布线VDL2同一层的第二平坦化膜170上的第五导电层构成。在这种情况下,第三电源布线VSL可以在与第二电源布线VDL2相同的方向上延伸,并与第二电源布线VDL2隔开。

并且,虽然未单独示出,但第三电源布线VSL可以通过贯通第二平坦化膜170的孔(未图示)而连接到第三电源辅助布线AVSL。第三电源辅助布线AVSL可以通过第二十四接触孔CT24而连接到第十九漏极电极D19。由此,如图12所示,第十九晶体管T19可以连接到第三电源布线VSL。

并且,虽然未单独示出,但考虑到用于容易实现第二电源布线VDL2与第三电源布线VSL之间的绝缘的布局,第三电源布线VSL也可以利用第三平坦化膜180上的第六导电层构成,而不是利用第二平坦化膜170上的第五导电层构成。

如图26所示,第二阳极连接电极ANDE2可以通过贯通第二平坦化膜170的孔而连接到第一阳极连接电极ANDE1。

第二平坦化膜170上的第五导电层VDL2、VSL、ANDE2可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金构成的单层或多层。

覆盖第二平坦化膜170上的第五导电层VDL2、VSL、ANDE2的第三平坦化膜180可以利用丙烯酸树脂(acryl resin)、环氧树脂(epoxy resin)、酚醛树脂(phenolic resin)、聚酰胺树脂(polyamide resin)、聚酰亚胺树脂(polyimide resin)等有机膜形成。第三平坦化膜180可以被称为第五绝缘膜。

第三平坦化膜180上的第六导电层AND、CSD可以包括多个子像素RP、GP、BP中的每一个的阳极电极AND和阴极电极CSD。

在多个子像素RP、GP、BP中的每一个中,阳极电极AND和阴极电极CSD可以彼此隔开。

如图26所示,阳极电极AND可以通过贯通第三平坦化膜180的孔而连接到第二阳极连接电极ANDE2。第二阳极连接电极ANDE2可以通过贯通第二平坦化膜170的孔而连接到第一阳极连接电极ANDE1,第一阳极连接电极ANDE1可以通过第二十接触孔CT20而连接到第七连接电极CCE7。如图24所示,第七连接电极CCE7可以通过第十六接触孔CT16而连接到第十七漏极电极D17和第十八漏极电极D18。由此,如图12所示,发光元件LE可以连接到第十七晶体管T17和第十八晶体管T18。

尽管未单独示出,但是在第一方向DR1上相邻的子像素的阴极电极CSD可以彼此连接。作为一示例,构成一个像素PX并沿一方向并排排列的子像素RP、GP、BP的阴极电极CSD可以利用彼此连接的图案构成。

而且,在第三电源布线VSL利用第二平坦化膜170上的第五导电层构成的情况下,阴极电极CSD可以通过贯通第三平坦化膜180的孔而连接到第三电源布线VSL。或者,在第三电源布线VSL利用第三平坦化膜180上的第六导电层构成的情况下,阴极电极CSD可以配备为与第三电源布线VSL连接的图案。

第三平坦化膜180上的第六导电层AND、CSD可以形成为利用钼(Mo)、铝(Al)、铬(Cr)、金(Au)、钛(Ti)、镍(Ni)、钕(Nd)及铜(Cu)中的一种或它们的合金形成的单层或多层。作为一示例,第六导电层可以包括诸如铝和钛的堆叠结构(Ti/Al/Ti)、铝和ITO的堆叠结构(ITO/Al/ITO)、APC合金以及APC合金和ITO的堆叠结构(ITO/APC/ITO)之类的反射率高的金属物质。作为另一示例,第六导电层可以利用Al/Ti的双层结构构成。

在第六导电层AND、CSD中的一部分上的第七导电层ANDP、CSDP可以包括覆盖阳极电极AND的阳极垫ANDP和覆盖阴极电极CSD的阴极垫CSDP。

第七导电层ANDP、CSDP可以利用诸如ITO及IZO等之类的透明导电性物质(TCO:Transparent Conductive Material)构成。

如上所述,借由利用第七导电层ANDP、CSDP构成的阳极垫ANDP及阴极垫CSDP,能够更加坚固地固定发光元件LE,并能够防止阳极电极AND及阴极电极CSD的腐蚀或损伤。

此外,晶体管阵列层TFTL还可以包括布置在第三平坦化膜180上并且覆盖阳极垫ANDP的边缘中的至少一部分和阴极垫CSDP的边缘中的至少一部分的保护膜PAS。

作为一示例,保护膜PAS可以覆盖阳极垫ANDP的边缘中除了与阴极垫CSDP面对的一部分之外的剩余部分。而且,保护膜PAS可以覆盖阴极垫CSDP的边缘中除了与阳极垫ANDP面对的一部分之外的剩余部分。即,保护膜PAS可以对应于发光元件LE的周围。

保护膜PAS可以利用硅氮化物层、硅氮氧化物层、硅氧化物层、钛氧化物层或铝氧化物层形成。

阳极垫ANDP可以通过阳极接触电极ANDC而连接到发光元件LE的第一接触电极CTE1。

阴极垫CSDP可以通过阴极接触电极CSDC而连接到发光元件LE的第二接触电极CTE2。

阳极接触电极ANDC及阴极接触电极CSDC可以利用导电性粘合物质构成。

关于发光元件LE,上面结合图10进行了说明,因此省略重复说明。

另外,如上所述,一实施例的显示装置10为了降低连接部SM(图1)的可识别性,可以包括与基板SUB的边缘邻近布置的像素PX。此时,与基板SUB的边缘邻近布置的像素PX相对强烈地暴露于外部静电,从而容易被损坏。为了防止这种情况,根据一实施例的显示装置10还可以包括防静电图案。

图28是示出根据一实施例的显示装置的显示面板的布局图。图29是示出关于图28的P区域的一示例的布局图。

图30是示出针对布置在图29的Q区域中的第三导电层和第四导电层的一示例的布局图。图31是示出针对布置在图29的Q区域中的第三导电层、第四导电层、第五导电层和第六导电层的一示例的布局图。图32是示出针对布置在图29的Q区域中的第三导电层、第四导电层、第五导电层、第六导电层和第七导电层的一示例的布局图。

在图28和图29中,为了便于图示和说明,选择了显示面板100中的一部分构成要素,并且变形了所选择的构成要素的布置形态、尺寸和数量等而图示,并且一实施例的显示面板100不限于图28和图29的图示。

参照图28,一实施例的显示装置10的显示面板100包括:基板SUB,包含排列多个子像素RP、GP、BP的显示区域DA和作为显示区域DA的周围的非显示区域NDA;晶体管阵列层TFTL,布置在基板SUB的第一面上;以及多个发光元件LE,布置在晶体管阵列层TFTL上的显示区域DA中并且分别对应于多个子像素RP、GP、BP。

晶体管阵列层TFTL包括:多个像素驱动部PD_RP、PD_GP、PD_BP,布置在利用显示区域DA的一部分构成的电路区域CCA中,分别对应于多个子像素RP、GP、BP且分别包括至少一个晶体管;两个以上的栅极驱动部GDR,布置在电路区域CCA中,沿一方向(例如,第一方向DR1)彼此隔开并且向连接到多个像素驱动部PD_RP、PD_GP、PD_BP的栅极布线GL供应各自的信号;第一栅极电压供应布线GVPL1,布置在显示区域DA中的电路区域CCA的周围的一部分,并且沿一方向(例如,第一方向DR1)延伸;以及两条以上的第一栅极电压辅助布线GVAL1,沿与一方向(例如,第一方向DR1)交叉的另一方向(例如,第二方向DR2)延伸并且连接在两个以上的栅极驱动部GDR中的每一个与第一栅极电压供应布线GVPL1之间。

参照图29及图30,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1通过至少一个第一栅极电压布线接触孔GVLH1而连接到第一栅极电压供应布线GVPL1。即,两条以上的第一栅极电压辅助布线GVAL1可以布置在与第一栅极电压供应布线GVPL1不同的层,并且可以通过贯通两条以上的第一栅极电压辅助布线GVAL1与第一栅极电压供应布线GVPL1之间的绝缘膜的至少一个第一栅极电压布线接触孔GVLH1而连接到第一栅极电压供应布线GVPL1。

参照图30,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1比第一栅极电压供应布线GVPL1更远离基板SUB的与第一栅极电压供应布线GVPL1邻近的边缘。

即,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1可以以预定的第一间隔SD1与基板SUB的边缘隔开,并且第一栅极电压供应布线GVPL1可以以小于第一间隔SD1的第二间隔SD2与基板SUB的边缘隔开。

换言之,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1以到达用于与第一栅极电压供应布线GVPL1连接的至少一个第一栅极电压布线接触孔CVLH1的宽度延伸,并且不延伸超过第一栅极电压供应布线GVPL1以进一步邻近于基板SUB的边缘。

由此,可以防止布置于基板SUB的边缘的布线之间的短路不良。

而且,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1可以像第一栅极电压供应布线GVPL1一样沿第一方向DR1延伸,并且可以与第一栅极电压供应布线GVPL1重叠。

如此,由于两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1与第一栅极电压供应布线GVPL1之间的重叠区域可以增加,因此可以配备为彼此隔开的两个以上的第一栅极电压布线接触孔GVLH1。如上所述,通过增加第一栅极电压布线接触孔GVLH1的数量,可以降低两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1与第一栅极电压供应布线GVPL1之间的电连接的电阻。

如图28、图29和图30所示,根据一实施例的显示装置10的显示面板100的晶体管阵列层TFTL还可以包括布置在显示区域DA中的电路区域CCA周围的第二栅极电压供应布线GVPL2以及分别连接在两个以上的栅极驱动部GDR与第二栅极电压供应布线GVPL1之间的两条以上的第二栅极电压辅助布线GVAL2。

第二栅极电压供应布线GVPL2布置在显示区域DA中的电路区域CCA的周围,并且沿一方向(例如,第一方向DR1)延伸。即,第二栅极电压供应布线GVPL2可以与第一栅极电压供应布线GVPL1平行地布置。

而且,第二栅极电压供应布线GVPL2可以比第一栅极电压供应布线GVPL1更远离基板SUB的边缘。即,第一栅极电压供应布线GVPL1和第二栅极电压供应布线GVPL2中的第一栅极电压供应布线GVPL1布置为更邻近于基板SUB的边缘。

两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2通过至少一个第二栅极电压布线接触孔GVLH2而连接到第二栅极电压供应布线GVPL2。

在此,与两条以上的第一栅极电压辅助布线GVAL1不同地,两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2可以比第二栅极电压供应布线GVPL2更邻近于邻近的基板SUB的与第一栅极电压供应布线GVPL1的边缘。

即,两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2可以以大于第一间隔SD1的第三间隔SD3与基板SUB的边缘隔开。而且,第二栅极电压供应布线GVPL2可以以大于第三间隔SD3的第四间隔SD4与基板SUB的边缘隔开。

这是因为,由于第二栅极电压供应布线GVPL2比第一栅极电压供应布线GVPL1更远离基板SUB的边缘,因此两条以上的第二栅极电压辅助布线GVAL2发生短路不良的可能性相对较低。据此,两条以上的第二栅极电压辅助布线GVAL2可以以完全覆盖第二栅极电压供应布线GVPL2的宽度布置,因此,由于连接不良而导致的对齐误差可能增加,从而使制造工艺变得容易。

而且,两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2可以像第二栅极电压供应布线GVPL2一样沿第一方向DR1延伸,并且可以与第二栅极电压供应布线GVPL2重叠。

如此,由于两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2与第二栅极电压供应布线GVPL2之间的重叠区域可以增加,因此可以配备彼此隔开的两个以上的第二栅极电压布线接触孔GVLH2。如上所述,通过增加第二栅极电压布线接触孔GVLH2的数量,可以降低两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2与第二栅极电压供应布线GVPL2之间的电连接的电阻。

如图28和图29所示,根据一实施例的显示装置10的显示面板100包括排列在显示区域DA中的多个像素PX。多个像素PX中的每一个可以利用沿第一方向DR1或第二方向DR2相邻的子像素RP、GP、BP构成。

由于显示区域DA包括利用中心的一部分构成的电路区域CCA,因此多个像素PX中的一部分像素PX可以布置在显示区域DA的电路区域CCA中,并且剩余一部分可以布置在与基板SUB的边缘邻近的电路区域CCA的周围。即,多个子像素RP、GP、BP的阳极电极AND和阴极电极CSD可以排列在显示区域DA中,相反,多个子像素RP、GP、DP的像素驱动部PD_RP、PD_GP、PD_BP可以限制性地布置在电路区域CCA中。

换言之,与布置在电路区域CCA中的像素PX对应的子像素RP、GP、BP中的每一个的发光元件LE可以布置为沿第一方向DR1或第二方向DR2与各自的像素驱动部PD_RP、PD_GP、PD_BP邻近。

相反,尽管未单独示出,但是与布置在电路区域CCA周围的像素PX对应的子像素RP、GP、BP的发光元件LE可以连接到布置在电路区域CCA中的各自的像素驱动部PD_RP、PD_GP、PD_BP。为此,布置在电路区域CCA周围的子像素RP、GP、BP的第一阳极连接电极ANDE1或第二阳极连接电极ANDE2可以从电路区域CCA向电路区域CCA周围延伸。

作为一示例,如图30所示,布置在电路区域CCA周围的子像素RP、GP、BP的第一阳极连接电极ANDE1可以从电路区域CCA沿第二方向DR2延伸至显示区域DA的边缘。

上面已经结合图12至图27说明了图27中所示的多个子像素RP、GP、BP的像素驱动部PD_RP、PD_GP、PD_BP,因此省略重复的说明。

如图28所示,两个以上的栅极驱动部GDR可以划分在电路区域CCA中的未布置多个子像素RP、GP、BP的像素驱动部PD_RP、PD_GP、PD_BP的一部分区域中而布置。在这种情况下,可以防止非显示区域NDA的宽度因布置栅极驱动部GDR而变大。

两个以上的栅极驱动部GDR中的每一个可以包括第一扫描信号驱动部SCDR1(图11)、第二扫描信号驱动部SCDR2(图11)、扫频信号驱动部SWDR(图11)和发光信号输出部EMDR(图11)中的至少一个。例如,两个以上的栅极驱动部GDR中的每一个可以包括第一扫描信号驱动部SCDR1(图11)、第二扫描信号驱动部SCDR2(图11)、扫频信号驱动部SWDR(图11)和发光信号输出部EMDR(图11)。

或者,两个以上的栅极驱动部GDR中的每一个可以利用第一扫描信号驱动部SCDR1(图11)、第二扫描信号驱动部SCDR2(图11)、扫频信号驱动部SWDR(图11)和发光信号输出部EMDR(图11)中的一个形成。

然而,这仅是示例性的,根据一实施例,除了两个以上的栅极驱动部GDR划分在电路区域CCA中而布置并且向多条栅极布线GL供应各自的信号之外,两个以上的栅极驱动部GDR可以变形为任何形态。由于已经结合图11和图12等说明了多条栅极布线GL,因此省略其重复的说明。

为了降低瓦片形显示装置TD(图1)中连接部SM(图1)的可识别性,各显示装置10的非显示区域NDA可以以小于像素PX之间的隔开距离的宽度构成。

如图28所示,非显示区域NDA可以包括与显示区域DA的第二方向DR2的一侧邻近的第一垫区域PDA1和与显示区域DA的第二方向DR2的另一侧邻近的第二垫区域PDA2。

晶体管阵列层TFTL还可以包括布置在第一垫区域PDA1和第二垫区域PDA2中的垫。

作为一示例,第一垫区域PDA1的垫可以通过侧面布线SSL(图5)及连接布线CCL而布置于基板SUB的第二面下方,并连接到安装有向数据布线DL供应各自的信号的源极驱动部200(图11)的集成电路芯片的柔性膜。在此,安装有源极驱动部200(图11)的集成电路芯片的柔性膜可以与第一垫区域PDA1邻近地布置。

第一垫区域PDA1的垫可以通过数据垫布线DPL而分别连接到数据布线DL。数据垫布线DPL可以布置在显示区域DA中的电路区域CCA的周围。

而且,第二垫区域PDA2的垫可以通过侧面布线SSL(图5)及连接布线CCL而布置于基板SUB的第二面下方,并连接到安装有供应各种电压的电源供应部400(图11)的集成电路芯片的柔性膜。

电源供应部400可以输出与第一子像素RP对应的第一PAM数据电压、与第二子像素GP对应的第二PAM数据电压、与第三子像素BP对应的第三PAM数据电压、第一电源电压VDD1、第二电源电压VDD2、第三电源电压VSS、初始化电压VI以及栅极电平电压VGL、VGH。

在此,安装有电源供应部400的集成电路芯片的柔性膜可以与第二垫区域PDA2邻近地布置。

第二垫区域PDA2的垫可以包括通过第一电源连接布线VDCL1而连接到第一电源布线VDL1的垫、通过控制信号供应布线CSPL而连接到两个以上的栅极驱动部GDR的垫、连接到第一栅极电压供应布线GVPL1的垫以及连接到第二栅极电压供应布线GVPL2的垫。

而且,虽然未图示,第二垫区域PDA2的垫还可以包括连接到第二电源布线VDL2的垫。

第一电源连接布线VDCL1及控制信号供应布线CSPL可以布置在显示区域DA中的电路区域CCA的周围。

第一栅极电压供应布线GVPL1可以连接到布置在第二垫区域PDA2中的至少一个垫。

由此,第一栅极电压供应布线GVPL1和连接到第一栅极电压供应布线GVPL1的两条以上的第一栅极电压辅助布线GVAL1可以将从电源供应部400供应的预定的第一栅极电平电压(例如,图11的VGH)传输到两个以上的栅极驱动部GDR。

并且,第一栅极电压辅助布线GVAL1还可以连接到布置在电路区域CCA中的多个子像素RP、GP、BP的像素驱动部PD_RP、PD_GP、PD_BP。

第一栅极电压供应布线GVPL1和与第一栅极电压供应布线GVPL1连接的两条以上的第一栅极电压辅助布线GVAL1可以将从电源供应部400(图11)供应的预定的第一栅极电平电压(例如,图11的VGH)传输到两个以上的栅极驱动部GDR。此外,两条以上的第一栅极电压辅助布线GVAL1还可以连接到多个子像素RP、GP、BP的像素驱动部PD_RP、PD_GP、PD_BP,以传输预定的第一栅极电平电压(例如,图11的VGH)。

而且,第二栅极电压供应布线GVPL2和与第二栅极电压供应布线GVPL2连接的两条以上的第二栅极电压辅助布线GVAL2可以向两个以上的栅极驱动部GDR传输从电源供应部400(图11)供应并且具有与第一栅极电平电压不同的电压电平的第二栅极电平电压(例如,图11的VGL)。例如,第二栅极电平电压可以具有低于第一栅极电平电压的电压电平。

参照图31,根据一实施例的显示装置10的显示面板100的晶体管阵列层TFTL还可以包括布置在覆盖包括第一栅极电压供应布线GVPL1和第二栅极电压供应布线GVPL2等的第四导电层的第二平坦化膜170上的第五导电层。

第二平坦化膜170上的第五导电层可以包括第三电源布线VSL以及多个子像素RP、GP、BP各自的第二阳极连接电极ANDE2_RP、ANDE2_GP、ANDE2_BP。

第三电源布线VSL与多个子像素RP、GP、BP各自的第二阳极连接电极ANDE2_RP、ANDE2_GP、ANDE2_BP隔开。

并且,第五导电层还可以包括与第三电源布线VSL及第二阳极连接电极ANDE2_RP、ANDE2_GP、ANDE2_BP隔开的第二电源布线VDL2(图17)。

根据一实施例的显示装置10的显示面板100的晶体管阵列层TFTL还可以包括布置在覆盖第五导电层的第三平坦化膜180上的第六导电层,其中,所述第五导电层包括第三电源布线VSL和多个子像素RP、GP、BP中的各自的第二阳极连接电极ANDE2_RP、ANDE2_GP、ANDE2_BP等。

第三平坦化膜180上的第六导电层可以包括多个子像素RP、GP、BP各自的阳极电极AND_RP、AND_GP、AND_BP以及阴极电极CSD_RP、CSD_GP、CSD_BP。

而且,第六导电层还可以包括阴极垂直图案CSVP和阴极水平图案CSHP。

阴极垂直图案CSVP布置在构成各像素PX的子像素RP、GP、BP之间以及各像素PX在第一方向DR1上的两侧,并且沿第二方向DR2延伸。

阴极水平图案CSHP连接到构成各像素PX的子像素RP、GP、BP的阴极电极CSD_RP、CSD_GP、CSD_BP以及阴极垂直图案CSVP,并且沿第一方向DR1延伸。

如图32所示,根据一实施例的显示装置10的显示面板100的晶体管阵列层TFTL还可以包括布置在包含阳极电极AND_RP、AND_GP、AND_BP和阴极电极CSD_RP、CSD_GP、CSD_BP等的第六导电层的一部分以及第三平坦化膜180上的第七导电层。

第七导电层可以包括多个子像素RP、GP、BP各自的阳极垫ANDP_RP、ANDP_GP、ANDP_BP以及阴极垫CSDP_RP、CSDP_GP、CSDP_BP。

根据一实施例的显示装置10的显示面板100还可以包括布置在基板SUB的第一面中的非显示区域NDA的一部分并且利用第七导电层构成的防静电图案ESDP。

防静电图案ESDP可以包括与显示区域DA的边缘平行地布置的主图案ESDM和从主图案ESDM向显示区域DA侧突出的多个子图案ESDS。

多个子图案ESDS可以分别布置于多个像素PX中的与主图案ESDM相邻的像素之间。

由于这种防静电图案ESDP,可以防止外部静电的流入,因此可以防止与基板SUB的边缘邻近地布置而可能受到静电的相对大的影响的子像素RP、GP、BP的像素驱动部PD_RP、PD_GP、PD_BP或发光元件LE的损坏。

分别布置在多个像素PX中的与主图案ESDM相邻的像素之间的多个子图案ESDS可以与第一栅极电压供应布线GVPL1的一部分和第二栅极电压供应布线GVPL2的一部分重叠。

尤其,多个子图案ESDS中的至少一个可以与第一栅极电压供应布线GVPL1和第一栅极电压辅助布线GVAL1之间的第一栅极电压布线接触孔GVLH1重叠。

并且,多个子图案ESDS中的至少一个可以与第二栅极电压供应布线GVPL2和第二栅极电压辅助布线GVAL2之间的第二栅极电压布线接触孔GVLH2重叠。

如此,可以防止由于静电通过第一栅极电压互连接触孔GVLH1和第二栅极电压互连接触孔GVLH2流入而导致的对导电层或绝缘膜的损坏。

防静电图案ESDP可以利用与阳极垫ANDP(图27)及阴极垫CSDP(图27)同一层的第七导电层构成。

而且,布置在非显示区域NDA的第一垫区域PDA1和第二垫区域PDA2(图28和图29)中的垫PAD(图5)可以包括利用第七导电层构成的第二垫层PAD2。

据此,为了布置于第一垫区域PDA1及第二垫区域PDA2的垫PAD(图5)与防静电图案ESDP之间的绝缘,防静电图案ESDP可以与第一垫区域PDA1及第二垫区域PDA2隔开。

另外,如图5和图18至图27所示,显示面板100的晶体管阵列层TFTL可以包括覆盖第三导电层VIL、GILk、GWLk、PWELk、HVDL、GVAL1、SWPLk、GCLk、PAELk、TSTL、AVSL、DCE1、DCE2、CCE1至CCE8的第一平坦化膜160,覆盖第一平坦化膜160上的第四导电层DLj、VVDL、RDL、ANDE1、VDCE的第二平坦化膜170以及覆盖第二平坦化膜170上的第五导电层VDL2、VSL、ANDE2的第三平坦化膜180。

在此,第一平坦化膜160、第二平坦化膜170及第三平坦化膜180中的每一个可以利用丙烯酸树脂(acryl resin)、环氧树脂(epoxy resin)、酚醛树脂(phenolic resin)、聚酰胺树脂(polyamide resin)、聚酰亚胺树脂(polyimide resin)等有机膜形成。

分别利用有机膜形成的第一平坦化膜160、第二平坦化膜170及第三平坦化膜180相比于利用无机膜形成的缓冲膜BF、栅极绝缘膜130、第一层间绝缘膜141及第二层间绝缘膜142等以相对厚的厚度布置。

据此,如图5所示,为了防止由于对应于第一平坦化膜160、第二平坦化膜170及第三平坦化膜180的厚度的阶梯差而导致的侧面布线SSL(图5)的断线,第一平坦化膜160、第二平坦化膜170及第三平坦化膜180的边缘可以利用阶梯形态构成。

即,在与基板SUB的边缘对应的非显示区域NDA或与其邻近的显示区域DA的边缘中,第三平坦化膜180的边缘与第二平坦化膜170的边缘相比更远离基板SUB的边缘隔开,使得第二平坦化膜170的边缘可以不被第三平坦化膜180覆盖而暴露。与此类似地,第一平坦化膜160的边缘可以比第二平坦化膜170的边缘相比更邻近于基板SUB的边缘,并且可以不被第二平坦化膜170覆盖而暴露。

如上所述,由于第一平坦化膜160、第二平坦化膜170和第三平坦化膜180的边缘在与基板SUB的边缘对应的非显示区域NDA或与基板SUB的边缘邻近的显示区域DA的边缘利用阶梯形态形成,因此可能引起布线之间的短路不良。

作为一示例,由于第一栅极电压供应布线GVPL1布置在显示区域DA的边缘,因此第二平坦化膜170的边缘可以布置在第一栅极电压供应布线GVPL1与基板SUB的边缘之间。

图33是示出短路不良的比较例的剖面图。图34是示出沿图32的R-R剖切的面的一示例的剖面图。图35是示出沿图32的S-S'剖切的面的一示例的剖面图。

参照图33,在两条以上的第一栅极电压辅助布线GVAL1利用第一平坦化膜160上的第四导电层构成的情况下,通过第一栅极电压布线接触孔GVLH1而连接到第一栅极电压供给布线GVPL1的两条以上的第一栅极电压辅助布线GVAL1的一端EN_GVAL1中的一部分可以不被第二平坦化膜170覆盖。

据此,可能导致第一栅极电压供应布线GVPL1与防静电图案ESDP之间的短路不良SERR。

为了防止这种情况,如图34所示,根据一实施例,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1不被布置为超过第一栅极电压供应布线GVPL1而更加邻近于基板SUB的边缘。

即,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1可以以预定的第一间隔SD1与基板SUB的边缘隔开,并且第一栅极电压供应布线GVPL1可以以小于第一间隔SD1的第二间隔SD2与基板SUB的边缘隔开。

在此,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1仅延伸到第一栅极电压布线接触孔GVLH1,并且不再经过第一栅极电压供应布线GVPL1而延伸到基板SUB的边缘。

如此,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1不布置于第一栅极电压供应布线GVPL1与基板SUB的边缘之间,因此能够被第二平坦化膜170可靠地覆盖。即,可以改善两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1被第二平坦化膜170覆盖的可靠性。

并且,即使第二平坦化膜170布置为仅覆盖到第一栅极电压供应布线GVPL1为止,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1也可以被第二平坦化膜170覆盖,从而有利于减小非显示区域NDA的宽度。

相反,如图35所示,第二栅极电压供应布线GVPL2与第一栅极电压供应布线GVPL1相比更远离基板SUB的边缘,因此两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2暴露于第二平坦化膜170外部的可能性非常低。

因此,两条以上的第二栅极电压辅助布线GVAL2中的每一条的一端EN_GVAL2可以以大于第一间隔SD1的第三间隔SD3与基板SUB的边缘隔开。而且,第二栅极电压供应布线GVPL2可以以大于第三间隔SD3的第四间隔SD4与基板SUB的边缘隔开。

图36是示出图34的另一示例的剖面图。

如图36所示,根据另一示例,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1还可以仅延伸到第一栅极电压供应布线GVPL1的通过第一栅极电压布线接触孔GVLH1而暴露的一部分。

在这种情况下,两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1可以以比第一间隔SD1大的第五间隔SD5与基板SUB的边缘隔开。

由此,能够提高关于两条以上的第一栅极电压辅助布线GVAL1中的每一条的一端EN_GVAL1被第二平坦化膜170覆盖的可靠性,因此能够进一步防止短路不良。

以上,参照附图说明了本发明的实施例,但本发明所属技术领域的普通技术人员可以理解,在不改变本发明的技术思想或必要特征的情况下,可以以其他具体形态实施。因此,应当理解,上述实施例在所有方面都是示例性的,而不是限制性的。

- 薄膜晶体管及包括薄膜晶体管的显示装置

- 触摸传感器和包括该触摸传感器的显示装置

- 包括眼睛跟踪器的投影显示装置

- 保护膜、包括该保护膜的窗和制造显示装置的方法

- 光学构件、包括其的显示装置和制造该光学构件的方法

- 显示装置以及包括该显示装置的瓦片型显示装置

- 显示装置、显示装置的制造方法及瓦片型显示装置