布线电路基板

文献发布时间:2024-01-17 01:20:32

技术领域

本发明涉及一种布线电路基板。

背景技术

以往,布线电路基板具备第1绝缘层和导体图案。导体图案配置在第1绝缘层之上。导体图案具有端子和布线。布线与端子连接。端子由配置在第1绝缘层之上的第1导体层和配置在第1导体层之上的第2导体层构成(例如参照下述专利文献1。)。

现有技术文献

专利文献

专利文献1:日本特开2019-212349号公报

发明内容

发明要解决的问题

在专利文献1所记载那样的布线电路基板中,存在想要在加强期望的部分的同时确保与电子元器件之间的连接的容易性(安装性)这样的期望。

本发明提供能够在加强期望的部分的同时确保安装性的布线电路基板。

用于解决问题的方案

本发明[1]包含一种布线电路基板,其中,该布线电路基板具备:第1绝缘层;以及导体图案,其配置在所述第1绝缘层之上,具有端子和与所述端子连接的布线,该布线具有与所述端子分开地配置的第1部分和配置在所述端子与所述第1部分之间的第2部分,所述导体图案具有配置在所述第1绝缘层之上的第1导体层和配置在所述第1导体层之上的第2导体层,所述布线的所述第1部分和所述端子包含由所述第1导体层和所述第2导体层构成的部分,所述布线的所述第2部分由所述第1导体层或所述第2导体层构成。

根据这样的结构,布线中的与端子分开地配置的第1部分包含由第1导体层和第2导体层构成的部分。

由此,能够利用布线的一部分(第1部分)来加强布线电路基板的期望的部分。

另外,端子包含由第1导体层和第2导体层构成的部分。配置在端子与第1部分之间的第2部分由第1导体层或所述第2导体层构成。

因此,在端子之上安装电子元器件时,能够抑制布线的第2部分与电子元器件接触,能够使端子的第2导体层和电子元器件可靠地接触。

其结果,能够将端子可靠地连接于电子元器件。也就是说,能够确保布线电路基板的安装性。

总之,能够在加强期望的部分的同时确保安装性。

本发明[2]包含一种布线电路基板,其中,该布线电路基板具备:第1绝缘层;导体图案,其配置在所述第1绝缘层之上,具有端子和与所述端子连接的布线,该布线具有与所述端子分开地配置的第1部分和配置在所述端子与所述第1部分之间的第2部分,该导体图案具有配置在所述第1绝缘层之上的第1导体层和配置在所述第1导体层之上的第2导体层;以及中间绝缘层,其配置在所述第1导体层与所述第2导体层之间,所述端子包含由所述第1导体层、所述第2导体层和所述中间绝缘层构成的部分,所述布线的所述第1部分包含由所述第1导体层和所述第2导体层构成的部分,所述布线的所述第2部分由所述第1导体层和所述第2导体层中的至少一者构成。

根据这样的结构,布线中的与端子分开地配置的第1部分包含由第1导体层和第2导体层构成的部分。

由此,能够利用布线的一部分(第1部分)来加强布线电路基板的期望的部分。

另外,端子包含由第1导体层、第2导体层和中间绝缘层构成的部分。配置在端子与第1部分之间的第2部分由第1导体层和第2导体层中的至少一者构成。

因此,在端子之上安装电子元器件时,能够抑制布线的第2部分与电子元器件接触,能够使端子的第2导体层和电子元器件可靠地接触。

其结果,能够将端子可靠地连接于电子元器件。也就是说,能够确保布线电路基板的安装性。

总之,能够在加强期望的部分的同时确保安装性。

本发明[3]在上述[1]或[2]的布线电路基板的基础上,所述第1部分的宽度大于所述第2部分的宽度。

根据这样的结构,能够增加布线的第1部分的截面积而实现布线的电阻的降低。

本发明[4]在上述[1]~[3]中的任一项所述的布线电路基板的基础上,该布线电路基板还具备第2绝缘层,该第2绝缘层配置在所述第1绝缘层之上且覆盖所述布线,所述第2绝缘层与所述端子隔开间隔地配置。

根据这样的结构,在端子之上安装电子元器件时,能够抑制第2绝缘层与电子元器件接触。

其结果,能够实现布线电路基板的安装性的进一步的提高。

本发明[5]在上述[4]的布线电路基板的基础上,配置在所述第2部分之上的所述第2绝缘层薄于所述端子的所述第2导体层。

根据这样的结构,在端子之上安装电子元器件时,能够进一步抑制第2绝缘层与电子元器件接触。

其结果,能够实现布线电路基板的安装性的进一步的提高。

本发明[6]在上述[1]~[3]中的任一项所述的布线电路基板的基础上,该布线电路基板还具备第2绝缘层,该第2绝缘层配置在所述第1绝缘层之上且覆盖所述布线,配置在所述第2部分之上的所述第2绝缘层薄于所述端子的所述第2导体层。

根据这样的结构,在端子之上安装电子元器件时,能够抑制第2绝缘层与电子元器件接触。

其结果,能够实现布线电路基板的安装性的进一步的提高。

本发明[7]在上述[1]~[6]中的任一项所述的布线电路基板的基础上,所述布线的所述第2部分由所述第1导体层构成,整个所述第2导体层与所述第1导体层接触。

根据这样的结构,能够增加布线的第1部分的截面积而实现布线的电阻的降低。

本发明[8]在上述[1]~[6]中的任一项所述的布线电路基板的基础上,所述布线的所述第2部分由所述第2导体层构成,整个所述第1导体层与所述第2导体层接触。

根据这样的结构,能够增加布线的第1部分的截面积而实现布线的电阻的降低。

发明的效果

根据本发明的布线电路基板,能够在加强期望的部分的同时确保安装性。

附图说明

[图1]图1是本发明的一个实施方式的布线电路基板的俯视图。

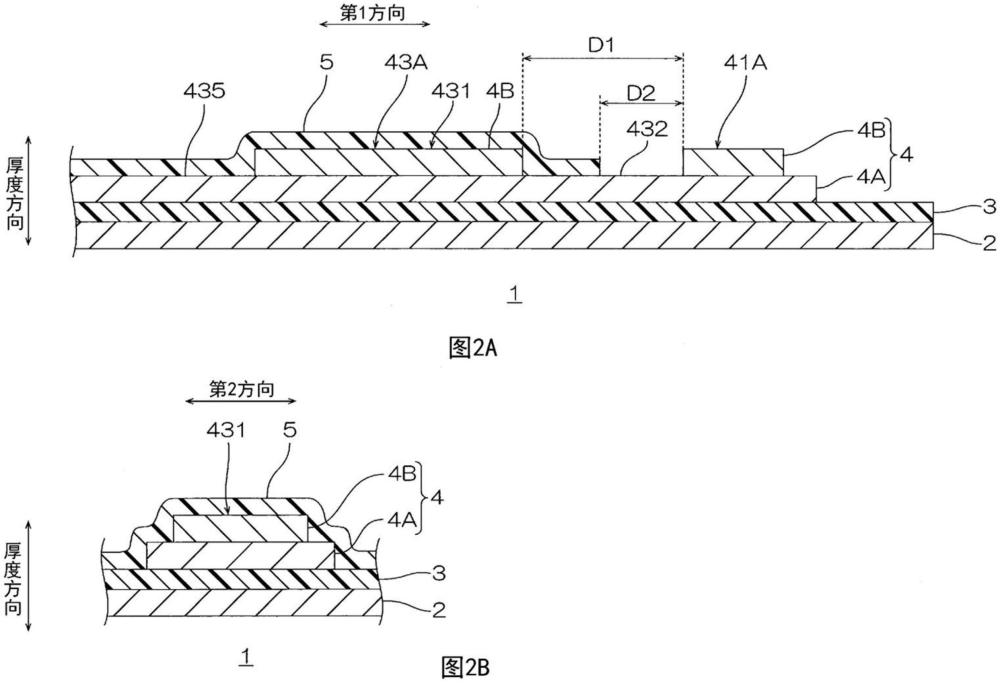

[图2]图2A是图1所示的布线电路基板的A-A剖视图。图2B是图1所示的布线电路基板的B-B剖视图。

[图3]图3是说明第1变形例的说明图。

[图4]图4是说明第2变形例的说明图。

[图5]图5是说明第3变形例的说明图。

[图6]图6是说明第4变形例的说明图。

[图7]图7是说明第5变形例的说明图。

[图8]图8是说明第6变形例的说明图。

[图9]图9是说明第7变形例的说明图。

[图10]图10是说明第8变形例的说明图。

[图11]图11A是说明第9变形例的说明图。图11B是说明第10变形例的说明图。图11C是说明第11变形例的说明图。图11D是说明第12变形例的说明图。

具体实施方式

1.布线电路基板

如图1所示,本发明的一个实施方式的布线电路基板1沿第1方向延伸。布线电路基板1是挠性布线电路基板。布线电路基板1具有片形状。布线电路基板1具有第1端部11、第2端部12、多个柔性部13A、13B、13C、13D。此外,柔性部的数量并无限定。

第1端部11是布线电路基板1的第1方向上的一端部。在本实施方式中,第1端部11具有矩形形状。此外,第1端部11的形状并无限定。

第2端部12是布线电路基板1的第1方向上的另一端部。第2端部12在第1方向上与第1端部11分开地配置。在本实施方式中,第2端部12具有矩形形状。此外,第2端部12的形状并无限定。

柔性部13A、13B、13C、13D在第1方向上配置在第1端部11与第2端部12之间。柔性部13A、13B、13C、13D分别沿第1方向延伸。柔性部13A、13B、13C、13D相互隔开间隔地在第2方向上排列。在本实施方式中,第2方向与第1方向正交。柔性部13A、13B、13C、13D在第2方向上均比第1端部11和第2端部12细。柔性部13A、13B、13C、13D均比第1端部11和第2端部12柔软。

如图2A所示,布线电路基板1具备金属支承层2、第1绝缘层3、导体图案4和第2绝缘层5。

(1)金属支承层

金属支承层2沿第1方向延伸。金属支承层2支承第1绝缘层3、导体图案4和第2绝缘层5。金属支承层2由金属构成。作为金属,例如,可举出不锈钢合金、铜合金。

金属支承层2的厚度例如为15μm以上,优选为20μm以上。若金属支承层2的厚度为上述下限值以上,则能够确保布线电路基板1的弹性。金属支承层2的厚度例如为500μm以下,优选为250μm以下。若金属支承层2的厚度为上述上限值以下,则能够确保布线电路基板1的挠性。

(2)第1绝缘层

第1绝缘层3在布线电路基板1的厚度方向上配置在金属支承层2之上。厚度方向与第1方向和第2方向正交。第1绝缘层3在厚度方向上配置在金属支承层2与导体图案4之间。第1绝缘层3使金属支承层2和导体图案4绝缘。第1绝缘层3由具有挠性的树脂构成。作为树脂,例如,可举出聚酰亚胺。

若能够使金属支承层2和导体图案4绝缘,则第1绝缘层3的厚度并无限定。第1绝缘层3的厚度例如为1μm以上,优选为3μm以上,例如为50μm以下,优选为35μm以下。

(3)导体图案

导体图案4在厚度方向上配置在第1绝缘层3之上。导体图案4在厚度方向上配置于第1绝缘层3的与金属支承层2所在侧相反的那一侧。导体图案4由金属构成。作为金属,例如,可举出铜。

(3-1)导体图案的形状

如图1所示,导体图案4具有多个第1端子41A、41B、41C、41D、多个第2端子42A、42B、42C、42D、以及多个布线43A、43B、43C、43D。此外,第1端子的数量、第2端子的数量和布线的数量并无限定。第1端子41A是端子的一个例子。

第1端子41A、41B、41C、41D配置于第1端部11。在本实施方式中,第1端子41A、41B、41C、41D相互隔开间隔地在第2方向上排列。第1端子41A、41B、41C、41D分别具有方形焊盘形状。

第2端子42A、42B、42C、42D配置于第2端部12。在本实施方式中,第2端子42A、42B、42C、42D相互隔开间隔地在第2方向上排列。第2端子42A、42B、42C、42D分别具有方形焊盘形状。

布线43A将第1端子41A和第2端子42A电连接。布线43A的一端与第1端子41A连接。布线43A的另一端与第2端子42A连接。在本实施方式中,布线43A具有第1部分431、第2部分432、第3部分433、第4部分434和第5部分435。

第1部分431配置于第1端部11。第1部分431配置于布线43A的中途。第1部分431在第1方向上与第1端子41A分开地配置。

第1部分431与第1端子41A之间的间隔D1(参照图2)例如为0.03mm以上,优选为0.1mm以上,更优选为0.2mm以上,并且例如为10mm以下,优选为5mm以下。

第1部分431沿第1方向和第2方向延伸。第1部分431具有平板形形状。在本实施方式中,第1部分431具有矩形形状。第1部分431大于第1端子41A。第1部分431的宽度(第2方向上的长度)大于第2部分432的宽度和第5部分435的宽度。由此,能够增加布线43A的第1部分431的截面积而实现布线43A的电阻的降低。另外,通过将第1部分431配置于第1端部11,能够加强第1端部11。换言之,在第1端子41A的附近,能够加强布线电路基板1的一部分。由此,能够实现布线电路基板1的安装性的进一步的提高。

第2部分432在第1方向上配置在第1端子41A与第1部分431之间。第2部分432将第1端子41A和第1部分431电连接。第2部分432的一端与第1端子41A连接。第2部分432的另一端与第1部分431连接。

第3部分433配置于第2端部12。第3部分433在第1方向上与第1部分431分开地配置。第3部分433配置于布线43A的中途。第3部分433在第1方向上与第2端子42A分开地配置。在本实施方式中,第3部分433与第2端子42A之间的间隔等于第1部分431与第1端子41A之间的间隔D1。此外,第3部分433与第2端子42A之间的间隔也可以不同于第1部分431与第1端子41A之间的间隔D1。另外,在本实施方式中,第3部分433具有与第1部分431相同的形状。此外,第3部分433也可以具有与第1部分431不同的形状。第3部分433大于第2端子42A。第3部分433的宽度大于第4部分434的宽度和第5部分435的宽度。由此,能够增加布线43A的第3部分433的截面积而降低布线43A的电阻。另外,通过将第3部分433配置于第2端部12,能够加强第2端部12。换言之,在第2端子42A的附近,能够加强布线电路基板1的一部分。由此,能够实现布线电路基板1的安装性的进一步的提高。

第4部分434在第1方向上配置在第2端子42A与第3部分433之间。第4部分434将第2端子42A与第3部分433电连接。第4部分434的一端与第2端子42A连接。第4部分434的另一端与第3部分433连接。

第5部分435配置于柔性部13A。第5部分435沿着柔性部13A延伸。第5部分435将第1部分431和第3部分433电连接。第5部分435的一端与第1部分431连接。第5部分435的另一端与第3部分433连接。

关于布线43B、43C、43D的说明与关于布线43A的说明相同。因此,省略关于布线43B、43C、43D的说明。

(3-2)导体图案的层构造

如图2A所示,导体图案4具有第1导体层4A和第2导体层4B。

在第1端子41A、第2端子42A(参照图1)和布线43A都设置第1导体层4A。第1导体层4A在厚度方向上配置在第1绝缘层3之上。布线43A的第2部分432、布线43A的第4部分434(参照图1)和布线43A的第5部分435不具有第2导体层4B,而由第1导体层4A构成。

由此,在第1端子41A之上安装电子元器件时,能够抑制布线43A的第2部分432与电子元器件接触,能够使第1端子41A的第2导体层4B和电子元器件可靠地接触。其结果,能够将第1端子41A可靠地连接于电子元器件。另外,在第2端子42A之上安装电子元器件时,能够抑制布线43A的第4部分434与电子元器件接触,能够使第2端子42A的第2导体层4B和电子元器件可靠地接触。其结果,能够将第2端子42A可靠地连接于电子元器件。也就是说,能够确保布线电路基板1的安装性。

第1导体层4A的厚度例如为1μm以上,优选为3μm以上,并且例如为50μm以下,优选为30μm以下。

也就是说,布线43A的第2部分432、布线43A的第4部分434和布线43A的第5部分435的厚度例如为1μm以上,优选为3μm以上,并且例如为50μm以下,优选为30μm以下。

第2导体层4B设于第1端子41A、第2端子42A(参照图1)、布线43A的第1部分431、布线43A的第3部分433(参照图1)。也就是说,第1端子41A、第2端子42A、布线43A的第1部分431、布线43A的第3部分433包含由第1导体层4A和第2导体层4B构成的部分。由此,能够利用布线43A的一部分(第1部分431)来加强布线电路基板1的期望的部分。

第2导体层4B的厚度例如为1μm以上,优选为3μm以上,并且例如为50μm以下,优选为30μm以下。

第1端子41A、第2端子42A、布线43A的第1部分431和布线43A的第3部分433厚于布线43A的第2部分432、布线43A的第4部分434和布线43A的第5部分435。第1端子41A、第2端子42A、布线43A的第1部分431和布线43A的第3部分433的厚度例如为1μm以上,优选为3μm以上,并且例如为50μm以下,优选为30μm以下。

如图1所示,在本实施方式中,在第1端子41A、第2端子42A、布线43A的第1部分431和布线43A的第3部分433,第2导体层4B配置于比第1导体层4A的边缘靠内侧的位置。由此,如图2B所示,布线43A的第1部分431的周缘部具有阶梯形状。布线43A的第3部分433、第1端子41A和第2端子42A也与布线43A的第1部分431相同。

如图2A和图2B所示,第2导体层4B在厚度方向上配置在第1导体层4A之上。在本实施方式中,整个第2导体层4B与第1导体层4A接触。由此,能够增加布线43A的第1部分431和第3部分433的截面积而实现布线43A的电阻的降低。

此外,关于第1端子41B(参照图1)、第2端子42B(参照图1)和布线43B(参照图1)的层构造的说明、关于第1端子41C(参照图1)、第2端子42C(参照图1)和布线43C(参照图1)的层构造的说明、以及关于第1端子41D(参照图1)、第2端子42D(参照图1)和布线43D(参照图1)的层构造的说明都与关于第1端子41A、第2端子42A和布线43A的层构造的说明相同。

因此,省略关于第1端子41B、第2端子42B和布线43B的层构造的说明、关于第1端子41C、第2端子42C和布线43C的层构造的说明以及关于第1端子41D、第2端子42D和布线43D的层构造的说明。

(4)第2绝缘层

如图1所示,第2绝缘层5覆盖布线43A。此外,第2绝缘层5还覆盖布线43B、43C、43D。第2绝缘层5配置在第1绝缘层3之上。

如图1和图2A所示,第2绝缘层5未覆盖第1端子41A和布线43A的第2部分432的一端。第2绝缘层5在第1方向上与第1端子41A隔开间隔地配置。由此,在第1端子41A之上安装电子元器件时,能够抑制第2绝缘层5与电子元器件接触。其结果,能够实现布线电路基板1的安装性的进一步的提高。

第2绝缘层5与第1端子41A之间的间隔D2例如为0.01mm以上,优选为0.05mm以上,并且例如为1mm以下,优选为0.1mm以下。

此外,如图1所示,第2绝缘层5在第1方向上也与第2端子42A隔开间隔地配置。第2绝缘层5未覆盖第2端子42A和布线43A的第4部分434的一端。

另外,第2绝缘层5在第1方向上也与第1端子41B、41C、41D、和第2端子42B、42C、42D隔开间隔地配置。第2绝缘层5未覆盖第1端子41B、41C、41D、布线43B、43C、43D各自的第2部分432的一端、第2端子42B、42C、42D、布线43B、43C、43D各自的第4部分434的一端。

如图2A所示,配置在第2部分432之上的第2绝缘层5薄于第1端子41A的第2导体层4B。由此,在第1端子41A之上安装电子元器件时,能够抑制第2绝缘层5与电子元器件接触。其结果,能够实现布线电路基板1的安装性的进一步的提高。

第2绝缘层5的厚度例如为1μm以上,优选为3μm以上,并且例如为60μm以下,优选为40μm以下。

第2绝缘层5的厚度相对于第2导体层4B的厚度的比例例如小于100%,优选为90%以下,更优选为75%以下,并且例如为10%以上。

另外,如图1和图2B所示,第2绝缘层5将第1部分431的周缘部全部覆盖。通过第2绝缘层5将第1部分431的周缘部全部覆盖,能够增加第2绝缘层5与导体图案4之间的接触面积。其结果,能够抑制第2绝缘层5自导体图案4剥离。

2.作用效果

(1)根据布线电路基板1,如图2A所示,布线43A中的与第1端子41A分开地配置的第1部分431包含由第1导体层4A和第2导体层4B构成的部分。

由此,能够利用第2导体层4B来加强布线43A的一部分(第1部分431)。在本实施方式中,通过加强第1部分431,在第1端子41A的附近,能够加强布线电路基板1的一部分。

另外,第1端子41A包含由第1导体层4A和第2导体层4B构成的部分。配置在第1端子41A与第1部分431之间的第2部分432由第1导体层4A构成。

因此,在第1端子41A之上安装电子元器件时,能够抑制布线43A的第2部分432与电子元器件接触,能够使第1端子41A的第2导体层4B和电子元器件可靠地接触。

其结果,能够将第1端子41A可靠地连接于电子元器件。也就是说,能够确保布线电路基板1的安装性。

总之,能够在利用布线43A的一部分(第1部分431)来加强期望的部分的同时确保安装性。

(2)根据布线电路基板1,如图1所示,第1部分431的宽度大于第2部分432的宽度。

因此,能够增加布线43A的第1部分431的截面积而实现布线43A的电阻的降低。

(3)根据布线电路基板1,如图2A所示,第2绝缘层5与第1端子41A隔开间隔D2地配置。

由此,在第1端子41A之上安装电子元器件时,能够抑制第2绝缘层5与电子元器件接触。

其结果,能够实现布线电路基板1的安装性的进一步的提高。

(4)根据布线电路基板1,如图2A所示,配置在第2部分432之上的第2绝缘层5薄于第1端子41A的第2导体层4B。

由此,在第1端子41A之上安装电子元器件时,能够进一步抑制第2绝缘层与电子元器件接触。

其结果,能够实现布线电路基板1的安装性的进一步的提高。

(5)根据布线电路基板1,如图2A所示,整个第2导体层4B与第1导体层4A接触。

由此,能够增加布线43A的第1部分431的截面积而实现布线43A的电阻的降低。

3.变形例

以下,参照图3~图11D说明布线电路基板的变形例。在以下的变形例中,对于与上述实施方式相同的构件标注相同的附图标记,并省略说明。

(1)如图3所示,也可以是,配置在第2部分432之上的第2绝缘层5厚于第1端子41A的第2导体层4B。在该情况下,从布线电路基板1的安装性的观点出发,第2绝缘层5优选与第1端子41A隔开间隔D2地配置。

(2)如图4所示,也可以是,仅第2导体层4B的一部分与第1导体层4A接触。详细而言,布线电路基板1还具备配置在第1导体层4A与第2导体层4B之间的中间绝缘层100。中间绝缘层100具有通路100A。第2导体层4B的一部分经由通路100A与第1导体层4A接触。

中间绝缘层100的厚度例如为1μm以上,优选为3μm以上,并且例如为60μm以下,优选为40μm以下。

(3)如图5所示,第2绝缘层5也可以覆盖整个第2部分432。换言之,也可以是,在第2绝缘层5与第1端子41A之间不存在间隔D2。在该情况下,从布线电路基板1的安装性的观点出发,配置在第2部分432之上的第2绝缘层5优选薄于第1端子41A的第2导体层4B。

(4)如图6所示,布线43A的第1部分431也可以延伸到第2端子42A的附近。在该情况下,布线43A不具有第3部分433和第5部分435。

(5)如图7所示,第2导体层4B的厚度也可以与第1导体层4A的厚度不同。在该变形例中,第2导体层4B厚于第1导体层4A。

(6)如图8所示,第2导体层4B也可以薄于第1导体层4B。

另外,布线43A的第2部分432也可以由第2导体层4B构成。在该情况下,第1导体层4A设于第1端子41A、第2端子42A(参照图1)、布线43A的第1部分431和布线43A的第3部分433(参照图1)。在第1端子41A、第2端子42A(参照图1)、布线43A都设置第2导体层4B。也可以是,整个第1导体层4A与第2导体层4B接触。

(7)如图9所示,也可以是,第2绝缘层5覆盖布线43A的第1部分431和第5部分435,而未覆盖第1端子41A和布线43A的第2部分432。此外,在该情况下,第2绝缘层5覆盖布线43A的第3部分433(参照图1),而未覆盖第2端子42A(参照图1)和布线43A的第4部分434(参照图1)。

(8)如图10所示,也可以是,第1端子41A包含由第1导体层4A、第2导体层4B和中间绝缘层100构成的部分。在该情况下,布线43A的第2部分432由第1导体层4A和第2导体层4B中的至少一者构成。在该变形例中,布线43A的第2部分432由第1导体层4A和第2导体层4B构成。布线43A的第2部分432可以由第1导体层4A构成,也可以由第2导体层4B构成。

在该变形例中,第2导体层4B的厚度也可以与第1导体层4A的厚度不同。第2导体层4B可以厚于第1导体层4A,也可以薄于第1导体层4B。

(9)如图11A~图11D所示,在第1端子41A或第2端子42A中,第1导体层4A、第2导体层4B和中间绝缘层100各自的宽度并无限定。

如图11A所示,中间绝缘层100的边缘可以与第1导体层4A的边缘一致。如图11B所示,中间绝缘层100可以配置于比第1导体层4A的边缘靠内侧的位置。如图11C所示,第1导体层4A可以配置于比中间绝缘层100的边缘靠内侧的位置。

另外,如图11D所示,第1导体层4A可以配置于比第2导体层4B的边缘靠内侧的位置。

(10)在这些变形例中,也能够获得与上述实施方式相同的作用效果。

此外,提供了上述发明作为本发明的例示的实施方式,但这仅是例示,并不能限定性地解释本发明。对于该技术领域的技术人员而言明显的本发明的变形例包含于前述的权利要求书中。

产业上的可利用性

本发明的布线电路基板被用于与电子元器件之间的连接。

附图标记说明

1、布线电路基板;3、第1绝缘层;4、导体图案;4A、第1导体层;4B、第2导体层;5、第2绝缘层;41A、第1端子;43A、布线;431、第1部分;432、第2部分;D2、间隔。

- 电子部件收纳用封装体、多连片布线基板、电子装置以及电子模块

- 电路布线形成方法、电路基板及布线膜的膜厚度比布线膜的宽度大的电路布线膜

- 电路布线形成方法、电路基板及布线膜的膜厚大于布线膜的宽度的电路布线膜