用于输入缓冲器功率节省的设备和方法

文献发布时间:2024-01-17 01:23:59

背景技术

归因于半导体装置之间的通信的高速性质,许多半导体装置在发射器侧上采用预加重电路以基于沟道的预期效应而预失真信号以用于在沟道上传输,和/或在接收器侧上采用去加重电路以补偿沟道的预期效应。去加重电路可在经由半导体装置上的电路系统对信号进行解码之前将信号幅度降低到正常电平。在一些常规实施方案中,去加重电路系统可针对特定频率应用而设计和优化,从而使得难以或不可能将去加重电路重新用于其它频率应用。因此,可能需要具有在多于一个频率应用中控制或配置去加重电路系统的能力。

发明内容

本文中描述实例设备。实例设备可包含:输入缓冲器,其耦合到端子且配置成接收输入信号且提供具有增益的输出信号;及去加重电路,其耦合到所述缓冲器且配置成基于延时设置而选择性地调整所述输入缓冲器的所述增益。另外或替代地,所述去加重电路可配置成当所述延时设置处于第一值时将所述输入缓冲器的所述增益调整第一量,且当所述延时设置为第二值时将所述输入缓冲器的所述增益调整第二量。另外或替代地,所述去加重电路可包含与所述输入缓冲器的一部分并联耦合的多个传输门,其中所述去加重电路配置成基于启用所述多个传输门中的一或多个而调整所述输入缓冲器的所述增益。在一些实例中,所述多个传输门是经由控制信号启用的晶体管。另外或替代地,所述去加重电路可进一步配置成基于所述输入缓冲器是否为单端差分输入缓冲器而选择性地调整所述输入缓冲器的所述增益。另外或替代地,所述实例设备可进一步包含输入缓冲器控制电路,所述输入缓冲器控制电路配置成使得所述去加重电路基于所述延时设置及所述输入缓冲器是配置为单端输入缓冲器还是差分输入缓冲器而调整所述输入缓冲器的所述增益。另外或替代地,所述输入缓冲器控制电路可配置成接收指示所述延时设置的模式寄存器设置,且使得所述去加重电路基于所述接收到的模式寄存器设置而调整所述输入缓冲器的所述增益。另外或替代地,所述输入缓冲器可包含放大器,其中通过限制所述放大器的电流消耗来进一步控制所述输入缓冲器的所述增益。

另一实例设备可包含:输入缓冲器,其包括耦合到一对串联耦合的反相器的放大器;去加重电路,其与所述一对串联耦合的反相器中的一个并联耦合到所述输入缓冲器,所述去加重电路包括并联耦合到电阻的多个晶体管;及输入缓冲器控制电路,其配置成基于延时设置而选择性地启用所述多个晶体管中的一个以调整所述一对反相器中的所述一个两端的增益。在一些实例中,所述多个晶体管中的至少两个可具有不同的沟道宽度。另外或替代地,当启用所述晶体管时,所述一对串联耦合的反相器中的所述一个两端的增益可减小。另外或替代地,所述输入缓冲器控制电路可配置成基于所述延时设置而通过限制所述放大器的电流消耗来调整所述放大器的增益。

本文中描述实例方法。实例方法可包含:在半导体装置的输入缓冲器控制电路处接收延时设置;基于所述延时设置而经由耦合到输入缓冲器的去加重电路设置所述半导体装置的输入缓冲器的增益的一部分;及基于所述延时设置而启用所述输入缓冲器。另外或替代地,所述方法可进一步包含:响应于所述延时设置具有第一值而将所述增益的所述部分设置为第一量;及响应于所述延时设置具有第二值而将所述增益的所述部分设置为第二量。另外或替代地,所述方法可进一步包含通过启用所述去加重电路的传输门来设置所述增益的所述部分。在一些实例中,所述传输门是晶体管。另外或替代地,所述方法可进一步包含基于所述输入缓冲器是配置成单端操作还是差分操作而基于经由所述去加重电路设置所述输入缓冲器的所述增益的所述部分。另外或替代地,所述方法可进一步包含将所述输入缓冲器的所述增益的所述部分设置为在所述延时小于阈值时比在所述延时大于所述阈值时更高。另外或替代地,所述方法可进一步包含从所述半导体装置的模式寄存器接收所述延时设置。另外或替代地,所述方法可进一步包含通过限制所述输入缓冲器的放大器的电流消耗来进一步控制所述输入缓冲器的所述增益。在一些实例中,所述延时设置包含读取延时。在一些实例中,所述延时设置包含写入延时。在一些实例中,所述延时设置包含附加延时。在一些实例中,所述延时设置包含读取延时、写入延时或附加延时的任何组合。

附图说明

图1为根据本公开的实施例的设备的框图。

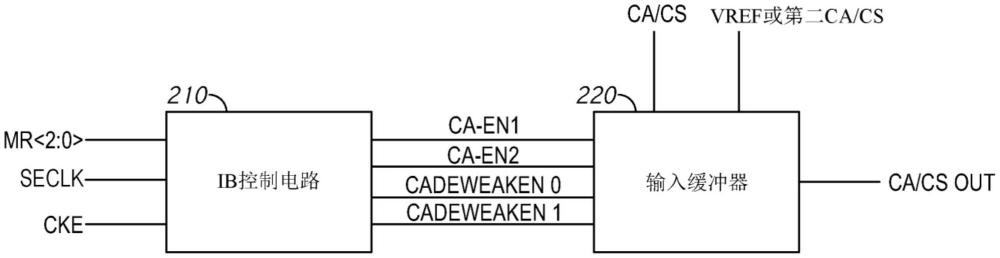

图2为根据本公开的实施例的命令/地址输入电路的部分的示范性框图。

图3为根据本公开的实施例的输入缓冲器控制电路的示范性示意图。

图4为根据本公开的实施例的输入缓冲器的示范性示意图。

图5为根据本公开的实施例的输入缓冲器控制电路的示范性示意图。

图6为根据本公开的实施例的输入缓冲器的示范性示意图。

具体实施方式

本公开描述具有能够控制去加重强度的可配置去加重电路的可配置输入缓冲器上的功率节省的实例。具有可配置去加重电路的输入缓冲器可包含与反相器串联连接的放大器。去加重电路可与反相器并联耦合。放大器可连接到沟道,且可配置成接收含有用例如数据、命令、地址、其它控制信号等信息编码的信号。在一些实例中,放大器可为单端放大器,所述单端放大器配置成将所接收信号的幅度与参考信号进行比较,以便将放大的输出信号提供到可配置去加重电路和反相器。在其它实例中,放大器可为差分放大器,所述差分放大器配置成比较两个差分信号的幅度,以便将放大的输出信号提供到可配置去加重电路和反相器。

在一些实例中,可经由提供到放大器的限流启用信号来控制放大器的增益。从放大器的输出实现的增益量还可由可配置去加重电路控制。在一些实例中,可配置去加重电路可调整耦合到放大器的输出节点的反相器两端的电阻,以便调整反相器两端的增益。去加重电路可包含从放大器的输出节点到反相器的输出节点与反相器并联耦合的两个或更多个梯级传输门电路的梯形电路。梯形电路的一或多个梯级上的晶体管可被选择性地启用以充当额外传输门,以调整反相器两端的电阻。去加重电路两端的电阻越低(例如,所启用的梯形电路的传输门越多),反相器两端的增益越低。相反,去加重电路两端的电阻越高(例如,所启用的梯形电路的传输门越少),反相器两端的增益越高。通过在放大器的输出处增加反相器两端的增益,可减少由输入缓冲器消耗的电流量。输入缓冲器可基于数据频率而选择增益。对于较高频率,由去加重电路提供的增益可减小。对于较低频率,由去加重电路提供的增益可增加。

下文阐述某些细节以提供对本公开的实例的充分理解。然而,所属领域的技术人员将清楚,可在没有这些特定细节的情况下实践本公开的实例。此外,本文中所描述的本公开的特定实例不应解释为将本公开的范围限于这些特定实例。在其它情况下,尚未详细展示众所周知的电路、控制信号、时序协议和软件操作,以便避免不必要地混淆本公开的实例。另外,例如“耦合(couples和coupled)”的术语意味着两个组件可直接或间接电耦合。间接耦合可暗指两个组件通过一或多个中间组件耦合。

图1为根据本公开的实施例的设备的框图。所述设备可包含半导体装置100,且将如此提及。在一些实施例中,半导体装置100可包含但不限于例如集成到单个半导体芯片中的DRAM装置,例如双数据速率(DDR)存储器或低功率DDR(LPDDR)存储器。半导体装置100包含存储器阵列150。存储器阵列150包含多个存储体,每一存储体包含多个字线WL、多个位线BL和/BL,以及布置在多个字线WL与多个位线BL的交叉点处的多个存储器单元MC。存储器单元MC为易失性存储器单元,需要周期性刷新以便维持存储于存储器阵列中的数据。

字线WL的选择由行地址控制电路140执行,且位线BL的选择由列解码器145执行。感测放大器(SAMP)针对其对应位线BL和/BL定位,耦合到至少一个相应本地I/O线对(LIOT/B),所述相应本地I/O线对又经由充当开关的传送门(TG)耦合到至少一个相应主I/O线对(MIOT/B)。

存储器阵列150可划分成存储器存储体BANK0-7,其中每一存储器存储体具有规则阵列和冗余阵列。规则阵列包含通常用于存储数据的存储器单元,其中存储器单元对应于相应存储器地址。冗余阵列包含可用于“修复”规则阵列的有缺陷存储器单元的存储器单元。存储器单元可配置为存储器的冗余行和存储器的冗余列。存储器的冗余行可用于修复规则阵列的存储器的行,且存储器的冗余列可用于修复规则阵列的存储器的列。冗余存储器用于通过使对应于缺陷存储器单元的存储器地址映射到冗余阵列的存储器单元来修复规则阵列的有缺陷存储器单元。因此,当将有缺陷存储器位置的存储器地址提供到半导体装置100时,存取冗余阵列中存储器地址所映射到的存储器位置而不是规则阵列中对应于所述存储器地址的有缺陷存储器位置。

半导体装置100可采用多个外部端子,其包含耦合到命令和地址总线以接收命令和地址的命令/地址端子CA。多个外部端子进一步包含用以接收时钟信号的时钟端子CK和CK/、数据端子DQ和数据掩蔽端子DM,以及电源端子VDD、VSS、VDDQ和VSSQ。

命令/地址端子CA可被供应例如来自存储器控制器的存储器地址。经由命令/地址输入电路105将供应到命令/地址端子CA的存储器地址传送到地址解码器112。地址解码器112接收存储器地址且将经解码行地址XADD供应到行地址控制电路140,且将经解码列地址YADD供应到列解码器145。

命令/地址端子CA可进一步被供应来自例如存储器控制器的命令。命令可作为内部命令信号ICMD经由命令/地址输入电路105提供到命令解码器115。命令解码器115包含用以对内部命令ICMD进行解码以产生用于执行操作的内部命令和信号的电路。举例来说,命令解码器115可将激活命令ACT和刷新命令AREF提供到行地址控制电路140以选择字线,且可将读取/写入命令R/W提供到列解码器145以选择位线。当执行刷新操作时,刷新命令AREF可由命令解码器115提供到行控制电路140。刷新命令AREF可表示由半导体装置100接收刷新命令产生的自动刷新命令,且还可表示当将半导体装置100设置为自刷新模式时在内部产生的自刷新命令。

当接收到读取命令且随所述读取命令及时供应存储器地址时,从存储器阵列150中由存储器地址指定的存储器单元读取读取数据。经由读取/写入放大器155和输入/输出电路160将读取数据从数据端子DQ输出到外部。当接收到写入命令且随写入命令及时供应存储器地址时,将写入数据和数据掩码(当适用时)供应到数据端子DQ和DM,且将写入数据写入到存储器阵列150中由存储器地址指定的存储器单元。写入数据由输入/输出电路160中的数据接收器接收,且经由输入/输出电路160和读取/写入放大器155供应到存储器阵列150。

在读取和写入命令的存取操作期间,行地址控制电路140可包含用于确定存储器地址是否已映射到冗余阵列中的存储器位置的电路,举例来说,当对应于规则阵列中的有缺陷存储器位置的存储器地址已映射到冗余阵列的存储器位置(例如,存储器的冗余行)时。存储已经重新映射的存储器地址,且将与存取操作相关联的存储器地址与所存储的存储器地址进行比较。已经映射到冗余存储器的存储器地址可存储于非易失性存储装置中。非易失性存储装置的实例为以待存储的存储器地址编程的熔丝电路(以及反熔丝电路)。当与存取操作相关联的存储器地址匹配所存储的存储器地址时,存取冗余阵列中的存储器位置而不是规则阵列中的存储器位置。

如先前所描述,周期性地刷新易失性存储器单元以便维持由存储器阵列存储的数据。存储器单元通常作为存储器单元的行来刷新。行地址控制电路140可包含在刷新操作期间使用的刷新控制电路。当将有效刷新命令AREF提供到行地址控制电路140时执行刷新操作。每一刷新命令AREF产生与待刷新的刷新地址相关联的存储器位置。在本公开的一些实施例中,刷新地址可在半导体装置100内部产生。在本公开的一些实施例中,类似电路和操作可包含于列解码器145中。

转向半导体装置100中包含的外部端子的阐释,时钟端子CK和/CK被供应互补外部时钟信号。外部时钟信号可供应到时钟输入电路120。时钟输入电路120可产生内部时钟信号ICLK。内部时钟信号ICLK供应到内部时钟产生器电路130和命令解码器115。当通过来自命令/地址输入电路105的时钟启用CKE启用时,内部时钟产生器电路130的电路基于内部时钟信号ICLK而提供各种内部时钟信号LCLK。内部时钟信号LCLK可用于对各种内部电路的操作进行定时。举例来说,LCLK信号可提供到输入/输出电路160以用于对输入/输出电路160的操作进行定时以在数据端子DQ上提供和接收数据。

电源端子VDD和VSS被供应电源电位。这些电源电位供应到内部电压产生器电路170。内部电压产生器电路170基于提供到电源端子VDD和VSS的电源电位而产生各种内部电位VPP、VOD、VARY、VPERI等。内部电位VPP主要用于行地址控制电路140中,内部电位VOD和VARY主要用于包含于存储器阵列150中的感测放大器SAMP中,且内部电位VPERI用于许多其它外围电路块中。

电源端子VDDQ和VSSQ也被供应电源电位。电源电位供应到输入/输出电路160。在本公开的一些实施例中,提供到电源端子VDDQ和VSSQ的电源电位可与提供到电源端子VDD和VSS的电源电位相同。将专用电源电位提供到电源端子VDDQ和VSSQ,使得由输入/输出电路160产生的电源噪声不传播到其它电路块。

在一些实例中,命令/地址输入电路105可包含耦合到输入缓冲器控制电路107的输入缓冲器106。输入缓冲器106可为具有能够控制去加重强度的可配置去加重电路系统的可配置输入缓冲器。输入缓冲器106可各自包含与去加重电路串联连接的放大器。放大器可连接到CA或CS端子中的相应一个,且可配置成接收含有用例如数据、命令、地址、其它控制信号等信息编码的信号。在一些实例中,每一放大器可为单端放大器,所述单端放大器配置成将所接收信号的幅度与参考信号进行比较,以便将放大的输出信号提供到与反相器并联耦合到可配置去加重电路的节点。在其它实例中,每一放大器可为差分放大器,所述差分放大器配置成比较两个差分信号的幅度,以便将放大的输出信号提供到可配置去加重电路和反相器。在一些实例中,可经由从输入缓冲器控制电路107提供到放大器的限流启用信号来控制放大器的增益。从放大器的输出实现的增益量还可由可配置去加重电路控制。在一些实例中,可配置去加重电路可调整耦合到放大器的输出节点的反相器两端的电阻,以便调整反相器两端的增益。去加重电路可包含从放大器的输出节点到反相器的输出节点与反相器并联耦合的两个或更多个梯级传输门电路的梯形电路。梯形电路的一或多个梯级上的晶体管可被选择性地启用以充当额外传输门,以调整反相器两端的电阻。去加重电路两端的电阻越低(例如,所启用的梯形电路的传输门越多),反相器两端的增益越低。相反,去加重电路两端的电阻越高(例如,所启用的梯形电路的传输门越少),反相器两端的增益越高。

输入缓冲器控制电路107可配置成控制提供到放大器的启用信号,以及基于来自115的模式寄存器设置而控制去加重电路的哪些传输门被启用。模式寄存器设置可定义各种延时(例如,读取延时、写入延时、附加延时或其任何组合)以及CK和/CK信号是单端时钟信号还是差分时钟信号。在一些实例中,接收读取命令与提供输出数据之间的延时可由读取延时和附加延时定义。在一些实例中,接收写入命令与接收写入数据之间的延时可由写入延时和附加延时定义。这些信号可帮助定义输入缓冲器106应能够操作的速度。通过在放大器的输出处增加反相器两端的增益,可减少由输入缓冲器消耗的电流量。输入缓冲器可基于数据频率而选择增益。对于较高频率,由去加重电路提供的增益可减小。对于较低频率,由去加重电路提供的增益可增加。

图2为根据本公开的实施例的命令/地址输入电路200的部分的示范性框图。在一些实施例中,图1的命令/地址输入电路105可实施命令/地址输入电路200。命令/地址输入电路200可包含耦合到输入缓冲器220的输入缓冲器控制电路210。

输入缓冲器控制电路210可配置成接收模式寄存器设置MR<2:0>、单端时钟启用信号SECLK和时钟启用信号CKE。响应于MR<2:0>设置、CLK信号和CKE信号,输入缓冲器控制电路210可提供第一和第二缓冲器启用信号CA-EN1和CA-EN2,且第一和第二缓冲器削弱信号CADEWEAKEN0和CADEWEAKEN1。MR<2:0>信号可定义延时设置(例如,读取延时、写入延时、附加延时或其任何组合)。

输入缓冲器220可配置成接收来自输入缓冲器控制电路210的CA-EN1/2和CADEWEAKEN0/1信号,以及来自CA/CS端子和参考电压VREF的信号。输入缓冲器220可配置成基于所接收输入信号而提供经由CA/CS端子接收到的信号作为CA/CS OUT信号。

在操作中,输入缓冲器220可包含能够控制去加重强度的可配置去加重电路系统。输入缓冲器控制电路210可基于模式寄存器设置MR<2:0>而控制输入缓冲器220的去加重电路系统,所述模式寄存器设置指示应预期输入缓冲器220支持的时钟速度。

具体来说,输入缓冲器控制电路210可配置成基于MR<2:1>设置、SECLK设置和CKE信号而设置CA-EN1和CA-EN2信号。当启用CKE时,且当设置MR<2:1>设置或设置SECLK信号两者以指示单端时钟时,可将CA-EN2信号设置为高。否则,可将其设置为低。当设置CKE信号时,可将CA-EN1信号设置为高。否则,可将其设置为低。

输入缓冲器控制电路210可配置成基于MR<2:0>设置、SECLK设置和CKE信号而设置CADEWEAKEN0/1信号。输入缓冲器控制电路210可配置成当设置SECLK信号且设置MR<1:0>信号中的仅一个时将CADEWEAKEN1信号设置为高。否则,可将其设置为低。输入缓冲器控制电路210可配置成当将CA-EN2信号设置为低且将CADEWEAKEN1信号设置为高时将CADEWEAKEN0信号设置为高。否则,可将其设置为低。设置SECLK信号,且设置MR<1:0>信号中的仅一个。

输入缓冲器220可包含与去加重电路串联连接的放大器。放大器可连接到相应CA/CS端子,且可配置成接收含有用例如数据、命令、地址、其它控制信号等信息编码的信号。在一些实例中,放大器可为单端放大器,所述单端放大器配置成将所接收信号的幅度与VREF信号进行比较,以便将放大的输出信号提供到与反相器并联耦合到可配置去加重电路的节点。在其它实例中,输入缓冲器220可连接到第二CA/CS端子(例如,而非接收VREF信号),且放大器可为差分放大器,所述差分放大器配置成比较来自两个CA/CS端子的两个差分信号的幅度,以便将放大的输出信号提供到可配置去加重电路和反相器。在一些实例中,可经由从输入缓冲器220提供到放大器的限流CA-EN1和CA-EN2来控制放大器的增益。举例来说,当设置CA-EN1和CA-EN2信号两者时,放大器可在全强度下操作。当清除CA-EN2信号时,放大器可在较低容量下操作。在一些实例中,较低容量可小于50%,例如33%。当将CA-EN1和CA-EN2信号两者设置为低时,可停用放大器。

从输入缓冲器控制电路210的输出实现的增益量还可由可配置去加重电路控制。在一些实例中,可配置去加重电路可调整耦合到放大器的输出节点的反相器两端的电阻,以便调整反相器两端的增益。去加重电路可包含从放大器的输出节点到反相器的输出节点与反相器并联耦合的两个或更多个梯级传输门电路的梯形电路。梯形电路的一或多个梯级上的晶体管可经由CADEWEAKEN0/1信号选择性地启用以充当额外传输门,以调整反相器两端的电阻。去加重电路两端的电阻越低(例如,所启用的梯形电路的传输门越多),反相器两端的增益越低。相反,去加重电路两端的电阻越高(例如,所启用的梯形电路的传输门越少),反相器两端的增益越高。因此,当将CADEWEAKEN0/1信号两者设置为低时,去加重电路可实现最低增益(例如,更好地用于较高速度应用)。当将CADEWEAKEN0/1信号两者设置为低时,去加重电路可实现最高增益(例如,更好地用于较低速度应用)。当将CADEWEAKEN0/1信号中的一个设置为高且将另一个设置为低时,去加重电路可实现中间增益(例如,经调谐以用于中等速度应用)。

图3为根据本公开的实施例的输入缓冲器控制电路300的示范性示意图。在一些实施例中,图1的输入缓冲器控制电路107和/或图2的输入缓冲器控制电路210可实施输入缓冲器控制电路300。

输入缓冲器控制电路300可配置成接收MR<2:0>设置、CKE和SECLK信号,且可包含共同控制CA-EN1、CA_EN2和CADEWEAKEN0/1信号的若干逻辑门。反相器322和反相器328可基于CKE信号的值而控制CA-EN1信号。一般来说,CA-EN1信号可经由反相器322和反相器328跟踪CKE信号的值。可将CA-EN1、CA-EN2和CADEWEAKEN0/1信号提供到输入缓冲器(例如,图1的输入缓冲器106和/或图2的输入缓冲器220中的一个)以控制增益和电流消耗。

NAND门310、反相器314、NAND门316、反相器322、NAND门324、反相器326和反相器330可基于SECLK和MR<2:1>设置而控制CA-EN2信号。NAND门310可将NAND逻辑应用于MR<2:1>设置以提供输出信号。因此,如果MR<2:1>设置两者均为高,那么NAND门310的输出为低,从而指示较低延时(例如,读取延时、写入延时、附加延时或其任何组合)。NAND门316可将NAND逻辑应用于NAND门310的输出和经由反相器314反相的SECLK信号(例如,差分时钟信号)。因此,如果NAND门310的输出为高(例如,指示较高延时(例如,读取延时、写入延时、附加延时或其任何组合))且SECLK指示差分时钟信号,那么NAND门316的输出为低。否则,将其设置为高。反相器326可将NAND逻辑应用于反相CKE信号(例如,经由反相器322)和NAND门316的输出。当CKE信号设置为低且NAND门316的输出为高(例如,单端时钟信号或低延时操作)时,NAND门324的输出设置为低。否则,将其设置为高。与反相器330串联耦合的反相器326可提供NAND门316的输出作为CA-EN2信号。

AND门340、NOR门342、NAND门344和反相器346可基于MR<2:0>设置和SECLK信号而控制CADEWEAKEN1信号。当MR<2:0>设置中的多于一个设置为高(例如,指示至少中间延时)时,可将AND门340和NOR门342设置为低。否则,可将AND门340和NOR门342的输出设置为高(例如,指示较高延时)。NAND门344可将NAND逻辑应用于NOR门342的输出和SECLK信号。因此,如果NAND门310的输出为高(例如,指示较高延时)且SECLK指示单端时钟信号,那么NAND门344的输出为低。否则,可将其设置为高。NAND门344的输出可经由反相器346反相以提供CADEWEAKEN1信号。在一些实例中,所述延时可包含读取延时。在其它实例中,所述延时可包含写入延时、附加延时或读取延时、写入延时或附加延时的任何组合。

CADEWEAKEN0信号可经由反相器352、NAND门354和反相器356基于CA-EN2信号与CADEWEAKEN1信号的组合而设置。NAND门354可将NAND逻辑应用于反相CA-EN2信号(经由反相器352)和CADEWEAKEN1信号。因此,如果将CADEWEAKEN1设置为高,且将CA-EN2信号设置为低,那么将NAND门354的输出设置为低。否则,将其设置为高。反相器356可以将NAND门354的输出反相以提供CADEWEAKEN0信号。

图4为根据本公开的实施例的输入缓冲器400的示范性示意图。在一些实施例中,图1的输入缓冲器106和/或图2的输入缓冲器220中的任一个可实施输入缓冲器400。

输入缓冲器400可包含放大器410、与电阻器430串联耦合的去加重电路420、反相器440和反相器442。放大器410可配置成接收CA-EN1/2信号,以及来自CA/CS端子的信号和参考电压VREF。输入缓冲器220可配置成基于VREF信号和CA-EN1/2信号而将经由CA/CS端子接收到的信号提供到去加重电路420和反相器440。在其它实例中,放大器410可连接到第二CA/CS端子(例如,而非接收VREF信号),且放大器410可为差分放大器,所述差分放大器配置成比较来自两个CA/CS端子的两个差分信号的幅度,将输出信号提供到去加重电路420和电阻器430。当设置CA-EN1和CA-EN2信号两者时,放大器410在满功率下启用。当CA-EN1和CA-EN2信号两者均未设置时,可停用放大器410。当仅设置CA-EN1信号时,放大器410可在较低功率下操作。在一些实例中,较低功率小于满功率的50%。在一些实例中,较低功率为满功率的33%。

去加重电路420可与电阻器430串联耦合,且包含晶体管422、晶体管424和串联耦合的晶体管426和晶体管428。可经由电源电压VSS启用串联耦合的晶体管426和晶体管428。然而,晶体管422和晶体管424可分别经由CADEWEAKEN0/1信号选择性地启用,以改变去加重电路420两端的电阻,这可影响反相器440两端的增益。举例来说,通过启用晶体管422和晶体管424中的一个或两个,可减小与电阻器430串联的去加重电路420的电阻,这可减小反相器440两端的增益。反相器440两端的增益在晶体管422和晶体管424两者均被启用时可处于其最低值,且在晶体管422和晶体管424两者均未被启用时可处于其最高值。将去加重电路420实施为可配置的且允许调整反相器440两端的增益可有助于在更宽的时钟频率阵列上且以降低的功耗进行操作。在一些实例中,晶体管422和晶体管424可具有类似的沟道宽度。在其它实例中,晶体管422和晶体管424可具有不同的沟道宽度。在一些实例中,晶体管422和晶体管424的沟道宽度可大于晶体管426和晶体管428的沟道宽度。在操作中,输入缓冲器220可包含能够控制去加重强度的可配置去加重电路系统。输入缓冲器控制电路210可基于模式寄存器设置MR<2:0>而控制输入缓冲器220的去加重电路系统,所述模式寄存器设置指示应预期输入缓冲器220支持的时钟速度。

反相器442可将反相器440和电阻器430的输出反相以提供CA/CS OUT信号。

图5和6分别包含图3的输入缓冲器控制电路300和图4的输入缓冲器400的替代实施例的示范性示意图。图5为根据本公开的实施例的输入缓冲器控制电路500的示范性示意图。在一些实施例中,图1的输入缓冲器控制电路107和/或图2的输入缓冲器控制电路210可实施输入缓冲器控制电路500。输入缓冲器控制电路500可包含先前已关于图3的输入缓冲器控制电路300描述的元件。图5中已使用与图3中所使用的参考标号相同的参考标号来标识那些元件,且共同元件的操作如先前所描述的那样。因此,为了简洁起见,将不重复对这些特定元件的操作的详细描述。

输入缓冲器控制电路500可配置成接收MR<2:0>设置、CKE和SECLK信号,且可包含共同控制CA-EN1和CA_EN2信号的若干逻辑门。不同于图3的输入缓冲器控制电路300,图5的输入缓冲器控制电路500并不包含控制CADEWEAKEN0/1信号的逻辑。图5的输入缓冲器控制电路500可将CA-EN1和CA-EN2信号提供到图6的输入缓冲器600。

图6为根据本公开的实施例的输入缓冲器600的示范性示意图。在一些实施例中,图1的输入缓冲器106和/或图2的输入缓冲器220中的任一个可实施输入缓冲器600。输入缓冲器600可包含先前已关于图4的输入缓冲器400描述的元件。图6中已使用与图4中所使用的参考标号相同的参考标号来标识那些元件,且共同元件的操作如先前所描述的那样。因此,为了简洁起见,将不重复对这些特定元件的操作的详细描述。

输入缓冲器600可包含放大器410、与电阻器430串联耦合的去加重电路420、反相器440和反相器442,如图4的输入缓冲器400中的情况。然而,晶体管422和晶体管424可分别经由CA-EN2信号的反相版本来控制,而不是经由CADEWEAKEN0/1信号来控制。否则,输入缓冲器400的操作可与参考图4的输入缓冲器400描述的操作相同。参考图5和6描述的实施例可提供更简单的实施方案,尽管分别与图3和4的实施例相比具有更少的配置选项。

从前述内容应了解,尽管本文中已出于说明的目的描述了本公开的具体实施例,但可以在不脱离本公开的精神和范围的情况下进行各种修改。因此,本公开的范围不应受本文中所描述的具体实施例中的任一个限制。

- 用于认证用户的方法、输入设备和计算机可读介质

- 用于UE功率节省的调度功率配置文件的设备、系统和方法

- 用于无线通信系统中的电子设备节省功率的方法和设备