一种基于BRAM的迭代型NTT交错存储系统

文献发布时间:2024-01-17 01:27:33

技术领域

本发明涉及基于格的Kyber方案技术领域,具体涉及一种基于BRAM的迭代型NTT交错存储系统。

背景技术

随着信息技术以及互联网的飞速发展,如何确保信息传递过程中的安全性以及保密性一直是信息技术领域的关键问题之一。在当前的密码体系中,一些经典的公钥密码算法例如RSA和椭圆曲线加密(E11iptic curve cryptography,ECC)随着量子计算机的出现而变得岌岌可危,因此需要新的密码学方案来应对量子计算机攻击,后量子密码方案应运而生。

而基于格的Kyber方案是四种被NIST所标准化的后量子密码方案之一,它能够提供更强的安全性、更高的效率,成为目前唯一一个将被制定为标准化算法的密钥封装机制(Key Encapsulation Mechanism,KEM)协议。

多项式乘法是R-LWE,LWE,M-LWE格密码方案的核心运算模块,一般采用Schoolbook或者NTT算法实现。由于NTT算法相较Schoolbook算法具有明显的时间复杂度优势,因此在高速实现的设计当中,一般采用NTT(数论变换,Number Theoretic Transform)方案。至此,以NTT为核心运算的格密码体系基本形成。

NTT模块是Kyber方案中的关键部分,如何做好NTT模块的优化和加速是当前基于格的密码方案研究的主要内容。

专利号为CN115756386A的发明中公开了一种基于格密码的高效轻量级NTT乘法器电路,包括NTT控制单元、双端口RAM、两个并行的NTT蝶形计算单元;其中,NTT蝶形计算单元模式可切换,NTT控制单元与双端口RAM连接,双端口RAM分别与两个并行的NTT蝶形计算单元连接;数据通过双端口RAM输入到NTT蝶形计算单元中,通过NTT控制单元的模式控制信号来选择不同的NTT蝶形计算单元模式,NTT蝶形计算单元处理数据并通过巴雷特约减单元将计算得到的乘法结果约减后,按照NTT算法特有的顺序写回双端口RAM中。该发明减少了计算复杂度和硬件资源消耗,并提高了模乘单元运算的速度。但该发明涉及两个并行的NTT蝶形计算单元,运行周期长,运行速度也受到了限制。

发明内容

为了解决现有迭代型NTT架构运行周期长,速度受限的问题,本发明提出了一种基于BRAM的迭代型NTT交错存储系统,对迭代型NTT架构做了进一步优化,并且通过优化NTT运算中的存储方式,通过交错存取数据,大大减少了蝶形运算单元的等待周期。

为实现上述技术目的,本发明采取的技术方案为:

一种基于BRAM的迭代型NTT交错存储系统,所述迭代型NTT交错存储系统包括蝶形运算单元、分布式ROM、第一地址控制单元、第二地址控制单元以及数据存储单元;

所述第一地址控制单元、数据存储单元、第二地址控制单元、蝶形运算单元依次回环连接;所述数据存储单元包括相互独立的第一BRAM单元和第二BRAM单元;

所述第一BRAM单元和第二BRAM单元均采用双端口BRAM,存储有预处理后的数据;所述分布式ROM用于存储旋转因子;

所述第二地址控制单元按照起始点组的变化以及每组蝶形运算的点数,读取第一BRAM单元和第二BRAM单元的数据,使得上下两路输入数据按照数论变换变化规则进入蝶形运算单元进行处理;所述第一地址控制单元用于将蝶形运算单元的运算结果存储至第一BRAM单元或者第二BRAM单元;上下路输入点的间距逐级递减,每一级的第一组输入点被设置为起始点组;

具体地,每一级蝶形运算单元输出后,均由当前存储蝶形运算单元输出数据的存储单元进行下一级的蝶形运算单元输入;蝶形运算单元输出的数据按照下一级的蝶形运算单元数据地址要求存入当前级的存储单元,直至迭代完成;最后一级时,蝶形运算单元不进行乘法操作。

进一步地,所述蝶形运算单元采用GS结构或者CT结构。

进一步地,当采用GS结构时,所述蝶形运算单元包括模加模块、模减模块和巴雷特模乘模块;所述模加模块、模减模块分别对待处理的两个数据进行加法和减法运算,加法运算结果直接输出,减法运算结果与相应的旋转因子通过巴雷特模乘单元进行乘法运算后输出。

进一步地,当采用CT结构时,所述蝶形运算单元包括模加模块、模减模块和巴雷特模乘模块;

所述巴雷特模乘模块将其中一个待处理的数据与相应的旋转因子进行乘法运算,所述模加模块、模减模块分别对巴雷特模乘模块输出的乘法运算结果和另一个待处理的数据和进行加法和减法运算,再将运算结果输出。

进一步地,所述第一地址控制单元、第二地址控制单元根据每一级标志信号的变化,完成地址交错变换以及第一BRAM单元和第二BRAM单元的交替存取。

进一步地,对于n点输入的NTT变换,总共进行log

进一步地,所述蝶形运算单元的输入点为128个,所述迭代型NTT交错存储系统的级数为7级。

进一步地,对于128点输入,数论变换变化规则为:

第一级采用一个蝶形组,每组蝶形运算数目为64,第二级采用两个蝶形组,每组蝶形运算数目为32,每一级的蝶形组数目呈2的幂次增加,对应每组的蝶形运算数目呈2的幂次递减,且每一级的总蝶形运算数目保持不变为64个;

进行数论变换算法时,数据经过预处理后进入第一轮变换,第一轮蝶形运算单元的两个输入点间距为n/2,下半部分四次蝶形变换分别与旋转因子的0到n/2-1次幂相乘;第二轮变换时,原序列被拆成两组,每部分作n/4次蝶形变换,蝶形运算单元的两个输入点间距为n/4,上下部分两次蝶形变换分别与旋转因子的平方ω

与现有技术相比,本发明的有益效果如下:

本发明的基于BRAM的迭代型NTT交错存储系统,可以减少基于BRAM的迭代型NTT的BF等待周期,大大提升了处理数据的效率,经测试,总周期数减少约50%,同时优化了存储方式。

附图说明

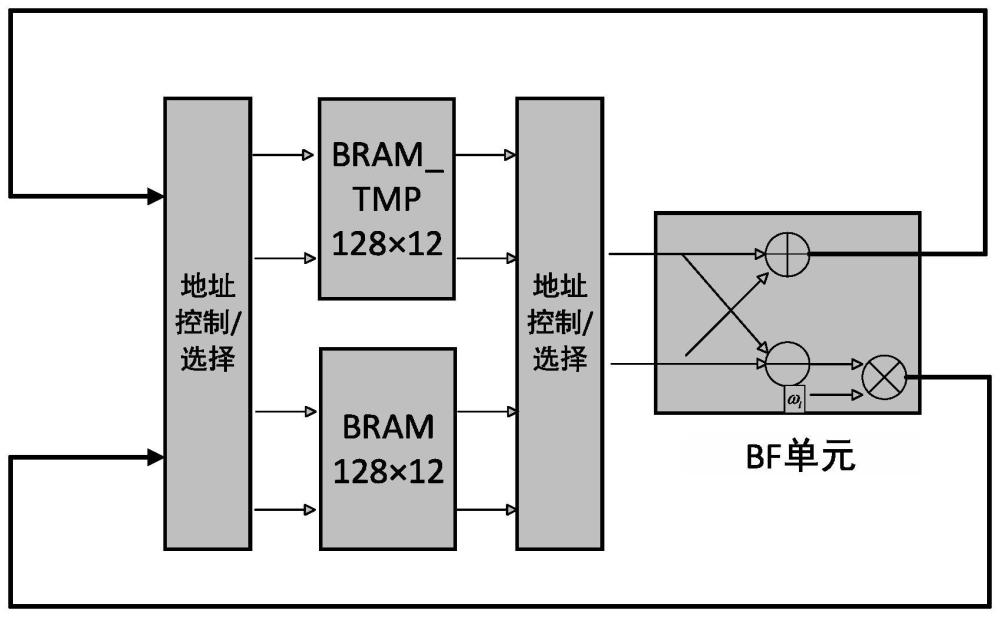

图1为现有的基于BRAM的迭代型NTT结构图;

图2为8点NTT蝶形变换图;

图3为两种蝶形运算单元的结构图;

图4为本发明的RTL原理图;

图5为本发明的基于BRAM的迭代型NTT交错存储系统结构示意图。

具体实施方式

以下结合附图对本发明的实施例作进一步详细描述。

参见图5,本发明公开了一种基于BRAM的迭代型NTT交错存储系统,所述迭代型NTT交错存储系统包括蝶形运算单元、分布式ROM、第一地址控制单元、第二地址控制单元以及数据存储单元;

所述第一地址控制单元、数据存储单元、第二地址控制单元、蝶形运算单元依次回环连接;所述数据存储单元包括相互独立的第一BRAM单元和第二BRAM单元;

所述第一BRAM单元和第二BRAM单元均采用双端口BRAM,存储有预处理后的数据;所述分布式ROM用于存储旋转因子;

所述第二地址控制单元按照起始点组的变化以及每组蝶形运算的点数,读取第一BRAM单元和第二BRAM单元的数据,使得上下两路输入数据按照数论变换变化规则进入蝶形运算单元进行处理;所述第一地址控制单元用于将蝶形运算单元的运算结果存储至第一BRAM单元或者第二BRAM单元;上下路输入点的间距逐级递减,每一级的第一组输入点被设置为起始点组;

具体地,每一级蝶形运算单元输出后,均由当前存储蝶形运算单元输出数据的存储单元进行下一级的蝶形运算单元输入;蝶形运算单元输出的数据按照下一级的蝶形运算单元数据地址要求存入当前级的存储单元,直至迭代完成;最后一级时,蝶形运算单元不进行乘法操作。

图1为现有的基于BRAM的迭代型NTT结构图。NTT本质上就是对模意义下的多项式进行DFT的一种算法,NTT采用了一个取模数与多项式系数域元素个数互质的取模数,并利用数论中的同余定理,将复数域上的DFT转化为模意义下的多项式运算。

对于多项式来说,最常用的表示方式为系数表示法,例如,a(x)=1+x+2x

在FFT中,关键在于选取特殊的取值点进行点值表示,在NTT中也需要通过选取特殊的点值(称作旋转因子ω)进行计算。对于用点值形式表示的n-1阶多项式,选取的n个特殊点即为旋转因子ω的n次幂。多项式系数用a

假设

1.计算旋转因子的n次幂:[ω

2.利用NTT变换,计算a(x)和b(x)的点值形式

3.计算

4.利用INTT变换,将

算法的具体流程如下:

算法1:基于NTT的环多项式乘法算法

对于基于M-LWE的格密码实现方案,新参数的模数由7681减小到3329,多项式的最高次为256,即输入为256个点。然而该模数并不满足NTT乘法的条件q=1mod 2n即3329仅存在256次原根而非512次原根。根据NIST的计算规则,虽然3329无法分解不可约多项式x

其中ζ=17,所有的256次原根为{ζ,ζ

观察可以发现,其中奇数项和偶数项的常数项系数计算式为:

上述式子中,如果将ζ

化简后的奇数偶数项写为:

因为NTT在计算时候会丢弃小位宽的数据,因此本申请中NTT算法中的乘法都采用的是FPGA中的DSP资源实现,为了减少该资源的消耗,利用偶数项结果通过简单的数学变换可以将PWM中的五次乘法减少到四次:

因此q=3329时NTT算法的多项式乘法参数如表1:

表1 q=3329NTT算法的多项式乘法参数

根据先前NTT的分析,通过奇偶分治,可以得到:

但是实际上,也可以进行前n/2项和后n/2项的拆分得到下面两个式子:

a

而根据这两种不同的拆分方式,本申请设计了两种不同的蝶形运算单元结构,即CT(Cooley-Tukey)和GS(Gentleman-Sande)如图3所示,其中的加法器减法器均为模加模减。具体地,当采用GS结构时,所述蝶形运算单元包括模加模块、模减模块和巴雷特模乘模块;所述模加模块、模减模块分别对待处理的两个数据进行加法和减法运算,加法运算结果直接输出,减法运算结果与相应的旋转因子通过巴雷特模乘单元进行乘法运算后输出。当采用CT结构时,所述蝶形运算单元包括模加模块、模减模块和巴雷特模乘模块;所述巴雷特模乘模块将其中一个待处理的数据与相应的旋转因子进行乘法运算,所述模加模块、模减模块分别对巴雷特模乘模块输出的乘法运算结果和另一个待处理的数据和进行加法和减法运算,再将运算结果输出。

两种蝶形运算单元最主要的区别在于乘法操作和模加模减的先后顺序。其中模加模减对应的算法如算法2和算法3所示:

硬件电路中设置总和位宽为13bit和差值为13bit,通过判断1bit的进位和借位就可以得到最终在[0,q-1]的模加或模减结果。模加和模减在相同的时钟周期内完成,在蝶形运算单元的上半部分只涉及到模加运算,为了配平时序,乘法结果需要同时输出并增加5级触发器作为延时单元。

对于上一小节提到的GS和CT两种蝶形运算单元,两者除了蝶形运算单元中乘法运算的顺序不一样之外,输入输出数据的顺序也不同。CT蝶形运算单元的输入需要进行比特位翻转操作之后才能输入BF单元,同理GS蝶形运算单元的输出需要进行位反转之后才能输入到下一级的运算中。基于GS和CT不同的蝶形运算单元,设计不同的NTT架构。以8点为例,图2是用Gs实现的8点NTT变换蝶形图。由图2可知,在GS NTT架构中,开始需要对输入数据进行预处理,同时最后一级的BF单元不需要执行乘法操作,相应的,在CT NTT架构中,则一般不需要预处理,但是对于旋转因子的变化则有特殊要求。

以GS蝶形变换图为例,对于n点输入的NTT变换,总共需要进行log

算法4:基于GS单元的NTT算法

相较于流水型NTT结构清晰,层级分明,主要通过流水处理输入数据,并利用延时和多路转接来完成地址控制,本申请的迭代型NTT的架构较为简单,由于仅利用一个蝶形运算单元结构,需要较为复杂的地址控制单元。

本申请的迭代型NTT主要由两个双端口BRAM,蝶形计算单元和地址控制单元组成。其中地址控制部分,本申请与流水型中起始点组的变化相同,每一级按照NTT规律改变起始点组以及每组蝶形运算的点数,通过启动信号控制数据的读出和写入过程。除此之外,由于上述设计利用两个BRAM完成数据的存取,BRAM间的数据传输会造成大量时钟周期的浪费。因此本申请针对数据存取特点,提出了2BRAM交错存取数据的方法,完全消除了BRAM间数据传输的周期浪费,大大优化了迭代型NTT设计的总周期数,具体的电路结构如图1所示。

对于128点输入,与流水型NTT需要数据流水输入不同,为了实现NTT算法中输入数据地址的规律变化,需要先将预处理后的数据悉数存入BRAM单元中,根据双端口BRAM的特点按照起始点组的变化以及每组蝶形运算的点数,同时读取两个通道的数据送入BF单元进行处理。比如,第一级分别将0到63送入上路,而64到127送入下路,第二级则将0到31和64到95送入上路,而将32到63和96到127送入下路。除了起始点组需要按照规律送入BF单元之外,每一级完成后,需要及时更改switch信号用于交替处理BRAM中的存储数据。例如第一级,128个数据从BRAM中读出,在经过BF单元以及模乘运算之后,送入BRAM_TMP单元中,那么在下一级(即第二级)则需要数据从BRAM_TMP输出到BF单元,并且在运算完成后,送入BRAM相应的地址单元中,如此往复,完成共7次迭代过程

针对优化后的迭代型NTT以及MDC流水型NTT的硬件实现,其在FPGA XilinxArtix-7上的实现结果如下。为了方便比较,仅考虑128点的输入下的设计(256点约为128点硬件消耗的两倍),输入用BRAM读取,且设计包含预处理,图4是优化后的迭代型NTT的RTL原理图,在优化后的迭代型NTT中,输入数据经过预处理进入到NTT运算模块中,根据每一级标志信号的变化,完成地址交错变换以及两个BRAM单元的交替存取。

针对优化后的迭代型NTT以及MDC流水型NTT的硬件实现,其在FPGA XilinxArtix-7上的具体实现的RTL原理图如图4所示。其中输入用BRAM读取,且设计包含预处理,表2为本发明与现有设计的资源消耗以及性能表现方面的比较:

表2本发明与现有设计的资源消耗以及性能表现方面的比较结果

经测试,迭代型NTT的硬件资源消耗远小于流水型NTT,并且仅用了1个DSP单元完成设计。相较于流水型,本申请在运算最大频率上提升了约21%,整体资源消耗基本持平。对于传统的迭代型设计,本申请采用双BRAM交错存取数据从而取消了BF大量的等待周期,因此运算总周期数减少了24.1%,资源占用减少了34.4%。

本领域内的技术人员应明白,本申请的实施例可提供为方法、系统、或计算机程序产品。因此,本申请可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本申请可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。本申请实施例中的方案可以采用各种计算机语言实现,例如,面向对象的程序设计语言Java和直译式脚本语言JavaScript等。

本申请是参照根据本申请实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器运行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上运行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上运行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

尽管已描述了本申请的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本申请范围的所有变更和修改。

显然,本领域的技术人员可以对本申请进行各种改动和变型而不脱离本申请的精神和范围。这样,倘若本申请的这些修改和变型属于本申请权利要求及其等同技术的范围之内,则本申请也意图包含这些改动和变型在内。

- 一种光驱交错排列式光存储系统

- 一种物理BRAM匹配方法

- 基于交错时间分区的移动互联网数据存储系统及其方法

- 基于交错时间分区的移动互联网数据存储系统及其方法