一种提高干扰性能的电介质状态检测电路与采用此电路的电设备

文献发布时间:2024-01-17 01:15:20

技术领域

本发明涉及一种检测电路,属于电子技术领域,具体的说是涉及一种提高干扰性能的电介质状态检测电路。

背景技术

检测导电介质的通断或状态是许多设备需要的功能。所述的导电介质可以是一段电介质、一个开关等。

有一个(专利号为CN209764979U和专利名称为一种新型导电介质通断检测电路)的实用新型专利,该专利公开了一种新型导电介质通断检测电路,包含交流电压信号生成电路、导电介质检测信号隔离电路、滤波整形电路及微处理器;所述微处理器分别与所述交流电压信号生成电路及滤波整形电路电连接;所述交流电压信号生成电路与导电介质检测信号隔离电路电连接;所述导电介质检测信号隔离电路与滤波整形电路及待测导电介质电连接;其中,微处理器,用于控制交流电压信号生成电路生成交流电压波和用于根据滤波整形电路的输出信号判断待测导电介质通断与否;所述检测信号隔离电路用于隔离待测导电介质的检测信号;所述滤波整形电路用于将交流电压信号生成电路生成的交流电压波整形为0V以上直流电。

类似以上专利的现有技术有如下问题:微处理器的接受端口总会收到外界干扰信号,微处理器难以区分干扰或对待测电介质的检测返回信号,容易造成错误指示通断。

发明内容

本发明所要解决的技术问题是:在有干扰时,逻辑处理器件(包括微处理器)难以区分干扰信号或对待测电介质的检测响应信号,容易错误判断。

本发明所采用的基本技术方案是:

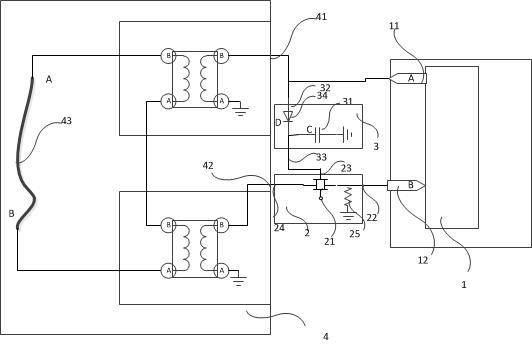

参见图1,一种提高干扰性能的电介质状态检测电路,包含负责对待测试电介质43进行激励与响应的测试回路4,其特征在于:包含逻辑处理器件1、接受控制电路2、激励信号保持电路3;所述逻辑处理器件1的激励端口11、所述激励信号保持电路3的控制输入端口32和所述测试回路4的输入端口41同时电连接,所述激励信号保持电路3的控制输出端口33与所述接受控制电路2的控制输入端口23电连接;所述接受控制电路2的测试输出端口22与所述逻辑处理器件1的接受端口12电连接,所述接受控制电路2的测试输入端口24与所述测试回路的输出端口42电连接;所述激励信号保持电路3的控制输入端口32没有收到所述逻辑处理器件电路1发出的测试激励信号时,所述激励信号保持电路3的控制输出端口33输出代表没有激励信号的特定信号;所述激励信号保持电路3的控制输入端口32收到所述逻辑处理器件电路1发出的测试激励信号时,所述供给激励信号保持电路3的控制输出端口33输出设定时长的代表有激励信号的特定信号;当所述接受控制电路2的控制输入端口23收到所述设定时长的代表有激励信号的特定信号时,所述接受控制电路2的测试输入端口24信号传输到所述接受控制电路2的测试输出端口22端口,进而传送给所述逻辑处理器件1;当所述接受控制电路2的控制输入端口23收到所述代表没有激励信号的特定信号时,所述接受控制电路2的测试输出端口22输出代表没有测试输出的信号,所述代表没有测试输出的信号可以是所述测试回路4的测试输入端口41没有得到测试信号时,测试输出端口42的信号电平,也可以是某一特定的不同的电平。所述逻辑处理器件1根据收到的信号推断出待测电介质的状态。

注1:所述代表有激励信号的特定信号、所述代表没有激励信号的特定信号是实现方案设想的相对量,如一个高电平,另一个就是低电平。

本发明还公开了一种电设备,采用了以上提高干扰性能的电介质状态检测电路,用以检测待测电介质状态。

本发明有益的技术效果是:

通过激励信号控制激励信号保持电路3,进而通过激励信号保持电路3控制接受控制电路2,使得所述逻辑处理器件电路1只在设定时长的时间范围内接受激励信号通过待测电介质而得到的响应信号,而屏蔽设定时间范围之外的信号,可以极大提高抗干扰性能和降低误判率。

附图说明

图1为本发明的激励信号控制接受通道实施例示意图。

具体实施方式

以下将结合附图及实施例,示例性地详细说明本发明的实施方式,借此对本发明如何应用技术手段来解决技术问题,并达成技术效果的实现过程能充分理解并据以实施。

所述激励信号保持电路3的功能是从控制输入端口32接收到激励信号后,激励信号保持电路3的控制输出端口33输出一定时长的打开通道信号,给所述接受控制电路2,当控制输入端口32接收到没有激励信号或收到激励信号的设定一定时长之外,激励信号保持电路3的控制输出端口33输出关闭通道信号。所述一定时长是为了让所述逻辑处理器件电路1接收到自己发出的激励信号通过所述测试回路4的响应信号,又能在所述一定时长之外,屏蔽所述测试回路4的响应信号的影响。

注2:所述打开通道信号与所述关闭通道信号是实现方案设想的相对量,如一个高电平,另一个就是低电平。

所述接受控制电路2的功能是当所述接受控制电路2的控制输入端口23收到所述打开通道信号时,所述接受控制电路2的测试输出端口22输出测试输入端口24的信号;所述接受控制电路2的控制输入端口23收到所述关闭通道信号时,所述接受控制电路2的测试输出端口22输出没有响应输出的信号,或者某一特定的不同其他值的电平。

这样,在所述一定时长内,所述逻辑处理器件1根据收到的信号推断出待测电介质的状态,而不会被所述一定时长之外的所述响应信号干扰。

所述激励信号保持电路3和所述接受控制电路2,对本领域技术人员而言,为实现他们的功能,有大量的可以选用的电路形式。例如激励信号保持电路3可以采用单稳触发器、555集成电路等电路。接受控制电路2可以采用晶闸管控制电路、比较器电路、CMOS门电路、带片选引脚的逻辑电路等。

以下通过实施例1,示意性地介绍本发明的工作过程,没有限定所采用的电路形式。基于本发明的目的和工作过程的相应的电路形式,都在本专利的保护范围。

实施例1:

激励信号控制接受通道方案,参见图1的电路图的连接,在发明内容中已经非常详细的介绍,下面就具体的电路和工作流程做一些补充。

所述激励信号保持电路3包括二极管34和电容31,电容31一端接信号地,激励信号的高电平通过二极管34给电容31充电至高电平,以后即使激励信号变成低电平,电容C放电到某一阈值之下,会有一段时间,此时间就是以上所述的一定时长。所以,在有激励信号时,所述激励信号保持电路3的控制输出端口33会维持一定时长的高电平。没有激励信号或激励信号后的一定时长之外,所述激励信号保持电路3的控制输出端口33是低电平。

所述接受控制电路2包括一个CMOS门器件21,接受控制电路2的控制输入端口23与CMOS门器件21的控制集电连接。当接受控制电路2的控制输入端口23处于高于阈值的高电平时,CMOS门器件21导通,使得测试输出端口22与测试输入端口24相互导通。当接受控制电路2的控制输入端口23处于低电平时,CMOS门器件21关闭,测试输出端口22与测试输入端口24相互没有关系,测试输出端口22通过下拉电阻置为低电平。本实施例中,所述测试回路4,测试激励信号是交变的信号,有激励信号时的响应信号为交变的信号,没有激励信号时的响应信号为低电平。

所述测试回路4,在本案例中采用双隔离变压器的方案。本发明对所述测试回路4并没有限定,满足本发明思路的测试回路设计都是可以的。

所述逻辑处理器件电路1可以是处理器、FPGA、CPLD或者常规逻辑电路单元。即使是用纯逻辑器件组成的电路,作为单片机的一个硬纯件外设,减轻单片机程序负担,也是可以的。

所述逻辑处理器件1产生某一设定电平的信号或者交变的信号,交变的信号可以是矩形波或正弦波或者某种交变波形,交变信号的频率等参数适配电路而定。

以上所述仅为本发明的优选实施例而已,示意性地说明本发明,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种交流供电设备的备电系统、电路板及备电方法

- 一种检测电路和方法、开关控制电路以及反激变换电路

- 一种隔离型电介质状态检测电路与采用此电路的电设备

- 一种隔离型电介质通断检测电路与采用此电路的电设备