具宽输出电压范围的充电式电荷泵浦

文献发布时间:2023-06-19 09:26:02

技术领域

本公开提供一种具宽输出电压范围的充电式电荷泵浦。当充电式电荷泵浦工作于预设状态时,泵浦电容的顶板电连接于供电输入端并与输出端相隔离,而泵浦电容的底板电连接于接地端并与输出端相隔离。当充电式电荷泵浦被上脉冲信号触发时,泵浦电容的顶板与供电输入端相隔离并电连接于输出端,而泵浦电容的底板电连接于供电输入端并与接地端及输出端相隔离。当充电式电荷泵浦被下脉冲信号触发时,泵浦电容的顶板电连接于接地端并与供电输入端及输出端相隔离,而泵浦电容的底板与接地端相隔离并电连接于输出端。

背景技术

传统上用于频率合成器(PLL)的电荷泵浦包含一对电流镜(current mirror)装置,以将固定大小的电流引入回路滤波器中,其中电流镜装置是被所接收的上脉冲信号(uppulse signal)或下脉冲信号(down pulse signal)触发而作动。这种电荷泵浦因其线性特征及低噪性能而被广泛运用于各种模拟PLL应用中。然而,这种电荷泵浦的性能易受到各种固有非线性效应(例如电流不匹配、电荷注入、时钟馈通等效应)影响,且需要极精细的电路布局来避免大电流镜装置之间的任何不匹配。此外,实际可用的线性输出电压范围为总供应范围(即自接地端电压(0V)至供电电位(VDD))的子集,且通常小于VDD的70%。再者,层叠式的常态电流支路更进一步限制了实际可用的输出电压范围及最小供电电压。

另外,在PLL应用环境中,电荷泵浦中的电流(或电荷)不匹配将直接导致PLL输出频谱中产生参考突波(reference spur)。因此,具电流镜的电荷泵浦多采用高增益的辅助反馈回路,以精确匹配上下电流的大小。这种实施方式示例于图1中,如图1所示,电荷泵浦需具有轨对轨输入/输出范围放大器(rail-to-rail input/output range amplifier),并包含持续开通的复制偏路(replica bias path)。即便电荷泵浦处于闲置状态时(即电荷泵浦未接收到脉冲输入),复制偏路仍需维持开通。因此,现有具电流镜的电荷泵浦的复杂度明显较高,且其所需的电源及空间亦明显较大。

而为了有效抑制电荷泵浦的非线性效应,Schober的专利案US8525564B2提出一种充电式电荷泵浦。如图2所示,电荷泵浦被所接收的上/下脉冲输入触发时,泵浦电容的电荷(理论上被充电至VDD)分摊至负载电容,这种电容电荷的重分配设计有助于提升匹配性能并减少所消耗的电能。然而,由于电容电荷的重分配,这种充电式电荷泵浦的可用线性输出电压范围将比一般的电荷泵浦更低。

有鉴于此,本公开提出一种新颖的充电式电荷泵浦结构,其兼具前述的现有电荷泵浦的所有优点,并同时将输出电压范围扩展到-0.84·VDD至1.82·VDD,且其近似的线性输出电压范围亦扩展到~-0.7·VDD至~1.4·VDD。此宽输出电压范围适用于需要宽调制范围的压控振荡器(voltage-controlled oscillator,VCO)或PLL。此外,其稳态涟波大小小于饱和输出电压(即-0.84·VDD或1.82·VDD)的0.03%,且电荷泵浦的响应不受任何记忆效应所影响。因此,本公开的充电式电荷泵浦适用于可利用其负偏压电位或高于供电电压的正偏压电位的各种应用环境(例如射频天线器)。

发明内容

本公开的目的在于提供一种充电式电荷泵浦,其是由标准供电电位(VDD)进行供电,充电式电荷泵浦提供自-0.84·VDD至1.82·VDD的输出电压范围,故可拓展其操作范围而避免受电源供应所限制。同时,近似的线性输出电压范围扩展到~-0.7·VDD至~1.4·VDD,据此可提供总可用范围宽至~2.1·VDD的输出电压给PLL或其他工作于电荷泵浦传输特性的线性范围内的应用电路。此外,充电式电荷泵浦的传输特性不受任何记忆效应所影响,使得电位转换的间隔时间不受当前电荷泵浦的状态所影响。

为达上述目的,本公开提供一种充电式电荷泵浦。充电式电荷泵浦包含供电输入端、接地端、输出端、泵浦电容、第一NMOS、正保持子电路、第一动态基体偏压产生器、正电荷传输子电路、第一静态基体偏压产生器、第一PMOS、负保持子电路、第二动态基体偏压产生器、负电荷传输子电路、第二静态基体偏压产生器及数字逻辑电路。供电输入端架构于接收处于供电电位(VDD)的供电输入电压。接地端的电位为0V。输出端架构于输出输出电压。泵浦电容包含顶板及底板。第一NMOS电连接于接地端与顶板之间。正保持子电路电连接于供电输入端与顶板之间。第一动态基体偏压产生器电连接于正保持子电路。正电荷传输子电路电连接于顶板与输出端之间。第一静态基体偏压产生器电连接于正电荷传输子电路及顶板。第一PMOS电连接于供电输入端与底板之间。负保持子电路电连接于接地端与底板之间。第二动态基体偏压产生器电连接于负保持子电路。负电荷传输子电路电连接于底板与该输出端之间。第二静态基体偏压产生器电连接于负电荷传输子电路及底板。数字逻辑电路架构于接收上脉冲信号及下脉冲信号,并输出多个开关信号,以控制与数字逻辑电路电连接的第一NMOS、正保持子电路、第一动态基体偏压产生器、正电荷传输子电路、第一静态基体偏压产生器、第一PMOS、负保持子电路、第二动态基体偏压产生器、负电荷传输子电路及第二静态基体偏压产生器,使输出电压的范围为-0.84·VDD至1.82·VDD。当充电式电荷泵浦工作于预设状态时,泵浦电容的顶板电连接于供电输入端并与输出端相隔离,而泵浦电容的底板电连接于接地端并与输出端相隔离。当充电式电荷泵浦被上脉冲信号触发时,泵浦电容的顶板与供电输入端相隔离并电连接于输出端,而泵浦电容的底板电连接于供电输入端并与接地端及输出端相隔离。当充电式电荷泵浦被下脉冲信号触发时,泵浦电容的顶板电连接于接地端并与供电输入端及输出端相隔离,而泵浦电容的底板与接地端相隔离并电连接于输出端。

附图说明

图1为现有具电流镜结构的电荷泵浦的电路结构示意图。

图2为现有充电式电荷泵浦的电路结构示意图。

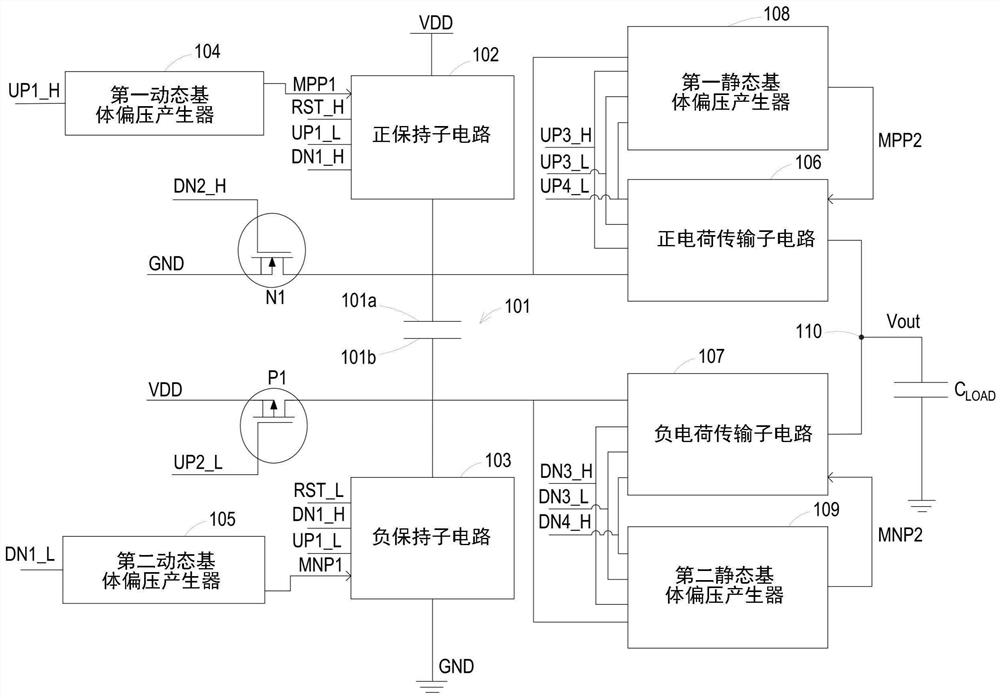

图3A及图3B为本公开优选实施例的充电式电荷泵浦的电路结构示意图。

图4为三态相位频率检测器的典型输出波形示意图。

图5为图3B的数字逻辑电路的逻辑电路结构示意图。

图6为图5的上脉冲信号、下脉冲信号及致动信号在充电式电荷泵浦的三种不同状态下的波形示意图。

图7为图5的开关缓冲器的电路结构示意图。

图8为图7中的各个信号的波形示意图。

图9及图10示出在充电式电荷泵浦被上脉冲信号或下脉冲信号触发时,上脉冲信号及下脉冲信号与其对应的致动信号及开关信号的波形。

图11为本公开的充电式电荷泵浦的细节元件的电路结构示意图。

图12为本公开的充电式电荷泵浦与典型的三态相位频率检测器的方框示意图。

图13A及图13B为图12中的参考信号、反馈信号、上脉冲信号及下脉冲信号的波形示意图。

图14A为对应图13A中的上脉冲信号的输出电压及稳定输出电压的电压涟波的波形示意图。

图14B为对应图13B中的下脉冲信号的输出电压及稳定输出电压的电压涟波的波形示意图。

图15为结合图14A及图14B所示波形的示意图。

图16A及图16B为具有一连串交互的上脉冲信号及下脉冲信号的测试波形示意图。

图17A及图17B分别为对应图16A及图16B的测试波形的输出电压的波形示意图。

附图标记说明:

101:泵浦电容

101a:顶板

101b:底板

102:正保持子电路

103:负保持子电路

104:第一动态基体偏压产生器

105:第二动态基体偏压产生器

106:正电荷传输子电路

107:负电荷传输子电路

108:第一静态基体偏压产生器

109:第二静态基体偏压产生器

110:输出端

111:数字逻辑电路

21、22、26:差分缓冲器

23、24、25:及闸

27、28:开关缓冲器

271:初级时钟分配器

272:第一次级时钟分配器

273:第二次级时钟分配器

UPO_H、UPO_L、DNO_H、DNO_L:差分信号

RESET_ACTIVE、UP_ACTIVE、DN_ACTIVE:致动信号

RST_H、RST_L、UP1_H、UP1_L、UP2_H、UP2_L、UP3_H、UP3_L、UP4_H、UP4_L、DN1_H、DN1_L、DN2_H、DN2_L、DN3_H、DN3_L、DN4_H、DN4_L:开关信号

UP_IN1:第一内部信号

UP_IN2:第二内部信号

Tdly1、Tdly2:延迟时间

VDD:供电电位

GND:接地端

UP:上脉冲信号

DN:下脉冲信号

Vout:输出电压

C

N1、N2、N3、N4、N5、N6、N7、N8、N9、N10、N11、N12、N13、N14、N15:NMOS

P1、P2、P3、P4、P5、P6、P7、P8、P9、P10、P11、P12、P13、P14、P15:PMOS

MPP1:第一节点

MNP1:第二节点

MPP2:第三节点

MNP2:第四节点

V

2:三态相位频率检测器

REF_IN:参考信号

DIV_IN:反馈信号

T

T

具体实施方式

体现本公开特征与优点的一些典型实施例将在后段的说明中详细叙述。应理解的是本公开能够在不同的实施方式上具有各种的变化,其皆不脱离本公开的范围,且其中的说明及图示在本质上当作说明之用,而非架构于限制本公开。

图3A及图3B为本公开优选实施例的充电式电荷泵浦的电路结构示意图。如图3A及图3B所示,充电式电荷泵浦包含供电输入端、0V的接地端(GND)、输出端110、泵浦电容101、第一NMOS(N-type Metal-Oxide-Semiconductor,N型金属氧化物半导体)N1、第一PMOS(P-type Metal-Oxide-Semiconductor,P型金属氧化物半导体)P1、正保持子电路102、负保持子电路103、第一动态基体偏压产生器104、第二动态基体偏压产生器105、正电荷传输子电路106、负电荷传输子电路107、第一静态基体偏压产生器108、第二静态基体偏压产生器109及数字逻辑电路111。供电输入端架构于接收处于供电电位(VDD)的供电输入电压。输出端110架构于输出一输出电压Vout,且输出端110可例如但不限于与输出负载电容C

第一动态基体偏压产生器104动态地产生升压正电位,并提供至正保持子电路102中的PMOS装置,第二动态基体偏压产生器105动态地产生降压负电位,并提供至负保持子电路103中的NMOS装置。第一静态基体偏压产生器108持续地提供最高的正电位至正电荷传输子电路106中的PMOS装置,第二静态基体偏压产生器109持续地提供最低的负电位至负电荷传输子电路107中的NMOS装置。

本公开的充电式电荷泵浦工作于下列三种模式:

(1)充电式电荷泵浦处于预设状态,于此状态下,电荷泵浦未接收到任何高准位的上脉冲信号UP或下脉冲信号DN,且输出电压Vout保持不变;

(2)充电式电荷泵浦被上脉冲信号UP触发,使得输出电压Vout上升,直至饱和于1.82·VDD的电位;以及

(3)充电式电荷泵浦被下脉冲信号DN触发,使得输出电压Vout下降,直至饱和于-0.84·VDD的电位。

充电式电荷泵浦的详细作动示例说明如下。

当充电式电荷泵浦处于预设状态时,正保持子电路102将顶板101a与供电输入端相连接,负保持子电路103将底板101b电连接于接地端,泵浦电容101对应被充电至供电电位VDD,其中泵浦电容101的顶板101a的电位为VDD,泵浦电容101的底板101b的电位为0V。此外,正电荷传输子电路106及负电荷传输子电路107分别将顶板101a及底板101b与输出端110相隔离。

当充电式电荷泵浦被上脉冲信号UP触发时,正保持子电路102将顶板101a与供电输入端相隔离,底板101b通过第一PMOS P1与供电输入端电连接,使顶板101a的电位提升至~2·VDD。随即开通正电荷传输子电路106而使顶板101a与输出端110相连接。因此,泵浦电容101与负载电容C

当充电式电荷泵浦被下脉冲信号DN触发时,负保持子电路103将底板101b与接地端相隔离,顶板101a通过第一NMOS N1与接地端电连接,使底板101b的电位下降至~–VDD。随即开通负电荷传输子电路107而使底板101b与输出端110相连接。因此,泵浦电容101与负载电容C

本公开为实现充电式电荷泵浦的电路层级结构及其相应作动方式,克服了多项设计难题。首先,当充电式电荷泵浦处于预设状态时,须持续隔离输出端与泵浦电容101的顶板101a或底板101b之间的电连接,且于输出电压Vout处在-0.84·VDD至1.82·VDD的范围内,皆须持续保持隔离。其次,当充电式电荷泵浦被上脉冲信号UP触发时,电位被提升至~2·VDD的顶板101a须与电位为VDD的供电输入端相隔离,同理,当充电式电荷泵浦被下脉冲信号DN触发时,电位被降低至~-VDD的底板101b须与接地端相隔离。此外,在电荷泵浦的全部工作范围内,均须确保寄生PN接面二极管(在CMOS工艺中产生于NMOS及PMOS装置内)维持逆偏(即关断)。另外,需确保所有开关事件均无相互重叠,并使电荷的重分配以预设顺序进行,据此令击穿电流(shoot-through current)最小化。

本公开的特定电路设计(将于后段具体说明)是用以使所有可能的p-n接面二极管在充电式电荷泵浦的工作范围内均保持关断。数字逻辑电路111以特定顺序产生多个开关信号,且于任两个开关事件之间均具有一间隔时间,借此避免电荷损耗并确保充电式电荷泵浦以高电荷传输效率持续运行。

图4为三态相位频率检测器的典型输出波形示意图。图5为图3B的数字逻辑电路的逻辑电路结构示意图。图6为图5的上脉冲信号、下脉冲信号及致动信号在充电式电荷泵浦的三种不同状态下的波形示意图。充电式电荷泵浦的数字逻辑电路111优选但不限于自三态相位频率检测器接收上脉冲信号UP及下脉冲信号DN。如图4及图6所示,于一段时间内,上脉冲信号UP及下脉冲信号DN均处于高准位,因此,无法直接缓冲上脉冲信号UP及下脉冲信号DN来产生所需的开关信号。如图5所示,数字逻辑电路111包含三个差分缓冲器(21、22、26)、三个及(AND)闸(23、24、25)及两个开关缓冲器(27、28)。差分缓冲器(21、22、26)根据对应的输入信号产生两个异相差分信号,其中该两个异相差分信号所导致的总延迟时间相同。为除去上脉冲信号UP与下脉冲信号DN间的重叠,首先,利用两个差分缓冲器21及22将上脉冲信号UP及下脉冲信号DN划分为四个差分信号UPO_H、UPO_L、DNO_H及DNO_L。接着,利用三个及闸23、24及25根据四个差分信号UPO_H、UPO_L、DNO_H及DNO_L提取出三个致动信号RESET_ACTIVE、UP_ACTIVE及DN_ACTIVE。差分缓冲器26电连接于及闸23,以接收致动信号RESET_ACTIVE,且差分缓冲器26输出两个开关信号RST_H及RST_L。开关缓冲器27电连接于及闸24,以接收致动信号UP_ACTIVE,且开关缓冲器27输出四组开关信号UP1_H/UP1_L、UP2_H/UP2_L、UP3_H/UP3_L及UP4_H/UP4_L。开关缓冲器28电连接于及闸25,以接收致动信号DN_ACTIVE,且开关缓冲器28输出四组开关信号DN1_H/DN1_L、DN2_H/DN2_L、DN3_H/DN3_L及DN4_H/DN4_L。

当上脉冲信号UP及下脉冲信号DN均为低准位时,致动信号RESET_ACTIVE为高准位,其代表充电式电荷泵浦处于预设状态。当上脉冲信号UP为高准位且下脉冲信号DN为低准位时,致动信号UP_ACTIVE为高准位。同理,当上脉冲信号UP为低准位且下脉冲信号DN为高准位时,致动信号DN_ACTIVE为高准位。如图6所示,其举例示出了三个致动信号RESET_ACTIVE、UP_ACTIVE及DN_ACTIVE在充电式电荷泵浦的三种不同状态下的对应波形。

图7为图5的开关缓冲器的电路结构示意图。图8为图7中的各个信号的波形示意图。以开关缓冲器27为例,如图7所示,开关缓冲器27包含初级时钟分配器271、第一次级时钟分配器272及第二次级时钟分配器273。初级时钟分配器271电连接于及闸24,以接收图5所示的致动信号UP_ACTIVE,且初级时钟分配器271依据致动信号UP_ACTIVE输出第一内部信号UP_IN1及第二内部信号UP_IN2。第一次级时钟分配器272电连接于初级时钟分配器271,以接收第一内部信号UP_IN1,且第一次级时钟分配器272依据第一内部信号UP_IN1输出四个开关信号UP3_H、UP3_L、UP4_H及UP4_L。第二次级时钟分配器273电连接于初级时钟分配器271,以接收第二内部信号UP_IN2,且第二次级时钟分配器273依据第二内部信号UP_IN2输出四个开关信号UP2_L、UP2_H、UP1_H及UP1_L。

众所皆知的是,时钟分配器的架构可使同相输出与异相输出在传输逻辑0及逻辑1时产生不同程度地路径延迟,故时钟分配器(271、272、273)可输出不具相互重叠的边沿的两个异相输出信号,其中两输出信号的边沿之间的相对相位差是由输入信号间的相对延迟所决定。初级时钟分配器271的延迟元件的数量为两次级时钟分配器272及273的延迟元件的数量的两倍。如图8所示,延迟时间Tdly1约略为延迟时间Tdly2的两倍,故可确保开关信号UP1_H/UP1_L与开关信号UP2_H/UP2_L之间、开关信号UP2_H/UP2_L与开关信号UP3_H/UP3_L之间以及开关信号UP3_H/UP3_L与开关信号UP4_H/UP4_L之间皆具有相同的相位差。借此,开关缓冲器27以特定顺序产生四组开关信号,且非同组开关信号的边沿相互不重叠。开关缓冲器28的元件是与开关缓冲器27相似,故于此不再赘述。

当充电式电荷泵浦被上脉冲信号UP触发时,上脉冲信号UP、致动信号UP_ACTIVE及其对应开关信号的波形图是如图9所示。而当充电式电荷泵浦被下脉冲信号DN触发时,下脉冲信号DN、致动信号DN_ACTIVE及其对应开关信号的波形图如图10所示。

图11为本公开的充电式电荷泵浦的细节元件的电路结构示意图。如图11所示,正保持子电路102包含第二PMOS P2、第三PMOS P3、第四NMOS N4及第五NMOS N5。负保持子电路103包含第二NMOS N2、第三NMOS N3、第四PMOS P4及第五PMOS P5。第一动态基体偏压产生器104包含第六NMOS N6及第一节点MPP1。第二动态基体偏压产生器105包含第六PMOS P6及第二节点MNP1。正电荷传输子电路106包含第七PMOS P7、第八PMOS P8、第九PMOS P9及第十三NMOS N13。负电荷传输子电路107包含第七NMOS N7、第八NMOS N8、第九NMOS N9及第十三PMOS P13。第一静态基体偏压产生器108包含第十PMOS P10、第十一PMOS P11、第十二PMOS P12、第十四NMOS N14、第十五NMOS N15及第三节点MPP2。第二静态基体偏压产生器109包含第十NMOS N10、第十一NMOS N11、第十二NMOS N12、第十四PMOS P14、第十五PMOSP15及第四节点MNP2。

充电式电荷泵浦的整体运行可归类为三种工作状态,即分别为处于预设状态的充电式电荷泵浦、被上脉冲信号UP触发的充电式电荷泵浦以及被下脉冲信号DN触发的充电式电荷泵浦。

当充电式电荷泵浦处于预设状态时,第四NMOS N4及第四PMOS P4分别被开关信号RST_H及RST_L所开通,使第二PMOS P2的栅极及第二NMOS N2的栅极的电位分别维持于接地(即0V)及VDD,进而使第二PMOS P2及第二NMOS N2导通,且泵浦电容101被充电至供电电位VDD,其中顶板101a的电位为VDD,底板101b的电位为0V。

至于正电荷传输子电路106,于预设状态下,开关信号UP3_L及UP4_L处于高逻辑准位,开关信号UP3_H处于低逻辑准位。由于第十三NMOS N13保持开通且其栅极及源极连接于VDD,故第九PMOS P9的栅极维持在高电位。正电荷传输子电路106架构于将输出端110与泵浦电容101的顶板101a相隔离,正电荷传输子电路106的运行可依据自输出电压范围所拆分的三个区段进行分析,该三个区段定义如下:

(1)Vout (2)VDD-|V (3)Vout>VDD+|V 于区段(1)中,第八PMOS P8导通,使得第七PMOS P7的栅极连接于VDD并关断第七PMOS P7。于区段(2)中,第八PMOS P8及第九PMOS P9关断,第七PMOS P7的栅极的电位维持于VDD,且不产生电荷漏泄。于区段(3)中,第九PMOS P9导通,第七PMOS P7的栅极连接于输出端110。借此,于预设状态下,可确保第七PMOS P7在输出电压Vout的全部范围内(即-0.84·VDD至1.82·VDD)均维持关断。 至于负电荷传输子电路107,于预设状态下,开关信号DN3_L处于高逻辑准位,开关信号DN3_H及DN4_H处于低逻辑准位。由于第十三PMOS P13保持开通,故第九NMOS N9的栅极维持在低电位。负电荷传输子电路107架构于将输出端110与泵浦电容101的底板101b相隔离,负电荷传输子电路107的运行可依据自输出电压范围所拆分的三个区段进行分析,该三个区段定义如下: (4)Vout>V (5)-|V (6)Vout<-|V 于区段(4)中,第八NMOS N8导通,使得第七NMOS N7的栅极接地并关断第七NMOSN7。于区段(5)中,第八NMOS N8及第九NMOS N9关断,第七NMOS N7的栅极维持接地,且不产生电荷漏泄。于区段(6)中,第九NMOS N9导通,第七NMOS N7的栅极连接于输出端110。借此,于预设状态下,可确保第七NMOS N7在输出电压Vout的全部范围内(即-0.84·VDD至1.82·VDD)均维持关断。 因此,当充电式电荷泵浦处于预设状态时,第七PMOS P7及第七NMOS N7在输出电压Vout的全部范围内(即-0.84·VDD至1.82·VDD)均维持关断,故可隔绝输出端110与泵浦电容101的顶板101a及底板101b之间的电连接。 当充电式电荷泵浦被上脉冲信号UP触发时,首先,开关信号RST_H及开关信号RST_L分别为低准位及高准位,分别使第四PMOS P4及第四NMOS N4关断。接着,开关信号UP1_L降至低准位,使得正保持子电路102中的第三PMOS P3及负保持子电路103中的第五PMOS P5导通,进而使第二PMOS P2的栅极与漏极相连接,并迫使第二PMOS P2的栅极处于低电位。由于第二PMOS P2及第二NMOS N2皆关断,故可使顶板101a及底板101b分别与供电输入VDD及接地端相隔离。于开关过渡期中,在开关信号UP1_H升至高准位时,第一节点MPP1上由持续导通的第六NMOS N6所致的预设高电位会被提升VDD的大小。而后,第一PMOS P1被开关信号UP2_L导通,因而将底板101b连接于供电输入端,并将顶板101a的电位提升至~2·VDD。由于第三PMOS P3已被导通,故第二PMOS P2的栅极接收顶板101a中为~2·VDD的升高电位。借此,第二PMOS P2保持关断,顶板101a保持与电位为VDD的供电输入端相隔离。同时,因第一节点MPP1连接于第二PMOS P2及第三PMOS P3的基体,故在充电式电荷泵浦被上脉冲信号UP触发的期间内,第一节点MPP1上被提升的电位可避免该两个PMOS装置的漏极-基体p-n接面二极管在顶板101a的电位提升时产生顺偏。 于电荷传输过程中,开关信号UP3_L为低准位,使得第八PMOS P8关断,开关信号UP3_H为高准位,使得第九PMOS P9的栅极的预设高电位提升VDD的大小,并进而关断第九PMOS P9。于一段有限时间后,开关信号UP4_L降至低准位,致使第七PMOS P7的栅极的电位下降VDD的大小,进而开通第七PMOS P7,使正电荷可通过第七PMOS P7的漏极。当充电式电荷泵浦回到预设状态时,首先,开关信号UP4_L升至高准位,使得第七PMOS P7关断。接着,开关信号UP3_H及UP3_L分别降至低准位及升至高准位。如图9所示,由数字逻辑电路111中的时钟分配器产生的特定开关顺序可确保第七PMOS P7仅在第八PMOS P8及第九PMOS P9皆关断时处于导通状态。 第一静态基体偏压产生器108为正电荷传输子电路106的复制电路,且其输出端位于第三节点MPP2,其中第三节点MPP2连接于正电荷传输子电路106的PMOS装置P7、P8及P9的基体。在预设状态下,第十五NMOS N15的栅极及源极连接于VDD,使得第三节点MPP2上具有较高电压。当充电式电荷泵浦被上脉冲信号UP触发时,第一静态基体偏压产生器108将随着正电荷传输子电路106一同被致动,通过开关信号UP4_L开通第十PMOS P10,第一静态基体偏压产生器108位于第三节点MPP2的输出端电连接于顶板101a。因此,一旦输出电压Vout跨越第三节点MPP2上由持续导通的第十五NMOS N15所致的预设高电位,第三节点MPP2接收输出电压Vout并具有与之相同的电位。据此,第三节点MPP2的电位追随并保持于充电式电荷泵浦中为稳态且最高的正电位,并将第三节点MPP2上的电位作为基体偏压提供至PMOS装置P7、P8及P9。由于PMOS装置的基体几近不存在电荷泄漏,故第三节点MPP2上的正电位可存储于电容C12,且不受输出电压Vout变化的影响。借此,在电荷泵浦的整体运行范围内,均可确保PMOS装置P7、P8及P9的p-n接面二极管保持关断。 当充电式电荷泵浦被上脉冲信号UP触发时,负电荷传输子电路107保持与预设状态相近的状态,且第七NMOS N7维持关断,以将底板101b与输出端110相隔离。 当充电式电荷泵浦被下脉冲信号DN触发时,首先,开关信号RST_H及RST_L分别为低准位及高准位,使得第四NMOS N4及第四PMOS P4关断。接着,开关信号DN1_H升为高准位,致使第三NMOS N3导通,并将第二NMOS N2的栅极与漏极相连接,同时,第五NMOS N5导通,使得第二PMOS P2的栅极处于高电位。由于第二NMOS N2及第二PMOP P2均关断,故泵浦电容101的顶板101a及底板101b分别与供电输入VDD及接地端相隔离。与此同时,因开关信号DN1_L降至低准位,故第二节点MNP1上由持续导通的第六PMOS P6所致的预设低电位会被降低VDD的大小。而后,第一NMOS N1被开关信号DN2_H导通,使得顶板101a连接于接地端,并将底板101b的电位降低至~-VDD。由于第三NMOS N3被导通,故第二NMOS N2的栅极接收底板101b上降至~-VDD的负电位。借此,第二NMOS N2保持关断,底板101b与接地端相隔离。同时,因第二节点MNP1连接于第二NMOS N2及第三NMOS N3的基体,故在充电式电荷泵浦被下脉冲信号DN触发的期间内,第二节点MNP1上被降低的电位可避免该两个NMOS装置的漏极-基体p-n接面二极管在底板101b的电位降低时产生顺偏。 于电荷传输过程中,开关信号DN3_H为高准位,使得第八NMOS N8关断,开关信号DN3_L为低准位,因而将第九NMOS N9的栅极的预设低电位降低VDD的大小,进而关断第九NMOS N9。于一段有限时间后,开关信号DN4_H升至高准位,致使第七NMOS N7的栅极电位提升VDD,进而导通第七NMOS N7,且负电荷可自底板101b被传输至输出端110。当充电式电荷泵浦回到预设状态时,首先,开关信号DN4_H升至高准位,使得第七NMOS N7关断。接着,开关信号DN3_H及DN3_L分别降至低准位及升至高准位。如图10所示,由数字逻辑电路111中的时钟分配器产生的特定开关顺序可确保第七NMOS N7仅在第八NMOS N8及第九NMOS N9皆关断时处于导通状态。 NMOS装置N7、N8及N9的基体偏压是由第二静态基体偏压产生器109提供,其中第二静态基体偏压产生器109为负电荷传输子电路107的复制电路,且其输出端连接于第四节点MNP2。在预设状态下,第十五PMOS P15的栅极及源极连接于接地端,使得第四节点MNP2上具有较低电压。当充电式电荷泵浦被下脉冲信号DN触发时,一旦输出电压Vout低于第四节点MNP2上预设的初始低电压,第四节点MNP2将接收输出电压Vout并具有与之相同的电位。据此,第四节点MPP2的电位追随并保持于充电式电荷泵浦中为稳态且最低的负电位,故在电荷泵浦的整体运行范围内,均可确保NMOS装置N7、N8及N9的p-n接面二极管保持关断。 当充电式电荷泵浦被下脉冲信号DN触发时,正电荷传输子电路106保持与预设状态相近的状态,且第七PMOS P7维持关断,以将顶板101a与输出端110相隔离。 本公开的充电式电荷泵浦是运用多样电路设计技术,使得充电式电荷泵浦的输出电压Vout的范围可拓展为-0.84·VDD至1.82·VDD,其中各项电路设计技术摘要如下。 首先,包括N6、N13、N14及N15的各个NMOS装置被设定为具有低临界电压(低V 另外,正保持子电路102中的PMOS装置的基体偏压是由第一动态基体偏压产生器104提供,负保持子电路103中的NMOS装置的基体偏压是由第二动态基体偏压产生器105提供。当充电式电荷泵浦被上脉冲信号UP触发时,第一动态基体偏压产生器104的第一节点MPP1的预设高电位提升VDD的大小,连接于PMOS装置P2及P3的基体的第一节点MPP1因而可于此期间内提供动态上升的基体偏压至该些PMOS装置。反之,当充电式电荷泵浦被下脉冲信号DN触发时,第二动态基体偏压产生器105的第二节点MNP1的预设低电位降低VDD的大小,连接于NMOS装置N2及N3的基体的第二节点MNP1因而可于此期间内提供动态下降的基体偏压至该些NMOS装置。 再者,正电荷传输子电路106中的PMOS装置的基体偏压是由第一静态基体偏压产生器108提供,负电荷传输子电路107中的NMOS装置的基体偏压是由第二静态基体偏压产生器109提供。当充电式电荷泵浦被上脉冲信号UP触发时,一旦输出电压Vout高过第三节点MPP2的初始高电位,则第一静态基体偏压产生器108的输出亦将随输出电压Vout改变。因此,不论实时输出电压Vout的大小为何,第三节点MPP2均可提供稳定状态下的最高正电位至PMOS装置P7、P8及P9。当充电式电荷泵浦被下脉冲信号DN触发时,一旦输出电压Vout低于第四节点MNP2的初始低电位,则第二静态基体偏压产生器109的输出亦将随输出电压Vout改变。因此,不论实时输出电压Vout的大小为何,第四节点MNP2均可提供稳定状态下的最低负电位至NMOS装置N7、N8及N9。 更甚者,数字逻辑电路111可实现特定的开关顺序,并避免在电荷传输过程中的多个开关事件相互重叠,借此可消除电荷损耗的可能。举例而言,仅有在连接于第七PMOS P7或第七NMOS N7的栅极的PMOS装置或NMOS装置关断的期间内,第七PMOS P7或第七NMOS N7才会导通。借此使输出电压Vout保持与泵浦电容101的顶板101a及底板101b相隔离。 图12为本公开的充电式电荷泵浦与典型的三态相位频率检测器的方框示意图。图13A及图13B为图12中的参考信号、反馈信号、上脉冲信号及下脉冲信号的波形示意图。如图12所示,其是以典型的三态相位频率检测器2印证充电式电荷泵浦的运行。三态相位频率检测器2接收参考信号REF_IN及反馈信号DIV_IN,并输出上脉冲信号UP及下脉冲信号DN,充电式电荷泵浦电连接于三态相位频率检测器2,以接收上脉冲信号UP及下脉冲信号DN。如图13A所示,当参考信号REF_IN的相位超前反馈信号DIV_IN的相位ΔΦ秒时,上脉冲信号UP处于高准位,而在下脉冲信号DN短暂升至高准位的期间内(维持一重置时间T 图15为结合图14A及图14B所示波形的示意图。如图15所示,本公开的充电式电荷泵浦的总输出电压范围大于供电电位VDD的2.6倍。如以供电电位VDD为标准,则输出电压Vout的近似线性范围可扩展到~-0.7·VDD至~1.4·VDD,因此,本公开的充电式电荷泵浦的近似线性输出电压范围亦大于供电电位VDD的2倍。 为提升充电式电荷泵浦的适用性,需使其传输特性不受任何记忆效应所影响,这意味着在相同运行参数的条件下,由任一电位转换至另一电位的间隔时间不受当前电荷泵浦的状态所影响。于图16A及图16B中是通过输入一连串交互的上脉冲信号UP及下脉冲信号DN至充电式电荷泵浦来证实其传输特征不受记忆效应所影响。图16A及图16B为具有一连串交互的上脉冲信号及下脉冲信号的测试波形示意图。任一由上脉冲信号UP或下脉冲信号DN所致的触发维持一段时间,并足以使充电式电荷泵浦的输出电压在下一触发点前达到饱和。图17A及图17B分别为对应图16A及图16B的测试波形的输出电压的波形示意图。如图17A及图17B中所示,于此示例中,无论充电式电荷泵浦自t=0的时刻启动或是已达到过-0.84·VDD,输出电压Vout自0V升至1.6V所耗费的时间均相同。同样地,无论充电式电荷泵浦自t=0的时刻启动或是已达到过1.82·VDD,输出电压Vout自0V降至-0.8V所耗费的时间均相同。由此可证,充电式电荷泵浦的输出响应明显不存在记忆效应。 综上所述,本公开提供一种具宽输出电压范围的充电式电荷泵浦,当充电式电荷泵浦由标准供电电位(VDD)进行供电时,充电式电荷泵浦的输出电压范围为-0.84·VDD至1.82·VDD。同时,相较于现有的电荷泵浦,本公开的近似的线性输出电压范围以及可用的线性输出电压范围均有所扩展。此外,数字逻辑电路以特定顺序产生多个开关信号,并避免在电荷传输过程中的多个开关事件相互重叠,借此可防止电荷损耗并确保并确保充电式电荷泵浦以高电荷传输效率持续运行。另外,充电式电荷泵浦的传输特性不受任何记忆效应所影响。再者,当输出电压饱和于-0.84·VDD/1.82·VDD时,稳定输出电压仅具有极小的涟波,其涟波的峰对峰值低于对应稳定输出电压的0.03%。 须注意,上述仅是为说明本公开而提出的优选实施例,本公开不限于所述的实施例,本公开的范围由权利要求决定。且本公开得由本领域技术人员任施匠思而为诸般修饰,然皆不脱权利要求所欲保护者。

- 具宽输出电压范围的充电式电荷泵浦

- 宽输出电压范围低电流失配的电荷泵电路设计方法及应用