一种数字直流电能表实验室误差校验系统及方法

文献发布时间:2023-06-19 09:46:20

技术领域

本发明涉及电工仪器仪表行业电能表校准技术领域,并且更具体地,涉及一种数字直流电能表实验室误差校验系统及方法。

背景技术

随着基于L/T860(IEC61850)标准的数字化变电站自动化系统的应用和推广,变电站过程层设备与间隔层设备之间的信息交互发生了较大的改变。过程层电子式互感器、智能化一次设备的应用,使得数字量输入式电能表成为数字化变电站电能计量的重要设备。传统的电子式和感应式电能表,均为模拟量输入式电能表,由更高等级的模拟量输入式标准电能表对其进行校准,其校准结果可以溯源到国家标准。数字量输入式电能表的输入信号为数字信号,无法使用模拟量输入式标准电能表对其进行校准。数字量输入式电能表作为电能计量装置,属于法制计量管理范畴,其校准结果必须溯源到国家标准。

针对数字化直流电能计量系统中电子式互感器输出的形式为FT3数字信号(理论上,我们认为电子式互感器和合并单元是一个整体,这个整体对电能表输出FT3信号),直流数字表接收FT3数字信号进行电能计量,虽然数字电能表在进行计量时已经不再使用A/D转换这样的模拟采样环节,单纯只进行数学计算,理论上应该不存在误差,但是在实际的使用中,存在采样点,计算浮点数位数截断,电压电流同步采样延迟以及现在不同厂家使用的计算方式不同等问题,因此数字电能表也存在其固有的误差,因此在使用之前,必须对其进行校准。但是目前市场上常规的校验设备已经无法满足对这种数字电能表进行误差校验,因此,我们提出了一种有效解决直流数字电能表的整体的、多表位的校验系统和方法。

发明内容

针对上述问题,本发明一种数字直流电能表实验室误差校验系统,包括:

模拟信号源、所述模拟信号源输出模拟电压/电流信号;

MU同步采样模块,所述MU同步采样模块输出同步采样时钟信号,连接被检数字直流电能表,使用输出的同步采样时钟信号控制被检数字直流电能表接收所述模拟电压/电流信号;

所述被检数字直流电能表接收所述模拟电压/电流信号后,输出被检电能脉冲;

模拟标准表、所述模拟标准表接收同步采样时钟信号,并根据同步采样时钟信号接收模拟电压/电流信号,根据所述模拟电压/电流信号输出标准电能脉冲;

误差比较器,所述误差比较器接收被检电能脉冲及标准电能脉冲,对所述被检电能脉冲及标准电能脉冲进行比较,获取被检数字直流电能表的误差值。

可选的,系统还包括:主处理器,所述主处理器用于调用误差值,对误差值进行显示,及对误差比较器进行参数设置。

可选的,误差比较器内置有多路数字信号处理器。

可选的,还包括:信号分流器,所述信号分流器置于MU同步采样模块及连接的被检数字直流电能表间,将模拟电压/电流信号分流,接入被检数字直流电能表,所述被检数字直流电能表数目与误差比较器内置的数字信号处理器数目相同。

可选的,标准电能脉冲为高频电能脉冲,且标准电能脉冲包括多路,数目与误差比较器内置的数字信号处理器数目相同。

可选的,MU同步采样模块作为同步源使用,包括:

FPGA处理器,输出待处理的同步时钟信号及同步时钟信号;

高精度A/D采样单元,接收待处理的同步时钟信号,去除待处理的同步时钟信号的歪斜,并将处理后的待处理的同步时钟信号,作为同步时钟信号发送至FPGA;

DSP处理器,接收同步时钟信号并输出。

可选的,误差比较器采集被检电能脉冲及标准电能脉冲后,过滤不稳定的脉冲信号,对稳定的被检电能脉冲及标准电能脉冲进行比较。

本发明还提供一种数字直流电能表实验室误差校验方法,包括:

控制模拟信号源输出模拟电压/电流信号至模拟标准表和被检数字直流电能表;

同时控制MU同步采样模块输出同步采样时钟信号,并输入至模拟标准表和被检数字直流电能表;

所述被检数字直流电能表接收所述模拟电压/电流信号后,输出被检电能脉冲;

所述模拟标准表接收所述模拟电压/电流信号后,输出标准电能脉冲;

控制误差比较器接收被检电能脉冲及标准电能脉冲,对所述被检电能脉冲及标准电能脉冲进行比较,获取被检数字直流电能表的误差值。

本发明使得模拟标准表和被检数字电能表收到的电压电流采样保持一致,可以最大化地减少系统误差对数字表误差的影响,保证误差计算的精准。

附图说明

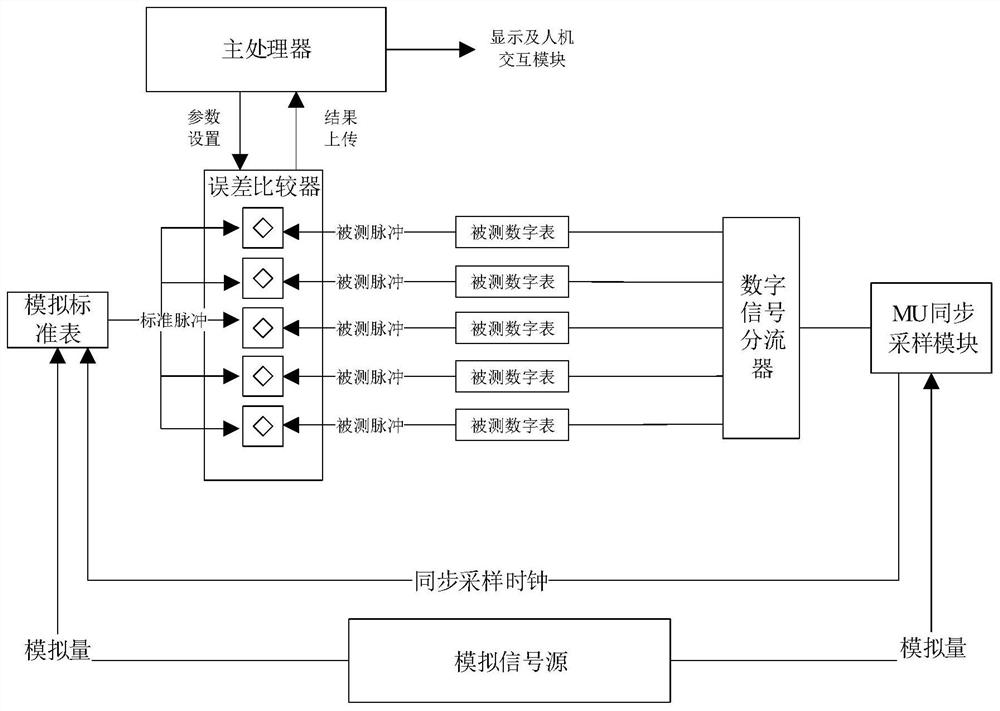

图1为本发明一种数字直流电能表实验室误差校验系统结构图;

图2为本发明一种数字直流电能表实验室误差校验系统MU同步采样模块结构图;

图3为本发明一种数字直流电能表实验室误差校验系统主处理器原理图;

图4为本发明一种数字直流电能表实验室误差校验方法流程图。

具体实施方式

现在参考附图介绍本发明的示例性实施方式,然而,本发明可以用许多不同的形式来实施,并且不局限于此处描述的实施例,提供这些实施例是为了详尽地且完全地公开本发明,并且向所属技术领域的技术人员充分传达本发明的范围。对于表示在附图中的示例性实施方式中的术语并不是对本发明的限定。在附图中,相同的单元/元件使用相同的附图标记。

除非另有说明,此处使用的术语(包括科技术语)对所属技术领域的技术人员具有通常的理解含义。另外,可以理解的是,以通常使用的词典限定的术语,应当被理解为与其相关领域的语境具有一致的含义,而不应该被理解为理想化的或过于正式的意义。

本发明一种数字直流电能表实验室误差校验系统,包括:

模拟信号源、所述模拟信号源输出模拟电压/电流信号;

MU同步采样模块,所述MU同步采样模块输出同步采样时钟信号,连接被检数字直流电能表,使用输出的同步采样时钟信号控制被检数字直流电能表接收所述模拟电压/电流信号;

所述被检数字直流电能表接收所述模拟电压/电流信号后,输出被检电能脉冲;

模拟标准表、所述模拟标准表接收同步采样时钟信号,并根据同步采样时钟信号接收模拟电压/电流信号,根据所述模拟电压/电流信号输出标准电能脉冲;

误差比较器,所述误差比较器接收被检电能脉冲及标准电能脉冲,对所述被检电能脉冲及标准电能脉冲进行比较,获取被检数字直流电能表的误差值。

主处理器,所述主处理器用于调用误差值,对误差值进行显示,及对误差比较器进行参数设置。

信号分流器,所述信号分流器置于MU同步采样模块及连接的被检数字直流电能表间,将模拟电压/电流信号分流,接入被检数字直流电能表,所述被检数字直流电能数目与误差比较器内置的数字信号处理器数目相同。

误差比较器内置有多路数字信号处理器。

标准电能脉冲为高频电能脉冲,且标准电能脉冲包括多路,数目与误差比较器内置的数字信号处理器数目相同。

MU同步采样模块作为同步源使用,包括:

FPGA处理器,输出待处理的同步时钟信号及同步时钟信号;

高精度A/D采样单元,接收待处理的同步时钟信号,去除待处理的同步时钟信号的歪斜,并将处理后的待处理的同步时钟信号,作为同步时钟信号发送至FPGA;

DSP处理器,接收同步时钟信号并输出。

误差比较器采集被检电能脉冲及标准电能脉冲后,过滤不稳定的脉冲信号,对稳定的被检电能脉冲及标准电能脉冲后进行比较。

如图2所示,其中MU同步采样模块作为同步源,使用MU同步采样模块内部的FPGA模块提供整个系统的时钟同步信号,由于FPGA模块采用了INTEL公司的最新高性能FPGA芯片进行时钟控制,提供了丰富的时钟资源,内置数字时钟管理器(DCM)用于提供整个系统的时钟同步信号并有助于时钟信号的操控。

数字时钟管理器内含一个延迟锁相环,建立时钟的镜像将时钟信号从FPGA模块发送到另一个器件后,又收回时钟信号,去除数字时钟管理器输出时钟信号的歪斜,从而避免时钟分配延迟。此外由于数字时钟管理器可以在时钟路径上引入延迟,数据总线上的各个数据位可以在不同的时间到达,为了正确对数据位采样,接收端的时钟信号适当地与所有数据位的到达保持同步,确保了信号的保真度,同时FPGA模块控制高精确AD采样,保证采样数据精确。

模拟标准表接收同步源的同步采样时钟,使得模拟标准表和被检数字电能表收到的电压电流采样保持一致,可以最大化的减少系统误差对数字电能表误差的影响,保证误差计算的精准。

误差比较器采用了多路独立的高速数字处理器DSP进行分别计算,每个DSP处理器采用BIOS高效处理系统,DSP会同时对模拟标准表的标准脉冲和被测数字电能表的被测脉冲进行采集,其中,模拟标准表输出的脉冲为高频脉冲信号,DSP会对脉冲进行精确采集并进行记录,同时等待被测脉冲信号的输入,系统在自动过滤掉前几次不稳定的脉冲信号之后,会对后面稳定的脉冲信号进行误差计算,参与计算的常数和圈数等参数设置由主处理器统一设置,因此每个DSP处理器对应处理一个被测脉冲,保证了被测数字电能表的脉冲信号被第一时间采集和计算,同时多路DSP处理器各自独立计算,互不干涉,进一步保证了测试的精准度。解决了电能表校验时时间量不一致的问题和多表同时检定的问题,采用本误差比较器能非常快的对被测信号进行响应并计算。

其中模拟标准表的脉冲输出常数和圈数是可设的,参数设置由主处理器统一设置,确保和被检的数字电能表参数保持一致,可以更客观的体现数字电能表在现场实际情况下的误差。

如图3所示,系统组成方面,在最大化方便用户使用和更直观的显示和设置的同时,也为了误差计量的准确和更客观的体现数字电能表的误差状态,软件系统采用了一个主处理器CPU,底层多级处理器CPU协同处理的方式进行设计,主处理器CPU采用常规的LINUX操作系统,给用户带来非常良好和方便的操作体验,同时对底层的采样处理器、协议打包处理器、误差计算处理器分别进行协同控制,在最大化保证了系统稳定的同时,各个处理器又独立工作,互不干扰,最大化的提升了误差测量的精度,同时,上位机CPU的LINUX操作系统对用户的极大的友好界面,方便用户接打印设备、存储类设备,甚至是网络,实现校验结果的打印、自定义测量、无人值守测量、远程控制测量等各种功能,极大的方便用户的操作,而底层CPU的软件采用实时性很强的UCOS操作系统和BIOS_5_42系统,可以实现更高效的计算和更精确的误差测量。

模拟标准表检测被检的数字电能表,这个模拟标准不是单纯的模拟表,是经过同步时钟采样的标准表,输出的脉冲是高频脉冲,模拟标准表接收同步源的同步采样时钟,使得模拟标准表和被检数字电能表收到的电压电流采样保持一致,可以最大化地减少系统误差对数字表误差的影响,保证误差计算的精准。

误差比较器采用了多路独立的高速数字处理器DSP进行分别计算,互不干涉,进一步保证了测试的精准度,解决了电能表的校验时时间量不一致的问题和多表同时检定的问题,采用本误差比较器能非常快的对被测信号进行响应并计算。

模拟标准表的脉冲输出常数和圈数是可设的,参数设置由主处理器统一设置,确保和被检的数字电能表参数保持一致,可以更客观的体现数字电能表在现场实际情况下的误差表现。

软件系统采用了一个主处理器CPU,底层多级处理器CPU协同处理的方式进行设计,主处理器CPU采用常规的LINUX操作系统,给用户带来非常良好和方便的操作体验,同时对底层的采样处理器、协议打包处理器、误差计算处理器分别进行协同控制,在最大化保证了系统稳定的同时,各个处理器又独立工作,互不干扰,最大化的提升了误差测量的精度。

上位机CPU的LINUX操作系统方便用户接打印设备、存储类设备、网络设备,实现结果的打印、自定义测量、无人值守测量、远程控制测量等各种功能,极大的方便用户的操作。

本发明还提供一种数字直流电能表实验室误差校验方法,如图4所示,包括:

控制模拟信号源输出模拟电压/电流信号至模拟标准表和被检数字直流电能表;

同时控制MU同步采样模块输出同步采样时钟信号,并输入至模拟标准表和被检数字直流电能表;

所述被检数字直流电能表接收所述模拟电压/电流信号后,输出被检电能脉冲;

所述模拟标准表接收所述模拟电压/电流信号后,输出标准电能脉冲;

控制误差比较器接收被检电能脉冲及标准电能脉冲,对所述被检电能脉冲及标准电能脉冲进行比较,获取被检数字直流电能表的误差值。

本发明使得模拟标准表和被检数字电能表收到的电压电流采样保持一致,可以最大化地减少系统误差对数字表误差的影响,保证误差计算的精准。

本领域内的技术人员应明白,本申请的实施例可提供为方法、系统、或计算机程序产品。因此,本申请可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本申请可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、CD-ROM、光学存储器等)上实施的计算机程序产品的形式。本申请实施例中的方案可以采用各种计算机语言实现,例如,面向对象的程序设计语言Java和直译式脚本语言JavaScript等。

本申请是参照根据本申请实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

尽管已描述了本申请的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本申请范围的所有变更和修改。

显然,本领域的技术人员可以对本申请进行各种改动和变型而不脱离本申请的精神和范围。这样,倘若本申请的这些修改和变型属于本申请权利要求及其等同技术的范围之内,则本申请也意图包含这些改动和变型在内。

- 一种数字直流电能表实验室误差校验系统及方法

- 一种满足在线校验过程电能数据无损的数字直流电能表及现场校验系统