计算装置及其操作方法

文献发布时间:2023-06-19 10:27:30

技术领域

本发明涉及一种电子装置,且特别是涉及一种计算装置及其操作方法。

背景技术

计算装置在许多应用中都需要使用一或多个查找表(lookup table)。举例来说,推荐系统(recommendation system)是一种讯息分析系统,用于预测用户对于物品或服务的“评分”或“偏好”。常见的推荐系统是由词性表查找(word embedding table lookup)模块和神经网络运算(neural network computation)模块所组成。所述词性表大多由数个到数十个大小不一的查找表所组成,大的查找表可能占用数千兆位组(gigabyte,GB)的容量,小的查找表可能只需要数字节(byte)的容量。查表得出的讯息经过神经网络的运算,可以得出推荐系统的结果。

一般的计算装置具有硬式磁盘驱动器(hard disk drive,HDD)与随机存取内存(random access memory,RAM)。硬式磁盘驱动器的存储空间大(成本便宜),但是访问速度慢。随机存取内存的速度较快,但是存储空间小(成本较高)。在系统关机前,处理器会将查找表从随机存取内存搬移到硬式磁盘驱动器。在系统开机后,处理器会将查找表从硬式磁盘驱动器搬移到随机存取内存,以加快访问速度和系统效能。无论如何,碍于随机存取内存的容量有限,有一些查找表(例如查找表A)可能暂时不会被搬移到随机存取内存。在内存空间已满的情况下,当在硬式磁盘驱动器中的查找表A需要被存取的时候,处理器会将在随机存取内存中的查找表B写回硬式磁盘驱动器中,然后将查找表A从硬式磁盘驱动器搬移到随机存取内存。因此在查表过程中,常需要在不同存储媒体间大量搬移数据,造成查表所需时间过久。

另外,目前的查找表是被存放在特定内存,而不论当时在系统中有无更适合存放这个查找表的其他内存。一般的计算装置具有多种内存。例如,计算装置可能具有速度较快的内存与速度较慢的内存。目前的查表系统并不会根据查找表的特性而有差异化处理方式,亦即不会动态地决定将查找表存放在多个内存的哪一个,因此查表较无效率。举例来说,某一个频繁存取的查找表可能默认地被存放在速度较慢的内存,造成查表所需时间过久。

须注意的是,“先前技术”段落的内容是用来帮助了解本发明。在“先前技术”段落所揭露的部份内容(或全部内容)可能不是所属技术领域中具有通常知识者所知道的习知技术。在“先前技术”段落所揭露的内容,不代表该内容在本发明申请前已被所属技术领域中具有通常知识者所知悉。

发明内容

本发明是针对一种计算装置及其操作方法,以存取在内存中的查找表。

根据本发明的实施例,计算装置包括多个内存以及一个处理电路。处理电路耦接至这些内存。处理电路依据至少一个查找表的特性动态地决定将所述至少一个查找表存放在这些内存的哪一个。然后,处理电路可以使用所述至少一个查找表去执行至少一个算法。

根据本发明的实施例,操作方法包括:由处理电路依据至少一个查找表的特性动态地决定将所述至少一个查找表存放在多个内存的哪一个;以及由处理电路使用所述至少一个查找表去执行至少一个算法。

根据本发明的实施例,计算装置包括至少一个内存、一个处理器以及至少一个查表电路。所述至少一内存用以存放至少一个查找表。处理器用以发出查表命令以及执行至少一个算法。所述至少一查表电路耦接至处理器与所述至少一内存。当处理器发出查表命令给所述至少一查表电路时,所述至少一查表电路依据处理器的查表命令查找被存放在所述至少一内存的所述至少一个查找表,以获得至少一个对应数据。处理器使用所述至少一查表电路所提供的所述至少一个对应数据去执行所述至少一个算法。

在根据本发明的实施例中,所述处理电路可以依据查找表的特性而动态地决定将这个查找表存放在多个内存的哪一个。因此,查表效率可以被有效提升。在一些实施例中,依据处理器所发出的查表命令,查表电路可以查找被存放在内存中的查找表,然后将查找结果(对应数据)回传给处理器。因此,查表电路可以分担工作而使处理器的效率可以被有效提升。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

图1为依照本发明的一实施例的一种计算装置的电路方块(circuit block)示意图;

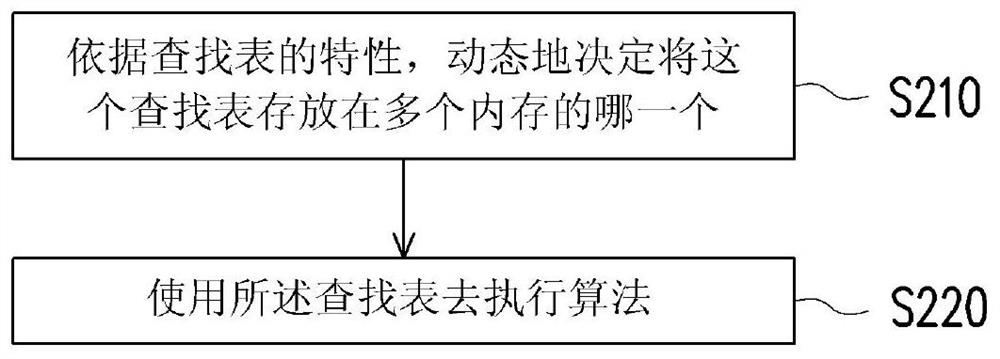

图2为依照本发明的一实施例的一种计算装置的操作方法的流程示意图;

图3为依照本发明的一实施例说明图1所示处理电路的电路方块示意图;

图4为依照本发明的另一实施例说明图1所示处理电路的电路方块示意图;

图5为依照本发明的另一实施例的一种计算装置的操作方法的流程示意图;

图6为依照本发明的又一实施例的一种计算装置的操作方法的流程示意图;

图7为依照本发明的又一实施例说明图1所示计算装置的电路方块示意图。

附图标号说明

100:计算装置;

110:处理电路;

111:处理器;

112、113、114:查表电路;

120_1、120_2、120_3、120_4、120_i、120_i+1、120_n:内存;

130:非挥发性存储装置;

S210、S220、S510~S560、S610~S660:步骤。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

在本案说明书全文(包括申请专利范围)中所使用的“耦接(或连接)”一词可指任何直接或间接的连接手段。举例而言,若文中描述第一装置耦接(或连接)于第二装置,则应该被解释成该第一装置可以直接连接于该第二装置,或者该第一装置可以透过其他装置或某种连接手段而间接地连接至该第二装置。本案说明书全文(包括申请专利范围)中提及的“第一”、“第二”等用语是用以命名组件(element)的名称,或区别不同实施例或范围,而并非用来限制组件数量的上限或下限,亦非用来限制组件的次序。另外,凡可能之处,在图式及实施方式中使用相同标号的组件/构件/步骤代表相同或类似部分。不同实施例中使用相同标号或使用相同用语的组件/构件/步骤可以相互参照相关说明。

图1是依照本发明的一实施例的一种计算装置100的电路方块(circuit block)示意图。于图1所示实施例中,计算装置100包括处理电路110以及多个内存(例如内存120_1、…、120_n)。处理电路110耦接至内存120_1~120_n。内存120_1~120_n的数量n可以依照设计需求来决定。内存120_1~120_n包含多种类的内存。例如,在一些实施例中,内存120_1~120_n可以包含静态随机存取内存(static random access memory,SRAM)、动态随机存取内存(dynamic random access memory,DRAM)、磁性随机存取内存(magnetic random-access memory,MRAM)、磁阻随机存取内存(magnetoresistive random access memory,MRAM)与快闪(Flash)内存中的至少二种。一般而言,访问速度较慢的内存通常具有较大的存储空间(因为成本便宜),而速度较快的内存通常具有较小的存储空间(因为成本较高)。

在计算装置100关机前,处理电路110可以将在内存120_1~120_n中的重要数据(例如查找表)搬移(写回)到计算装置100的非挥发性存储装置(non-volatile storagedevice)130。依照设计需求,非挥发性存储装置130可以包括硬式磁盘驱动器(hard diskdrive,HDD)、固态驱动器(solid state drive,SSD)或是其他非挥发性存储设备。在计算装置100开机后,处理电路110可以将所述重要数据(例如查找表)从非挥发性存储装置130搬移到内存120_1~120_n中。须注意的是,图1绘示了非挥发性存储装置130与内存120_1~120_n之间的数据流,然而所述数据流不代表非挥发性存储装置130的实际耦接关系。例如,在一些实施例中,非挥发性存储装置130可能耦接至处理电路110,而由处理电路110传输数据于非挥发性存储装置130与内存120_1~120_n之间。

图2是依照本发明的一实施例的一种计算装置100的操作方法的流程示意图。请参照图1与图2。在步骤S210中,处理电路110可以依据查找表的特性而动态地决定将这个查找表存放在内存120_1~120_n的哪一个。根据多个查找表的每一个的特性(大小、存取频率等等),处理电路110可以使用不同种类的内存来储存,以达到兼顾访问速度、存取功耗、存储成本等最有效率的配置。在步骤S220中,处理电路110可以使用所述查找表去执行至少一个算法。

举例来说,推荐系统(recommendation system)可以预测使用者对于物品或服务的“评分”或“偏好”。常见的推荐系统可以执行词性表查找(word embedding tablelookup)、神经网络运算(neural network computation)以及/或是其他算法。一般而言,所述词性表包括多个大小不一的查找表。处理电路110可以执行所述推荐系统的各种算法,而内存120_1~120_n可以存放所述推荐系统的大量查找表。在计算装置100关机前,处理电路110可以将这些查找表从内存120_1~120_n搬移到非挥发性存储装置130。在计算装置100开机后,处理电路110可以将这些查找表从非挥发性存储装置130搬移到内存120_1~120_n,以加快访问速度和系统效能。不同于习知技术之处包括,本实施例的处理电路110可以依据这些查找表的特性而动态地决定将这些查找表存放在内存120_1~120_n的位置。因此,在计算装置100关机前所述推荐系统的这些查找表在内存120_1~120_n的位置可能不同于在计算装置100开机后这些查找表在内存120_1~120_n的位置。处理电路110可以对内存120_1~120_n进行查表而得出对应数据(查表结果),然后使用所述对应数据去执行所述神经网络运算与/或其他算法而得出推荐系统的结果。

处理电路110可以依据查找表的特性而动态地决定将这个查找表存放在内存120_1~120_n的哪一个。举例来说,“查找表的特性”包括查找表的数据量以及存取频率中的至少一个。

在一些实施例中,处理电路110可以依据“多个查找表中的较大存取频率查找表优先存放在多个内存中的较快内存”的原则,将这些查找表存放在内存120_1~120_n。举例来说,处理电路110可以依照多个查找表目前的存取频率,将频繁存取的查找表存放在内存120_1~120_n中速度较快的内存,以及将不常存取的查找表存放在内存120_1~120_n中速度较慢的内存。

在另一些实施例中,处理电路110可以依据“多个查找表中的较小数据量查找表优先存放在多个内存中的较小空间内存”的原则,将这些查找表存放在内存120_1~120_n。举例来说,处理电路110可以依照多个查找表目前的数据量,将数据量大的查找表存放在内存120_1~120_n中存储空间较大的内存,以及将数据量小的查找表存放在内存120_1~120_n中存储空间较小的内存。

在又一些实施例中,处理电路110可以依据“多个查找表中的较小数据量查找表优先存放在多个内存中的较快内存”的原则,将这些查找表存放在内存120_1~120_n。举例来说,处理电路110可以依照多个查找表目前的数据量,将数据量大的查找表存放在内存120_1~120_n中速度较慢的内存,以及将数据量小的查找表存放在内存120_1~120_n中速度较快的内存。

基于上述,处理电路110可以依据查找表的特性而动态地决定将这个查找表存放在内存120_1~120_n的哪一个。因此,处理电路110处理电路110的查表效率可以被有效提升。

图3是依照本发明的一实施例说明图1所示处理电路110的电路方块示意图。于图3所示实施例中,处理电路110包括处理器(processor)111以及查表电路112。依照设计需求,查表电路112可以是场可程序逻辑门阵列(Field Programmable Gate Array,FPGA)、特殊应用集成电路(Application-specific integrated circuit,ASIC)或是其他组件/电路。跟通用型的处理器比起来,查表专用的FPGA(或ASIC)具有成本较低、运作功耗较低、查表速度快、效率高等优势。

处理器111可以执行至少一个算法。基于算法的运行,处理器111可以发出查表命令给查表电路112。查表电路112耦接至处理器111,以接收所述查表命令。查表电路112还耦接至内存120_1~120_n,以存取一或多个查找表。当处理器111发出查表命令给查表电路112时,查表电路112依据处理器111的查表命令去查找被存放在内存120_1~120_n的查找表,以获得至少一个对应资料(查表结果)。查表电路112将所述对应数据回传给处理器111。处理器111可以使用查表电路112所提供的对应资料(查表结果)去执行所述算法。

基于上述,依据处理器111所发出的查表命令,查表电路112可以查找被存放在内存120_1~120_n中的查找表,然后将查找结果(对应数据)回传给处理器。在发出查表命令后,处理器111可更专注于运算,不用因为等待对应数据(查表结果)而闲置。因此,查表电路112可以分担工作而使处理器111的效率可以被有效提升。

图4是依照本发明的另一实施例说明图1所示处理电路110的电路方块示意图。于图4所示实施例中,处理电路110包括处理器111、查表电路113以及查表电路114。基于算法的运行,处理器111可以发出查表命令给查表电路113与/或查表电路114。查表电路113以及查表电路114耦接至处理器111,以接收所述查表命令。查表电路113还耦接至内存120_1~120_i,以存取一或多个查找表。查表电路114还耦接至内存120_i+1~120_n,以存取一或多个查找表。其中,i与n为正整数,且i小于n。图4所示处理器111可以参照图3所示处理器111的相关说明,而图4所示查表电路113以及查表电路114可以参照图3所示查表电路112的相关说明来类推,故不再赘述。

请参照图1。计算装置100运作时,处理电路110会将需要查询的查找表从非挥发性存储装置130读出。根据各个查找表之特性(所需之存储空间大小、存取频率等等),处理电路110可以将多个查找表加载到不同类型的内存中,以优化系统整体成本、功耗和运算效能。举例来说,内存120_1~120_n包括速度较快(但是存储空间小)的第一内存(例如SRAM),以及速度较慢(但是存储空间大)的第二内存(例如DRAM)。处理电路110可以将存储空间需求较大或不常存取的查找表放在DRAM以降低存储成本,而将存储空间需求小或常常存取的查找表放在SRAM以降低访问时间以及所需功耗。另外,存储空间需求大的查找表若是有需常读取的部份(entry),可将此部份放到SRAM以加快读取速度。

举例来说,当处理电路110从非挥发性存储装置130读出某一个查找表(目前查找表)时,处理电路110可以依照查找表的特性为这个目前查找表计算评价,然后处理电路110可以依据“较大评价查找表优先存放在较快内存”的原则,将这个目前查找表存放在第一内存(较快内存,例如SRAM)以及第二内存(较慢内存,例如DRAM)其中一个。举例来说,处理电路110可以使用评价公式F=α*v+β*f来计算这个目前查找表的评价,其中F表示这个目前查找表的评价,v表示这个目前查找表的资料量,f表示这个目前查找表的存取频率,而α与β为依照设计需求来决定的两个实数。当目前查找表的评价F大于某一个门坎(此门坎可以依照设计需求来决定)时,处理电路110可以将目前查找表存放在第一内存(较快内存)。当目前查找表的评价F小于所述门坎时,处理电路110可以将目前查找表存放在第二内存(较慢内存)。

图5是依照本发明的另一实施例的一种计算装置100的操作方法的流程示意图。请参照图1与图5。处理电路110会将非挥发性存储装置130的查找表进行排序(步骤S510),然后依序从这些查找表中选择一个查找表(步骤S520)。排序的依据可以依照设计需求来决定。举例来说,在一些实施例中,处理电路110可以依照查找表的数据量而将非挥发性存储装置130的多个查找表进行排序,然后依序从这些查找表中选择数据量最小的查找表。在另一些实施例中,处理电路110可以依照查找表的存取频率而将非挥发性存储装置130的多个查找表进行排序,然后依序从这些查找表中选择存取频率最大的查找表。

当第一内存(较快内存)的剩余空间是足够的(步骤S530的判断结果为“足够”),处理电路110可以将步骤S520所选的查找表从非挥发性存储装置130搬移至第一内存(步骤S540)。当第一内存(较快内存)的剩余空间是不够的(步骤S530的判断结果为“不够”),处理电路110可以将步骤S520所选的查找表从非挥发性存储装置130搬移至第二内存(较慢内存)(步骤S550)。

当步骤S540或步骤S550完成时,处理电路110可以进行步骤S560,以判断非挥发性存储装置130有无查找表尚未搬移。当非挥发性存储装置130有查找表尚未搬移时(步骤S560的判断结果为“有”),处理电路110可以回到步骤S520,以依序选择下一个查找表。

请参照图1。在一些实施例中,处理电路110可以将非挥发性存储装置130的多个查找表的每一个分为多个部份(entry)。处理电路110可以依据“多个部份中的较大存取频率部份存放在多个内存中的较快内存”的原则,将一个查找表分散地存放在多个内存。

图6是依照本发明的又一实施例的一种计算装置100的操作方法的流程示意图。请参照图1与图6。处理电路110可以将非挥发性存储装置130的多个查找表的每一个分为多个部份(entry)。处理电路110可以将这些部份进行排序(步骤S610),然后依序从这些部份中选择一个部份(步骤S620)。排序的依据可以依照设计需求来决定。举例来说,在一些实施例中,处理电路110可以依照存取频率而将非挥发性存储装置130的这些部份进行排序,然后依序从这些部份中选择存取频率最大的部份。

当第一内存(较快内存)的剩余空间是足够的(步骤S630的判断结果为“足够”),处理电路110可以将步骤S620所选的部份(entry)从非挥发性存储装置130搬移至第一内存(步骤S640)。当第一内存(较快内存)的剩余空间是不够的(步骤S630的判断结果为“不够”),处理电路110可以将步骤S620所选的部份从非挥发性存储装置130搬移至第二内存(较慢内存)(步骤S650)。

当步骤S640或步骤S650完成时,处理电路110可以进行步骤S660,以判断非挥发性存储装置130有无部份(entry)尚未搬移。当非挥发性存储装置130有部份尚未搬移时(步骤S660的判断结果为“有”),处理电路110可以回到步骤S620,以依序选择下一个部份。因此,一个查找表可以被分散地存放在不同类型的多个内存。

图7是依照本发明的又一实施例说明图1所示计算装置100的电路方块示意图。于图7所示实施例中,计算装置100包括处理电路110、内存120_1、内存120_2、内存120_3、内存120_4以及非挥发性存储装置130。图7所示处理电路110、内存120_1~120_4以及非挥发性存储装置130可以参照图1至图6所示处理电路110、内存120_1~120_n以及非挥发性存储装置130的相关说明,故不再赘述。

须注意的是,图7绘示了非挥发性存储装置130与内存120_1~120_4之间的数据流,以及处理电路110与内存120_1~120_4之间的数据流,然而这些数据流实际耦接关系。例如,在一些实施例中,非挥发性存储装置130可能耦接至处理电路110,而由处理电路110传输数据于非挥发性存储装置130与内存120_1~120_n之间。在另一些实施例中,非挥发性存储装置130与内存120_1~120_4可能经由相同(或不同)总线(bus)耦接至处理电路110

于图7所示实施例中,处理电路110包括处理器111以及查表电路112。查表电路112耦接至内存120_1~120_4,以存取一或多个查找表。基于算法的运行,处理器111可以发出查表命令给查表电路112。查表电路112依据处理器111的查表命令去查找被存放在内存120_1~120_4的查找表,以获得至少一个对应资料(查表结果)。图7所示处理器111以及查表电路112可以参照图3所示处理器111以及查表电路112的相关说明,故不再赘述。

于图7所示实施例中,内存120_1可以包含容量为16千字节(Kilobyte,KB)的SRAM,内存120_2可以包含容量为256KB的SRAM,内存120_3可以包含容量为16千兆位组(Gigabyte,GB)的DRAM,内存120_4可以包含容量为16兆字节(Megabyte,MB)的MRAM。一般而言,SRAM的访问速度快于DRAM的访问速度,而MRAM的访问速度则介于SRAM与DRAM之间。

图7所示计算装置100可以被应用为推荐系统的硬件运算平台。在计算装置100开机后,或者当处理器111需要词性查找表的数据时,推荐系统的多个查找表会从非挥发性存储装置130被搬移到内存120_1~120_4中。处理电路110可以依据查找表的特性而动态地决定将这个查找表存放在内存120_1~120_4的哪一个。推荐系统的查表操作则由查表电路112执行。查表电路112可以将查表结果传送给处理器111。处理器111可以处理推荐系统的神经网络运算。

一般而言,在查表电路112将查找表由非挥发性存储装置130复制(搬移)到内存(例如内存120_1)的过程中,若选定的内存120_1无足够的空间来存放这个查找表,则内存120_1的旧数据会被写回非挥发性存储装置130,然后查表电路112将这个查找表复制(搬移)到内存120_1以覆盖掉这个旧数据。之后处理器111若需要先前被覆盖掉的这个旧数据,则查表电路112需要再次从非挥发性存储装置130复制(搬移)这个旧数据到内存120_1。此类数据的重复搬移会造成系统消耗不必要功耗,以及可能造成处理器111无法及时拿到所需数据而造成系统效能降低。

为了避免上述情形频繁发生,图7所示查表电路112可以将数据量为2KB以下而且最频繁查找的查找表存放在内存120_1(即16KB SRAM),将数据量为64KB以下而且次频繁查找的查找表存放在内存120_2(即256KB SRAM)。此外,若是有些容量大于64KB的查找表,而且这个查找表的部分(entry)的内容有很高的机率被读取,则这个部分也会被存放在内存120_2(这个查找表的其他部分可以被留置在非挥发性存储装置130中,或是被复制/搬移到内存120_3)。对于非挥发性存储装置130中的其余查找表,查表电路112可以将数据量为1MB以下的查找表存放在内存120_4(即16MB MRAM),以及将数据量为1MB以上的查找表存放在内存120_3(即16GB DRAM)。

综上所述,处理电路110可以将频繁查找的查找表尽量放在较快内存(例如SRAM),以提高查找速度。因为独立的内存120_1(16KB SRAM)被用来存放最频繁查找的查找表,所以降低内存120_1的查找表被其他数据覆盖的机率。处理电路110可以将数据量为1MB以下的查找表存放在内存120_3(即16GB DRAM),以降低资料量为1MB以下的查找表被其他大数据量的查找表所覆盖的机率。将大数据量的查找表被存放在内存120_3(即16GB DRAM),以节省系统内存成本。

依照不同的设计需求,上述处理电路110、处理器111以及(或是)查表电路112的方块的实现方式可以是硬件(hardware)、韧体(firmware)、软件(software,即程序)或是前述三者中的多者的组合形式。

以硬件形式而言,上述处理电路110、处理器111以及(或是)查表电路112的方块可以实现于集成电路(integrated circuit)上的逻辑电路。上述处理电路110、处理器111以及(或是)查表电路112的相关功能可以利用硬件描述语言(hardware descriptionlanguages,例如Verilog HDL或VHDL)或其他合适的编程语言来实现为硬件。举例来说,上述处理电路110、处理器111以及(或是)查表电路112的相关功能可以被实现于一或多个控制器、微控制器、微处理器、特殊应用集成电路(ASIC)、数字信号处理器(digital signalprocessor,DSP)、场可程序逻辑门阵列(FPGA)及/或其他处理单元中的各种逻辑区块、模块和电路。

以软件形式及/或韧体形式而言,上述处理电路110、处理器111以及(或是)查表电路112的相关功能可以被实现为编程码(programming codes)。例如,利用一般的编程语言(programming languages,例如C、C++或汇编语言)或其他合适的编程语言来实现上述处理电路110、处理器111以及(或是)查表电路112。所述编程码可以被记录/存放在记录媒体中,所述记录媒体中例如包括只读存储器(Read Only Memory,ROM)、存储装置及/或随机存取内存(Random Access Memory,RAM)。计算机、中央处理器(Central Processing Unit,CPU)、控制器、微控制器或微处理器可以从所述记录媒体中读取并执行所述编程码,从而达成相关功能。作为所述记录媒体,可使用“非临时的计算机可读取媒体(non-transitorycomputer readable medium)”,例如可使用带(tape)、碟(disk)、卡(card)、半导体内存、可程序设计的逻辑电路等。而且,所述程序也可经由任意传输媒体(通信网路或广播电波等)而提供给所述计算机(或CPU)。所述通信网路例如是互联网(Internet)、有线通信(wiredcommunication)、无线通信(wireless communication)或其它通信介质。

综上所述,在一些实施例中,所述处理电路110可以依据查找表的特性而动态地决定将这个查找表存放在多个内存120_1~120_n的哪一个。因此,查表效率可以被有效提升。在一些实施例中,依据处理器111所发出的查表命令,查表电路112可以查找被存放在内存120_1~120_n中的查找表,然后将查找结果(对应数据)回传给处理器111。因此,查表电路112可以分担工作而使处理器111的效率可以被有效提升。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 存储装置、存储装置的操作方法和计算装置的操作方法

- 存储装置及其操作方法、计算系统及其操作方法