一种高速输出的HCSL电平驱动电路

文献发布时间:2023-06-19 10:48:02

技术领域

本发明涉及集成电路领域,尤其涉及一种高速输出的HCSL电平驱动电路。

背景技术

目前的HCSL电路为典型的漏端开路模式,开关管PMOS管源极连接电流源,漏极开路,与片外的对地电阻形成信号对地通路,输入差分信号Inp/n通过控制PMOS开关电流,实现在外界对地电阻上形成差分电压信号。

HCSL电平由于外接50Ω电阻值固定,且电平幅度较大,因此尾电流值大,对应的开关管尺寸较大。由于开关管的寄生较重,对该电平信号的速率影响较大;另外,由于输出级经过PAD与外接电路级联,开关管在高速开关时,对阻抗匹配有较大影响,会在高速信号传输时引入较大反射。因此,常规的HCSL输出驱动电路的速率不超过250MHz。

发明内容

本发明为解决背景技术中存在的上述技术问题,而提供一种带扩频功能的高速输出的HCSL电平驱动电路,具有增大电路工作频率,同时提高信号的阻抗匹配效果。

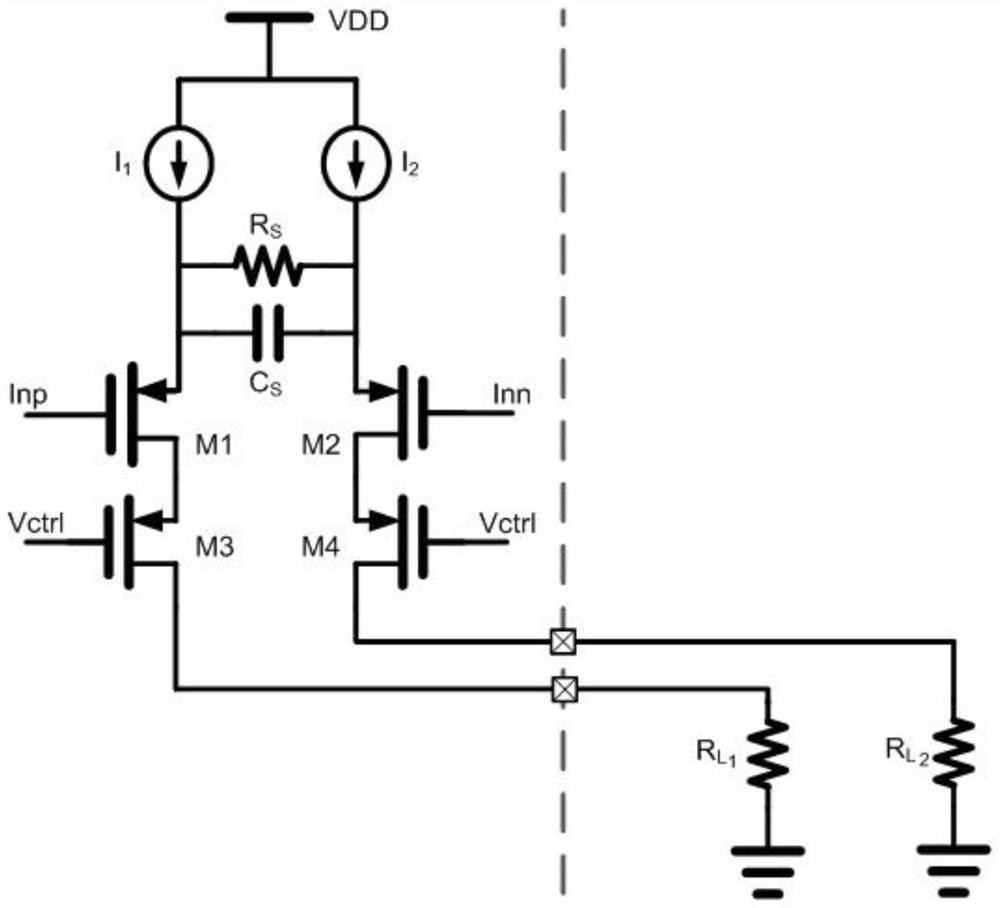

本发明的技术解决方案是:本发明为一种高速输出的HCSL电平驱动电路,包括PMOS开关管M1和PMOS开关管M2,PMOS开关管M1的源极连接电流源I1,PMOS开关管M2的源极连接电流源I2,PMOS开关管M1的漏极通过负载电阻RL1接地,PMOS开关管M2的漏极通过负载电阻RL2接地,其特殊之处在于:所述PMOS开关管M1的源极和PMOS开关管M2的源极之间串联有电阻Rs和电容Cs,电阻Rs与电容Cs并联。

优选的,PMOS开关管M1与负载电阻RL1之间串联有PMOS管M3,PMOS开关管M2与负载电阻RL2之间串联有PMOS管M4。

优选的,PMOS管M3和PMOS管M4的栅极分别受片内电压Vctrl的控制。

本发明通过在传统HCSL电平驱动电路的漏极开路结构基础上,增加零点,补偿信道、寄生带来的频率衰减,即通过在PMOS管M1和PMOS管M2源极串联电阻Rs和串联电容Cs,引入零点的方式;同时通过增加隔离PMOS管M3和PMOS管M4,控制输出级的阻抗。PMOS管M3、PMOS管M4的栅极受电压Vctrl控制,通过电压的大小,控制M3和M4的阻抗,实现对整个HCSL输出级的阻抗调整。通过调整阻抗,可实现与信道、终端负载的阻抗匹配,减小信号反射,提高信号质量。因此本发明具有以下优点:

1)增大驱动电路的带宽。本发明在现有的HCSL电平驱动电路基础上通过在两差分源极引入源极串联电阻Rs和电容Cs实现,电阻Rs和电容Cs在电路传输函数中引入一个零点,能够抬升在对应频率下的电路频率相应,通过合理设置Rs和Cs的值,能够将零点放置在合理的频率点,从而抵消寄生效应对整体电路频率响应带来的衰减作用,从而起到增大电路工作频率的作用。

2)提高阻抗匹配效果。本发明在PMOS开关管M1与负载电阻RL1之间以及PMOS开关管M2与负载电阻RL2之间,分别串联插入两个栅极受片内电压Vctrl控制的PMOS管M3和PMOS管M4,通过Vctrl的控制,使得PMOS管M3和PMOS管M4工作在特定工作区,保证PMOS管M3或PMOS管M4与串联的PMOS开关管M1或PMOS开关管M2阻抗保持不变,不受开关管高速开关的影响,从而将信号反射降低。

附图说明

图1为本发明的电路原理图。

具体实施方式

下面结合附图和具体实施例对本发明的技术方案做进一步详细描述。

参见图1,本发明的具体实施例的结构包括PMOS开关管M1、PMOS开关管M2、PMOS管M3和PMOS管M4,PMOS开关管M1的源极连接电流源I1,PMOS开关管M2的源极连接电流源I2,PMOS开关管M1的漏极接PMOS管M3的源极,PMOS管M3的漏极通过负载电阻RL1接地,PMOS开关管M2的漏极接PMOS管M4的源极,PMOS管M4的漏极通过负载电阻RL2接地,PMOS开关管M1的源极和PMOS开关管M2的源极之间串联有电阻Rs和电容Cs,电阻Rs与电容Cs并联,PMOS管M3和PMOS管M4的栅极分别受片内电压Vctrl的控制。

本发明具体应用时,输入差分信号Inp/n来控制PMOS管M1/PMOS管M2的开启和关断,PMOS管M1和PMOS管M2的源极连接电流源I1和电流源I2,同时,在两差分源极引入源极串联电阻Rs和电容Cs,电阻Rs和电容Cs在电路传输函数中引入一个零点,能够抬升在对应频率下的电路频率,通过合理设置Rs和Cs的值,能够将零点放置在合理的频率点,从而抵消寄生效应对整体电路频率响应带来的衰减作用,从而起到增大电路工作频率的作用。

PMOS开关管M1与负载电阻RL1之间以及PMOS开关管M2与负载电阻RL2之间,分别串联插入两个栅极受片内电压Vctrl控制的PMOS管M3和PMOS管M4,使得PMOS管M3和PMOS管M4工作在特定工作区,保证PMOS管M3或PMOS管M4与串联的PMOS开关管M1或PMOS开关管M2阻抗保持不变,不受开关管高速开关的影响,从而将信号反射降低。

通过以上技术方案的实施,能够进一步提升HCSL电平驱动器的工作频率,经过仿真测试,用本发明实现的HCSL电平驱动电路,最高工作频率可达400MHz。

最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细地说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

- 一种高速输出的HCSL电平驱动电路

- 一种可实现输出高电平转换的输出驱动电路