具有内存的芯片

文献发布时间:2023-06-19 11:22:42

技术领域

本发明涉及一种芯片,尤其涉及一种具有内存的芯片。

背景技术

芯片是一种用以执行特定功能或通用功能的集成电路。芯片包含控制电路及内存。内存除了提供芯片运作时使用外,部分芯片的内存储存有固件(Firmware),固件是芯片的基本驱动程序,芯片通过其固件执行该芯片之功能,此外,与该芯片连接的装置能通过该芯片的韧体而得知该芯片的类型及作用性。

因应客制化或不同的应用情形,芯片的固件有更新的需求,固件的更新是通过芯片的通信界面来进行。然而,不同的芯片具有不同的通信界面,例如I2C、SMBus(SystemManagement Bus)、通用串行总线(USB,Universal Serial Bus)、串行端口等等,因此,对芯片固件更新,除了需符合该芯片的通信界面外,更新时的传输速度会受限于传通信界面的传输速度。

发明内容

鉴于上述说明,本发明提供一种具有内存的芯片,适于对该内存内的固件进行更新。

依据一些实施例,芯片包含一电源引脚、一接地引脚、多个输入输出引脚、一可读写内存、一切换电路、以及一控制电路。输入输出引脚包含多个映像引脚以及一控制引脚。可读写内存包含一频率端口、多个输入输出端口、以及一致能端口。控制电路依据该控制引脚选择性地致动或不致动该切换电路,当切换电路被致动时,切换电路将频率端口、输入输出端口、以及致能端口分别电性连接映像引脚。

依据一些实施例,芯片包含一芯片电路。当切换电路未被致动时,映像引脚、频率端口、输入输出端口、以及致能端口经由切换电路电性连接芯片电路。

依据一些实施例,控制电路为一逻辑电路,输入输出引脚包含多个控制引脚,在逻辑电路于控制引脚之组合为一默认值时,致动切换电路。

依据一些实施例,控制电路为一主控制器,主控制器依据控制引脚致动切换电路,并将频率端口、输入输出端口、以及致能端口分别电性连接映像引脚。当切换电路未被致动时,频率端口、输入输出端口、以及致能端口经由切换电路分别电性连接主控制器。

因此,依据一些实施例,芯片的切换电路被致动时,可读写内存的频率端口、输入输出端口、以及致能端口分别电性连接映像引脚,烧录装置即可直接通过映像引脚直接控制可读写内存,并刻录可读写内存内的固件,此烧录作业不受限于芯片的通信界面,同时,烧录的传输速度亦不受限于该通信界面的传输速度。

附图说明

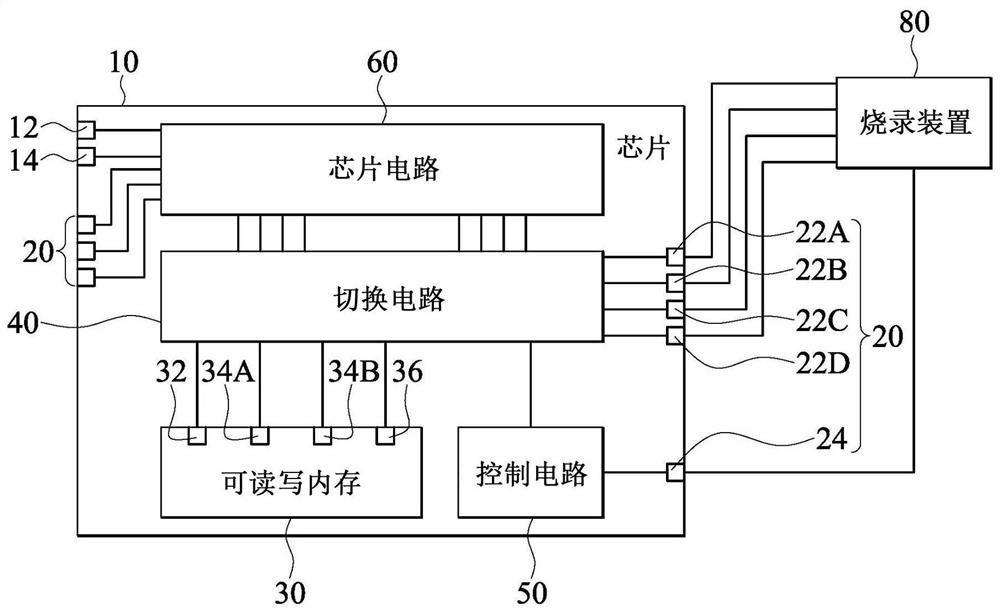

图1示出了依据一些实施例的芯片的方框示意图;

图2示出了依据一些实施例的切换电路的方框示意图;

图3示出了依据一些实施例的芯片的方框示意图;

图4示出了依据一些实施例,控制电路的方框示意图;以及

图5示出了依据一些实施例的芯片的方框示意图。

具体实施方式

参照图1,图1示出了依据一些实施例的芯片10的方框示意图。芯片10包含一电源引脚12、一接地引脚14、多个输入输出引脚20、一可读写内存30、一切换电路40、以及一控制电路50。输入输出引脚20包含多个映像引脚22A~22D以及一控制引脚24。可读写内存30包含一频率端口32、多个输入输出端口34A~34B、以及一致能端口36。控制电路50依据该控制引脚24致动或不致动切换电路40。当切换电路40被致动,切换电路40将频率端口32、输入输出端口34A~34B、以及致能端口36分别电性连接映像引脚22A~22D。

因此,烧录装置80通过控制引脚24,使控制电路50致动切换电路40,切换电路40被致动时,可读写内存30的频率端口32、输入输出端口34A~34B、以及致能端口36分别电性连接映像引脚22A~22D,烧录装置80即可直接通过映像引脚22A~22D直接控制可读写内存30并刻录可读写内存30内的固件,此刻录作业不受限于芯片10的通信界面,同时,刻录的传输速度亦不受限于该通信界面的传输速度。

芯片10是具有可读写内存30的芯片10,该可读写内存30可储存有固件。依据一些实施例,芯片10是通用型集成电路或功能型集成电路,芯片10例如但不限于中央处理器(CPU,Central Processing Unit)、微处理器(Microprocessor)、专用应用集成电路(ASIC,Application-specific Integrated Circuit)、系统单芯片(SOC,System on a Chip)等。

芯片10具有多个引脚,用以与外围装置电性连接及通信。芯片10的引脚包括电源引脚12、接地引脚14、及输入输出引脚20。电源引脚12例如但不限于用以供应芯片10运作的电源的引脚。电源引脚12的电源可以是来自于烧录装置80,或其他外部装置。依据一些实施例,芯片10包括多个电源引脚12。

前述接地引脚14例如但不限于,用以让芯片10以及烧录装置80接地的引脚。在一些实施例中,烧录装置80的接地与该接地引脚14电性连接。依据一些实施例,芯片10包括多个接地引脚14。

烧录装置80(Programmer)用以对芯片10的可读写内存30进行刻录,更新内存30内的数据,烧录装置80可为例如但不限于通用型刻录器(Universal Programmer)、量产型刻录器、专用型刻录器等等。

可读写内存30例如但不限于电可擦除可编程只读存储器(EEPROM,Electrically-Erasable Programmable Read-Only Memory)、闪存(Flash Memory)、及其他非易失性内存(NVM,Non-Volatile Memory)。可读写内存30的频率端口32用以接收外部提供的频率信号,可读写内存30依据该频率运作。可读写内存30的输入输出端口34A~34B用于接收或传送可读写内存30的数据。可读写内存30的致能端口36用以供外部装置控制可读写内存30,具体而言,外部装置例如但不限于微处理器,微处理器产生一致能信号,以致能可读写内存30。在一些实施例中,该致能信号为一电平信号。例如,电平信号为高电平时,表示致能;电平信号为低电平时,表示不致能。但并不以此为限,电平信号为低电平时,表示致能;电平信号为高电平时,表示不致能。在一些实施例中,致能信号为一序列信号,例如,当微处理器传送一序列信号至致能端口36,可读写内存30在序列信号的内容符合一致能序列时,可读写内存30即被致能,反之,可读写内存30即不被致能。

在一些实施例中,芯片10包含一芯片电路60。芯片电路60用以存取可读写内存30的数据,并用以执行芯片10的功能。依据一些实施例,芯片10有两种模式,一种为烧录模式、一种为常态模式。当切换电路40未被控制电路50致动时,即常态模式,此时,映像引脚22A~22D、频率端口32、输入输出端口34A~34B、以及致能端口36经由切换电路40电性连接芯片电路60,且芯片10执行其既有的功能。

在一些实施例中,芯片电路60包含一主控制器62(如图3所示),主控制器62用以存取该可读写内存30的数据。当切换电路40未被控制电路50致动时,即常态模式,频率端口32、输入输出端口34A~34B、以及致能端口36经由切换电路40电性连接主控制器62,因此,主控制器62能存取与控制可读写内存30。

参照图2,图2示出了依据一些实施例的切换电路40的方框示意图。芯片10的切换电路40包括多个开关42A~42H,部分的开关42E~42H分别对应可读写内存30的频率端口32、输入输出端口34A~34B及致能端口36,另一部分的开关42A~42D分别对应芯片10的映像引脚22A~22D。当芯片10的切换电路40未被致动时,映射引脚22A~22D经由部分的开关42A~42D电性连接至芯片电路60,频率端口32、输入输出端口34A~34B、以及致能端口36经由另一部分的开关42E~42H电性连接至芯片电路60,因此,芯片电路60能执行芯片10的功能。当芯片10的切换电路40被致动时,可读写内存30的频率端口32、输入输出端口34A~34B、以及致能端口36分别电性连接映像引脚22A~22D。以开关42A及开关42E为例,开关42A对应芯片电路的接点61A及映射引脚22D,开关42E对应致能端口36及芯片电路的接点61E,开关42A对应开关42E,当开关42A及开关42E未被致动时,开关42A电性连接映射引脚22D至接点61A,开关42E电性连接致能引脚36至接点61E。当开关42A及开关42E被致动时,开关42A通过开关切换将映射引脚22D电性连接至致能引脚36。

前述控制电路50依据该控制引脚24选择性地致动或不致动切换电路40。在一些实施例中,控制引脚24接收一电平信号或一序列信号,且控制电路50依据接收的信号选择性地致动或不致动该切换电路40。例如,电平信号为高电平时,表示致动;电平信号为低电平时,表示不致动。但并不以此为限,电平信号为低电平时,表示致能;电平信号为高电平时,表示不致能。例如,当微处理器传送一序列信号至控制引脚24,控制电路50在序列信号的内容符合一致动序列时,致动切换电路40,反之,不致动切换电路40。在一些实施例中,控制电路50包含一主控制器,该主控制器电性连接控制引脚24,并接收外部提供的电平信号或数字序列。

参照图3,图3示出了依据一些实施例的芯片电路60A的方框示意图。在一些实施例中,控制电路50A为一逻辑电路,输入输出引脚20包含多个控制引脚24A~24C,在逻辑电路于控制引脚24A~24C的组合为一默认值时,致动切换电路40,进入烧录模式。依据一些实施例,逻辑电路具有一个或多个输入端,其可分别电性连接控制引脚24A~24C,用以输出至少一逻辑结果。逻辑电路可以是但不限于一个逻辑门,也可以是多个逻辑门的组合,其中逻辑门例如但不限于反相器、与门、或门、互斥或门、缓冲门或其他逻辑门等。默认值可为逻辑0与逻辑1的组合。

参照图4,图4示出了依据一些实施例的控制电路50B的方框示意图。控制电路50B包含一驱动电路52以及一通讯电路54。通讯电路54电性连接控制引脚24,并根据控制引脚24接收的信号,致动驱动电路52。当驱动电路52被致动时,致动切换电路40,使芯片10进入烧录模式。依据一些实施例,通讯电路54可以是例如但不限于RS232的通信界面。依据一些实施例,驱动电路52可以是例如但不限于放大控制信号的电路。

参照图5,图5示出了依据一些实施例的芯片10的方框示意图。控制电路50C为一主控制器,主控制器依据该控制引脚24接收的信号致动切换电路40,即进入烧录模式,将频率端口32、输入输出端口34A~34B、以及致能端口36分别电性连接映像引脚22A~22D。在此实施例中,控制电路50C(主控制器)与烧录装置80之间可以是但不限于以I

综上所述,在一些实施例中,芯片10的切换电路40被致动时,可读写内存30的频率端口32、输入输出端口34A~34B、以及致能端口36分别电性连接映像引脚22A~22D,烧录装置80即可直接通过映像引脚22A~22D直接控制可读写内存30并烧录可读写内存30内的固体,此烧录作业不受限于芯片的通信界面,同时,烧录的传输速度亦不受限于该通信界面的传输速度。

【符号说明】

10 芯片 12电源引脚

14 接地引脚 20 输入输出引脚

22A~22D映射引脚 24、24A~24C控制引脚

30 可读写内存 32频率端口

34A~34B输入输出端口 36致能端口

40 切换电路 42A~42H开关

50、50A~50C 控制电路 52驱动电路

54 通讯电路 60、60A~60B芯片电路

61A、61A”接点 61E、61E” 接点

62 主控制器 80烧录装置。

- 基于内存芯片互连的内存访问处理方法、内存芯片及系统

- 控制内存芯片的方法、芯片控制器和内存控制器