一种降低导通电阻的Trench MOSFET结构

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及的是一种降低导通电阻的Trench MOSFET结构,属于半导体技术领域。

背景技术

随着半导体集成电路技术的不断发展,芯片尺寸不断缩小,操作电压也越来越小,因此对电源管理尤其是低压直流-直流降压转换的效率的要求越来越高,高效率小体积开关模式电源应运而生。

这种功率MOS器件的应用相当广泛,可普及到现代生活的每一个角落。比如在PC、笔记本电脑领域,同时电动车、油电混合车(新能源车)、快速充电、无线充电等领域的应用也正在快速兴起,几乎所有的这些领域都用到这种功率MOSFET器件,而Trench MOSFET则是这个大家庭的重要成员。

众所周知,功率MOSFET的击穿电压与导通电阻间的矛盾关系备受关注,往往在优化导通电阻的同时,其击穿电压也会下降。

现有技术传统低压Trench MOSFET器件结构其漏极位于衬底层背面,其导通电阻主要由源极接触电阻、源区体电阻、沟道电阻、积累层电阻、寄生结型晶体管电阻,漂移层电阻、衬底电阻、以及漏极接触电阻组成,在低压Trench MOSFET中,漂移层电阻约占比23%。

发明内容

本发明提出的是一种降低导通电阻的Trench MOSFET结构,其目的旨在克服现有技术存在的上述不足,通过位于衬底层表面的N+漏极,在器件开通时,载流子直接通过界面漏区N+和源区N+之间的N-漂移区,大大缩短了载流子在低掺杂区即高阻区的运动距离,从而降低器件导通电阻。

本发明的技术解决方案:一种降低导通电阻的Trench MOSFET结构,其结构包括衬底层和位于衬底层表面的源区金属层、漏区金属层、栅区金属层;衬底层上方与源区金属层、漏区金属层、栅区金属层之间从下至上依次设有水平N+漏层、N-漂移区、P型阱区层和N+型源区层;还包括双沟槽结构:槽型多晶硅栅区和槽型场氧;槽型场氧右侧设与水平N+漏层连接的纵向N+漏区;源区金属层、漏区金属层、栅区金属层分别通过接触孔内金属分别与N+型源区层、纵向N+漏区、槽型多晶硅栅区连接。

优选的,所述的水平N+漏层和纵向N+漏区,其重掺杂为低阻区。

优选的,所述的N-漂移区,其轻掺杂为高阻区。

优选的,所述的P型阱区层高度不超过沟槽结构的底部。

优选的,所述的槽型多晶硅栅区顶部位于N+型源区层的底部之上。

优选的,所述的槽型多晶硅栅区内壁及底部附有绝缘栅氧化层,绝缘栅氧化层中间填充有多晶硅,多晶硅与绝缘栅氧化层侧面端及底部接触。

优选的,所述的多晶硅的高度小于沟槽结构的深度。

优选的,所述的槽型场氧贯穿N+型源区层、P型阱区层及N-漂移区,槽型场氧底部与水平N+漏层表面接触,槽型场氧内填充二氧化硅。

优选的,还包括绝缘介质层,绝缘介质层位于N+型源区层上方,绝缘介质层上开有接触孔。

本发明的优点:结构设计合理,利用表面漏区缩短了载流子在高阻区的漂移路径,能有效的减少其导通电阻。具体的,衬底层表面N+漏区,同时采用双氧化槽:槽型场氧和槽型多晶硅栅,器件开通时,利用表面N+漏区结构,降低了载流子在漂移区的漂移距离;器件关断时,利用槽型场氧右侧薄硅内将存在大量电离施主正电荷,能有效地均匀整个有源区电场分布,有利于器件横向尺寸的进一步缩小。

附图说明

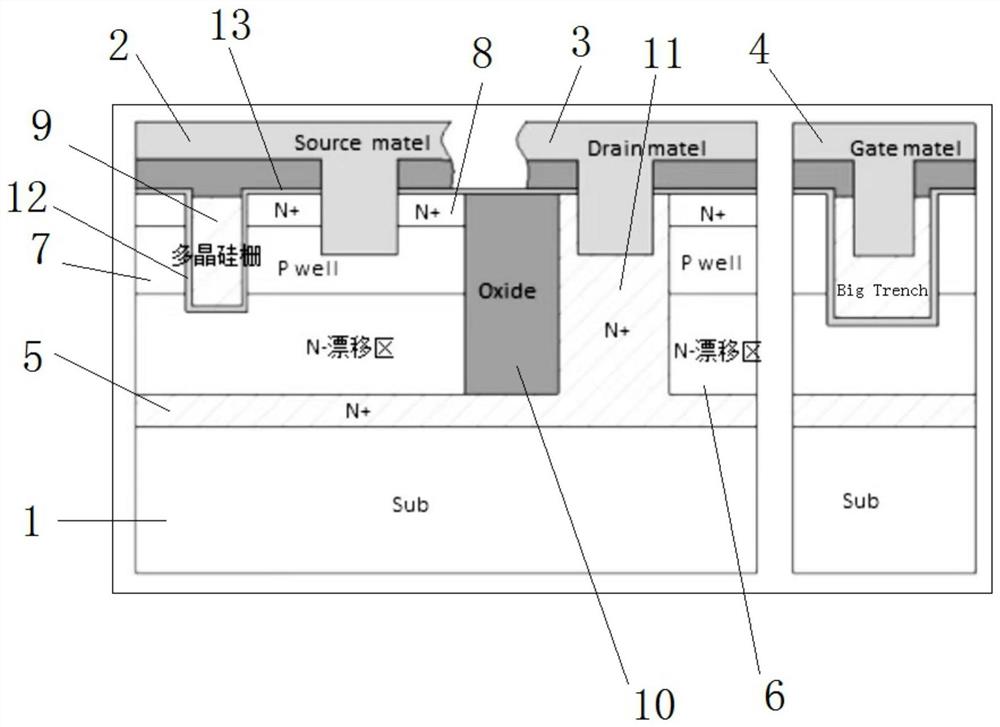

图1是本发明降低导通电阻的Trench MOSFET结构的结构示意图。

图中的1是衬底层、2是源区金属层、3是漏区金属层、4是栅区金属层、5是水平N+漏层、6是N-漂移区、7是P型阱区层、8是N+型源区层、9是槽型多晶硅栅区、10是槽型场氧、11是纵向N+漏区、12是绝缘栅氧化层、13是绝缘介质层。

具体实施方式

下面结合实施例和具体实施方式对本发明作进一步详细的说明。

如图1所示,一种降低导通电阻的Trench MOSFET结构,其结构包括衬底层和位于衬底层表面的源区金属层(Source matel)、漏区金属层(Drain matel)、栅区金属层(Gatematel);衬底层上方与源区金属层、漏区金属层、栅区金属层之间从下至上依次设有水平N+漏层、N-漂移区、P型阱区层(P well)和N+型源区层;还包括双沟槽结构:槽型多晶硅栅区和槽型场氧(Oxide);槽型场氧右侧设与水平N+漏层连接的纵向N+漏区;源区金属层、漏区金属层、栅区金属层分别通过接触孔内金属分别与N+型源区层(源区体区)、纵向N+漏区(N+漏区)、槽型多晶硅栅区(栅区多晶硅)连接。

所述的水平N+漏层和纵向N+漏区,其重掺杂为低阻区。

所述的N-漂移区,其轻掺杂为高阻区。

所述的P型阱区层高度不超过沟槽结构的底部。

所述的槽型多晶硅栅区顶部位于N+型源区层(源极区)的底部之上。

所述的槽型多晶硅栅区内壁及底部附有绝缘栅氧化层,绝缘栅氧化层中间填充有多晶硅,多晶硅与绝缘栅氧化层侧面端及底部接触。

所述的多晶硅的高度小于沟槽结构的深度。

所述的槽型场氧贯穿N+型源区层、P型阱区层及N-漂移区,槽型场氧底部与水平N+漏层(N+低阻层)表面接触,槽型场氧内填充二氧化硅。

还包括绝缘介质层,绝缘介质层位于N+型源区层上方,绝缘介质层上开有接触孔,接触孔穿过绝缘介质层、延伸至P型阱区层、纵向N+漏区、Big Trench(Cell区沟槽内多晶硅栅通过版图设计的bus line到Big Trench连接到Gate matel形成栅极)内。

器件结构具体描述如下:

水平N+漏层厚度1.5um,槽型场氧宽度0.3~0.7um、厚度3~6um,N+漏区层(水平N+漏层和纵向N+漏区)浓度10e19cm-3;其Ronsp会随着槽型场氧宽度和厚度的增加而增加,槽型场氧宽度的增加意味着晶胞尺寸的变大,槽型场氧厚度的增加意味着高阻的N-漂移区变厚;此结构仅适用于低压Trench MOSFET。

以上所述各结构均为现有技术,本领域技术人员可使用任意可实现其对应功能的现有设计。

以上所述的仅是本发明的优选实施方式,应当指出,对于本领域的普通技术人员来说,在不脱离本发明创造构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。

- 一种降低导通电阻的Trench MOSFET结构

- 一种降低低压Trench DMOS导通电阻的制造方法