半导体封装

文献发布时间:2023-06-19 11:54:11

技术领域

本发明涉及半导体技术领域,尤其涉及一种半导体封装。

背景技术

无源部件是不产生电力,但消耗电力、存储和/或释放电的电力。无源元件包括电阻器、电容器和电感器。在大多数电路中,无源部件连接到有源部件,有源部件通常是半导体器件,例如放大器和逻辑芯片。

因此,如何与半导体器件连接以提高传输速度已成为工业上的重要任务。

发明内容

有鉴于此,本发明提供一种半导体封装,以解决上述问题。

根据本发明的第一方面,公开一种半导体封装,包括:

第一基板;

第二基板;

导电部件,设置在该第一基板和该第二基板之间,其中,该第一基板和该第二基板彼此隔开间隔;

电子部件,设置在该间隔内;以及

无源部件,设置在该间隔内。

根据本发明的第二方面,公开一种半导体封装,包括:

第一基板,包括第一最外侧导电层;

第二基板,包括第二最外侧导电层;

导电部件,设置在该第一基板和该第二基板之间,其中,该第一基板和该第二基板彼此隔开一定间隔;

电子部件,设置在该间隔内;以及

有无源部件,设置在该间隔内,其中该无源部件通过穿过该第一最外层导电层、该导电部件和该第二最外层导电层的导电路径与该电子部件电连接。

本发明的半导体封装由于具有:第一基板;第二基板;导电部件,设置在该第一基板和该第二基板之间,其中,该第一基板和该第二基板彼此隔开间隔。电子部件,设置在该间隔内;以及无源部件,设置在该间隔内。采用这种方式,电子部件与无源部件之间的导电路径较短,可以缩短两者的连接路径,信号的传递更快。

附图说明

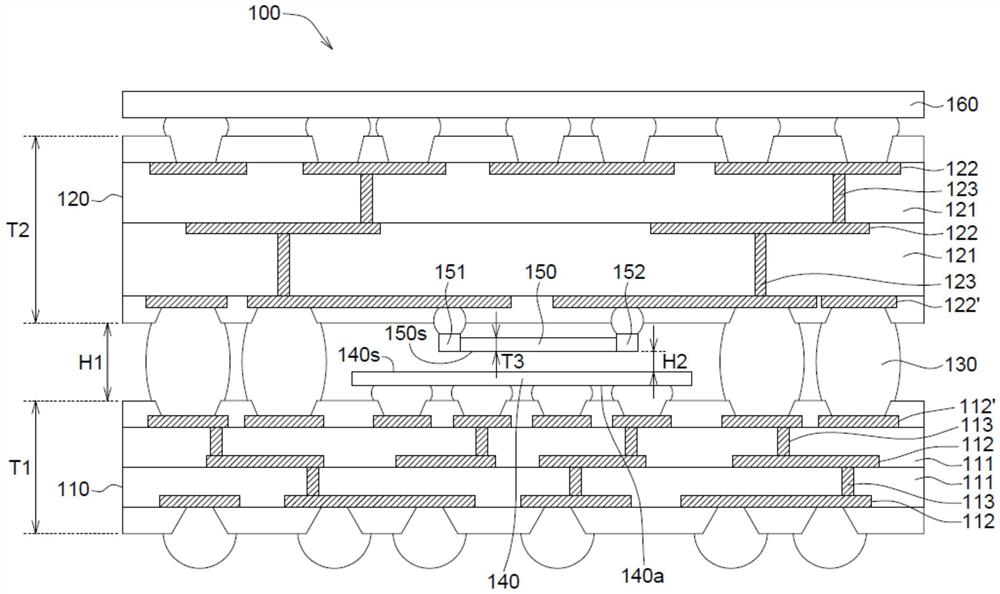

图1示出了根据本发明实施例的半导体封装的示意图;

图2示出了根据本发明另一实施例的半导体封装的示意图;

图3示出了根据本发明另一实施例的半导体封装的示意图;

图4示出了根据本发明另一实施例的半导体封装的示意图。

具体实施方式

参照图1,图1示出了根据本发明实施例的半导体封装100的示意图。半导体封装件100可以应用于电子设备,诸如移动电话、膝上型计算机、平板计算机、台式计算机等。半导体封装件例如是PoP(Package-On-Package,封装上封装)结构。

半导体封装件100包括第一基板110、第二基板120、至少一个导电部件130、至少一个电子部件140和至少一个无源部件150。导电部件130设置在第一基板110和第二基板120之间,第一基板110和第二基板120彼此隔开间隔H1。电子部件140和无源部件150均设置在间隔H1内。因此,电子部件140和无源部件150可以通过短(或更短)的导电路径电连接,因此,它可以提高电子部件140和无源部件150之间的信号传输速度。

另外,第一基板110具有厚度T1,第二基板120具有厚度T2,其中间隔H1可以小于厚度T1和/或厚度T2。因此,与将无源元件150布置在与电子元件140相对的第一基板110上(垂直导电路径行进穿过厚度T1)相比,从电子部件140到无源部件150的垂直导电路径更短。具体来说,通常无源元件150安装在第一基板110的与安装电子部件140的相对侧(图1中第一基板110的下表面),先前技术的这种方式使得电子部件140和无源部件150之间的电性连接路径需要通过导电通孔113,而导电通孔113的阻抗较大,这样电子部件140和无源部件150之间电连接路径阻抗较大,并且连接路径较长,不利于电子部件140和无源部件150之间的信号传送。本发明图1的方案将无源部件150安装在第一基板120的下表面,并且与电子部件140相邻设置,这样电子部件140和无源部件150之间的电性连接路径无需经过导电通孔113等之类的通孔,因此电子部件140和无源部件150之间电连接路径阻抗较小,并且连接路径更短,从而可以提高电子部件140和无源部件150之间的信号传输速度。并且图1的这种方式在制造时,可以让电子部件140形成在第一基板110上,让无源部件150形成在第二基板120上,之后通过导电部件130将带有电子部件140的第一部件110和带有无源部件150的第二基板120连接在一起,这种分别分开制造,然后再进行组装的方式更加方便制造,并且组装方式灵活,可以根据所需自由调整组装在一起封装。

在一个实施例中,间隔H1例如在100微米至270微米之间。无源部件150具有例如在90微米和150微米之间的范围内的厚度T3。这样以便在间隔H1中放置无源部件150和电子部件140。

第一基板110可以是单层结构或多层结构。就多层结构而言,第一基板110包括多个介电层111、至少一个导电层112和至少一个导电通孔113,其中,一个导电层112形成在相邻的两个介电层111之间,并且相邻两个导电层112与至少一个导电通孔113电连接。在本实施例中,每个导电层112在第一方向上延伸并且包括至少一个导电迹线和/或至少一个导电垫。第一方向例如是第一基板110的平面的延伸方向,例如水平方向。电子部件140和无源部件150可以通过导电层112电连接。

就材料而言,导电层112和/或导电通孔113可以由包括例如铜等的材料制成。

在本实施例中,每个导电通孔113在第二方向上延伸。第二方向基本上垂直于第一方向。第二方向例如是第一基板110的厚度的延伸方向,例如垂直(或竖直)方向。

第二基板120例如是中介层。第二基板120可以是单层结构或多层结构。在多层结构方面,第二基板120包括多个介电层121,至少一个导电层122和至少一个导电通孔123,其中一个导电层122形成在相邻的两个介电层121之间,并且相邻两个导电层122与至少一个导电通孔123电连接。在本实施例中,每个导电层122沿第三方向延伸并且包括至少一个导电迹线和/或至少一个导电垫。另外,第三方向例如是第一基板120的平面的延伸方向,例如水平方向。电子部件140和无源部件150可以通过导电层122电连接。

就材料而言,导电层122和/或导电通孔123可以由包括例如铜等的材料制成。

在本实施例中,每个导电通孔123在第四方向上延伸。第四方向基本垂直于第三方向。第四方向例如是第二基板120的厚度的延伸方向,例如垂直(竖直)方向。

导电部件130例如是焊球。电子部件140和无源部件150可以通过导电部件130电连接。

就导电率而言,导电部件130的导电率例如低于导电层112和导电层122的导电率。另外,导电部件130在第二方向或第四方向上将第一基板110和第二基板120电连接。因此,导电层112和123可以提高电子部件140和无源部件150之间的传输速度。

第一基板110的导电层112包括第一最外部导电层112’。第二基板120的导电层122包括第二最外部导电层122’、电子部件140直接或间接与第一最外部导电层112’连接。第一最外导电层112’与无源部件150与第二最外导电层122'直接或间接连接,其中,导电部件130连接第一最外导电层112'和第二最外导电层122’。因此,无源部件150通过穿过第一最外部导电层112’、导电部件130和第二最外部导电层122’的导电路径与电子部件140电连接。由于导电路径行进穿过最外层导电层,因此阻抗损耗低,并且导电路径中信号的传输速度较高。另外,导电路径大部分行进穿过具有较高导电性(高于导电部件130的导电性)的导电层,因此阻抗损耗低并且在导电路径中的传输速度较高。

在一个实施例中,电子部件140例如是逻辑芯片等。在一个实施例中,无源部件150例如是电阻器、电感器和/或电容器。

在本实施例中,电子部件140设置在第一基板110上,无源部件150设置在第二基板上,其中无源部件150和电子部件140以背对背的方式设置。例如,电子部件140具有第一背面140s,无源部件150具有第二背面150s,其中第一背面140s和第二背面150s彼此面对。

在另一个实施例中,电子部件140设置在第二基板120上,而无源部件150设置在第一基板110上。

另外,电子部件140例如是倒装芯片。例如,电子部件140具有与第一背面140s相对的有源表面140a,其中有源表面140a面对第一基板110。无源部件150包括与第二最外部导电层122'电连接的第一电极151和第二电极152。

在本实施方式中,第一背面140s与第二背面150s隔开间隔H2。因此,可以避免电子部件140和无源部件150之间的干扰应力。在另一个实施例中,第一背面140s可以与第二背面150s接触。因此,在第一后表面140s和第二后表面150s之间产生了导热通道(或路径),例如电子部件140的热量通过与之接触的无源部件150、第二最外部导电层122'、导电通孔123、导电层122等散发出去,提高散热效率,保证封装的正常运行。

另外,如图1所示,半导体封装100还包括至少一个电子设备160,例如存储器。电子设备160设置在第二基板120上。电子设备160可以通过导电层122和导电通孔123与无源部件150电连接。此外,电子设备160可以通过导电层122、导电通孔123和第一最外部导电层112'与电子组件140电连接。

参照图2,图2示出了根据本发明另一实施例的半导体封装200的示意图。

半导体封装200包括第一基板110、第二基板120、至少一个导电部件130、至少一个电子部件140、至少一个无源部件150以及至少一个电子设备160。

半导体封装件200包括与半导体封装件100相同或相似的特征,不同之处在于无源部件150和电子部件140并排设置。

电子部件140和无源部件150都设置在第一基板110上。在另一个实施例中,电子部件140和无源部件150都可以设置在第二基板120上。

在本实施例中,电子部件140具有面对第一基板110的有源表面140a,而无源部件150包括与第一最外导电层112'电连接的第一电极151和第二电极152。

在本实施例中,第一基板110的导电层112包括第一最外部导电层112',并且电子部件140和无源部件150与第一最外部导电层112'直接或间接连接。图2的这种方式可以使电子部件140和无源部件150之间导电路径更短,例如电子部件140和无源部件150可以通过第一外部导电层112'电连接(虽然图2中未示出,但是图2仅是截面图,在同一层中的第一外部导电层112'在图中未示出的地方可以相互连接),这样电子部件140和无源部件150之间的电路路径的阻抗也较小,可以提高电子部件140和无源部件150之间的信号传输速度。此外,电子部件140和无源部件150并排放置可以让第一基板110和第二基板120之间的间隔无需太大,从而减小封装的尺寸。

参照图3,图3示出了根据本发明另一实施例的半导体封装300的示意图。

半导体封装300包括第一基板110、第二基板120、至少一个导电部件130、至少一个电子部件140、至少一个无源部件150以及至少一个电子设备160。

半导体封装300包括与半导体封装100相同或相似的特征,不同之处在于无源部件150直接或间接设置在电子部件140上。因此,无源部件150在不穿过第一基板110的导电层112、第二基板120的导电层122和导电部件130的情况下,可以通过短(较短或最短)的导电路径与电子部件140电连接。

在本实施例中,无源部件150设置在电子部件140和第二基板120之间。例如,无源部件150包括设置在第一背面上的第一电极151和第二电极152。电子部件140的140s(面向第二基板120)并与电子部件140电连接。

另外,无源部件150的第二后表面150s可以与第二基板120分离,或者与第二基板120接触。图3中的方式可以使无源部件150和电子部件140之间的导电路径更短,电子部件140和无源部件150之间的电路路径的阻抗也较小,可以提高电子部件140和无源部件150之间的信号传输速度。

参照图4,图4示出了根据本发明另一实施例的半导体封装400的示意图。

半导体封装400包括第一基板110、第二基板120、至少一个导电部件130、至少一个电子部件140、至少一个无源部件150以及至少一个电子设备160。

半导体封装件400包括与半导体封装件300相同或相似的特征,不同之处在于无源部件150布置在电子部件140和第一基板110之间。无源部件150包括第一电极151和第二电极152、第一电极151和第二电极152设置在电子部件140的有源表面140a上(面对第一基板110)并且与电子部件140电连接。

另外,电子部件140的第一后表面140s可以与第二基板120分离,或者与第二基板120接触。图4中的方式可以使无源部件150和电子部件140之间的导电路径更短,电子部件140和无源部件150之间的电路路径的阻抗也较小,可以提高电子部件140和无源部件150之间的信号传输速度。并且无源部件150布置在电子部件140和第一基板110之间可以节省安装空间,使得第一基板110与第二基板120之间的间隔无需过大,从而减小封装尺寸。在图4的实施例中,可以通过高度较高的连接元件连接电子部件140与第一最外部导电层112’,这样可以留出放置无源元件150的空间,当然该连接元件的高度小于导电部件130的高度。无源元件150的第一电极151和第二电极152可以是例如通过连接元件直接连接到电子部件140,或者连接到第一最外部导电层112’以间接的连接到电子部件140。

本领域的技术人员将容易地观察到,在保持本发明教导的同时,可以做出许多该装置和方法的修改和改变。因此,上述公开内容应被解释为仅由所附权利要求书的界限和范围所限制。

- 半导体封装方法、半导体封装和堆叠半导体封装

- 半导体封装、半导体封装结构及制造半导体封装的方法