一种芯片可靠性评估方法、装置及芯片

文献发布时间:2023-06-19 13:45:04

技术领域

本发明涉及芯片领域,具体地涉及一种芯片可靠性评估方法、装置及芯片。

背景技术

可靠性预计是芯片可靠性设计的关键环节,其根据芯片组成的工艺、元器件、封装形式等推测出芯片的可靠性。目前芯片的可靠性预计方法主要有两大类:一是以《美国军用手册-电子设备可靠性预计(MIL-HDBK-217)》为蓝本制定的手册/标准的预计方法;二是基于失效物理(POF)的可靠性评价,是通过分析和检测找出失效原因,从本质上分析失效。其中基于手册的可靠性预计以经验的故障率模型为基础,需要大量的环境数据以及芯片运行数据,在准确性上很多局限。而失效物理法采用失效物理法预计芯片的可靠性,实验采用加速寿命的方法进行预测,但无法对芯片设计提供指导,是等芯片制造出来后对芯片可靠性的评估。

上述两种方法都仅仅考虑了过电干扰、热等环境对芯片的影响,没有考虑电磁干扰对芯片的影响。随着电力设备变电站就地化、小型化,以及高功率器件与低压芯片的合封趋势,强的电磁干扰对芯片的可靠性的影响将不能忽略,而电磁干扰的种类以及波形种类复杂多样,如何评价芯片在强的电磁干扰下的可靠性成为目前业界的难题。

发明内容

本发明实施例的目的是提供一种芯片可靠性评估方法、装置及芯片,所述芯片可靠性评估方法实现了芯片在不同电磁干扰下的可靠性的评估。

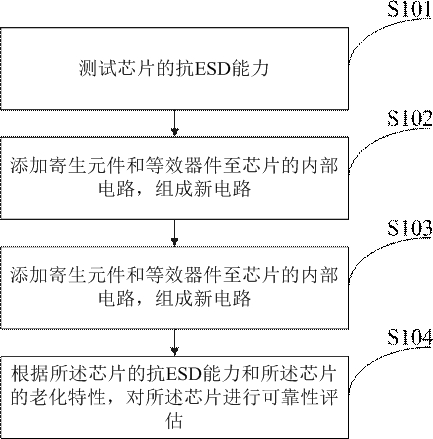

本发明提出了一种芯片可靠性评估方法,包括测试芯片的抗ESD能力;添加寄生元件和等效器件至芯片的内部电路,组成新电路,其中,所述寄生元件为所述芯片在电磁干扰下产生的电容和/或电感,所述等效器件为芯片封装等效的电阻和/或电感;对所述新电路进行老化测试,以确定所述芯片的老化特性;根据所述芯片的抗ESD能力和所述芯片的老化特性,对所述芯片进行可靠性评估。

可选的,所述测试芯片抗ESD能力,包括:对所述芯片中的器件进行TLP测试,以确定所述器件的最大脉冲电流;根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力。

可选的,所述根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力,包括:对所述器件施加HBM等效脉冲,测试所述器件的回滞曲线,根据所述回滞曲线和所述器件的最大脉冲电流,确定所述芯片的抗ESD能力。

可选的,所述对所述新电路进行老化测试确定所述芯片的老化特性,包括:根据所述芯片的内部电路和寄生元件建立SPICE模型;在恒定温度和电压下,输入干扰信号至所述芯片,建立所述芯片内部电路各个器件的老化模型;将等效器件添加至所述芯片的内部电路建立封装后的芯片网表;将所述SPICE模型带入所述芯片网表中进行仿真,将仿真结果带入所述老化模型,得到所述芯片的老化特性。

可选的,所述SPICE模型包括衬底二极管。

可选的,所述老化模型至少包括:温度、电压、干扰信号的个数、干扰信号的幅值;所述仿真结果包括器件的承受电压及干扰信号。

相应的,本发明实施例还提供一种芯片可靠性评估装置,包括:ESD测试单元,用于测试芯片的抗ESD能力;老化测试单元,用于对新电路进行老化测试确定所述芯片的老化特性;所述新电路包括:寄生元件、等效器件及芯片的内部电路,其中,所述寄生元件为所述芯片在电磁干扰下产生的电容和/或电感,所述等效器件为芯片封装等效的电阻和/或电感;评估单元,用于根据所述芯片的抗ESD能力和所述芯片的老化特性对所述芯片进行可靠性评估。

可选的,所述测试芯片的抗ESD能力,包括:对所述芯片中的器件进行TLP测试,以确定所述器件的最大脉冲电流;根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力。

可选的,所述根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力,包括:对所述器件施加HBM等效脉冲,测试所述器件的回滞曲线,根据所述回滞曲线和所述器件的最大脉冲电流,确定所述芯片的抗ESD能力。

可选的,所述对所述新电路进行老化测试确定所述芯片的老化特性,包括:根据所述芯片的内部电路和寄生元件建立SPICE模型;在恒定温度和电压下,输入干扰信号至所述芯片,建立所述芯片内部电路各个器件的老化模型;将等效器件添加至所述芯片的内部电路建立封装后的芯片网表;将所述SPICE模型带入所述芯片网表中进行仿真,将仿真结果带入所述老化模型,得到所述芯片的老化特性。

相应的,本发明实施例还提供一种芯片,所述芯片至少包括:根据上述所述的芯片可靠性评估方法确定的可靠的ESD电路及内部电路。

本发明提出的芯片可靠性评估方法,包括:测试芯片的抗ESD能力;添加寄生元件和等效器件至芯片的内部电路,组成新电路,其中,所述寄生元件为所述芯片在电磁干扰下产生的电容和/或电感,所述等效器件为芯片封装等效的电阻和/或电感;对所述新电路进行老化测试,以确定所述芯片的老化特性;根据所述芯片的抗ESD能力和所述芯片的老化特性,对所述芯片进行可靠性评估。本发明以失效物理的可靠性预计方法为基础,结合电路的老化仿真方法,实现了芯片在不同电磁干扰下可靠性的预测。

本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:

图1和2是本发明的一种芯片可靠性评估方法流程示意图;

图3是本发明的一种测试芯片的ESD电路的退化规律示意图;

图4是本发明的一种芯片进行TLP测试的回滞曲线示意图;

图5是本发明的一种新电路进行老化测试的流程示意图;

图6是本发明的一种电磁干扰波形图。

具体实施方式

以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

发明人通过研究发现,随着电力设备变电站就地化、小型化,以及高功率器件与低压芯片的合封趋势,强的电磁干扰对芯片的可靠性的影响将不能忽略,而电磁干扰的种类以及波形种类都复杂多样。

为了评估不同电磁干扰对芯片可靠性的影响,发明人根据不同电磁信号对芯片的不同损伤程度对电磁信号进行了分类,具体包括:对芯片造成功能性损伤的强电磁信号,类似大的雷击浪涌信号;及只退化芯片性能的弱电磁信号。

所述弱电磁信号又可以分为两类,一类是可被电磁防护电路(ESD电路)防护的信号,如人体模型(HBM),充电设备模型(CDM)和机器模型(MM)等信号,另一类是直接进入芯片核心电路的电磁信号,如宽电压低幅值的脉冲信号。其中,HBM模拟由于人体放电而产生的ESD,这被认为是ESD的主要来源,CDM模拟带电设备与导电材料接触时的放电,MM表示从物体到组件的放电,对象可以是任何工具或生产设备。本发明主要就所述弱电磁信号对芯片的电磁干扰进行可靠性评估。

图1是本发明的一种芯片可靠性评估方法流程示意图,如图1所示,步骤S101为测试芯片的抗ESD能力,按照一种优选的实施方式,所述测试芯片抗ESD能力,包括:对所述芯片中的器件进行TLP测试,以确定所述器件的最大脉冲电流;根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力。

图3是本发明的一种测试芯片的ESD电路的退化规律示意图,如图3所示,步骤S301为对所述芯片中的器件进行TLP测试,以确定所述器件的最大脉冲电流。所述TLP测试是利用传输线产生的矩形短脉冲来测量ESD保护元件的电流-电压特性曲线的方法。图4为TLP测试的回滞曲线的示意图,如图4所示,在进行TLP测试时,先从小电压脉冲开始,逐步增加电压直到获得足够多的数据点,作出完整的电压-电流曲线。通常测试脉冲的幅度会加大到使该彻底损伤为止,获得最大脉冲电流(二次崩溃电流)。

步骤S302为根据所述器件的最大脉冲电流和TLP、HBM的等效关系,确定所述芯片的抗ESD能力。对所述器件施加HBM等效脉冲,测试所述器件的回滞曲线,根据所述回滞曲线和所述器件的最大脉冲电流,确定所述芯片的抗ESD能力。通过对器件施加HBM等效脉冲,来考察不同的HBM冲击时间对器件造成的损伤,例如分别施加1、10、100、1000、10000、100000个数的等效脉冲,施加完毕在分别测试对应不同个数的器件回滞曲线。

步骤S102为添加寄生元件和等效器件至芯片的内部电路,组成新电路。

其中,所述寄生元件为所述芯片由电磁干扰导致器件电学特性与无电磁干扰下差异而等效的电容和/或电感,所述等效器件为芯片封装等效的电阻和/或电感。所述寄生元件的获取方法为分别测试有电磁干扰下的器件电学特性如电流I1、无电磁干扰下的电学行为I2,根据测试指标及差异进行寄生元件的等效。所述等效器件的获取方法为:将所述芯片的封装分别在盐雾/湿度条件下做腐蚀老化试验,得到腐蚀后金属管脚的导电率随时间的变化,从而得到盐雾和湿度对金属管脚导电率的老化公式R= f(t),并对公式建模,实现将封装形式和材质等效为电阻或者电感。

步骤S103为对所述新电路进行老化测试,以确定所述芯片的老化特性。按照一种优选的实施方式,所述对所述新电路进行老化测试确定所述芯片的老化特性,包括:根据所述芯片的内部电路和寄生元件建立SPICE模型;在恒定温度和电压下,输入干扰信号至所述芯片,建立所述芯片内部电路各个器件的老化模型;将等效器件添加至所述芯片的内部电路建立封装后的芯片网表;将所述SPICE模型带入所述芯片网表中进行仿真,将仿真结果带入所述老化模型,得到所述芯片的老化特性。

图5是本发明的一种新电路进行老化测试的流程示意图。如图5所示,步骤S501为根据所述芯片的内部电路和寄生元件建立SPICE模型。SPICE(Simulation Program withIntegrated Circuit Emphasis)用于精确仿真I/O缓冲器、终端和电路板迹线。在现有芯片内部电路中加入寄生器件(例如寄生的电感二极管等器件),通过器件设计、版图绘制以及流片测试、参数提取建立芯片内部电路的SPICE模型,在建立模型过程中考虑衬底二极管,如不包含则通过等效方式将衬底寄生加入SPICE模型当中。

步骤S502为在恒定温度和电压下,输入干扰信号至所述芯片,建立所述芯片内部电路各个器件的老化模型。具体的,将外部的电应力、温度以及电磁信号输入电路中采用SPICE模型进行老化仿真。现有器件可靠性模型不包含外界干扰信号,如在测试中仅仅测试HCI、NBTI等考虑温度、电压应力的器件电学特性老化行为。该类测试仅仅是恒定温度、恒定电压下的老化,而实际芯片在运行中不仅仅需要对器件施加恒定应力,而且会有不规则干扰信号周期性发生,如随时间波形的电压信号,如图6所示。本申请在建立器件老化模型时,不仅考虑恒定温度及电压的变化,还将干扰信号考虑到输入端,建立器件阈值电压、饱和电流等随温度、电压及特定干扰信号个数的老化函数,Vth=f(温度、电压、干扰个数、幅值)。

步骤S503为将等效器件添加至所述芯片的内部电路建立封装后的芯片网表。将封装形式和材质等效为电阻或者电感,在芯片网表中加入等效器件,建立封装后的芯片网表。采用竞争分析理论,取各种封装以及电路寿命最短的做为芯片寿命。

步骤S504为将所述SPICE模型带入所述芯片网表中进行仿真,将仿真结果带入所述老化模型,得到所述芯片的老化特性。所述老化特性包括芯片在不同电压、温度及干扰信号的芯片老化行为,例如电源芯片的输出电压在不同温度、电压及干扰信号下的输出电压,从而得到芯片在电磁干扰信号下的老化特性:V输出=f(温度、电压、干扰信号个数)。采用竞争分析理论,取各种封装以及电路寿命最短的做为芯片寿命。

步骤S104为根据所述芯片的ESD电路的退化规律和所述芯片的老化特性,对所述芯片进行可靠性评估。所述可靠性评估为情况在同样温度、电压及干扰信号个数情况下,电路退化指标比初始未加干扰下变化量小(如电源芯片输出电压变化量小),则所述芯片可靠性高;输出电压变化量大,则所述芯片可靠性低(或可靠性等级区分),可靠性参数以电源芯片为例,包括长时间干扰后的输出电压、转换效率等。

图2是本发明的一种芯片可靠性评估方法流程示意图,如图2所示,本发明为根据不同电磁干扰进行的芯片可靠性测试,该电磁信号为弱电磁信号,该电磁信号只能使芯片的性能指标退化,不影响功能指标。

对于较弱的电磁信号,可被ESD防护电路泄放的,可以首先对GGNMOS等ESD防护电路中的防护器件进行固定脉冲下的TLP测试,得到防护电路关键器件的回滞曲线,得到防护电路的设计窗口。然后持续增加脉冲的次数和脉冲宽度,测量不同脉冲次数和宽度下的器件回滞曲线,得到设计窗口随电磁干扰注入次数的退化规律,进而仿真持续电磁干扰下的ESD电路防护能力,防护电路的可靠性直接决定该种电磁干扰下的芯片寿命,所以电磁防护电路退化规律即是芯片可靠性预测模型。

按照一种优选的实施方式,上述可被ESD泄放的芯片评估包括以下几个步骤:选取芯片,分析初始ESD防护电路,并确认防护电路器件,如GGNMOS器件;针对GGNMOS器件设计测试结构,并流片制造(可与芯片制造同时);建立HBM或其他电磁波形在TLP中的等效脉冲(如宽度、幅值)如将2kV的HBM,等效为100ns、幅值1A的脉冲电流;正常TLP测试,即施加正常脉冲电流,测试各个脉冲下的输出电压点,测试TLP曲线;测试TLP曲线完毕,则对器件施加HBM等效脉冲,来考察不同的HBM冲击时间对器件造成的损伤,如分别施加1、10、100、1000、10000、100000个数的等效脉冲,施加完毕在分别测试对应不同个数的器件回滞曲线,评测各个脉冲个数下的触发电压、维持电压及失效电压随脉冲个数的老化程度,从而建立ESD器件设计窗口随外界干扰之间的老化关系,如 vt1=f(脉冲个数);粗略估计芯片受干扰次数,留取设计窗口随冲击次数带来的老化,足够余量,进行芯片ESD防护电路设计,同时也可以对芯片已有ESD防护电路进行设计窗口评估,评估芯片可承受HBM冲击次数。

对于不能被ESD泄放的电磁干扰信号如稳态的干扰以及持续的低幅值不规则的干扰信号,一方面建立底层器件在电热信号下的老化模型,同时建立因为干扰信号导致的焊接以及衬底产生的寄生电感、二极管等模型,在现有芯片核心电路中加入寄生的电感二极管等器件,随后将外部的电应力、温度以及电磁信号输入电路中采用SPICE模型进行老化仿真,得到芯片指标与电磁热信号下随时间变化的规律,建立电路的可靠性预测模型,在建立电路可靠性预测模型的同时进行电磁干扰下的封装材料失效机理的研究,建立封装可靠性预测模型,采用竞争分析理论,取各种封装以及电路寿命最短的做为芯片寿命,得到芯片可靠性预测模型。

按照一种优选的实施方式,上述不可被ESD泄放(能进入芯片核心电路)的芯片评估包括以下几个步骤:(1)器件SPICE模型建立:通过器件设计、版图绘制以及流片测试、参数提取建立芯片底层器件的SPICE模型,在建立模型过程中考虑衬底二极管,如不包含则通过等效方式将衬底寄生加入SPICE模型当中;(2)器件不同干扰下老化模型建立:现有器件可靠性模型不包含外界干扰信号,如在测试中仅仅测试HCI、NBTI等考虑温度、电压应力的器件电学特性老化行为。该类测试仅仅是恒定温度、恒定电压下的老化,而实际芯片在运行中不仅仅需要对器件施加恒定应力,而且会有不规则干扰信号周期性发生,如随时间波形的电压信号;则在建立器件老化模型时,不仅仅需要考虑恒定温度及电压的变化,还需要将干扰信号考虑到输入端,建立器件阈值电压、饱和电流等随温度、电压及特定干扰信号个数的老化函数,Vth=f(温度、电压、干扰个数、幅值);(3)封装老化:针对一款常用封装,分别在盐雾/湿度条件下做腐蚀老化试验,得到腐蚀后金属管脚的导电率随时间的变化,从而得到盐雾和湿度对金属管脚导电率的老化公式R= f(t),并对公式建模。将封装形式和材质等效为电阻或者电感,在芯片网表中加入等效器件,建立封装后的芯片网表;(4)将器件SPICE模型带入到该网表中进行仿真,仿真得到各个器件的承受电压及干扰信号,在引入器件老化模型,得到芯片在不同电压、温度及干扰信号的芯片老化行为,如电源芯片的输出电压在不同温度、电压及干扰信号下的输出电压,从而得到芯片在电磁干扰信号下的老化特性:V输出=f(温度、电压、干扰信号个数)。

本发明通过测试芯片的抗ESD能力;添加寄生元件和等效器件至芯片的内部电路,组成新电路,其中,所述寄生元件为所述芯片在电磁干扰下产生的电容和/或电感,所述等效器件为芯片封装等效的电阻和/或电感;对所述新电路进行老化测试,以确定所述芯片的老化特性;根据所述芯片的抗ESD能力和所述芯片的老化特性,对所述芯片进行可靠性评估。以失效物理的可靠性预计方法为基础,结合电路的老化仿真方法,实现了芯片在不同电磁干扰下可靠性的预测。

本发明实施例提供的一种芯片可靠性评估装置的具体实施细节及效果可参考前述实施方式,在此则不再赘述。

以上结合附图详细描述了本发明实施例的可选实施方式,但是,本发明实施例并不限于上述实施方式中的具体细节,在本发明实施例的技术构思范围内,可以对本发明实施例的技术方案进行多种简单变型,这些简单变型均属于本发明实施例的保护范围。

另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合。为了避免不必要的重复,本发明实施例对各种可能的组合方式不再另行说明。

此外,本发明实施例的各种不同的实施方式之间也可以进行任意组合,只要其不违背本发明实施例的思想,其同样应当视为本发明实施例所公开的内容。