半导体装置

文献发布时间:2023-06-19 09:26:02

技术领域

本发明涉及半导体装置。

背景技术

日本特开2008-306047号公报(日本特开2008-306047号公报)公开了具有三个分割FET构造的半导体装置。就该半导体装置而言,在半导体衬底的表面之上设置的发射极电极被与三个分割FET构造对应地分割为三个分割发射极电极。使探针与三个分割发射极电极的每一者接触,对三个分割FET构造中的每一者的特性(例如,各分割FET构造的接通电阻或接通电压)进行测定。

就专利文献1公开的半导体装置而言,漂移层及体区域横跨三个分割FET构造而连续地延伸。在三个分割FET构造之间,漂移层及体区域没有被分割。有时仅三个分割FET构造中的一个包含缺陷,由于该缺陷而产生漏电流。该漏电流扩展到横跨三个分割FET构造而延伸的漂移层及体区域的整体。漏电流不仅流入包含缺陷的一个分割FET构造,还流入不包含该缺陷的其他两个分割FET构造。在包含缺陷的一个分割FET构造中应该被测定的漏电流减少。具有缺陷的分割FET构造的特性的测定精度降低。

发明内容

本发明就是鉴于上述课题而提出的,其目的在于提供能够高精度地对多个单元区域的每一者的特性进行测定的半导体装置。

本发明的半导体装置具有半导体衬底、表面侧电极、背面侧电极。半导体衬底具有表面、背面。表面侧电极设置于半导体衬底的表面之上。背面侧电极设置于半导体衬底的背面之上。半导体衬底包含第一单元区域、与第一单元区域相邻的第二单元区域。在第一单元区域形成有第一半导体元件。在第二单元区域形成有第二半导体元件。表面侧电极包含形成于第一单元区域的第一电极、形成于第二单元区域的第二电极。第一半导体元件包含第一电极和形成于第一单元区域的表面侧的第一p区域。第二半导体元件包含第二电极、形成于第二单元区域的表面侧的第二p区域。第一电极与第二电极彼此分离。第一半导体元件的第一p区域与第二半导体元件的第二p区域彼此分离。

通过结合附图进行理解的与本发明相关的以下的详细说明,会使本发明的上述及其他目的、特征、方案以及优点变得明确。

附图说明

图1是实施方式1涉及的半导体装置的概略俯视图。

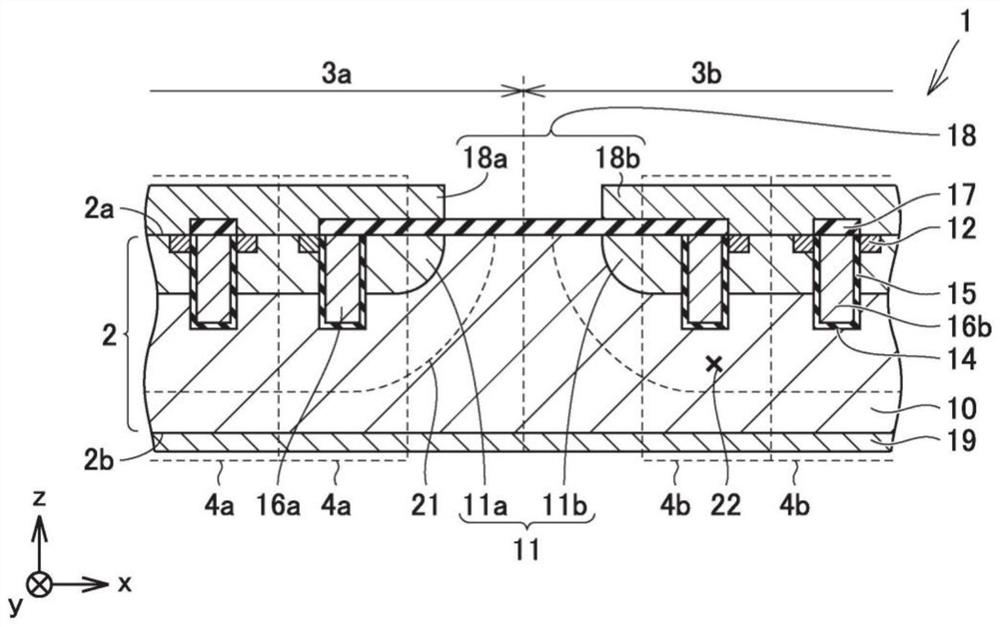

图2是实施方式1涉及的半导体装置的图1所示的剖面线II-II处的概略局部放大剖视图。

图3是表示实施方式1涉及的半导体装置的一个使用例即半导体模块的概略俯视图。

图4是表示实施方式1涉及的半导体装置的制造方法的一个工序的概略局部放大剖视图。

图5是表示实施方式1涉及的半导体装置的制造方法中的图4所示的工序的下一个工序的概略局部放大剖视图。

图6是表示实施方式1涉及的半导体装置的制造方法中的图5所示的工序的下一个工序的概略局部放大剖视图。

图7是表示实施方式1涉及的半导体装置的制造方法中的图6所示的工序的下一个工序的概略局部放大剖视图。

图8是表示实施方式1涉及的半导体装置的制造方法中的图7所示的工序的下一个工序的概略局部放大剖视图。

图9是表示实施方式1涉及的半导体装置的制造方法中的图8所示的工序的下一个工序的概略局部放大剖视图。

图10是表示对实施方式1涉及的半导体装置的多个单元区域的每一者的特性进行测定的电路的图。

图11是实施方式2涉及的半导体装置的概略局部放大剖视图。

图12是表示实施方式2涉及的半导体装置的制造方法的一个工序的概略局部放大剖视图。

图13是实施方式3涉及的半导体装置的概略俯视图。

图14是实施方式3涉及的半导体装置的图13所示的剖面线XIV-XIV处的概略局部放大剖视图。

图15是实施方式3涉及的半导体装置的图13所示的剖面线XV-XV处的概略局部放大剖视图。

图16是实施方式3涉及的半导体装置的图13所示的剖面线XVI-XVI处的概略局部放大剖视图。

图17是实施方式4涉及的半导体装置的概略俯视图。

图18是实施方式4涉及的半导体装置的图17所示的剖面线XVIII-XVIII处的概略局部放大剖视图。

图19是实施方式5涉及的半导体装置的概略俯视图。

图20是实施方式5涉及的半导体装置的图19所示的剖面线XX-XX处的概略局部放大剖视图。

图21是实施方式5涉及的半导体装置的图19所示的剖面线XXI-XXI处的概略局部放大剖视图。

图22是实施方式5涉及的半导体装置的图19所示的剖面线XXII-XXII处的概略局部放大剖视图。

图23是实施方式5涉及的半导体装置的图19所示的剖面线XXIII-XXIII处的概略局部放大剖视图。

图24是实施方式5涉及的半导体装置的图19所示的剖面线XXIV-XXIV处的概略局部放大剖视图。

图25是实施方式5涉及的半导体装置的图19所示的剖面线XXV-XXV处的概略局部放大剖视图。

图26是实施方式6涉及的半导体装置的概略俯视图。

图27是实施方式6涉及的半导体装置的图26所示的剖面线XXVII-XXVII处的概略局部放大剖视图。

具体实施方式

下面,对本发明的实施方式进行说明。此外,对相同的结构标注相同的标号,不重复其说明。

实施方式1.

参照图1及图2,对本实施方式的半导体装置1进行说明。半导体装置1例如是功率半导体装置。半导体装置1主要具有半导体衬底2、表面侧电极18、背面侧电极19。

半导体衬底2具有表面2a、与表面2a相反侧的背面2b。半导体衬底2例如是硅衬底或碳化硅衬底。如图1所示,在半导体衬底2的表面2a的俯视观察中,半导体衬底2包含元件区域3、包围元件区域3的外周区域4。

元件区域3包含多个单元区域。具体而言,元件区域3包含第一单元区域3a、与第一单元区域3a相邻的第二单元区域3b。元件区域3也可以进一步包含与第二单元区域3b相邻的第三单元区域3c。如图1所示,在半导体衬底2的表面2a的俯视观察中,第一单元区域3a、第二单元区域3b及第三单元区域3c排列于第一方向(x方向)。第三单元区域3c形成为相对于第二单元区域3b与第一单元区域3a线对称。第三单元区域3c具有与第一单元区域3a相同的结构。因此,以下主要详细地对第一单元区域3a及第二单元区域3b的构造进行说明。

如图2所示,在第一单元区域3a形成有第一半导体元件4a。在第二单元区域3b形成有第二半导体元件4b。在第三单元区域3c形成有至少一个第三半导体元件4c(参照图10)。第一半导体元件4a、第二半导体元件4b及第三半导体元件4c例如为功率半导体元件。第一半导体元件4a、第二半导体元件4b及第三半导体元件4c例如是沟槽栅极构造的晶体管。特定地,第一半导体元件4a、第二半导体元件4b及第三半导体元件4c例如是沟槽栅极构造的金属氧化膜半导体场效应晶体管(MOSFET)。第一半导体元件4a、第二半导体元件4b及第三半导体元件4c例如也可以是沟槽栅极构造的绝缘栅型双极晶体管(IGBT)。

表面侧电极18设置于半导体衬底2的表面2a之上。表面侧电极18例如由AlSi这样的导电材料形成。表面侧电极18包含形成于第一单元区域3a的第一电极18a、形成于第二单元区域3b的第二电极18b。第一电极18a和第二电极18b在第一单元区域3a和第二单元区域3b之间的边界处彼此分离。

背面侧电极19设置于半导体衬底2的背面2b之上。背面侧电极19例如由Ni这样的导电材料形成。背面侧电极19横跨多个单元区域(例如,第一单元区域3a及第二单元区域3b)而连续地形成。背面侧电极19在多个单元区域间没有被分割。

如图2所示,半导体衬底2包含n

第二半导体元件4b包含第二电极18b、n

n

第一p区域11a形成于第一单元区域3a。第二p区域11b形成于第二单元区域3b。第一p区域11a及第二p区域11b相对于n

n

栅极绝缘膜15至少设置于n

第一栅极电极16a隔着栅极绝缘膜15与p基极区域11(第一p区域11a)的该部分相对。第二栅极电极16b隔着栅极绝缘膜15与p基极区域11(第二p区域11b)的该部分相对。第一栅极电极16a及第二栅极电极16b例如沿与第一方向(x方向)垂直的第二方向(y方向)延伸。在第一半导体元件4a及第二半导体元件4b为沟槽栅极构造的晶体管的情况下,第一栅极电极16a及第二栅极电极16b为设置于沟槽14内的沟槽栅极电极。

第一半导体元件4a包含第一电极18a。在第一半导体元件4a为沟槽栅极构造的晶体管的情况下,第一电极18a作为第一源极电极起作用。第一电极18a与第一半导体元件4a的n

第一电极18a及第二电极18b通过层间绝缘膜17与第一栅极电极16a及第二栅极电极16b电绝缘。层间绝缘膜17将第一栅极电极16a、第二栅极电极16b及栅极绝缘膜15覆盖。层间绝缘膜17例如为SiO

在第一半导体元件4a及第二半导体元件4b为沟槽栅极构造的晶体管的情况下,背面侧电极19作为漏极电极起作用。背面侧电极19例如也可以与n

如图1所示,栅极配线7及栅极焊盘9设置于半导体衬底2的表面2a之上。栅极配线7沿半导体衬底2的元件区域3与外周区域4的边界延伸。栅极配线7例如由AlSi这样的导电材料形成。栅极配线7与第一半导体元件4a的第一栅极电极16a及第二半导体元件4b的第二栅极电极16b导通。栅极配线7与栅极焊盘9连接。导线(未图示)与栅极焊盘9键合。

在外周区域4,例如,也可以形成电场限制环构造(未图示)。电场限制环构造使半导体装置1的耐压提高。

参照图3,对本实施方式的半导体装置1的一个使用例即半导体模块24进行说明。半导体模块24例如可以是功率半导体模块。半导体模块24具有半导体装置1、金属框架25、导线26。使用导线26将半导体装置1的第一单元区域3a、第二单元区域3b及第三单元区域3c与金属框架25连接。第一单元区域3a、第二单元区域3b及第三单元区域3c均一地进行动作。

参照图1及图4至图9,对半导体装置1的制造方法的一个例子进行说明。

如图4所示,从n

如图8所示,在沟槽14内的栅极绝缘膜15之上形成第一栅极电极16a及第二栅极电极16b。例如,在栅极绝缘膜15及半导体衬底2的表面2a之上形成栅极电极膜(未图示)。对半导体衬底2的表面2a之上的栅极电极膜进行蚀刻。这样,在沟槽14内形成第一栅极电极16a及第二栅极电极16b。如图9所示,在半导体衬底2的表面2a的一部分、第一栅极电极16a及第二栅极电极16b之上形成层间绝缘膜17。在半导体衬底2的表面2a之上形成表面侧电极18(第一电极18a及第二电极18b)。第一电极18a和第二电极18b在第一单元区域3a和第二单元区域3b之间的边界处彼此分离。在半导体衬底2的背面2b之上形成背面侧电极19。这样,得到图1所示的半导体装置1。

参照图1及图10,对半导体装置1的作用进行说明。

就半导体装置1而言,假设仅多个单元区域中的一个(例如,第二单元区域3b)包含缺陷22,在多个单元区域的剩余区域(例如,第一单元区域3a、第三单元区域3c)没有缺陷22。使用图10所示的电路,对半导体装置1的多个单元区域(例如,第一单元区域3a、第二单元区域3b、第三单元区域3c)的每一者的特性进行测定。例如,将表面侧电极18、背面侧电极19与电源27连接,在表面侧电极18和背面侧电极19之间施加电压。仅在多个单元区域中的一个(例如,第二单元区域3b(第二半导体元件4b的第二电极18b))连接电流计28,对在多个单元区域中的一个(例如,第二单元区域3b)产生的漏电流进行测定。这样,对多个单元区域中的一个的特性进行测定。

如果在表面侧电极18和背面侧电极19之间施加电压,则在由n

就半导体装置1而言,在多个单元区域(例如,第一单元区域3a、第二单元区域3b及第三单元区域3c)之间,p基极区域11(例如,第一p区域11a及第二p区域11b)是分离的。因此,能够对从彼此相邻的单元区域扩展的耗尽区域21的重叠进行抑制。另外,在多个单元区域之间,表面侧电极18(例如,第一电极18a、第二电极18b及第三电极18c)是分离的。因此,对在多个单元区域中的一个(例如,第二单元区域3b)产生的漏电流流入多个单元区域的剩余区域(例如,第一单元区域3a、第三单元区域3c)进行抑制。由与多个单元区域中的一个(第二单元区域3b(第二半导体元件4b的第二电极18b))连接的电流计28测定的漏电流增加。就半导体装置1而言,能够高精度地对多个单元区域的每一者的特性进行测定。

对本实施方式的半导体装置1的效果进行说明。

本实施方式的半导体装置1具有半导体衬底2、表面侧电极18、背面侧电极19。半导体衬底2具有表面2a、背面2b。表面侧电极18设置于半导体衬底2的表面2a之上。背面侧电极19设置于半导体衬底2的背面2b之上。半导体衬底2包含第一单元区域3a、与第一单元区域3a相邻的第二单元区域3b。在第一单元区域3a形成有第一半导体元件4a。在第二单元区域3b形成有第二半导体元件4b。表面侧电极18包含形成于第一单元区域3a的第一电极18a、形成于第二单元区域3b的第二电极18b。第一半导体元件4a包含第一电极18a、形成于第一单元区域3a的表面2a侧的第一p区域11a。第二半导体元件4b包含第二电极18b、形成于第二单元区域3b的表面2a侧的第二p区域11b。第一电极18a和第二电极18b彼此分离。第一半导体元件4a的第一p区域11a和第二半导体元件4b的第二p区域11b彼此分离。

因此,对在多个单元区域中的一个(例如,第二单元区域3b)产生的漏电流流入多个单元区域中的剩余区域(例如,第一单元区域3a)进行抑制。就半导体装置1而言,能够高精度地对多个单元区域的每一者的特性进行测定。

实施方式2.

参照图11,对实施方式2的半导体装置1b进行说明。本实施方式的半导体装置1b具有与实施方式1的半导体装置1相同的结构,但主要在以下方面不同。

半导体衬底2还包含n

n

对半导体装置1b的作用进行说明。

如果为了对半导体装置1b的特性进行测定而在表面侧电极18和背面侧电极19之间施加电压,则耗尽区域21从彼此相邻的单元区域(例如,第一单元区域3a及第二单元区域3b)扩展。如果从相邻的单元区域(例如,第一单元区域3a及第二单元区域3b)扩展的耗尽区域21彼此重叠,则在多个单元区域中的一个(例如,第二单元区域3b)产生的漏电流会流入多个单元区域的剩余区域(例如,第一单元区域3a)。

n

参照图12,对实施方式2的半导体装置1b的制造方法的一个例子进行说明。本实施方式的半导体装置1b的制造方法具有与实施方式1的半导体装置1的制造方法相同的工序,但主要在以下方面不同。在本实施方式的半导体装置1b的制造方法中,在形成n

本实施方式的半导体装置1b除了实施方式1的半导体装置1的效果之外,还取得如下效果。

就本实施方式的半导体装置1b而言,半导体衬底2还包含n

n

实施方式3.

参照图13至图16,对实施方式3的半导体装置1c进行说明。本实施方式的半导体装置1c具有与实施方式1的半导体装置1相同的结构,但主要在以下方面不同。

第一栅极电极16a及第二栅极电极16b例如沿第一方向(x方向)延伸。如图13及图14所示,半导体装置1c还具有栅极配线8。栅极配线8设置于半导体衬底2的表面2a之上。栅极配线8沿与第一方向(x方向)垂直的第二方向(y方向)延伸。栅极配线8与栅极配线7连接。栅极配线8经由栅极配线7与栅极焊盘9导通。栅极配线8例如由AlSi这样的导电材料形成。栅极配线8通过层间绝缘膜17与n

在半导体衬底2的表面2a的俯视观察中,栅极配线8设置于彼此相邻的单元区域(例如,第一单元区域3a及第二单元区域3b)之间的边界之上。栅极配线8沿彼此相邻的单元区域间的边界延伸。例如,栅极配线8设置于第一单元区域3a和第二单元区域3b之间的边界之上。栅极配线8沿第一单元区域3a和第二单元区域3b之间的边界延伸。栅极配线8设置于第一电极18a和第二电极18b之间。在半导体衬底2的表面2a的俯视观察中,栅极配线8也可以设置于第一半导体元件4a的第一p区域11a与第二半导体元件4b的第二p区域11b之间。

栅极配线8与多个半导体元件(例如,第一半导体元件4a及第二半导体元件4b)的多个栅极电极(例如,第一栅极电极16a及第二栅极电极16b)导通。具体而言,如图14所示,彼此相邻的半导体元件(例如,第一半导体元件4a及第二半导体元件4b)的栅极电极(例如,第一栅极电极16a及第二栅极电极16b)经由栅极连接配线8c与栅极配线8连接。栅极连接配线8c例如由AlSi这样的导电材料形成。栅极连接配线8c通过层间绝缘膜17与表面侧电极18(例如,第一电极18a及第二电极18b)、p基极区域11(例如,第一p区域11a及第二p区域11b)及n

本实施方式的半导体装置1c除了实施方式1的半导体装置1的效果之外,还取得如下效果。

本实施方式的半导体装置1c还具有与第一半导体元件4a的第一栅极电极16a和第二半导体元件4b的第二栅极电极16b导通的栅极配线8。在半导体衬底2的表面2a的俯视观察中,栅极配线8设置于第一单元区域3a和第二单元区域3b之间的边界之上。

第一单元区域3a和第二单元区域3b之间的边界为半导体衬底2的无效区域。栅极配线8配置于半导体衬底2的无效区域。因此,能够增加半导体装置1c所包含的多个单元区域的面积及数量中的至少一个。能够增加半导体装置1c的多个单元区域的每一者所包含的半导体元件的数量。能够使半导体装置1c的性能提高。

实施方式4.

参照图17及图18,对实施方式4的半导体装置1d进行说明。本实施方式的半导体装置1d具有与实施方式1的半导体装置1相同的结构,取得相同的效果,但主要在以下方面不同。

就半导体装置1d而言,第一半导体元件4a、第二半导体元件4b及第三半导体元件4c(未图示)为平面栅极构造的晶体管。具体而言,栅极绝缘膜15设置于半导体衬底2的表面2a之上。栅极电极16隔着栅极绝缘膜15设置于半导体衬底2的表面2a之上,为平面栅极电极。第一半导体元件4a、第二半导体元件4b及第三半导体元件4c例如为平面栅极型的MOSFET。第一半导体元件4a、第二半导体元件4b及第三半导体元件4c也可以是平面栅极型的IGBT。

在本实施方式的变形例中,半导体装置1d也可以如实施方式2那样,还包含n

实施方式5.

参照图19至图25,对实施方式5的半导体装置1e进行说明。本实施方式的半导体装置1e具有与实施方式3的半导体装置1c相同的结构,但主要在以下方面不同。

与实施方式4的半导体装置1d相同地,就半导体装置1e而言,第一半导体元件4a、第二半导体元件4b及第三半导体元件4c(未图示)为平面栅极构造的晶体管。本实施方式的半导体装置1e取得实施方式3及实施方式4的效果。

实施方式6.

参照图26及图27,对实施方式6的半导体装置1f进行说明。本实施方式的半导体装置1f具有与实施方式4的半导体装置1d相同的结构,取得相同的效果,但主要在以下方面不同。

就半导体装置1f而言,第一半导体元件4a、第二半导体元件4b及第三半导体元件4c(未图示)为二极管。半导体装置1f不包含栅极电极(例如,第一栅极电极16a及第二栅极电极16b)、栅极绝缘膜15、n

具体而言,半导体衬底2包含n

n区域33相对于n

在本实施方式的变化例中,半导体装置1f也可以如实施方式2那样还包含n

应当认为本次公开的实施方式1-6在所有方面均为例示而不是限制性的。只要不矛盾,也可以组合本次公开的实施方式1-6中的至少两个。本发明的范围不是由上述说明表示,而是由权利要求书表示,旨在包含与权利要求书均等的含义及范围内的所有的变更。

虽然对本发明的实施方式进行了说明,但是应当认为本次公开的实施方式在所有方面均是例示而不是限制性的。本发明的范围由权利要求书表示,旨在包含与权利要求书均等的含义及范围内的所有的变更。