半导体元件及其制造方法

文献发布时间:2023-06-19 09:41:38

技术领域

本发明涉及半导体技术领域,特别是涉及一种半导体元件及其制造方法。

背景技术

半导体存储元件可分为挥发性存储元件(volatile memory devices)与非挥发性存储元件两类。相较于挥发性存储元件,非挥发性存储由于在保留数据时不需要电力,故广泛用于程序编码、嵌入系统、固态硬盘(solid state devices;SSD)、物联网(loT;internetof things)、人工智能(AI)与云端储存。

闪存(Flash)是非挥发性存储元件的一种,而闪存的NOR Flash具有重量轻、尺寸小、高容量与低功耗的优点,故广泛应用于各种个人计算机、消费型电子产品与网络通信产品,例如笔记本电脑、数字电视与行动通信装置。然而,NOR Flash读取的速度快,但其写入速度较慢。因此,NOR Flash的效能与密度仍待改善。

发明内容

本发明提供一种用于提升密度与提升效能的半导体元件及其制造方法。

依据本发明的一实施方式中,半导体元件的制造方法包括以下步骤。形成叠层,叠层包括第一多晶硅层、氮化硅层与第二多晶硅层。形成第一沟槽穿透叠层,其中第一沟槽具有蜿蜒状形状(在俯视图中可见)。填入第一隔离层于第一沟槽中。形成第二沟槽穿透叠层,以暴露第一多晶硅层、氮化硅层与第二多晶硅层的多个侧壁。移除氮化硅层,以形成第一凹陷,第一凹陷位于第一多晶硅层与第二多晶硅层之间。掺杂暴露的第一多晶硅层与第二多晶硅层的侧壁,以定义源极端点接触与漏极端点接触。形成第三多晶硅层于第一多晶硅层与第二多晶硅层上,以及位于第一多晶硅层与第二多晶硅层的第一凹陷中,使得第三多晶硅层具有凹部部分,凹部部分位于第一多晶硅层与第二多晶硅层之间。掺杂凹部部分,以定义源极区域与漏极区域。掺杂凹部部分的内侧,以形成井区,井区视为基极区域(bulk),其中基极区域面向第一沟槽。掺杂凹部部分,以定义通道区域,其中凹部部分定义为存储元件的本体。形成栅极介电层于第三多晶硅层上。形成栅极导电层于栅极介电层上,其中栅极导电层定义为字线,位于第一凹陷内的栅极导电层视为栅极。栅极面向第二沟槽。形成第二隔离层于栅极导电层与第三多晶硅层上。

在一些实施方式中,半导体的制造方法还包括以下步骤。形成第三隔离层于第一隔离层与第二隔离层上。蚀刻第三隔离层以形成第一通孔孔洞。填入导电材料于第一通孔孔洞中,以形成第一通孔接触,且第一通孔接触设置于漏极端点接触上。形成第四隔离层于该第三隔离层上。蚀刻第四隔离层,以形成第二凹陷。填入导电材料于第二凹陷中,以形成内连接导电垫,且内连接导电垫位于第四隔离层中。形成第五隔离层于第四隔离层与内连接导电垫上。蚀刻第五隔离层以形成第二通孔孔洞。填入导电材料于第二通孔孔洞中,以形成第二通孔接触。

在一些实施方式中,半导体的制造方法还包括形成漏极导电层,于第五隔离层与该第二通孔接触上,其中该漏极导电层定义为位线。

在一些实施方式中,第二隔离层平行于第一隔离层。

在一些实施方式中,第三多晶硅层还具有连接于凹部部分的第一部分与第二部分。第一部分与第二部分分别位于第一多晶硅层与第二多晶硅层上。

在一些实施方式中,内连接导电垫连接第一通孔接触与第二通孔接触。

在一些实施方式中,第一通孔接触对齐于漏极端点接触。

依据本发明的另一实施方式,半导体元件包括基板、第一多晶硅层、第二多晶硅层、第三多晶硅层、第一隔离层、栅极介电层、栅极导电层、第二隔离层、第三隔离层与第一通孔接触。第一多晶硅层与第二多晶硅层位于基板上。第三多晶硅层位于第一多晶硅层与第二多晶硅层之间。第三多晶硅层具有凹部部分,凹部部分定义为存储元件的本体。本体包括源极区域、漏极区域、通道区域与基极区域。第一隔离层邻接于第一多晶硅层、第二多晶硅层与第三多晶硅层。栅极介电层与栅极导电层嵌设于第三多晶硅层内。面相凹部部分的栅极导电层视为栅极。第二隔离层位于栅极导电层与第三多晶硅层上。基极区域与栅极分别面向第一隔离层与第二隔离层。

在一些实施方式中,半导体元件还包括第三隔离层、第一通孔接触、第四隔离层、内连接导电垫、第五隔离层与第二通孔接触。第三隔离层位于第一隔离层与第二隔离层上。第一通孔接触位于第三隔离层中。第四隔离层位于第三隔离层上。内连接导电垫位于第四隔离层中。第五隔离层位于第四隔离层上。第二通孔接触位于第五隔离层中。

在一些实施方式中,内连接导电垫与第一通孔接触及第二通孔接触相接触。

在一些实施方式中,第一通孔接触的材料与第二通孔接触的材料相同。

在一些实施方式中,第一通孔接触、内连接导电垫与栅极导电层定义为一组NOR闪存单元,且NOR闪存单元包括两个NOR闪存晶胞,且NOR闪存晶胞的每一个所定义的面密度低于每单位特征尺寸平方的六倍。

在一些实施方式中,半导体元件还包括漏极导电层,位于第五隔离层与第二通孔接触上,且漏极导电层定义为位线。

在一些实施方式中,第一隔离层具有蜿蜒状形状(在俯视图中可见),且存储元件的本体于第一隔离层上呈交错排列。

在一些实施方式中,第二隔离层具有直条形形状(在俯视图中可见)。

在一些实施方式中,半导体元件还包括第四多晶硅层,位于基板上,定义为共同接地线。

在一些实施方式中,第三多晶硅层覆盖第一多晶硅层与第二多晶硅层,且第三多晶硅层的凹部部分具有半椭圆轮廓(在俯视图中可见)。

在一些实施方式中,第三多晶硅层的边缘对齐于栅极导电层的边缘。

在一些实施方式中,第一通孔接触在基板的垂直投影与第二通孔接触在基板的垂直投影不完全重叠。

综上所述,本发明提供一种半导体元件及其制造方法。通过上述的半导体元件的制造方法,可增加半导体元件的密度,进而提升半导体元件的效能。

应当了解前面的一般描述和以下的详细描述都是示例,并且旨在提供对本发明的进一步解释。

附图说明

本发明的内容可从以下实施方式的详细说明及随附的图式理解。

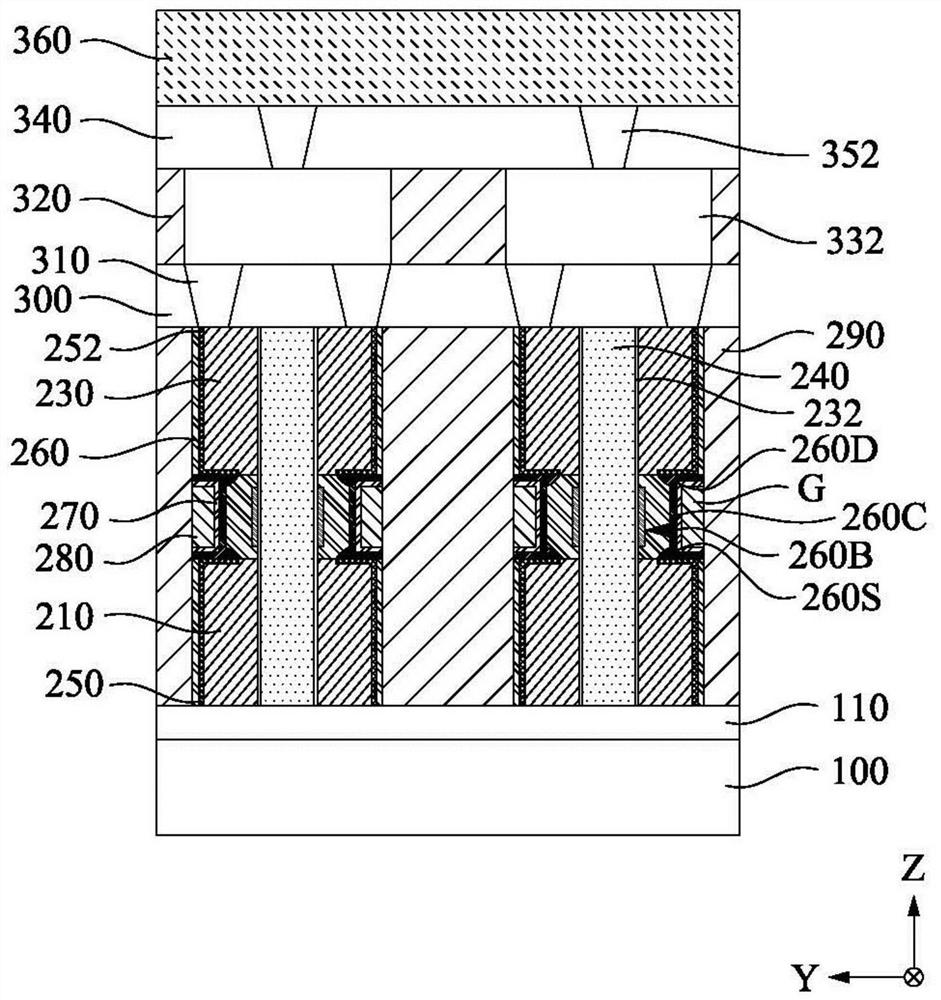

图1、图2、图3A、图4A、图5A、图6、图7、图8A、图9、图10A、图11A、图12A、图13A、图14、图15、图16、图17A、图18A与图21A是根据本发明的一实施方式在各个阶段形成半导体元件的方法的示意图。

图3B、图4B与图5B是根据本发明的一实施方式沿着图3A、图4A与图5A的氮化硅层的水平位置的半导体元件的俯视图。

图8B、图10B、图11B与图12B是根据本发明的一实施方式沿着图8A、图10A、图11A与图12A移除氮化硅层的水平位置的半导体元件的俯视图。

图11C绘示图11B中的晶体管元件的存储单元的示意图。

图13B是根据本发明的一实施方式沿着图13A的第一通孔接触的水平位置的半导体元件的俯视图。

图17B为沿着图17A的内连接导电垫的水平位置的半导体元件的俯视图。

图18B为沿着图18A的第二通孔接触的水平位置的半导体元件的俯视图。

图19绘示根据本发明一些实施方式沿图18B的1-1线所绘示的剖面图。

图20绘示根据本发明一些实施方式沿图18B的2-2线所绘示的剖面图。

图21B为沿着图21A的漏极导电层的水平位置的半导体元件的俯视图。

图22是根据本发明的一实施方式的NOR闪存单元数组的电路图。

【符号说明】

100:基板

110:第一多晶硅层

200:叠层

202:侧壁

204:侧壁

210:第二多晶硅层

214:侧

220:氮化硅层

230:第三多晶硅层

232:衬垫层

234:侧

240:第一隔离层

250:源极端点接触

252:漏极端点接触

260:第四多晶硅层

260B:基极区域

260C:通道区域

260D:漏极区域

260S:源极区域

262:凹部部分

264:第一部分

266:第二部分

270:栅极介电层

280:栅极导电层

290:第二隔离层

300:第三隔离层

310:第一通孔接触

320:第四隔离层

330:导电材料

332:内连接导电垫

340:第五隔离层

352:第二通孔接触

360:漏极导电层

400:NOR闪存单元

BL0:第一位线

BL1:第二位线

G:栅极

T1:第一沟槽

T2:第二沟槽

R1:第一凹陷

R2:第二凹陷

WL0:第一字线

WL1:第二字线

WL2:第三字线

WL3:第四字线

具体实施方式

以下揭露内容提供用于实施本发明的不同特征的诸多不同实施方式或示例。下文描述元件及排列的某些实施方式或示例以简化本发明。当然,此等仅是示例性且并非意欲为限制性。举例而言,部件的尺寸不限于所揭示范围或值,而是可取决于元件的制程条件及/或所期望性质。此外,随后的描述中在第二特征上方或在第二特征上形成第一特征可包含其中第一特征及第二特征直接接触形成的实施方式且也可包含其中可插入第一特征及第二特征中间以形成额外特征以使得第一特征及第二特征可不直接接触的实施方式。为简单与清晰起见,各特征可按不同比例而任意绘制。

进一步而言,为了便于描述,本文可使用诸如「下面」、「下方」、「下部」、「上方」、「上部」及类似者等空间相对性术语来描述如图中所图标的一个元件或特征与另一元件(或多个元件)或特征(或多个特征)的关系。除了图中所描绘的定向外,空间相对性术语意欲囊括使用或操作中的元件的不同定向。设备可经其他方式定向(旋转90度或处于其他定向)且因此可同样解读本文所使用的空间相对性描述词。

图1、图2、图3A、图4A、图5A、图6、图7、图8A、图9、图10A、图11A、图12A、图13A、图14、图15、图16、图17A、图18A与图21A是根据本发明的一实施方式在各个阶段形成半导体元件的方法的示意图。

参阅图1及图2。第一多晶硅层110形成在基板100之上,且叠层200形成在基板100与第一多晶硅层110之上。第一多晶硅层110定义为共同接地线(common ground line)。在一些实施方式中,叠层200包含第二多晶硅层210、氮化硅层220与第三多晶硅层230。换句话说,第二多晶硅层210、氮化硅层220与第三多晶硅层230堆叠排列于基板100之上,且最靠近基板100的第二多晶硅层210直接接触于第一多晶硅层110。

在一些实施方式中,基板100可以是硅基板。在一些其他的实施方式中,基板100可包括其他半导体元素,例如:锗(germauium),或包括半导体化合物,例如:碳化硅(siliconcarbide)、砷化镓(gallium arsenic)、磷化镓(gallium phosphide)、磷化铟(indiumphosphide)、砷化铟(indium arsenic)、及/或锑化铟(indium antimonide),或其他半导体合金,例如:硅锗(SiGe)、磷化砷镓(GaAsP)、砷化铟铝(AlInAs)、砷化镓铝(AlGaAs)、砷化铟镓(GaInAs)、磷化铟镓(GaInP)、及/或磷砷化铟镓(GaInAsP),以及以上之任意组合。在一些其他的实施方式中,基板100包括绝缘层覆硅(semiconductor-on-insulator;SOI)基板,例如具有埋层(buried layer)。

参阅图3A与图3B,其中图3B为沿着图3A的氮化硅层220的水平位置的半导体元件的俯视图。在形成叠层200之后,蚀刻叠层200的一部分,以形成第一沟槽T1穿透于叠层200。详细来说,叠层200上可借由适当的沉积、显影及/或蚀刻技术形成图案化的硬屏蔽层,并使用图案化的硬屏蔽层作为蚀刻屏蔽,以蚀刻叠层200。蚀刻叠层200终止于第一多晶硅层110。也就是说,形成第一沟槽T1,使得叠层200的侧壁202被暴露,且第一沟槽T1暴露下面的第一多晶硅层110。在一些实施方式中,第一沟槽T1在图3B的俯视图中呈现平行排列的蜿蜒状(serpentine shape)。详细来说,第一沟槽T1在图3B的俯视图中具有S形的轮廓。

在一些实施方式中,可以使用端点侦测(end point detection)的技术来确定蚀刻叠层200的停止位置。蚀刻制程可以使用干式或湿式蚀刻。当使用干式蚀刻时,制程的气体可包括四氟化碳(CF

在一些实施方式中,在图3B的第一沟槽T1与另一相邻的第一沟槽T1呈反对称(antisymmetrically)排列。详细来说,如图3B所示,第一沟槽T1的其中一个(例如左侧的第一沟槽T1)具有反S形(inverse S-shaped)的轮廓,且另一相邻的第一沟槽T1(例如右侧的第一沟槽T1)具有S形的轮廓。在其他的实施方式中,第一沟槽T1的其中一个可具有S形的轮廓,且另一个相邻的第一沟槽T1可具有反S形的轮廓。在一些实施方式中,第一沟槽T1的其中一个与另一相邻的第一沟槽T1呈对称(symmetrically)排列。举例来说,第一沟槽T1的其中一个可具有S形的轮廓,且另一相邻的第一沟槽T1可具有S形的轮廓。在其他的实施方式中,第一沟槽T1的其中一个可具有反S形的轮廓,且另一相邻的第一沟槽T1可具有反S形的轮廓。

参阅图4A与图4B,其中图4B为沿着图4A的氮化硅层220的水平位置的半导体元件的俯视图。衬垫层232形成在叠层200的暴露侧壁202(见图3A)上。衬垫层232可包括例如氮化硅或其他适当的绝缘材料。在形成衬垫层232之后,填入第一隔离层240于第一沟槽T1(见图3A)中。在一些实施方式中,在填入第一隔离层240之后,可进行平坦化制程,如化学机械研磨制程(CMP)来移除第一隔离层240与衬垫层232的多余材料。在一些实施方式中,第一隔离层240包括氧化硅层、氮化硅层或氮氧化硅层等等。第一隔离层240的材料可以是低介电(low-k)材料,例如是四乙氧基硅烷(tetraethoxysilane;TEOS)。第一隔离层240可借由化学气相沉积(CVD)、电浆增强化学气相沉积(PECVD)、原子层沉积(ALD)、可流动式化学气相沉积(FCVD)或低压化学气相沉积(LPCVD)来形成。

参阅图5A与图5B,其中图5B为沿着图5A的氮化硅层220的水平位置的半导体元件的俯视图。进行另一蚀刻制程,形成第二沟槽T2穿透叠层200,以暴露第二多晶硅层210、氮化硅层220与第三多晶硅层230的多个侧壁204。详细来说,第二沟槽T2穿透第二多晶硅层210、氮化硅层220与第三多晶硅层230。在一些实施方式中,如图5B所示,第二沟槽T2呈直条形的形状排列。

在一些实施方式中,蚀刻叠层200终止于第一多晶硅层110。也就是说,第二沟槽T2暴露下面的第一多晶硅层110。在一些实施方式中,可以使用端点侦测的技术来确定蚀刻叠层200的停止位置。蚀刻制程可以使用干式或湿式蚀刻。当使用干式蚀刻时,制程的气体可包括四氟化碳(CF

参阅图6。图5A的氮化硅层220被移除,以形成第一凹陷R1,且第一凹陷R1位于第二多晶硅层210与第三多晶硅层230之间。详细来说,由于形成第一凹陷R1,使得衬垫层232的一部分被暴露。也就是说,衬垫层232的一部分被第一凹陷R1暴露,而衬垫层232的其余部分分别被第二多晶硅层210与第三多晶硅层230所覆盖。在一些实施方式中,第一凹陷R1连通于第二沟槽T2。在一些实施方式中,在形成第一凹陷R1之后,第二多晶硅层210的一侧214与第三多晶硅层230的一侧234被暴露。

参阅图7。在形成第一凹陷R1之后,掺杂暴露的侧壁204(见图5A),以定义源极端点接触250与漏极端点接触252。详细来说,在暴露的侧壁204(见图5A)进行离子布植(ionimplantation)制程之后,进行退火制程以激活布植的掺杂剂。在一些实施方式中,掺杂暴露的侧壁204(见图5A)还包括掺杂第二多晶硅层210位于第一凹陷R1的一侧214(见图6)与第三多晶硅层230位于第一凹陷R1的一侧234(见图6)。进一步来说,第二多晶硅层210的一侧214(见图6)的一部分被掺杂,而第二多晶硅层210的一侧214(见图6)的其余部分未被掺杂。同样地,第三多晶硅层230的一侧234(见图6)的一部分被掺杂,而第三多晶硅层230的一侧234(见图6)的其余部分未被掺杂。在一些实施方式中,掺杂源极端点接触250与漏极端点接触252的掺杂剂可以包括P型掺杂剂或N型掺杂剂。举例而言,P型掺杂剂可以是硼(B)、二氟化硼(BF

参阅图8A与图8B,其中图8B为沿着图8A移除氮化硅层220(见图5A)的水平位置的半导体元件的俯视图。在本实施方式中,进行凹陷处晶胞整合(recessed cellintegration;RCI)制程。也就是说,在形成图7的第一凹陷R1之后,在第一凹陷R1中填入第四多晶硅层260。详细来说,第四多晶硅层260形成于第二多晶硅层210与第三多晶硅层230上,以及位于第二多晶硅层210与第三多晶硅层230的第一凹陷R1(见图7)中,使得第四多晶硅层260具有凹部部分262。凹部部分262位于第二多晶硅层210与第三多晶硅层230之间。

在填入第四多晶硅层260之后,掺杂凹部部分262,以形成源极区域260S与漏极区域260D。详细来说,借由以特定角度控制离子布植的掺杂剂,在第四多晶硅层260中形成源极区域260S与漏极区域260D,并进行退火制程以激活布植的掺杂剂。在一些实施方式中,掺杂源极区域260S与漏极区域260D的掺杂剂可以包括P型掺杂剂或N型掺杂剂。举例而言,P型掺杂剂可以是硼(B)、二氟化硼(BF

在一些实施方式中,第四多晶硅层260覆盖第二多晶硅层210与第三多晶硅层230。在一些实施方式中,第四多晶硅层260还具有连接凹部部分262的第一部分264与第二部分266。第一部分264位于第二多晶硅层210上,第二部分266位于第三多晶硅层230上,且凹部部分262位于衬垫层232的暴露部分上。换句话说,第四多晶硅层260的第一部分264与第二部分266凸出于凹部部分262。在一些实施方式中,第一部分264与第二部分266分别接触源极端点接触250与漏极端点接触252。

参阅图9。在掺杂凹部部分262以定义源极区域260S与漏极区域260D之后,掺杂凹部部分的内侧,以形成井区(well region)260W。井区260W是基极区域(bulk)260B的一部分。而后,掺杂凹部部分262,以定义通道区域260C,并利用掺杂浓度以及掺杂范围调整临界电压。详细来说,借由以特定角度控制离子布植的掺杂剂,并在对第四多晶硅层260的凹部部分262进行离子布植制程(例如进行低浓度离子布值制程)之后,进行退火制程以激活布植的掺杂剂,以形成通道区域260C。通道区域260C位于源极区域260S与漏极区域260D之间。在一些实施方式中,掺杂凹部部分262的掺杂剂可以包括P型掺杂剂或N型掺杂剂。举例而言,P型掺杂剂可以是硼(B)、二氟化硼(BF

在一些实施方式中,在布植制程之后进行的退火制程是在约700度摄氏至约1500摄氏度范围内的温度下执行的快速热退火(rapid thermal annealing;RTA)制程,持续约5秒至约250秒的范围之间。在其他的实施方式中,传统的炉管退火(conventional furnaceannealing;CFA)制程可以在约900摄氏度至约1500摄氏度范围内的温度下执行,持续约30分钟至约6小时的范围之间。

参阅图10A与图10B,其中图10B为沿着图10A移除氮化硅层220(见图5A)的水平位置的半导体元件的俯视图。形成栅极介电层270于第四多晶硅层260上。具体来说,栅极介电层270形成在第四多晶硅层260的侧壁上。在形成栅极介电层270之后,形成栅极导电层280于栅极介电层270上,且栅极导电层280定义为字线。详细来说,栅极介电层270共形地(conformally)形成于第四多晶硅层260的侧壁上,且栅极导电层280形成于栅极介电层270上。

在一些实施方式中,如图10A所示,栅极介电层270位于栅极导电层280与第四多晶硅层260之间。

在一些实施方式中,如图10B所示,第四多晶硅层260的凹部部分具有半椭圆轮廓。在一些实施方式中,第四多晶硅层260与栅极介电层270在移除氮化硅层220(见图5B)的位置在俯视图中具有半椭圆形的轮廓,因此,当填入栅极导电层280之后,栅极导电层280作为存储元件的栅极电极的部分会是对应的形状,例如是半椭圆柱形。换句话说,栅极导电层280的前述部分(即前述的栅极电极)与第四多晶硅层260的凹部部分262在俯视图中具有半椭圆形的轮廓。然而,本发明不限于此,栅极导电层280的前述部分(即前述的栅极电极)与第四多晶硅层260的凹部部分262从俯视图观之,也可为长方形、正方形、三角形、梯形、半圆形等形状。在一些实施方式中,如图10B所示,存储元件的本体(凹部部分262)呈反对称排列。换句话说,存储元件的本体(凹部部分262)在俯视图的分布形成交错的排列。具体来说,存储元件的本体(凹部部分262)交错排列于第一隔离层240上。

在一些实施方式中,栅极介电层270的材料可以是穿隧氧化物(tunnel oxide)、氮化硅、氧化铝(Al

参阅图11A与图11B,其中图11B为沿着图11A移除氮化硅层220(见图5A)的水平位置的半导体元件的俯视图。进行浅沟槽隔离蚀刻制程,使得一部分的第四多晶硅层260、栅极介电层270与栅极导电层280被移除。详细来说,可借由适当的沉积、显影及/或蚀刻技术形成图案化的硬屏蔽层,并使用图案化的硬屏蔽层作为蚀刻屏蔽,来蚀刻第四多晶硅层260、栅极介电层270与栅极导电层280,以形成第三沟槽T3。在一些实施方式中,如图11B所示,第三沟槽在俯视图中具有直条形形状。在一些实施方式中,栅极介电层270与栅极导电层280嵌设于第四多晶硅层260中。也就是说,栅极介电层270与栅极导电层280位于第四多晶硅层260的凹部部分262上。在一些实施方式中,栅极导电层280可作为字线,且栅极导电层280面对凹部部分262(第一凹陷R1)的位置可视为栅极G。基极区域260B面向第一隔离层240。在一些实施方式中,基极区域260B与栅极G分别面向不同的位置。详细来说,基极区域260B面向第一沟槽T1(见图3A与图3B),而栅极G面向第二沟槽T2(见图8A与图8B)。换句话说,基极区域260B面向第一沟槽T1(见图3A与图3B),而栅极G面向第三沟槽T3(见图11A与图11B)。

图11C绘示图11B中的晶体管元件的存储单元的示意图。如图11C所示,存储元件包括基极区域260B、通道区域260C、栅极介电层270以与门极G。基极区域260B朝着远离栅极G的方向渐缩。举例来说,基极区域260B朝着栅极G的方向可渐缩为一点。基极区域260B的形状可以是三角形。在一些实施方式中,基极区域260B的形状可以是半椭圆形、半圆形或梯形。

参阅图12A与图12B,其中图12B为沿着图12A移除氮化硅层220(见图5A)的水平位置的半导体元件的俯视图。在图11A与图11B的第三沟槽T3中填入绝缘材料,以形成第二隔离层290。换句话说,第二隔离层290形成于第四多晶硅层260上。详细来说,第二隔离层290覆盖第四多晶硅层260与栅极导电层280。在一些实施方式中,第二隔离层290平行于第一隔离层240。在一些实施方式中,第二隔离层290与第一隔离层240在俯视图中呈交替排列。在一些实施方式中,第二隔离层290在俯视图中具有直条形形状,与第一隔离层240在水平剖面图中具有的蜿蜒状形状不同。在一些实施方式中,基极区域260B面向第一隔离层240,而栅极G面向第二隔离层290。换句话说,基极区域260B与栅极G分别设置在栅极介电层270的两相对侧。

在一些实施方式中,第二隔离层290包括氧化硅层、氮化硅层或氮氧化硅层等等。第二隔离层290的材料可以是低介电(low-k)材料,例如是四乙氧基硅烷(tetraethoxysilane;TEOS)。第二隔离层290可借由化学气相沉积(CVD)、电浆增强化学气相沉积(PECVD)、原子层沉积(ALD)、可流动式化学气相沉积(FCVD)或低压化学气相沉积(LPCVD)来形成。可借由平坦化制程,例如化学机械研磨制程(CMP)来移除第二隔离层290的多余材料。

如图12A所示,在形成第二隔离层290之后,形成第三隔离层300于第二隔离层290与第四多晶硅层260上。换句话说,第三隔离层300形成于第一隔离层240与第二隔离层290上。在一些实施方式中,第三隔离层300垂直于第二隔离层290。也就是说,第三隔离层300垂直于第四多晶硅层260的长度方向。在一些实施方式中,第三隔离层300为金属层间介电(inter-metal dielectric;IMD)层。第三隔离层300可包括低介电材料。举例来说,低介电材料可为掺杂氧化物,例如磷硅玻璃(phosphor silicate glass;PSG)、硼磷硅玻璃(boronphosphor silicate glass;BPSG),或其他的适当材料。

参阅图13A与图13B,其中图13B为沿着图13A的第一通孔接触310的水平位置的半导体元件的俯视图。第一通孔接触310形成于第三隔离层300中,且第一通孔接触310接触于漏极端点接触252。详细来说,可利用适当的蚀刻方法来蚀刻第三隔离层300,以形成通孔孔洞。在第三隔离层300内的通孔孔洞中,填入适当的导电材料,以形成第一通孔接触310。举例来说,可借由化学气相沉积(CVD)在前述的通孔孔洞中填入钨,以形成第一通孔接触310。在一些实施方式中,第一通孔接触310对齐于漏极端点接触252。也就是说,第一通孔接触310的底表面接触于漏极端点接触252的顶表面。在一些其他的实施方式中,第一通孔接触310的底表面接触于漏极端点接触252与第三多晶硅层230的顶表面。

在一些实施方式中,在形成第一通孔接触310之后,可进行平坦化制程,如化学机械研磨制程(CMP)来移除多余材料。

在一些实施方式中,在形成第一通孔接触310之前,在通孔孔洞的内壁形成阻障层(barrier layer)。详细来说,阻障层可通过溅射沉积(sputter deposit)来形成,且阻障层的材料可例如是氮化钛(TiN)。在一些实施方式中,第一通孔接触310的材料可以是金属(例如:钨)。

参阅图14。在第三隔离层300上形成第四隔离层320。详细来说,第四隔离层320覆盖第一通孔接触310与第三隔离层300。在一些实施方式中,第四隔离层320平行于第三隔离层300,且第四隔离层320垂直于第二隔离层290。在一些实施方式中,第四隔离层320为金属层间介电层。第四隔离层320可包括低介电材料。举例来说,低介电材料可为掺杂氧化物,例如磷硅玻璃、硼磷硅玻璃,或其他的适当材料。

参阅图15。第四隔离层320被蚀刻,以形成第二凹陷R2。详细来说,第二凹陷R2被形成,以暴露第一通孔接触310。如此一来,后续在第二凹陷R2中填入导电材料时,可使导电材料接触于第一通孔接触310。

参阅图16。在图15的第二凹陷R2中,填入导电材料330。详细来说,一部分的导电材料330位于第四隔离层320中,而另一部分的导电材料330位于第四隔离层320上。也就是说,导电材料330覆盖第四隔离层320中,且一部分的导电材料330嵌设于第四隔离层320内。在一些实施方式中,平坦化第四隔离层320与导电材料330可以通过进行化学机械研磨制程(CMP),以移除多余材料。

参阅图17A与图17B,其中图17B为沿着图17A的内连接导电垫332的水平位置的半导体元件的俯视图。为了清楚说明本发明,第一通孔接触310在图17B中以虚线绘示,合先叙明。在填入导电材料330(见图16)于第二凹陷R2(见图15)之后,平坦化第四隔离层320与导电材料330(见图16),以形成内连接导电垫(interconnect conductive pad)332。详细来说,内连接导电垫332位于第四隔离层320中,且内连接导电垫332接触于第一通孔接触310。在一些实施方式中,内连接导电垫332的底表面与第一通孔接触310的顶表面共平面。

参阅图18A与图18B,其中图18B为沿着图18A的第二通孔接触352的水平位置的半导体元件的附视图。为了清楚说明本发明,第一通孔接触310与内连接导电垫332在图18B中以虚线绘示,合先叙明。

第五隔离层340形成于第四隔离层320与内连接导电垫332上。也就是说,第五隔离层340覆盖第四隔离层320与内连接导电垫332。在形成第五隔离层340之后,可利用适当的蚀刻方法来蚀刻第五隔离层340,使得第五隔离层340具有通孔孔洞。接着,在第五隔离层340内的通孔孔洞中,填入导电材料,以形成第二通孔接触352。在一些实施方式中,第五隔离层340可包括低介电材料。举例来说,低介电材料可为掺杂氧化物,例如磷硅玻璃、硼磷硅玻璃,或其他的适当材料。

在一些实施方式中,在形成第二通孔接触352之前,在通孔孔洞的内壁形成阻障层。详细来说,阻障层可通过溅射沉积来形成,且阻障层的材料可例如是氮化钛。在一些实施方式中,第二通孔接触352的材料可以是金属(例如:钨)。

在一些实施方式中,在形成第二通孔接触352之后,可进行平坦化制程,如化学机械研磨制程(CMP)来移除多余材料。

在一些实施方式中,内连接导电垫332连接第一通孔接触310与第二通孔接触352。也就是说,内连接导电垫332与第一通孔接触310以及第二通孔接触352相接触。

在一些实施方式中,第一通孔接触310在基板100的垂直投影与第二通孔接触352在基板100的垂直投影不完全重叠。也就是说,第一通孔接触310在基板100的垂直投影与第二通孔接触352在基板100的垂直投影可以是部分重叠或不重叠。

在一些实施方式中,第一通孔接触310的材料与第二通孔接触352的材料相同。举例来说,第一通孔接触310的材料与第二通孔接触352的材料可以是钨。

在一些实施方式中,第一通孔接触310、内连接导电垫332与栅极导电层280定义为一组NOR闪存单元400。NOR闪存单元400包括两个NOR闪存晶胞,且NOR闪存晶胞的每一个所定义的面密度低于每单位特征尺寸平方(F

在一些实施方式中,NOR闪存单元400与位于另一第一隔离层240上的NOR闪存单元400彼此呈非对称排列,以增加结构的密度。

在一些实施方式中,NOR闪存单元400可以并联的形式连接。详细来说,第二通孔接触352连接下面的内连接导电垫332,且内连接导电垫332连接下面并联的第一通孔接触310。随后,相邻的两个第一通孔接触310分别连接下面的漏极端点接触252,并经由存储元件的本体(图9的凹部部分262),再经由源极端点接触250连接至作为共同接地线的第一多晶硅层110。

图19绘示根据本发明一些实施方式沿图18B的1-1线所绘示的剖面图。图20绘示根据本发明一些实施方式沿图18B的2-2线所绘示的剖面图。如图19与图20所示,内连接导电垫332连接下面的第一通孔接触310,且第二通孔接触352位于内连接导电垫332的上面。

参阅图21A与图21B,其中图21B为沿着图21A的漏极导电层360的水平位置的半导体元件的俯视图。为了清楚说明本发明,第一通孔接触310、内连接导电垫332与第二通孔接触352在图21B中以虚线绘示,合先叙明。在第五隔离层340与第二通孔接触352之上,形成漏极导电层360。图21A中的漏极导电层360可被图案化而定义为图21B中的位线。为了清楚起见,与漏极导电层360相邻的第六隔离层在图21A中被省略,其中第六隔离层与漏极导电层360共平面。在一些实施方式中,在形成漏极导电层360之后,可进行平坦化制程,如化学机械研磨制程(CMP)来移除多余材料。

在一些实施方式中,在形成漏极导电层360之后,形成第七隔离层,以作为保护层。换句话说,第七隔离层覆盖漏极导电层360与前述的第六隔离层。在一些实施方式中,第七隔离层包括氧化硅层、氮化硅层或氮氧化硅层等等。在一些实施方式中,在形成第七隔离层之后,可进行平坦化制程,如化学机械研磨制程(CMP)来移除多余材料。在一些实施方式中,本发明提供的NOR闪存单元的制造方法可为多层的堆叠制程。也就是说,在前述的第七隔离层上可继续形成基板100、第一多晶硅层110与后续的制程,为简化之目的不再赘述。

参阅图22。图22是根据本发明的一实施方式的NOR闪存单元数组的电路图。第一列的NOR闪存单元的栅极连接至第一字线WL0,而第二列的NOR闪存单元的栅极连接至第二字线WL1。前述的栅极导电层280的栅极G可作为第一字线WL0与第二字线WL1。以此类推,第三列的NOR闪存单元的栅极连接至第三字线WL2,而第四列的NOR闪存单元的栅极连接至第四字线WL3。第一行的NOR闪存单元的漏极连接至第一位线BL0,而第二行的NOR闪存单元的漏极连接至第二位线BL1。前述的漏极导电层360可作为第一位线BL0与第二位线BL1。

综上所述,本发明提供一种半导体元件及其制造方法。通过上述的半导体元件的制造方法,可增加半导体元件的密度,进而提升半导体元件的效能。

虽然本发明已经将实施方式详细地揭露如上,然而其他的实施方式也是可能的,并非用以限定本发明。因此,权利要求的精神及范围不应限于本发明实施方式的描述。

本领域技术人员,在不脱离本发明的精神和范围内,当可作各种的改变或替换,因此所有的这些改变或替换都应涵盖于本发明权利要求的保护范围之内。

- 半导体元件中间体、含金属膜形成用组合物、半导体元件中间体的制造方法、半导体元件的制造方法

- III族氮化物半导体元件制造用基板的制造方法、III族氮化物半导体自支撑基板或III族氮化物半导体元件的制造方法、以及III族氮化物生长用基板