具有新颖虚设沟道结构的三维NAND存储器器件

文献发布时间:2023-06-19 10:21:15

背景技术

闪存器件已经经过了快速发展。闪存器件能够使所存储的数据保留长时间段而无需施加电压。此外,闪存器件的读取速率相对高,并且容易擦除所存储的数据并将数据重新写入闪存器件中。因此,已经在微计算机、自动控制系统等等中广泛使用闪存器件。为了增加闪存器件的比特密度并降低比特成本,已开发了三维(3D)-NAND(非AND)存储器器件。

3D-NAND存储器器件可以包括位于衬底之上的交替的字线层和绝缘层的堆叠体。该堆叠体可以包括阵列区域和阶梯区域。可以在阵列区域中形成沟道结构,并且可以在阶梯区域中形成虚设沟道结构。虚设沟道结构被配置为:当基于后栅极(gate-last)制造技术来形成字线(或栅极线)层时支撑阶梯区域,其中可以首先形成牺牲层,并且随后利用字线层来替代。近年来,随着3D-NAND的单元层超过100层,基于后栅极制造技术来形成字线层(或栅极线层)越来越具有挑战性,这是因为在形成字线层期间在阶梯区域中会发生塌陷。

发明内容

在本公开内容中,各实施例涉及一种包括螺纹配置中的虚设沟道结构的3D-NAND存储器器件并且提供了制造该3D-NAND存储器器件的方法。

在本公开内容中,提供了一种半导体器件。该半导体器件可以包括在垂直于该半导体器件的衬底的竖直方向上交替布置的字线层和绝缘层的堆叠体。该堆叠体可以包括第一阵列区域和相邻的第一阶梯区域。该半导体器件可以包括虚设沟道结构,该虚设沟道结构在竖直方向上延伸穿过堆叠体的第一阶梯区域中的字线层和绝缘层。字线层中的至少一个的位置可以比与字线层中的该至少一个相邻的绝缘层更加远离虚设沟道结构的中心轴。

在一些实施例中,每个字线层可以位于比与相应字线层相邻的绝缘层更加远离虚设沟道结构的中心轴。

该半导体器件还可以包括在衬底之上形成的隔离层,其中第一阶梯区域可以位于该隔离层中,并且虚设沟道结构可以延伸到衬底中并在竖直方向上进一步延伸穿过该隔离层。

此外,虚设沟道结构可以包括虚设层,该虚设层沿字线层和绝缘层布置并进一步延伸到衬底中。

在一些实施例中,该半导体器件可以包括第二阵列区域,其中第一阶梯区域被布置在第一阵列区域与第二阵列区域之间。

在其它实施例中,该半导体器件可以包括第二阶梯区域,其中第一阵列区域被布置在第一阶梯区域与第二阶梯区域之间。

在一些实施例中,虚设沟道结构可以具有垂直于中心轴的圆形横截面。在其它实施例中,虚设沟道结构可以具有垂直于中心轴的非圆形横截面。

在虚设沟道结构中,虚设层可以包括SiO、SiN、SiCN、SiCON、SiON或多晶硅中的至少一种。

该半导体器件还可以包括多个沟道结构、一个或多个缝隙结构、以及多个字线触点。沟道结构可以在第一阵列区域中形成,并延伸穿过字线层和绝缘层并进一步延伸到衬底中。该一个或多个缝隙结构可以在平行于衬底的水平方向上延伸并进一步延伸到衬底中。在一些实施例中,该一个或多个缝隙结构可以进一步延伸穿过第一阵列区域和第一阶梯区域以被布置在沟道结构之中。字线触点可以在竖直方向上从第一阶梯区域的字线层延伸。

在一些实施例中,该半导体器件可以包括另一虚设沟道结构,该另一虚设沟道结构在竖直方向上延伸穿过堆叠体的第一阵列区域中的字线层和绝缘层。

根据本公开内容的另一方面,提供了一种用于制造半导体器件的方法。在该方法中,可以形成初始堆叠体。该初始堆叠体可以包括在垂直于衬底的竖直方向上交替布置的牺牲层和绝缘层。该初始堆叠体可以包括第一阵列区域和相邻的第一阶梯区域。随后可以形成虚设沟道孔。虚设沟道孔可以在竖直方向上延伸穿过第一阶梯区域中的牺牲层和绝缘层并进一步延伸到衬底中。可以执行蚀刻工艺以使牺牲层的各部分从虚设沟道孔的中心轴凹进,以使得牺牲层中的至少一个的位置比与牺牲层中的该至少一个相邻的绝缘层更加远离虚设沟道孔的中心轴。

为了形成虚设沟道孔,可以在衬底之上形成隔离层以使得第一阶梯区域被布置在隔离层中。随后,可以形成虚设沟道孔以延伸穿过隔离层、以及第一阶梯区域中的牺牲层和绝缘层。

此外,可以在虚设沟道孔中沉积虚设层以形成虚设沟道结构,其中该虚设层沿牺牲层和绝缘层布置并进一步延伸到衬底中。

在该方法中,可以在初始堆叠体的第一阵列区域中形成沟道结构,其中该沟道结构可以延伸穿过牺牲层和绝缘层并进一步延伸到衬底中。

另外,可以形成缝隙结构以在平行于衬底的水平方向上延伸并进一步延伸到衬底中。在一些实施例中,缝隙结构可以进一步延伸穿过第一阵列区域和第一阶梯区域。此外,在初始堆叠体中可以利用字线层来替代牺牲层以形成交替的字线层和绝缘层的堆叠体,其中字线层可以由导电材料形成。此外,可以形成字线触点以在竖直方向上从第一阶梯区域的字线层延伸。

在一些实施例中,初始堆叠体可以包括第二阵列区域,其中第一阶梯区域可以被布置在第一阵列区域与第二阵列区域之间。

在一些实施例中,初始堆叠体可以包括第二阶梯区域,其中第一阵列区域可以被布置在第一阶梯区域与第二阶梯区域之间。

在一些实施例中,虚设沟道孔可以具有垂直于中心轴的横截面。横截面可以具有圆形形状或非圆形形状。

根据本公开内容的另一方面,提供了一种3D-NAND存储器器件。该3D-NAND存储器器件可以包括在垂直于该3D-NAND存储器器件的衬底的竖直方向上交替布置的字线层和绝缘层的堆叠体。该堆叠体可以包括第一阵列区域和相邻的第一阶梯区域。该3D-NAND存储器器件还可以包括虚设沟道结构,该虚设沟道结构在竖直方向上延伸穿过堆叠体的第一阶梯区域中的字线和绝缘层,其中字线层中的至少一个的位置比与字线层中的该至少一个相邻的绝缘层更加远离虚设沟道结构的中心轴。该3D-NAND存储器器件可以包括在第一阵列区域中形成的沟道结构。该沟道结构可以延伸穿过字线层和绝缘层并进一步延伸到衬底中。3D-NAND存储器器件可以包括延伸到衬底中的缝隙结构。该缝隙结构可以进一步在平行于衬底的水平方向上延伸,以延伸穿过第一阵列区域和第一阶梯区域。该3D-NAND存储器器件还可以包括字线触点,该字线触点在竖直方向上从第一阶梯区域的相应字线层延伸。

在一些实施例中,每个字线层可以位于比与相应字线层相邻的绝缘层更加远离虚设沟道结构的中心轴。

在该半导体器件中,虚设沟道结构可以包括虚设层,该虚设层沿字线层和绝缘层布置并进一步延伸到衬底中。

附图说明

通过与附图一起阅读以下具体实施方式最佳地理解本公开内容的各方面。注意,根据行业中的标准实践,各个特征未按比例绘制。事实上,为讨论清晰起见,各个特征的尺寸可以任意地增加或缩小。

图1是根据本公开内容的示例性实施例的示例性3D-NAND存储器器件的横截面视图。

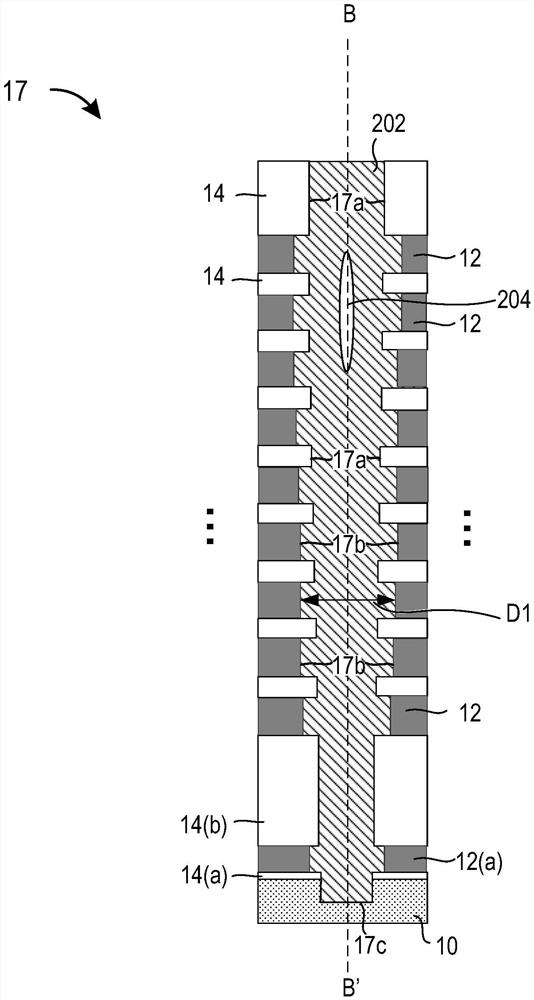

图2是根据本公开内容的示例性实施例的虚设沟道结构的横截面视图。

图3-图6是根据本公开内容的示例性实施例的制造虚设沟道结构的各个中间步骤的横截面视图。

图7是根据本公开内容的示例性实施例的用于制造3D-NAND存储器器件的过程的流程图。

具体实施方式

以下公开内容提供了用于实现所提供主题内容的不同特征的不同实施例或示例。以下描述组件和布置的特定示例以简化本公开内容。当然,这些仅仅是示例而并非旨在限制。例如,在以下描述中在第二特征上方或之上形成第一特征可以包括其中第一和第二特征可以直接接触的实施例,并且还可以包括其中可以在第一和第二特征之间形成另外的特征以使得第一和第二特征可能不直接接触的实施例。另外,本公开内容可以在各个示例中重复附图标记和/或字母。该重复是为了简化和清晰的目的,并且自身并不规定所讨论的各个实施例和/或配置之间的关系。

此外,在本文中可以使用空间相对术语(例如“之下”、“下方”、“下部”、“之上”、“上部”等等)以简化描述,以便描述一个元素或特征与另一元素或特征的关系,如附图中所示出的。空间相对术语旨在涵盖除了附图中所描绘的取向之外设备在使用或操作中的不同取向。装置可以以其它方式取向(旋转90度或处于其它取向)并且本文所使用的空间相对描述符同样可以相应地解读。

3D-NAND存储器器件可以包括在字线层和绝缘层的堆叠体中形成的阶梯区域和阵列区域。字线层和绝缘层可以交替地设置在衬底之上。字线层可以包括顺序地布置在衬底之上的一个或多个底部选择栅极(BSG)层、栅极层(或字线层)、以及一个或多个顶部选择栅极(TSG)层。阵列区域可以包括多个沟道结构。每个沟道结构可以耦合到字线层以形成相应的垂直NAND存储器单元串。垂直NAND存储器单元串可以包括沿衬底的高度方向(或Z方向)顺序地且串联地设置在衬底之上的一个或多个底部选择晶体管(BST)、多个存储器单元(MC)、以及一个或多个顶部选择晶体管(TST)。该一个或多个BST可以由沟道结构和该一个或多个BSG层形成,MC可以由沟道结构和字线层形成,并且该一个或多个TST可以由沟道结构和该一个或多个TSG层形成。

在3D-NAND器件中,阶梯区域可以包括多个虚设沟道结构,这些虚设沟道结构被配置为:在基于后栅极制造技术来形成字线层期间支撑/支承阶梯区域。在后栅极制造技术中,可以在衬底之上形成交替的牺牲层和绝缘层的初始堆叠体。随后可以在初始堆叠体中形成沟道结构,并且随后可以移除牺牲层并利用字线层来替代。在相关示例中,由于在绝缘层之间形成空间,因此在移除牺牲层时会发生绝缘层的塌陷。当虚设沟道结构之间的间隔增大时,塌陷会更糟。

在本公开内容中,提供了例如具有螺纹配置的虚设沟道结构。虚设沟道结构可以包括沿绝缘层并围绕中心轴形成的第一侧壁,以及沿字线层并围绕中心轴形成的第二侧壁,其中第二侧壁位于比第一侧壁更远离中心轴。基于螺纹配置,可以增加虚设沟道结构的有效临界尺寸(CD)。因此,可以减小虚设沟道结构之间的间隔,并且可以防止阶梯区域中的塌陷。

图1是示例性3D-NAND存储器器件100(也被称为器件100)的横截面视图。如图1中所示,3D-NAND存储器器件100可以具有衬底10。在衬底10之上交替地堆叠体多个字线层12a-12p和多个绝缘层14a-14q。在图1的示例性实施例中,包括16个字线层和17个绝缘层。应该注意,图1仅仅是示例,并且基于器件结构可以包括任意数量的字线层和绝缘层。

在一些实施例中,最低字线层12a可以充当连接到BST的栅极的底部选择栅极(BSG)层。在一些实施例中,BSG层12a之上的一个或多个字线层(例如字线层12b-12c)可以是连接到虚设存储器单元(虚设MC)的栅极的虚设字线层(或虚设BSG层)。BST和虚设MC一起能够控制阵列公共源极(ACS)区域16与存储器单元之间的数据传输。

在一些实施例中,最高字线层12p可以充当连接到TST的栅极的顶部选择栅极(TSG)层。在一些实施例中,TSG层12p之下的一个或多个字线层(例如字线层12n-12o)可以是连接到虚设存储器单元(虚设MC)的栅极的虚设字线层(或虚设TSG层)。TST和虚设MC一起控制位线(未示出)与存储器单元之间的数据传输。

绝缘层14a-14q可以位于衬底10上并且与字线层12a-12p交替地布置。字线层12a-12p通过绝缘层14a-14q彼此间隔开。另外,字线层12a-12p通过绝缘层14a-14q中的最低绝缘层14a与衬底10间隔开。

在一些实施例中,可以首先使用牺牲字线层(或牺牲层)(例如SiN)来形成图1中所示出的字线层12a-12p。可以移除牺牲字线层并利用高K层、粘合层、以及一个或多个金属层来替代。高K层可以由氧化铝(Al

在一些实施例中,3D-NAND存储器器件100可以具有阵列区域100A和两个阶梯区域100B-100C。阶梯区域100B-100C可以位于阵列区域100A的两侧。字线层和绝缘层可以以阶梯式轮廓或步进式轮廓延伸到阶梯区域100B-100C中。

3D-NAND存储器器件100可以包括阵列区域100A中的多个沟道结构18。在衬底10之上沿衬底的Z方向(也被称为竖直方向或高度方向)形成沟道结构18。如图1中所示,包括五个沟道结构18。然而,图1仅仅是示例,并且在3D-NAND存储器器件100中可以包括任意数量的沟道结构18。沟道结构18可以延伸穿过字线层12a-12p和绝缘层14a-14q,并进一步延伸到衬底10中以形成垂直存储器单元串的阵列。每个垂直存储器单元串可以包括对应的沟道结构,该沟道结构耦合到字线层12a-12p以形成一个或多个底部选择晶体管(BST)、多个存储器单元(MC)、以及一个或多个顶部选择晶体管(TST)。该一个或多个BST、MC和一个或多个TST顺序地且串联地设置在衬底之上。另外,每个沟道结构18还可以包括在竖直方向上围绕中心轴A-A’同心地布置的沟道层(未示出)、遂穿层(未示出)、电荷捕获层(未示出)和阻隔层(未示出)。

此外,每个沟道结构18还可以包括顶部沟道触点19和底部沟道触点21。底部沟道触点21可以延伸到衬底10中。沟道层、遂穿层、电荷捕获层和阻隔层可以位于底部沟道触点21之上。阻隔层可以在竖直方向上形成并与字线层12a-12p和绝缘层14a-14q直接接触。电荷捕获层可以沿阻隔层的内表面形成。遂穿层可以沿电荷捕获层的内表面形成,并且沟道层可以沿遂穿层的内表面形成。顶部沟道触点19可以沿沟道层的内表面形成,并且还布置在沿沟道层的内表面形成的介电层(未示出)之上。介电层还可以设置在底部沟道触点21之上。

在图1的实施例中,阻隔层由SiO

3D-NAND存储器器件100可以具有多个缝隙结构(或栅极线缝隙结构)。例如,图1中包括两个缝隙结构20a-20b。在一些实施例中,使用后栅极制造技术来形成3D-NAND存储器器件100,因此形成缝隙结构以协助移除牺牲字线层并形成真实栅极。在一些实施例中,缝隙结构可以由导电材料制成并位于阵列公共源极(ACS)区域16以充当触点。在衬底10中形成ACS区域以充当公共源极。在一些实施例中,缝隙结构可以由介电材料制成以充当分离结构。在图1的示例性实施例中,缝隙结构20a-20b位于阵列区域100A的两个相对的边界并连接到ACS区域16。

在一些实施例中,缝隙结构20a-20b可以延伸穿过字线层12a-12p和绝缘层14a-14q,并进一步沿衬底10的第一方向(也被称为长度方向或X方向)延伸。在一些实施例中,缝隙结构20a-20b可以具有介电间隔体26、导电层30和触点28。介电间隔体26可以沿缝隙结构的侧壁形成并与字线层和绝缘层直接接触。可以沿介电间隔体26并在ACS区域16之上形成导电层30。可以沿介电间隔体26并在导电层30之上形成触点28。在图1的实施例中,介电间隔体26由SiO

器件100还可以包括被布置在阶梯区域100B和100C中的多个虚设沟道结构17。虚设沟道结构可以在竖直方向上延伸穿过阶梯区域100B和100C中的字线层12a-12p和绝缘层14a-14q。虚设沟道结构17可以被配置为:在基于后栅极制造技术来形成字线(或栅极线)层12a-12p时支撑阶梯区域。在一些实施例中,虚设沟道结构17和沟道结构18由相同的材料形成并具有相似的配置。因此,每个虚设沟道结构17可以包括围绕垂直轴B-B’同心地布置的沟道层、遂穿层、电荷捕获层和阻隔层。在一些实施例中,沟道结构17和沟道结构18由不同的材料制成并具有不同的配置。例如,虚设沟道结构17可以由介电材料制成。

3D-NAND存储器器件100可以具有多个字线触点结构(或字线触点)22。字线触点结构22在介电层(或隔离层)24中形成并位于字线层12a-12p上以连接到字线层12a-12p。为简单和清晰起见,在阶梯区域100B和100C中的每个区域中仅示出了三个字线触点结构22。字线触点结构22还可以耦合到栅极电压。可以通过字线层12将栅极电压施加到BST、MC和TST的栅极以相应地对BST、MC和TST进行操作。

应该注意,图1仅仅是示例。在图1的示例性实施例中,器件100可以包括第一阵列区域(例如,阵列区域100A)、第一阶梯区域(例如,阶梯区域100B)和第二阶梯区域(例如,阶梯区域100C),其中第一阵列区域被布置在第一阶梯区域与第二阶梯区域之间。在另一示例性实施例中,器件100可以包括第一阵列区域、第二阵列区域和第一阶梯区域。第一阶梯区域可以被布置在第一阵列区域与第二阵列区域之间。

图2是虚设沟道结构17的横截面视图。如图2中所示,虚设沟道结构17可以具有圆柱形轮廓并延伸到衬底10中。虚设沟道结构17可以在竖直方向(或Z方向)上延伸穿过字线层12和绝缘层14。虚设沟道结构17可以具有垂直于中心轴B-B’的横截面。在一些实施例中,横截面可以具有圆形形状。在其它实施例中,横截面可以具有非圆形形状,例如胶囊形状、矩形形状和弧形形状。

仍然参考图2,虚设沟道结构17可以具有沿绝缘层14的第一侧壁17a、沿字线层12的第二侧壁17b、以及位于衬底10中的底部17c。字线层12比绝缘层14更加远离中心轴B-B’。在一个实施例中,每个字线层12可以位于比与相应字线层相邻的绝缘层14更加远离中心轴B-B’。在另一实施例中,字线层12的子集可以位于比与相应字线层相邻的绝缘层14更加远离中心轴B-B’。根据工艺变化,字线层12的子集可以是与虚设沟道结构17的底部相邻的字线层、与虚设沟道结构17的顶部相邻的字线层、或与虚设沟道结构17的中部相邻的字线层。例如,字线层12a比相邻的绝缘层14a和14b更加远离中心轴B-B’。因此,第二侧壁17b可以比第一侧壁17a更加远离中心轴B-B’凹进。虚设沟道结构17可以包括沿第一侧壁17a和第二侧壁17b设置的虚设层202。虚设层202还可以布置在虚设沟道结构17的底部17c之上。

应该注意,图2仅仅示出了虚设沟道结构17的被设置在字线层12和绝缘层14中的部分。如图1中所示,虚设沟道结构17还可以在竖直方向上延伸并设置在隔离层24中。另外,根据相应虚设沟道结构的位置,每个虚设沟道结构17可以延伸穿过阶梯区域中不同数量的字线层和绝缘层。

与相关示例相比,虚设沟道结构17可以具有“螺纹配置”或交错配置,其中字线层12的子集或全部与绝缘层14偏移。例如,字线层12可以比绝缘层14更加远离虚设沟道结构17的中心轴B-B’。螺纹配置可以增加虚设沟道结构17的有效临界尺寸(CD)。有效CD可以通过第二侧壁17b被定义为D1。相应地,阶梯区域(例如,100B或100C)中的两个虚设沟道结构17之间的间隔可以减小并且可以防止阶梯区域中的塌陷。

在一些实施例中,虚设层202可以由SiO、SiN、SiCN、SiCON或多晶硅制成。在一些实施例中,可以在形成虚设层202期间在虚设层202中形成一个或多个间隙(或空隙)204。可以应用任何适当的沉积工艺来形成虚设层202,例如化学气相沉积(CVD)工艺、物理气相沉积(PVD)工艺、扩散工艺、或原子层沉积(ALD)工艺。

图3-图6是制造具有螺纹配置的虚设沟道结构的各个中间步骤的横截面视图。如图3中所示,可以在衬底10之上形成交替的牺牲层304和绝缘层14的初始堆叠体。在一些实施例中,初始堆叠体可以具有第一阵列区域(例如,100A)、第一阶梯区域(例如,100B)和第二阶梯区域(例如,100C)。第一阵列区域被布置在第一阶梯区域与第二阶梯区域之间。在一些实施例中,初始堆叠体可以具有第一阵列区域、第二阵列区域和第一阶梯区域。第一阶梯区域被布置在第一阵列区域与第二阵列区域之间。

在图3的示例性实施例中,牺牲层304可以由介电材料(例如SiN或任何其它适当的介电材料)制成。例如,绝缘层14可以由SiO制成。牺牲层304和绝缘层14可以通过CVD工艺、PVD工艺、扩散工艺、ALD工艺、或任何其它适当的沉积工艺、或其组合来形成。

此外,可以在衬底10之上形成隔离层(例如,24)以使得初始堆叠体能够被隔离层覆盖。可以应用表面平坦化工艺(例如化学机械抛光(CMP)工艺)来移除初始堆叠体顶表面之上的多余隔离层。当CMP工艺完成时,隔离层的顶表面可以与初始堆叠体的顶表面齐平。随后可以在初始堆叠体中形成多个虚设沟道孔。图3示出了示例性虚设沟道孔302。虚设沟道孔302可以延伸穿过隔离层(未示出)、牺牲层304和绝缘层14,并进一步延伸到衬底10中。虚设沟道孔302可以具有沿牺牲层304和绝缘层14形成的初始侧壁302a以及位于衬底10中的底部302b。在一些实施例中,虚设沟道孔302的垂直于中心轴B-B’的横截面可以具有圆形形状。在其它实施例中,虚设沟道孔302的横截面可以具有非圆形形状,例如胶囊形状、矩形形状和弧形形状。

为了形成虚设沟道孔302,可以运行图案化工艺,该图案化工艺可以包括光刻工艺和蚀刻工艺。光刻工艺可以在隔离层(例如,24)之上形成具有图案的图案化掩模(未示出),并且蚀刻工艺随后可以将图案转移到隔离层和初始堆叠体中。当蚀刻工艺完成时,可以通过干剥离工艺移除图案化掩模。随后可以在移除图案化掩模时形成虚设沟道孔302。

在图4中,可以应用蚀刻工艺以从初始侧壁302a移除牺牲层304的各部分。相应地,牺牲层304可以从初始侧壁302a凹进或偏移。在一些实施例中,牺牲层304可以从初始侧壁302a凹进距离D2。距离D2可以在10nm至20nm的范围中。蚀刻工艺可以是湿法蚀刻工艺或等离子(或干法)蚀刻工艺。蚀刻工艺可以选择性地蚀刻牺牲层304,并使绝缘层14保持未被接触或轻微蚀刻。在图4的示例性实施例中,牺牲层304可以是SiN,并且蚀刻工艺可以是湿法蚀刻工艺,其中可以应用磷酸(例如,H

在图5中,可以沉积虚设层202以填充虚设沟道孔302。可以沿虚设沟道孔302的第一侧壁302’和第二侧壁302”形成虚设层202。相应地,虚设层202可以延伸穿过牺牲层304和绝缘层14,并进一步与牺牲层304和绝缘层14直接接触。虚设层202可以进一步延伸到衬底10中以设置在虚设沟道孔302的底部302b之上。虚设层202可以由SiO、SiN、SiCN、多晶硅或其它适当材料制成。可以应用任何适当的沉积工艺来形成虚设层202,例如化学气相沉积(CVD)工艺、物理气相沉积(PVD)工艺、扩散工艺、或原子层沉积工艺。在一些实施例中,可以在虚设层202中形成一个或多个间隙(或空隙)204。间隙204的形成可以由多种因素驱动,例如虚设沟道孔302的纵横比和/或沉积工艺的工艺条件。

在图6中,牺牲层304可以由字线层12替代以在衬底10之上形成交替的字线层12和绝缘层14的堆叠体。为了利用字线层12来替代牺牲层304,可以形成多个缝隙沟槽(未示出)。缝隙沟槽可以沿平行于衬底10的水平方向(例如X方向)延伸。随后,可以应用蚀刻工艺以通过缝隙结构移除牺牲层304,其中可以通过缝隙结构引入蚀刻酸或蚀刻等离子。相应地,可以在初始堆叠体中的绝缘层14之间形成空穴(或空间)。此外,可以在初始堆叠体中的绝缘层14之间中的空穴中形成字线层12以替代牺牲层304。在一些实施例中,可以移除牺牲层304并利用包括高K层、粘合层和/或一个或多个金属层的字线层12来替代。高K层可以由氧化铝(Al

在一些实施例中,在利用字线层12来替代牺牲层304之前,可以在初始堆叠体的阵列区域(例如,100A)中形成多个沟道结构(例如,18)。在一些实施例中,当利用字线层来替代牺牲层时,可以利用导电材料(例如多晶硅和/或钨)来填充缝隙沟槽以形成缝隙结构(例如,20a和20b)。另外,可以在阶梯区域(例如,100B和100C)中形成字线触点(例如,22)。字线触点可以在竖直方向上从字线层12延伸并进一步延伸穿过隔离层(例如,24)。

当利用字线层12来替代牺牲层304时,可以相应地形成虚设沟道结构17。如图6中所示,虚设沟道结构17可以具有与图2中的虚设沟道结构17类似的特征。例如,虚设沟道结构17可以具有沿绝缘层14的第一侧壁17a、沿字线层12的第二侧壁17b、以及位于衬底10中的底部17c。每个字线层12可以位于比与相应字线层相邻的绝缘层14更加远离虚设沟道结构17的中心轴B-B’。在其它实施例中,字线层12的子集可以位于比与该字线层子集相邻的绝缘层14更加远离中心轴B-B’。

图7是根据本公开内容的一些实施例的用于制造所公开的3D-NAND器件的过程700的流程图。过程700开始于步骤S702,在步骤702处,可以在垂直于衬底的竖直方向上在衬底之上形成交替的牺牲层和绝缘层的初始堆叠体。该初始堆叠体可以包括第一阵列区域和阶梯式配置中的相邻第一阶梯区域。在一些实施例中,可以如参考图1所示出地执行步骤S702。

在步骤S704处,可以形成虚设沟道孔以在竖直方向上延伸穿过第一阶梯区域中的牺牲层和绝缘层,并进一步延伸到衬底中。在一些实施例中,可以如参考图3所示出地执行步骤S704。

过程700随后行进至步骤S706。在步骤S706处,可以执行蚀刻工艺以使牺牲层的各部分从虚设沟道孔的中心轴凹进或偏移。相应地,每个牺牲层可以位于比与相应牺牲层相邻的绝缘层更加远离虚设沟道孔的中心轴。在其它实施例中,可以蚀刻牺牲层的子集并使其位于比绝缘层(例如,相应的相邻绝缘层)更加远离虚设沟道孔的中心轴。在一些实施例中,可以如参考图4所示出地执行步骤S706。

为了形成虚设沟道结构,过程700还可以包括:在虚设沟道孔中形成虚设层,并利用字线层来替代牺牲层,这可以如参考图5-图6所示出地执行。

应该注意,可以在过程700之前、之间和之后提供另外的步骤,并且对于过程700的另外实施例,所描述的一些步骤可以被代替、消除、或以不同顺序执行。例如,在利用字线层来替代牺牲层之前,可以在初始堆叠体的阵列区域中形成沟道结构。另外,当利用字线层来替代牺牲层时,还可以形成缝隙结构和字线触点。此外,可以在3D-NAND存储器器件的第一和第二触点结构之上形成各种另外的互连结构(例如,具有导线和/或通孔的金属化层)。这种互连结构将3D-NAND存储器器件与其它触点结构和/或有源器件电连接以形成功能电路。还可以形成另外的器件特征,例如钝化层、输入/输出结构等等。

本文所描述的各个实施例提供了针对相关3D-NAND存储器器件的若干优点。在本公开内容中,提供了具有螺纹配置的虚设沟道结构。虚设沟道结构可以包括沿绝缘层并围绕中心轴形成的第一侧壁,以及沿字线层并围绕中心轴形成的第二侧壁,其中第二侧壁位于比第一侧壁更远离中心轴。基于螺纹配置,可以增加虚设沟道结构的有效临界尺寸(CD)。因此,可以减小虚设沟道结构之间的间隔,并且可以防止阶梯区域中的塌陷。

前述内容概括了若干实施例的特征以使得本领域技术人员可以更好地理解本公开内容的各方面。本领域技术人员将意识到,他们可以容易地使用本公开内容作为用于设计或修改其它过程和结构以执行相同目的和/或实现本文所引入的实施例的相同优点的基础。本领域技术人员还将认识到,此类等效构造不会偏离本公开内容的精神和范围,并且他们可以对其作出各种改变、替换和更改而不会偏离本公开内容的精神和范围。

- 具有新颖虚设沟道结构的三维NAND存储器器件

- 具有虚设沟道结构的三维存储器件及其形成方法