薄膜晶体管及其制造方法和包括薄膜晶体管的显示设备

文献发布时间:2023-06-19 11:39:06

相关申请的交叉引用

本申请要求享有于2019年12月27日提交的韩国专利申请No.10-2019-0176126的权益,通过引用将该专利申请并入本文,如同在本文完全阐述一样。

技术领域

本发明涉及一种薄膜晶体管、制造薄膜晶体管的方法和包括薄膜晶体管的显示设备。

背景技术

晶体管广泛用作电子设备领域中的开关元件或驱动元件。特别是,由于可在玻璃基板或塑料基板上制造薄膜晶体管(TFT),所以TFT广泛用作诸如液晶显示装置或有机发光装置之类的显示设备的开关元件。

根据构成有源层的材料的种类、电极(栅极电极、源极电极和漏极电极)的布置结构、形成沟道的方法等,可以以各种结构形成薄膜晶体管。

近来,广泛使用氧化物半导体TFT(下文中,称为氧化物TFT),其具有比非晶硅TFT的迁移率更高的迁移率并且比多晶硅TFT更容易应用于大尺寸区域。

氧化物TFT结构的主要示例是共面结构(coplanar structure),在共面结构中,沉积有在有源层上被图案化的栅极绝缘层和栅极电极,并且布置在覆盖沉积结构的层间介电层上的源极电极和漏极电极分别通过穿过层间介电层的接触孔与有源层的源极区域和漏极区域连接。

在共面结构的氧化物TFT中,有源层的中间区域被用作沟道区域,沟道区域的两侧区域被导电化并用作源极区域和漏极区域。由于导电化的源极区域和漏极区域的载流子浓度高于沟道区域的载流子浓度,所以产生从源极区域和漏极区域到沟道区域的氢扩散。

由于这种氢扩散,在源极区域与沟道区域之间以及漏极区域与沟道区域之间形成扩散区域(由于氢扩散而导致特性变化的区域)。扩散区域可导致劣化,并且考虑到TFT的制造工艺,难以调整扩散区域的宽度。由于这个原因,TFT的可靠性可劣化。

此外,如果沟道区域较短,则可改进TFT的开关性能。扩散区域加剧了劣化,因而成为制造较短沟道区域的限制。

上述背景技术的公开内容为本发明的发明人所拥有,以设计出本申请,或者上述背景技术的公开内容是设计本申请的过程中获得的技术信息,但不能认为是在提交本申请之前对公众公开的已知技术。

发明内容

鉴于上述问题进行了本发明,本发明的一个目的是提供一种薄膜晶体管、制造薄膜晶体管的方法和包括薄膜晶体管的显示设备,其中薄膜晶体管被实现为防止在用作沟道的半导体与用作源极区域和漏极区域的第一导体部分和第二导体部分之间发生氢扩散。

本发明的另一个目的是提供一种薄膜晶体管、制造薄膜晶体管的方法和包括薄膜晶体管的显示设备,其中通过防止在半导体与第一导体部分之间以及在半导体与第二导体部分之间产生扩散区域,薄膜晶体管能够实现短沟道。

除了上述本发明的目的以外,所属领域技术人员将从本发明的以下描述清楚理解到本发明的其他目的和特征。

根据本发明的一个方面,可通过提供一种薄膜晶体管实现上述和其他目的,所述薄膜晶体管包括:形成在基板上的半导体;形成在所述半导体上的栅极绝缘膜;形成在所述栅极绝缘膜上的栅极电极;形成在所述基板上的第一绝缘膜;第一导体部分,所述第一导体部分形成在所述第一绝缘膜上并且形成在所述半导体的一侧;和第二导体部分,所述第二导体部分形成在所述第一绝缘膜上并且形成在所述半导体的另一侧,其中在所述半导体与所述第一导体部分之间可形成有所述第一绝缘膜的第一部分,并且在所述半导体与所述第二导体部分之间可形成有所述第一绝缘膜的第二部分。

根据本发明的另一个方面,可通过提供一种制造薄膜晶体管的方法实现上述和其他目的,所述方法包括以下步骤:形成依次沉积在基板上的半导体、栅极绝缘膜和栅极电极;在所述基板上形成第一绝缘膜以至少覆盖所述半导体的侧面;和在所述第一绝缘膜上在所述半导体的两侧形成彼此面对的第一导体部分和第二导体部分,其中形成所述第一导体部分和所述第二导体部分的步骤可包括:以形成在所述半导体的一侧的第一绝缘膜为边界在所述半导体的一侧形成所述第一导体部分、以及以形成在所述半导体的另一侧的第一绝缘膜为边界在所述半导体的另一侧形成所述第二导体部分。

根据本发明的其他方面,可通过提供一种显示设备实现上述和其他目的,所述显示设备包括显示面板,所述显示面板包括用于驱动与栅极线和数据线连接的多个像素的每一个的至少一个薄膜晶体管,其中所述至少一个薄膜晶体管可包括根据本发明实施方式的薄膜晶体管。

除了上述问题的方案以外的根据各实施方式的细节包括在下面的描述和附图中。

由于根据本发明的薄膜晶体管包括形成在用作沟道的半导体与用作源极区域和漏极区域的第一导体部分和第二导体部分之间的绝缘膜以用作氢扩散防止膜,所以可避免从第一导体部分和第二导体部分到半导体的氢扩散。

因此,由于在半导体与第一导体部分之间以及在半导体与第二导体部分之间未形成扩散区域,所以可防止发生由于扩散区域导致的劣化,由此可实现短沟道并且可提高薄膜晶体管的可靠性。

此外,由于第一导体部分和第二导体部分由具有比半导体的电阻相对较低的电阻的材料形成,所以可降低导电电阻,由此可更容易实现短沟道。

除了上述本发明的效果以外,所属领域技术人员将从本发明的以上描述清楚理解到本发明的其他优点和特征。

附图说明

将从下面结合附图的详细描述更清楚地理解本发明的上述和其他的目的、特征和其他优点,其中:

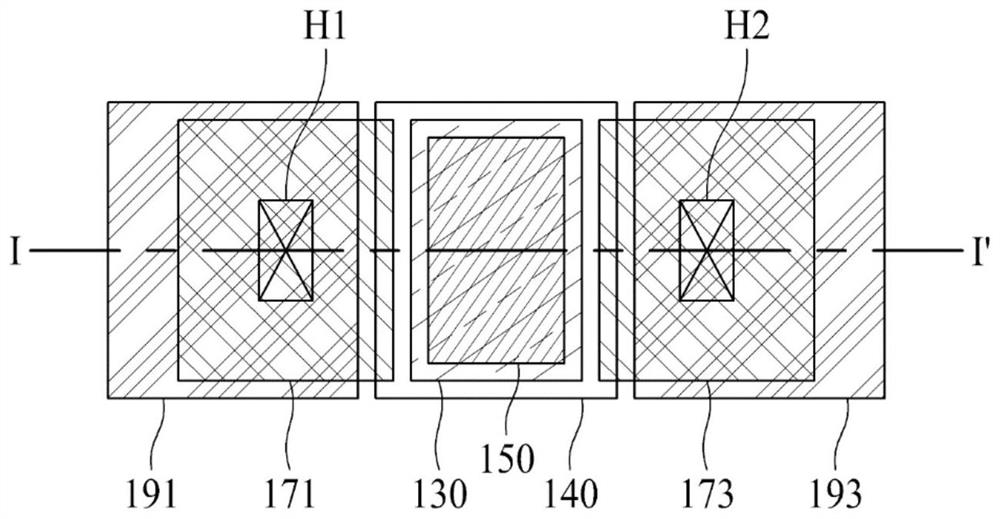

图1是图解根据本发明一个实施方式的薄膜晶体管的平面图;

图2是图解沿图1的线I-I’截取的薄膜晶体管的剖面图;

图3是图解根据本发明另一个实施方式的薄膜晶体管的剖面图;

图4是图解根据本发明其他实施方式的薄膜晶体管的剖面图;

图5A至图5L是图解根据本发明实施方式的制造薄膜晶体管的方法的示图;

图6是图解根据本发明实施方式的包括薄膜晶体管的显示设备的示意图;

图7是图解图6的显示面板中包括的一个像素P的电路结构的一示例的示图;

图8是图解图6的显示面板中包括的一个像素P的电路结构的另一示例的示图。

具体实施方式

下文中,将参照附图和实施方式描述根据本发明实施方式的薄膜晶体管、制造薄膜晶体管的方法和包括薄膜晶体管的显示设备。

图1是图解根据本发明一个实施方式的薄膜晶体管的平面图,图2是图解沿图1的线I-I’截取的薄膜晶体管的剖面图,图3是图解根据本发明另一个实施方式的薄膜晶体管的剖面图,图4是图解根据本发明其他实施方式的薄膜晶体管的剖面图。

如图1和图2中所示,根据本发明一个实施方式的薄膜晶体管100可包括基板110、形成在基板110上的缓冲层120、形成在缓冲层120上的半导体130、形成在半导体130上的栅极绝缘膜140、和形成在栅极绝缘膜140上的栅极电极150。

根据实施方式可省略缓冲层120,但下文中将描述包括缓冲层120的薄膜晶体管100的结构。

此外,薄膜晶体管100可包括:形成为围绕半导体130、栅极绝缘膜140和栅极电极150的第一绝缘膜160;以第一绝缘膜160为边界形成在半导体130的一侧的第一导体部分171;和以第一绝缘膜160为边界形成在半导体130的另一侧的第二导体部分173。

此时,第一绝缘膜160布置在半导体130的一侧与第一导体部分171之间以及在半导体130的另一侧与第二导体部分173之间,并且为了形成MIS(金属-绝缘体-半导体)接触结构,第一绝缘膜160与半导体130的一侧和第一导体部分171直接接触,并且与半导体130的另一侧和第二导体部分173直接接触。

详细地说,第一绝缘膜160的第一部分与半导体130的一侧和第一导体部分171的一侧直接接触,第一绝缘膜160的第二部分与半导体130的另一侧和第二导体部分173的一侧直接接触。

薄膜晶体管100可包括:全部形成在缓冲层120上的第二绝缘膜180;第一电极191,第一电极191设置在第二绝缘膜180上并且通过形成在第二绝缘膜180中的第一接触孔H1与第一导体部分171连接;和第二电极193,第二电极193设置在第二绝缘膜180上并且通过形成在第二绝缘膜180中的第二接触孔H2与第二导体部分173连接。

可使用玻璃基板或具有柔性特性的塑料基板作为基板110。当使用塑料基板作为基板110时,基板110可由聚酰亚胺等形成。

缓冲层120可由无机材料或有机材料形成。例如,缓冲层120可包括诸如SiO

缓冲层120可由单层或多层形成,以阻挡从基板110渗透的诸如水分和氧气之类的颗粒,根据实施方式可省略缓冲层120。

半导体130用作沟道,并且可由In、Ga、Zn和O制成的IGZO(InGaZnO)形成,但不限于此。半导体130可包括其他氧化物半导体材料,例如,IZO(InZnO)类、IGO(InGaO)类、ITO(InSnO)类、IGZO(InGaZnO)类、IGZTO(InGaZnSnO)类、ITZO(InSnZnO)类、IGTO(InGaSnO)类、GO(GaO)类、GZTO(GaZnSnO)类、ZTO(ZnSnO)类和GZO(GaZnO)类氧化物半导体材料中的至少之一。

在图2中,半导体130由单层形成,但可由多层结构形成。

半导体130可由图3中所示的双层结构或图4中所示的三层结构形成,或者可由四层或更多层的多层结构形成。

如图3中所示,当半导体130由双层结构形成时,半导体130可由第一半导体层131和形成在第一半导体层131上的第二半导体层133构成。此时,第一半导体层131和第二半导体层133的一侧隔着第一绝缘膜160面对第一导体部分171,并且第一半导体层131和第二半导体层133的另一侧隔着第一绝缘膜160面对第二导体部分173。为了形成MIS接触结构,第一绝缘膜160与第一半导体层131和第二半导体层133的每一个的一侧以及第一导体部分171的一侧直接接触,并且与第一半导体层131和第二半导体层133的每一个的另一侧以及第二导体部分173的一侧直接接触。

第一半导体层131用于保护第二半导体层133,第二半导体层133用作主沟道层。

优选地,第一半导体层131由具有比第二半导体层133的载流子浓度低的载流子浓度的材料,以比第二半导体层133的厚度厚的厚度形成。

第一半导体层131可由具有低载流子浓度但是具有低迁移率的材料形成,以提高工艺裕度。第一半导体层131通过防止氢从半导体130的外部渗透到第二半导体层133或者防止第二半导体层133的电子困在半导体130外部的绝缘层或绝缘膜中,防止第二半导体层133的电特性劣化。

第一半导体层131具有优异的膜稳定性和优异的机械稳定性,为此,第一半导体层131包括Ga。Ga与氧形成稳定的结合,并且包括Ga氧化物的膜具有优异的膜稳定性。

根据本发明的一个实施方式,第一半导体层131可包括IGZO(InGaZnO)类、IGO(InGaO)类、IGTO(InGaSnO)类、IGZTO(InGaZnSnO)类、GZTO(GaZnSnO)类、GZO(GaZnO)类和GO(GaO)类氧化物半导体材料中的至少之一。

为了具有优异的膜稳定性,以原子数为基准,相对于第一半导体层131的全部金属原子,第一半导体层131可包括40原子百分比(at%)或更多的Ga。当第一半导体层131中全部金属原子中的Ga的含量为40at%或更多时,第一半导体层131可具有优异的膜稳定性。

根据本发明的一个实施方式,第一半导体层131的全部金属原子可以是Ga。在这种情况下,第一半导体层131可由GO(GaO)类氧化物半导体材料制成,第一半导体层131中全部金属原子中的Ga的含量为100at%。

具有优异的膜稳定性和机械稳定性的第一半导体层131具有比第二半导体层133的电阻率大的电阻率。第一半导体层131也用作沟道层,因而应当具有相对优良的电特性。

考虑到第一半导体层131的电特性,相对于全部金属原子,第一半导体层131可包括90at%或更少的Ga,并且可进一步包括可提高迁移率或载流子浓度的其他金属原子。

第一半导体层131可形成为比第二半导体层133厚(例如,15nm或更大),并且当第一半导体层131具有高载流子浓度时,第一半导体层131可与第二半导体层133混合然后被导电化,由此需要适当控制载流子浓度。

第二半导体层133可由具有高载流子浓度且具有高迁移率特性的材料形成,以改进电流特性,并且第二半导体层133可由包含In/Sn的氧化物半导体中的至少之一形成。第二半导体层133具有比第一半导体层131的霍尔迁移率大的霍尔迁移率。因此,在第二半导体层133中可形成电流流动的主通道。

根据本发明的一个实施方式,第二半导体层133包括铟(In)。铟(In)提高半导体层的迁移率并且增加电荷密度。包括In的第二半导体层133可具有优异的霍尔迁移率。根据本发明的一个实施方式,第二半导体层133可具有比第一半导体层131大的In浓度。

根据本发明的一个实施方式,第二半导体层133例如可由诸如IZO(InZnO)类、IGO(InGaO)类、ITO(InSnO)类、IGZO(InGaZnO)类、IGZTO(InGaZnSnO)类和ITZO(InSnZnO)类氧化物半导体材料之类的氧化物半导体材料制成。然而,本发明的一个实施方式不限于上述材料,第二半导体层133可由本领域已知的其他氧化物半导体材料制成。例如,第二半导体层133可由不包含In的GZTO(GaZnSnO)类氧化物半导体材料制成。

根据本发明的一个实施方式,第二半导体层133可具有3nm至30nm的厚度。如果第二半导体层133的厚度太薄,则第二半导体层133的膜稳定性劣化,难以形成均匀的膜。因此,第二半导体层133可具有3nm或更大的厚度。

另一方面,如果第二半导体层133的厚度变得比所需的更厚,则包括第二半导体层133的薄膜晶体管的阈值电压的变化宽度可增加,所以第二半导体层133可具有30nm或更小的厚度。更详细地说,第二半导体层133可具有5nm至15nm的厚度。

根据本发明的一个实施方式,可通过金属有机化学气相沉积(MOCVD)形成第一半导体层131和第二半导体层133。可通过MOCVD形成具有均匀表面以及具有薄且稳定的膜特性的第一半导体层131和第二半导体层133。

此外,当通过MOCVD形成第一半导体层131和第二半导体层133时,第一半导体层131与第二半导体层133之间的边界被区分,并且第一半导体层131与第二半导体层133之间形成的混合区域的厚度减小。结果,第一半导体层131和第二半导体层133的有效厚度减小被最小化,由此即使第一半导体层131和第二半导体层133可能较薄,第一半导体层131和第二半导体层133仍可执行它们独有的功能。

当通过MOCVD形成第一半导体层131和第二半导体层133时,可在没有真空制动(vacuum braking)的情况下通过连续工艺依次形成第一半导体层131和第二半导体层133。结果,可降低工艺成本,并且可提高工艺的稳定性。如图4中所示,当半导体130形成为三层结构时,半导体130可由第一半导体层131、形成在第一半导体层131上的第二半导体层133和形成在第二半导体层133上的第三半导体层135构成。

此时,第一至第三半导体层131、133和135的每一个的一侧隔着第一绝缘膜160面对第一导体部分171,并且第一至第三半导体层131、133和135的每一个的另一侧隔着第一绝缘膜160面对第二导体部分173。为了形成MIS接触结构,第一绝缘膜160与第一至第三半导体层131、133和135的每一个的一侧以及第一导体部分171的一侧直接接触,并且与第一至第三半导体层131、133和135的每一个的另一侧以及第二导体部分173的一侧直接接触。

由于第一半导体层131和第二半导体层133具有与图2中所示的第一半导体层131和第二半导体层133相同的特性,所以将省略对它们的详细描述。

第三半导体层135是要与栅极绝缘膜140形成界面,以提高可靠性,第三半导体层135可由可执行抗氧化功能的氧化物膜(例如,IGZO等)形成,并且可形成为能够执行该功能的最小厚度(例如,3nm或更小)。

第三半导体层135例如可包括诸如IGO(InGaO)类、IGZO(InGaZnO)类、IGZTO(InGaZnSnO)类、IGTO(InGaSnO)类、GO(GaO)类、GZTO(GaZnSnO)类和GZO(GaZnO)类氧化物半导体材料中之类的Ga基氧化物半导体的至少之一。

为了具有优异的膜稳定性,以原子数为基准,相对于第三半导体层135的全部金属原子,第三半导体层135包括40原子百分比(at%)或更多的Ga。

根据本发明的一个实施方式,第三半导体层135的全部金属原子可以是Ga。在这种情况下,第三半导体层135可由GO(GaO)类氧化物半导体材料制成,第三半导体层135中全部金属原子中的Ga的含量为100at%。

以与第一半导体层131和第二半导体层133相同的方式,可通过金属有机化学气相沉积(MOCVD)形成第三半导体层135。在这种情况下,可在没有真空制动的情况下通过连续工艺依次形成第一半导体层131、第二半导体层133和第三半导体层135。这样,第一半导体层131可形成为比第二半导体层133厚,并且第二半导体层133可形成为比第三半导体层135厚。第一半导体层131的厚度、第二半导体层133的厚度和第三半导体层135的厚度可根据半导体130的总厚度、第一半导体层131的特性、第二半导体层133的特性和第三半导体层135的特性而变化。

优选地,第二半导体层133由具有比第一半导体层131的载流子浓度高的载流子浓度的材料形成。

栅极绝缘膜140和栅极电极150可由与应用于一般氧化物TFT的栅极绝缘膜和栅极电极相同的材料形成。

根据实施方式,栅极绝缘膜140可包括无机膜,例如,SiOx和SiNx中的至少之一,或者可包括Al

根据实施方式,栅极电极150可包括下述材料的至少之一:诸如Al或Al合金之类的Al基金属;诸如Ag或Ag合金之类的Ag基金属;诸如Cu或Cu合金之类的Cu基金属;诸如Mo或Mo合金之类的Mo基金属;Cr;Ta;Nd和Ti,并且栅极电极150可由单层或者两层或更多层的多层形成。

第一绝缘膜160全部形成在缓冲层120上,或者如果未形成缓冲层120,则形成在整个基板110上,并且第一绝缘膜160可形成为至少覆盖半导体130的侧面。

在这种情况下,半导体130的侧面可包括面对第一导体部分171的侧面(第一侧面)和面对第二导体部分173的侧面(第二侧面)。

就是说,第一绝缘膜160可形成在半导体130与第一导体部分171之间以及在半导体130与第二导体部分173之间。

例如,可通过原子层沉积(ALD)形成第一绝缘膜160,并且第一绝缘膜160可由可通过ALD形成的介电材料(例如,SiO

可通过金属有机化学气相沉积(MOCVD)形成第一绝缘膜160。更详细地说,可通过使用MOCVD的ALD形成第一绝缘膜160。

尽管图2示出了第一绝缘膜160形成为覆盖栅极绝缘膜140的侧面和上表面(具体地,未形成栅极电极150时而暴露的上部区域)并且还覆盖栅极电极150的侧面和上表面,但第一绝缘膜160可不形成在栅极绝缘膜140的侧面和上表面以及栅极电极150的侧面和上表面上。

就是说,第一绝缘膜160可形成为覆盖缓冲层120的其中未形成半导体130的区域或者在不形成缓冲层120的情况下覆盖基板110的其中未形成半导体130的区域、半导体130的侧面、以及栅极绝缘膜140的下表面(具体地,由于未与栅极电极150接触而暴露的下部区域)。

因此,如图2中所示,第一绝缘膜160可形成在第一导体部分171的上表面与栅极绝缘膜140的下表面之间以及在第二导体部分173的上表面与栅极绝缘膜140的下表面之间。

在这种情况下,在栅极绝缘膜140和栅极电极150的每一个中,栅极绝缘膜140的侧面和栅极电极150的侧面对应于的半导体130的侧面。

由于第一绝缘膜160形成在半导体130与第一导体部分171之间以及在半导体130与第二导体部分173之间,所以第一导体部分171、第一绝缘膜160和半导体130可形成金属绝缘体半导体(MIS)接触结构,并且第二导体部分173、第一绝缘膜160和半导体130可形成MIS接触结构。

由于第一绝缘膜160形成在半导体130与第一导体部分171之间以及在半导体130与第二导体部分173之间,所以可避免半导体130与第一导体部分171之间的氢扩散和半导体130与第二导体部分173之间的氢扩散,由此第一绝缘膜160可被认为是“氢扩散防止膜”。

由于可根据用作第一绝缘膜160的材料的特性以各种方式调节第一绝缘膜160的厚度,所以第一绝缘膜160的厚度不限于具体值。然而,第一绝缘膜160可形成为在防止发生从导体部分171和173向半导体130的氢扩散的同时不干扰载流子移动的厚度,并且可形成为可在第一导体部分171、第一绝缘膜160和半导体130之间形成MIS接触并且在第二导体部分173、第一绝缘膜160和半导体130之间形成MIS接触的适当厚度。优选地,第一绝缘膜160可形成为

第一导体部分171和第二导体部分173用作源极区域和漏极区域并且形成在第一绝缘膜160上,第一导体部分171形成为面对半导体130的第一侧面并且第二导体部分173形成为面对半导体130的第二侧面,由此第一导体部分171和第二导体部分173可形成为以半导体130为中心或者在半导体130的两侧彼此面对。

详细地说,第一导体部分171的一侧可与布置在半导体130的第一侧面处的第一绝缘膜160接触,并且第二导体部分173的一侧可与布置在半导体130的第二侧面处的第一绝缘膜160接触。

第一导体部分171和第二导体部分173可由IZO(InZnO)类材料形成,但不限于此。第一导体部分171和第二导体部分173可包括其他氧化物半导体材料,例如,IGO(InGaO)类、ITO(InSnO)类、IGZO(InGaZnO)类、IGZTO(InGaZnSnO)类、ITZO(InSnZnO)类、IGTO(InGaSnO)类、GO(GaO)类、GZTO(GaZnSnO)类、ZTO(ZnSnO)类和GZO(GaZnO)类氧化物半导体材料中的至少之一。

然而,第一导体部分171和第二导体部分173优选由具有比半导体130的电阻相对较低的电阻的材料形成,以降低导电电阻,使得可容易实现短沟道。

尽管第一导体部分171可用作薄膜晶体管100的源极区域并且第二导体部分173可用作薄膜晶体管100的漏极区域,但第一导体部分171可用作薄膜晶体管100的漏极区域并且第二导体部分173可用作薄膜晶体管100的源极区域。

第二绝缘膜180全部形成在缓冲层120上,以覆盖第一绝缘膜160、第一导体部分171和第二导体部分173,并且第二绝缘膜180可用作层间介电(ILD)膜。

例如,第二绝缘膜180可由诸如SiOx、SiNx和AlOx之类的无机绝缘材料以单层结构或多层结构形成,或者可由有机绝缘材料形成。

第一电极191可形成在第二绝缘膜180上并且通过形成在第二绝缘膜180中的第一接触孔H1与第一导体部分171连接,第二电极193可形成在第二绝缘膜180上并且通过形成在第二绝缘膜180中的第二接触孔H2与第二导体部分173连接。

第一电极191和第二电极193的每一个可由Mo、Al、Cr、W、Ti、Ni、Nd和Cu中的任意一种或其合金制成的单层或多层形成。

以这种方式,由于用作氢扩散防止膜的第一绝缘膜160形成在用作沟道的半导体130与用作源极区域和漏极区域的第一导体部分171和第二导体部分173之间,所以可避免从第一导体部分171和第二导体部分173向半导体130的氢扩散。

此外,本发明的第一绝缘膜160不仅可防止从第一导体部分171和第二导体部分173向半导体130的氢扩散,而且还可防止从通过在形成第二绝缘膜180或第一电极191和第二电极193的工艺之后的工艺形成的绝缘膜或有机膜向半导体130的氢扩散。

因此,由于在半导体130与第一导体部分171之间以及在半导体130与第二导体部分173之间未形成扩散区域,所以可避免由于扩散区域导致的劣化,由此可实现短沟道并且可提高薄膜晶体管的可靠性。

此外,由于第一导体部分171和第二导体部分173由具有比半导体130的电阻相对较低的电阻的材料形成,所以可降低导电电阻,由此可更容易实现短沟道。

上面已参照图1至图4描述了根据本发明实施方式的薄膜晶体管的结构。下文中,将参照图5A至图5L描述根据本发明实施方式的制造薄膜晶体管的方法。

图5A至图5L是图解根据本发明一个实施方式的制造薄膜晶体管的方法的示图。

首先,如图5A中所示,在形成于基板110上的缓冲层120上依次沉积要形成半导体130、栅极绝缘膜140和栅极电极150的第一半导体材料层130a、栅极绝缘膜材料层140a和栅极电极材料层150a。

例如,IGZO等可用作第一半导体材料,SiOx、SiNx等可用作栅极绝缘膜材料。诸如Al、Ag、Cu、Mo、Cr、Ta和Ti之类的金属或其合金可用作栅极电极材料。

不同于图5A,可在基板110上依次沉积第一半导体材料层130a、栅极绝缘膜材料层140a和栅极电极材料层150a。

下文中,将作为示例描述薄膜晶体管100包括缓冲层120的结构,但是之后将描述的制造薄膜晶体管的方法可同样应用于薄膜晶体管100不包括缓冲层120的情况。

此外,尽管图5A示出了半导体130形成为单层,但半导体130可如图3和4中所示形成为多层。

当如图3中所示半导体130形成为两层结构时,第一半导体材料层130a的沉积可包括依次沉积用于形成第一半导体层131的材料层和用于形成第二半导体层133的材料层。

此时,用于形成第一半导体层的材料层可由具有比用于形成第二半导体层的材料层的载流子浓度低的载流子浓度的材料制成,并且可沉积为比用于形成第二半导体层的材料层厚。

当如图4中所示半导体130形成为三层结构时,第一半导体材料层130a的沉积可包括依次沉积用于形成第一半导体层131的材料层、用于形成第二半导体层133的材料层和用于形成第三半导体层135的材料层。

此时,用于形成第一半导体层的材料层可沉积为比用于形成第二半导体层的材料层厚,并且用于形成第二半导体层的材料层可沉积为比用于形成第三半导体层的材料层厚。

之后,如图5B至图5F中所示,形成图案化的半导体130、栅极绝缘膜140和栅极电极150。

详细地说,在栅极电极材料层150a上形成被图案化的光刻胶PR(图5B),并且使用光刻胶图案作为掩模通过湿蚀刻将栅极电极材料层150a图案化,以形成栅极电极150(图5C)。使用光刻胶图案作为掩模通过干蚀刻将栅极绝缘膜材料层140a图案化,以形成栅极绝缘膜140(图5D),并且使用光刻胶图案作为掩模通过湿蚀刻将第一半导体材料层130a图案化,以形成半导体130(图5E),然后去除光刻胶图案(图5F)。

之后,如图5G中所示,在依次形成有图案化的半导体130、栅极绝缘膜140和栅极电极150的缓冲层120上形成第一绝缘膜160。

第一绝缘膜160形成为与半导体130的一侧和另一侧直接接触。当半导体130设置为如图3中所示包括第一半导体层131和第二半导体层133的双层结构时,第一绝缘膜160形成为与第一半导体层131和第二半导体层133的每一个的一侧以及第一半导体层131和第二半导体层133的每一个的另一侧接触。

当半导体130设置为如图4中所示包括第一至第三半导体层131、133和135的三层结构时,第一绝缘膜160形成为与第一至第三半导体层131、133和135的每一个的一侧以及第一至第三半导体层131、133和135的每一个的另一侧接触。

可通过原子层沉积(ALD)形成第一绝缘膜160,但不限于此。可通过金属有机化学气相沉积(MOCVD)形成第一绝缘膜160。更详细地说,可通过使用MOCVD的ALD形成第一绝缘膜160。

因此,第一绝缘膜160可形成为覆盖缓冲层120的暴露的上表面;半导体130的暴露的侧面;栅极绝缘膜140的暴露的下表面、侧面和上表面;以及栅极电极150的暴露的侧面和上表面。

不同于此实施方式,第一绝缘膜160可根据工艺不形成在栅极绝缘膜140的侧面和上表面以及栅极电极150的侧面和上表面上。

就是说,第一绝缘膜160可形成为覆盖缓冲层120的暴露的上表面、半导体130的暴露的侧面和栅极绝缘膜140的暴露的下表面。

之后,如图5H至5J中所示,在第一绝缘膜160上形成第一导体部分171和第二导体部分173。

详细地说,如图5H中所示,在整个第一绝缘膜160上沉积第二半导体材料层170a,并且通过在沉积第二半导体材料层170a的过程中执行的等离子体处理或氢处理将第二半导体材料层170a导电化。

例如,IZO等可用作第二半导体材料,并且可通过MOCVD沉积第二半导体材料层170a。然而,第二半导体材料的种类和沉积第二半导体材料层170a的方法不限于本实施方式。在沉积第二半导体材料层170a之后,在第二半导体材料层170a上将光刻胶PR图案化(图5I),并且使用光刻胶图案作为掩模通过湿蚀刻将第二半导体材料层170a图案化,以形成第一导体部分171和第二导体部分173,然后去除光刻胶图案(图5J)。

因此,第一导体部分171以形成在半导体130的一侧处的第一绝缘膜160为边界形成在半导体130的一侧,并且第二导体部分173以形成在半导体130的另一侧处的第一绝缘膜160为边界形成在半导体130的另一侧。

因此,第一导体部分171的一侧与形成在半导体130的一侧处的第一绝缘膜160直接接触,并且第二导体部分173的一侧与形成在半导体130的另一侧处的第一绝缘膜160直接接触。

详细地说,第一导体部分171的一侧与第一绝缘膜160中的形成为与半导体130的一侧接触的第一部分直接接触,并且第二导体部分173的一侧与第一绝缘膜160中的形成为与半导体130的另一侧接触的第二部分直接接触。

之后,如图5K中所示,在整个缓冲层120上形成第二绝缘膜180,由此第二绝缘膜180覆盖第一绝缘膜160、第一导体部分171和第二导体部分173。

之后,如图5L中所示,在第二绝缘膜180中形成与第一导体部分171连接的第一接触孔H1和与第二导体部分173连接的第二接触孔H2,并且在第二绝缘膜180上形成通过第一接触孔H1与第一导体部分171连接的第一电极191和通过第二接触孔H2与第二导体部分173连接的第二电极193。

第二绝缘膜180可在缓冲层120上形成为覆盖第一绝缘膜160、第一导体部分171和第二导体部分173。

例如,第二绝缘膜180可由诸如SiOx、SiNx和AlOx之类的无机绝缘材料以单层结构或多层结构形成,或者可由有机绝缘材料形成。

图6是图解根据本发明实施方式的包括薄膜晶体管的显示设备的示意图,图7是图解图6的显示面板中包括的一个像素P的电路结构的一示例的示图,图8是图解图6的显示面板中包括的一个像素P的电路结构的另一示例的示图。

参照图6,根据本发明实施方式的显示设备600可包括显示面板610、栅极驱动器620、数据驱动器630和控制器640。

显示面板610中可设置有栅极线GL和数据线DL,像素P可设置在栅极线GL和数据线DL的交叉区域中,并且每个像素P中可包括至少一个根据本发明实施方式的薄膜晶体管100。

栅极驱动器620被控制器640控制,并且在一帧内向栅极线GL依次提供可使开关元件导通的栅极脉冲GP。在这种情况下,一帧是指通过显示面板610输出一个图像的时间段。

此外,栅极驱动器620在一帧的不提供栅极脉冲的其他时间段向栅极线GL提供可使开关元件截止的栅极截止信号Goff。下文中,栅极脉冲GP和栅极截止信号Goff将统称为扫描信号SS。

如图6中所示,栅极驱动器620可封装在显示面板610中。以这种方式,栅极驱动器620直接封装在显示面板610中的结构将被称为面板内栅极(GIP)结构。

栅极驱动器620可封装在位于显示面板610外部的其他结构中,可封装在显示面板610的仅一侧中,或者可封装在显示面板610的两侧中。

数据驱动器630将从控制器640输入的图像数据RGB转换为模拟数据电压,并且在向栅极线GL提供栅极脉冲GP的每一个水平周期将一个水平行的数据电压Vdata提供至数据线DL,由此每个像素P基于图像数据显示亮度。

控制器640可通过使用从外部系统(未示出)提供的各种时序信号(例如,垂直同步信号、水平同步信号、时钟信号等)输出用于控制栅极驱动器620的栅极控制信号GCS和用于控制数据驱动器630的数据控制信号DCS。

此外,控制器640可采样从外部系统输入的输入图像数据,重新排列采样的图像数据并且将重新排列后的图像数据RGB提供至数据驱动器630。

显示面板610中包括的每个像素P可包括至少一个根据本发明实施方式的薄膜晶体管。

显示面板610可以是应用于液晶显示设备的液晶显示面板或应用于有机发光显示设备的有机发光显示面板。

当显示面板610是液晶显示面板时,显示面板610中包括的每个像素P可包括用作驱动液晶的开关元件的至少一个薄膜晶体管TFT。

如图7中所示,像素P中可设置根据本发明实施方式的薄膜晶体管TFT,薄膜晶体管TFT连接在数据线DL与像素电极PXL之间,并且薄膜晶体管TFT的栅极端子可与栅极线GL连接。

可通过提供至像素电极PXL的数据电压和提供至公共电极COM的公共电压改变液晶的折射率,由此液晶的光透射率可变化,并且可通过控制光透射率控制光的亮度。在这种情况下,在像素电极PXL与公共电极COM之间形成用于保持数据电压的存储电容Cst。

当显示面板610是有机发光显示面板时,如图8中所示,显示面板610中包括的每个像素P可包括用于输出光的有机发光二极管OLED、和用于驱动有机发光二极管OLED的像素驱动电路PDC。

像素P中可形成有用于向像素驱动器电路PDC提供驱动信号的信号线DL、GL、PLA、PLB、SL和SPL。

像素驱动电路PDC可包括:开关晶体管Tsw1,开关晶体管Tsw1连接至栅极线GL和数据线DL;驱动晶体管Tdr,驱动晶体管Tdr根据通过开关晶体管Tsw1传输的数据电压Vdata来控制输出到有机发光二极管OLED的电流的大小;和感测晶体管Tsw2,感测晶体管Tsw2用于感测驱动晶体管Tdr的特性。感测晶体管Tsw2、驱动晶体管Tdr和有机发光二极管OLED在第一节点n1处相连。开关晶体管Tsw1、驱动晶体管Tdr和电容器Cst在第二节点n2处相连。驱动晶体管Tdr通过高电位电压供应线PLA连接至高电位电压源ELVDD。有机发光二极管OLED通过低电位电压供应线PLB连接至低电位电压源ELVSS。感测晶体管Tsw2通过初始化电压供应线SL连接至初始化电压Vini。

栅极脉冲和栅极低信号提供至栅极线GL,它们被统称为栅极信号VG。

扫描脉冲和扫描低信号提供至与感测晶体管Tsw2的栅极连接的扫描脉冲线SPL,它们被统称为扫描控制信号SS。

开关晶体管Tsw1、驱动晶体管Tdr和感测晶体管Tsw2可以是根据本发明实施方式的氧化物薄膜晶体管。

除了晶体管Tsw1、Tdr和Tsw2以外,像素驱动电路PDC可进一步包括其他晶体管。进一步设置在像素驱动电路PDC中的晶体管可以是根据本发明实施方式的氧化物薄膜晶体管。

下面将描述根据本发明实施方式的薄膜晶体管、制造薄膜晶体管的方法和包括薄膜晶体管的显示设备。

根据本发明实施方式的薄膜晶体管可包括:形成在基板上的半导体;形成在所述半导体上的栅极绝缘膜;形成在所述栅极绝缘膜上的栅极电极;形成在所述基板上的第一绝缘膜;第一导体部分,所述第一导体部分形成在所述第一绝缘膜上并且形成在所述半导体的一侧;和第二导体部分,所述第二导体部分形成在所述第一绝缘膜上并且形成在所述半导体的另一侧,其中在所述半导体与所述第一导体部分之间可形成有所述第一绝缘膜的第一部分,并且在所述半导体与所述第二导体部分之间可形成有所述第一绝缘膜的第二部分。

根据本发明的实施方式,所述第一绝缘膜的第一部分可与所述半导体的一侧和所述第一导体部分的一侧直接接触,并且所述第一绝缘膜的第二部分可与所述半导体的另一侧和所述第二导体部分的一侧直接接触。

根据本发明的实施方式,所述半导体可包括:第一半导体层;和形成在所述第一半导体层上的第二半导体层,其中所述第一绝缘膜的第一部分可形成在所述第一半导体层和所述第二半导体层的每一个与所述第一导体部分之间,并且所述第一绝缘膜的第二部分可形成在所述第一半导体层和所述第二半导体层的每一个与所述第二导体部分之间。

根据本发明的实施方式,所述第一绝缘膜的第一部分可与所述第一半导体层和所述第二半导体层的每一个的一侧以及所述第一导体部分的一侧直接接触,并且所述第一绝缘膜的第二部分可与所述第一半导体层和所述第二半导体层的每一个的另一侧以及所述第二导体部分的一侧直接接触。

根据本发明的实施方式,所述第一半导体层可由具有比所述第二半导体层的载流子浓度低的载流子浓度的材料形成并且形成为比所述第二半导体层厚。

根据本发明的实施方式,所述半导体可包括:第一半导体层;形成在所述第一半导体层上的第二半导体层;和形成在所述第二半导体层上的第三半导体层,所述第一绝缘膜的第一部分可形成在所述第一半导体层、所述第二半导体层和所述第三半导体层的每一个与所述第一导体部分之间,并且所述第一绝缘膜的第二部分可形成在所述第一半导体层、所述第二半导体层和所述第三半导体层的每一个与所述第二导体部分之间。

根据本发明的实施方式,所述第一绝缘膜的第一部分可与所述第一半导体层、所述第二半导体层和所述第三半导体层的每一个的一侧以及所述第一导体部分的一侧直接接触,并且所述第一绝缘膜的第二部分可与所述第一半导体层、所述第二半导体层和所述第三半导体层的每一个的另一侧以及所述第二导体部分的一侧直接接触。

根据本发明的实施方式,所述第一半导体层可形成为比所述第二半导体层厚,并且所述第二半导体层可形成为比所述第三半导体层厚。

根据本发明的实施方式,所述第一绝缘膜可进一步形成在所述第一导体部分的上表面与所述栅极绝缘膜的下表面之间以及在所述第二导体部分的上表面与所述栅极绝缘膜的下表面之间。

根据本发明的实施方式,所述第一绝缘膜可进一步形成为覆盖所述栅极绝缘膜的侧面和暴露的上表面以及所述栅极电极的侧面和上表面。

根据本发明的实施方式,所述薄膜晶体管可进一步包括:第二绝缘膜,所述第二绝缘膜形成在所述基板上以覆盖所述第一绝缘膜、所述第一导体部分和所述第二导体部分;第一电极,所述第一电极形成在所述第二绝缘膜上并且通过形成在所述第二绝缘膜形中的第一接触孔与所述第一导体部分接触;和第二电极,所述第二电极形成在所述第二绝缘膜上并且通过形成在所述第二绝缘膜形中的第二接触孔与所述第二导体部分接触。

根据本发明的实施方式,所述第一导体部分和所述第二导体部分可由氧化物半导体材料形成,并且可由具有比所述半导体的电阻低的电阻的材料形成。

根据本发明的实施方式,所述第一绝缘膜可形成为

根据本发明实施方式的制造薄膜晶体管的方法可包括以下步骤:形成依次沉积在基板上的半导体、栅极绝缘膜和栅极电极;在所述基板上形成第一绝缘膜以至少覆盖所述半导体的侧面;和在所述第一绝缘膜上在所述半导体的两侧形成彼此面对的第一导体部分和第二导体部分,其中形成所述第一导体部分和所述第二导体部分的步骤可包括:以形成在所述半导体的一侧的第一绝缘膜为边界在所述半导体的一侧形成所述第一导体部分、以及以形成在所述半导体的另一侧的第一绝缘膜为边界在所述半导体的另一侧形成所述第二导体部分。

根据本发明的实施方式,形成所述第一绝缘膜的步骤可包括:将所述第一绝缘膜形成为与所述半导体的一侧直接接触并且与所述半导体的另一侧直接接触。

根据本发明的实施方式,形成所述第一导体部分和所述第二导体部分的步骤可包括:将所述第一导体部分的一侧形成为与形成在所述半导体的一侧的第一绝缘膜直接接触、以及将所述第二导体部分的一侧形成为与形成在所述半导体的另一侧的第一绝缘膜直接接触。

根据本发明的实施方式,形成所述半导体的步骤可包括:在所述基板上依次沉积用于形成第一半导体层的第一材料层和用于形成第二半导体层的第二材料层,其中所述第一材料层由具有比所述第二材料层的载流子浓度低的载流子浓度的材料形成并且沉积为比所述第二材料层厚。

根据本发明的实施方式,形成所述半导体的步骤可包括:在所述基板上依次沉积用于形成第一半导体层的第一材料层、用于形成第二半导体层的第二材料层和用于形成第三半导体层的第三材料层,其中所述第一材料层沉积为比所述第二材料层厚,并且所述第二材料层沉积为比所述第三材料层厚。

根据本发明的实施方式,形成所述第一绝缘膜的步骤可包括:将所述第一绝缘膜形成为覆盖所述栅极绝缘膜的暴露的下表面。

根据本发明的实施方式,形成所述第一绝缘膜的步骤可包括:将所述第一绝缘膜形成为覆盖所述栅极绝缘膜的侧面、所述栅极绝缘膜的暴露的上表面、以及所述栅极电极的侧面和上表面。

根据本发明实施方式的方法可进一步包括以下步骤:在所述基板上形成第二绝缘膜以覆盖所述第一绝缘膜、所述第一导体部分和所述第二导体部分;在所述第二绝缘膜中形成与所述第一导体部分连接的第一接触孔和与所述第二导体部分连接的第二接触孔;和在所述第二绝缘膜上形成第一电极和第二电极,所述第一电极通过所述第一接触孔与所述第一导体部分连接,所述第二电极通过所述第二接触孔与所述第二导体部分连接。

根据本发明的实施方式,所述第一导体部分和所述第二导体部分可由氧化物半导体材料形成,并且可由具有比所述半导体的电阻低的电阻的材料形成。

根据本发明的实施方式,所述第一绝缘膜可形成为

根据本发明实施方式的显示设备可包括显示面板,所述显示面板包括用于驱动与栅极线和数据线连接的多个像素的每一个的至少一个薄膜晶体管,所述薄膜晶体管可包括:形成在基板上的半导体;形成在所述半导体上的栅极绝缘膜;形成在所述栅极绝缘膜上的栅极电极;形成在所述基板上的第一绝缘膜;第一导体部分,所述第一导体部分形成在所述第一绝缘膜上并且形成在所述半导体的一侧;和第二导体部分,所述第二导体部分形成在所述第一绝缘膜上并且形成在所述半导体的另一侧,其中在所述半导体与所述第一导体部分之间可形成有所述第一绝缘膜的第一部分,并且在所述半导体与所述第二导体部分之间可形成有所述第一绝缘膜的第二部分。

对于所属领域技术人员来说显而易见的是,上述本发明不受上述实施方式和附图限制,并且在不背离本发明的精神或范围的情况下,可在本发明中进行各种替换、修改和变化。因而,本发明的范围由所附权利要求书限定,并且从权利要求书的含义、范围和等同概念得出的所有变化或修改都旨在落入本发明的范围内。

上述各实施方式可组合以提供进一步的实施方式。必要的话可修改实施方式的各方面,以利用各专利、申请和公开文献的构思提供进一步的实施方式。

根据上面的详细描述,可对实施方式进行这些和其他改变。通常,在所附的权利要求书中,使用的术语不应当解释为将权利要求限制于说明书和权利要求书中公开的具体实施方式,而是应当解释为包括落入这些权利要求涵盖的全部等同范围内的所有可能的实施方式。因此,权利要求书不受具体实施方式的限制。

- 制造薄膜晶体管的方法及其脱氢装置和包括该方法制造的薄膜晶体管的有机发光显示设备

- 薄膜晶体管及其制造方法和包括薄膜晶体管的显示设备