显示设备

文献发布时间:2023-06-19 11:39:06

相关申请的交叉引用

本申请要求于2019年12月26日向韩国知识产权局提交的大韩民国专利申请No.10-2019-0174886、以及2020年6月30日向韩国知识产权局提交的大韩民国专利申请No.10-2020-0080619的优先权权益,通过引用的方式将这两个专利申请的全部公开内容并入本文中。

技术领域

本公开涉及显示设备,并且更具体地,涉及具有弯曲区域的显示设备。

背景技术

随着信息社会的到来,对各种类型的显示设备、照明设备等的需求不断增长。近来,已经开发并且利用了诸如液晶显示设备、有机发光显示设备、量子点显示设备等的一系列显示设备。

此外,除了开发各种类型的显示设备之外,还开发了面板设计技术以减小显示设备的尺寸,或减小其中不显示图像的边框。在这种方法中,施加弯曲结构的技术对于减小显示设备的尺寸或边框的尺寸可能是非常有效的。然而,当施加弯曲结构时,穿过弯曲区域的信号线中的诸如断裂或短路的一些问题不容易解决。此外,即使检查弯曲区域中是否存在信号线中的这种问题也不容易。

发明内容

根据本公开的实施例,在通过将弯曲结构施加到显示面板来实施窄边框时,为了解决由于面板结构、面板制造工艺等中的一些限制而导致难以通过视觉检验或检验装备等来检查位于弯曲区域中的信号线中异常的存在与否的这种问题,可以提供能够准确地感测位于弯曲区域中的信号线中异常的存在与否的显示设备。

通过这些,可以提供一种显示设备,其能够对在位于弯曲区域中的信号线中诸如断裂、短路等的异常的存在与否执行准确的检查,并且因此,具有没有缺陷的正常弯曲结构。

此外,可以提供一种显示设备,其能够检测出在制造面板之后将在弯曲区域中发生的信号线中的异常。

根据本公开,可以提供一种显示设备,其能够识别出信号线中的异常是存在于弯曲区域中还是存在于除弯曲区域外的另一区域中。

尽管具有弯曲区域的显示设备具有如上所述的各种优点,但是另一方面,就缺陷发生的频率而言,弯曲区域最易损坏。向驱动电路提供信号以使像素发光的各种信号线可以穿过弯曲区域。因此,为了有效地校正可能在显示设备中发生的缺陷,可能期望优先检测在弯曲区域中发生的缺陷。

根据本公开的一个实施例,提供了一种显示设备,其包括:基板,所述基板包括布置了多个子像素并且显示图像的有源区域,以及是有源区域外部的区域的非有源区域;数据驱动电路,所述数据驱动电路将数据信号供应到多个子像素;栅极驱动电路,所述栅极驱动电路将栅极信号供应到多个子像素,以及传感器电路,其感测连接到栅极驱动电路的信号线中异常的存在与否。此外,基板的非有源区域包括与数据驱动电路电连接的驱动电路区域、位于驱动电路区域与有源区域之间并且可以弯曲的弯曲区域以及在弯曲区域和有源区域之间的链接区域。传感器电路包括:提供感测参考信号的感测参考信号线;提供读出信号的读出线;以及电连接至至少一个信号线、感测参考信号线和读出线的感测晶体管。在这种情况下,传感器电路可以设置在链接区域中。因此,可以准确地识别出何处发生了信号线的异常,并校正相应的缺陷。

根据本公开的一个实施例,提供了一种显示设备,该显示设备包括:信号线,其设置成穿过弯曲区域;传感器电路,其连接至该信号线;以及确定电路,其基于通过感测传感器电路获得的信息而确定信号线中的异常。传感器电路包括:连接到确定电路的读出线;提供用于比较确定电路从传感器电路接收的信息的感测参考信号的感测参考信号线;连接到信号线的感测晶体管;以及连接到感测参考信号线、读出线和感测晶体管的控制感测晶体管。因此,可以准确地识别出何处发生了信号线的异常,并校正相应的缺陷。

各种具体特征、配置、技术和过程包括在详细描述和附图中,并且将在下面进行详细讨论。

根据本公开的实施例,在通过将弯曲结构施加到显示面板来实施窄边框时,为了解决由于面板结构、面板制造工艺等中的一些限制而导致难以通过视觉检验或检验装备等来检查位于弯曲区域中的信号线中异常的存在与否的这种问题,可以提供能够准确地感测位于弯曲区域中的信号线中异常的存在与否的显示设备。

此外,根据本公开的实施例,可以提供一种显示设备,其能够检测出在制造面板之后将在弯曲区域中发生的信号线中的异常。

根据本公开的实施例,可以提供一种显示设备,其能够识别出信号线中的异常是存在于弯曲区域中还是存在于弯曲区域外部的另一区域中。

附图说明

图1示出了根据本公开的一个实施例的电子设备的系统构造。

图2示出了根据本公开的一个实施例的施加到显示设备的子像素的等效电路。

图3是示意性地示出了根据本公开的一个实施例的显示面板的弯曲和接线结构的平面图。

图4示出了根据本公开的一个实施例的显示面板的弯曲和链接区域以及与弯曲和链接区域相邻的区域中的弯曲和接线结构。

图5示出了根据本公开的一个实施例的布置在显示面板的弯曲区域中的信号线中的异常。

图6示出了根据本公开的一个实施例的用于感测布置在显示面板的弯曲区域中的信号线中异常的存在与否的传感器电路和确定电路。

图7是示出了根据本公开的一个实施例的传感器电路的感测操作的驱动时序图。

图8示出了根据本公开的一个实施例的在执行传感器电路的感测操作时,当第一信号线处于正常状态时的传感器电路的感测操作。

图9示出了根据本公开的一个实施例的在执行传感器电路的感测操作时,当第一信号线具有断裂时的传感器电路的感测操作。

图10示出了根据本公开的一个实施例的在执行传感器电路的感测操作时,在第一信号线处于正常状态的状况下和在第一信号线具有断裂的状况下的读出信号,所述读出信号由确定电路基于传感器电路的感测而产生。

图11示出了根据本公开的一个实施例的当在显示模式下驱动显示设备时包括在传感器电路中的感测参考信号、第一控制晶体管和第二控制晶体管的状态。

图12示出了根据本公开的一个实施例的当在显示模式下驱动显示设备时传感器电路的状态。

图13是示出了根据本公开的一个实施例的在显示设备中设置了传感器电路的部分的平面图。

图14、图16和图17示出了根据本公开的一个实施例的用于感测布置在显示面板的弯曲区域中的信号线中异常的存在与否的传感器电路。

图15是示出根据本公开的一个实施例的传感器电路的感测操作的驱动时序图。

具体实施方式

当将弯曲结构施加到显示面板以实施窄边框时,由于布置在弯曲区域中的信号线中可能经常出现诸如断裂或短路之类的一些问题,因此通过在显示面板上设置弯曲结构,缺陷率显著增加。由于弯曲过程问题或设计缺陷而导致的可立即识别的过程缺陷会导致信号线出现断裂,这会由于无法及时提供数据信号或GIP信号而导致显示屏出现异常。另一方面,在相对长的时间段后可以识别出微小的断裂或线电解腐蚀,或者由于腐蚀引起的缺陷导致逐渐地且微弱地提供相应的信号,从而导致可靠性规格不满足。由于布置在弯曲区域中的信号线之上或之下设置了数个层,因此通过视觉检验或检验装备等不容易检查布置在弯曲区域中的信号线中是否存在断裂或短路。

为了检查位于弯曲区域中的信号线中的断裂或短路,当去除在布置在弯曲区域中的信号线之上或之下设置的数个层时,信号线也可能被损坏,这使得难以识别缺陷。

此外,由于在执行弯曲处理之后需要执行几个处理,所以在这样的连续处理是在未识别出相关缺陷的状态下执行的情况下,处理时间和制造成本会增加,并且由于未及时执行可靠性故障分析,因此相应的产品开发周期可能会延迟。

为了解决这种问题,在本公开中,提供了用于使显示设备能够感测在位于弯曲区域中的信号线中异常的存在与否的实施例。通过这些,可以提供一种显示设备,其实现了对在位于弯曲区域中的信号线中是否存在断裂等的早期检查,并且因此,具有制造成本降低的正常弯曲结构。

在本公开中,提供了用于使显示设备能够识别出信号线的异常存在于弯曲区域中还是存在于弯曲区域外部的另一区域中的实施例。

此外,提供了具有用于感测位于弯曲区域中的信号线中异常的存在与否的传感器电路的显示设备的实施例。

通过参考下面参考附图来详细描述的本公开的实施例,本公开的优点和特征以及实现所述优点和特征的方法将显而易见。应当注意,本公开不限于以下阐述的实施例,并且可以以各种不同的形式来实施。因此,提供本公开的实施例以用于具体描述本公开,并且用于具体向所属领域中的技术人员告知本公开的范围,并且本发明的范围仅由所附权利要求限定。

另外,在附图中示出的用于描述本公开的示例性实施例的形状、尺寸、比率、角度、数量等仅仅是示例,并且本公开不限于此。在整个本说明书中,相似的附图标记通常表示相似的元件。此外,在本公开的以下描述中,当确定描述可能使本公开的一些实施例中的主题相当不清楚时,将省略对本文中包含的公知的功能和构造的详细描述。

本文中使用的诸如“包括”、“具有”、“包含”、“由…组成”等的术语通常旨在允许添加其他部件,除非这些术语与术语“仅”一起使用。除非上下文另外明确指出,否则本文中使用的单数形式旨在包括复数形式。

在解释本公开的实施例的任何元件或特征时,应该考虑的是,即使当不进行特定的描述时,层、区域和区的任何尺度和相对尺寸也包括公差或误差范围。

在本文中使用诸如“在...上”、“在...之上”、“在…上方”、“在...之下”、“在...下方”、“下方”、“下部”、“上部”、“接近”、“靠近”、“相邻”等空间上相对的术语,来描述一个元件或特征与另一(一个或多个)元件或(一个或多个)特征的如图中所示的关系,并且应解释为,除非使用了诸如“直接地”、“仅”的术语,否则一个或多个元件还可以“插入”元件之间。

在本文中用来描述事件、操作等之间的时间关系的诸如“之后”、“在…之后”、“接着”、“之前”等时间相对的术语通常旨在包括不会连续发生的事件、情况、操作等,除非使用诸如“直接地”、“立即地”等术语。

当本文中使用诸如“第一”、“第二”等术语来描述各种元件或部件时,应当认为这些元件或部件不限于此。这些术语仅仅在本文中用于区分一个元件与其他元件。因此,在本公开的技术概念中,下面提到的第一元件可以是第二元件。

应当理解,本文中所使用的术语“至少一个”可以包括通过组合一个或多个相关联的元件而获得的所有组合。例如,“第一项、第二项和第三项中的至少一个”可以包括由第一项、第二项和第三项中的两个或更多个以及第一项、第二项和第三项中的每一个获得的所有组合。

如本领域中的普通技术人员可以完全理解的,本公开的各种示例性实施例的元件或特征可以部分地或完全地彼此结合或组合,并且可以在技术上以各种方式互锁和操作,并且各种示例性实施例可以彼此独立地或关联地实现。

在下文中,将参考附图详细讨论根据本公开的实施例的显示设备的示例。在用附图标记表示附图的元件时,尽管在不同的附图中示出了元件,但是相同的元件将由相同的附图标记引用。为了便于描述,附图中所示的部件的比例被示出,并且可能与实际比例不同;因此,本公开的实施例不限于附图中所示的比例。

图1示出了根据本公开的一个实施例的电子设备100的系统构造。

参考图1,根据本公开的一个实施例的显示设备100包括:显示面板110,其中布置了多个数据线DL和多个栅极线GL,并且布置了连接到多个数据线DL和多个栅极线GL的多个子像素SP;以及驱动电路,所述驱动电路用于驱动显示面板110。

在功能方面,驱动电路可以包括:数据驱动电路120,所述数据驱动电路120驱动多个数据线DL;栅极驱动电路130,所述栅极驱动电路130驱动多个栅极线GL;控制器140,所述控制器140控制数据驱动电路120和栅极驱动电路130;等等。

显示面板110可以包括其中显示图像的有源区域AA和是有源区域AA外部的区域的非有源区域NA。多个子像素SP可以布置在有源区域AA中,并且用于传递数据信号的多个数据线DL和用于将栅极信号传递给多个子像素SP的多个栅极线GL可以布置在有源区域AA中。

布置在有源区域AA中的多个数据线DL可以向上延伸到非有源区域NA,并且电连接到数据驱动电路120,所述数据驱动电路120电连接到显示面板110。在另一示例中,布置在有源区域AA中的多个数据线DL可以分别电连接到布置在非有源区域NA中的多个数据链接线。多个数据线DL可以通过相应连接的数据链接线电连接到数据驱动电路120。在下文中,为了便于描述和易于理解,无论数据线DL具有用作数据链接线的延伸部分,还是数据线DL连接到单独的数据链接线,具有与数据线DL相同的电状态并且设置在非有源区域NA中的线被称为“数据链接线”。

布置在有源区域AA中的多个栅极线GL可以电连接到设置在非有源区域NA中或与非有源区域NA电连接的栅极驱动电路130。

允许栅极驱动电路130产生或驱动栅极信号所需的栅极驱动相关线可以布置在非有源区域NA中。显示面板110的非显示区域NA中的这种栅极驱动相关线的布置被称为玻璃上线(LOG)类型或面板上线(LOP)类型。

例如,栅极驱动相关线可以包括:一个或多个高电平栅极电压线,所述一个或多个高电平栅极电压线用于将高电平栅极电压传递到栅极驱动电路130;一个或多个低电平栅极电压线,所述一个或多个低电平栅极电压线用于将低电平栅极电压传递到栅极驱动电路130;多个时钟线,所述多个时钟线用于将多个时钟信号传递到栅极驱动电路130;以及一个或多个起始线,所述一个或多个起始线用于将一个或多个起始信号传递到栅极驱动电路130;等等。

多个数据线DL和多个栅极线GL可以布置成在显示面板110中彼此相交;然而,本公开的实施例不限于此。例如,多个数据线DL可以布置成行或列,并且多个栅极线GL可以布置成列或行。在下文中,为了便于描述和易于理解,假设多个数据线DL布置成列,并且多个栅极线GL布置成行。

控制器140通过供应操作或驱动数据驱动电路120和栅极驱动电路130所需的各种类型的控制信号(DCS、GCS)来控制数据驱动电路120和栅极驱动电路130的操作。

控制器140根据在每一帧中处理的时序开始图像数据扫描,将从其他设备或要适应的外部图像提供源输入的图像数据转换为在数据驱动电路120中使用的数据信号形式,并且然后输出由转换产生的图像数据DATA,并且根据图像数据扫描在预配置的时间控制数据线的驱动。

控制器140从外部图像提供源(例如,主机系统)接收各种类型的时序信号以及输入的图像数据,所述时序信号包括垂直同步信号Vsync、水平同步信号Hsync、输入数据使能信号DE、时钟信号CLK等。

除了将从要适应的外部图像提供源输入的图像数据转换为在数据驱动电路120中使用的数据信号形式并且然后输出由转换产生的图像数据DATA以外,为了控制数据驱动电路120和栅极驱动电路130,控制器140接收垂直同步信号Vsync、水平同步信号Hsync、数据输入信号DE、时钟信号CLK等中的一个或多个时序信号,产生数个类型的控制信号,并且然后将产生的控制信号供应到数据驱动电路120和栅极驱动电路130。

例如,为了控制栅极驱动电路130,控制器140输出数个类型的栅极控制信号GCS,包括栅极起始脉冲GSP、栅极移位时钟GSC、栅极输出使能信号GOE等。这里,栅极起始脉冲GSP用于控制栅极驱动电路130中包括的一个或多个栅极-驱动器集成电路G-DIC的操作起始时序。栅极移位时钟GSC是共同输入到一个或多个栅极驱动器集成电路的时钟信号,并且用于控制扫描信号(栅极脉冲)的移位时序。栅极输出使能信号GOE用于指示一个或多个栅极驱动器集成电路的时序信息。

此外,为了控制数据驱动电路120,控制器140输出数个类型的数据控制信号DCS,包括源极起始脉冲SSP、源极采样时钟SSC、源极输出使能信号SOE等。这里,源极起始脉冲SSP用于控制数据驱动电路120中包括的一个或多个源极-驱动器集成电路的数据采样起始时序。源极采样时钟SSC是用于控制每个源极-驱动器集成电路中的数据的采样时序的时钟信号。源极输出使能信号SOE用于控制数据驱动电路120的输出时序。

控制器140可以是在典型的显示技术中使用的时序控制器,或是除了时序控制器的典型功能之外能够额外地执行其他控制功能的控制装置/设备。

控制器140可以实施为与数据驱动电路120分离的部件,或实施为与数据驱动电路120集成的集成电路。

数据驱动电路120通过从控制器140接收图像数据DATA并且然后将数据信号提供给多个数据线DL来驱动多个数据线DL。这里,数据驱动电路120也可以被称为源极驱动电路。

数据驱动电路120可以通过包括一个或多个源极-驱动器集成电路来实施。每个源极-驱动器集成电路S-DIC可以包括移位寄存器、锁存电路、数模转换器DAC、输出缓冲器等。每个源极-驱动器集成电路S-DIC还可以包括一个或多个模数转换器ADC。

每个源极-驱动器集成电路S-DIC可以以卷带自动接合(TAB)类型、玻璃上芯片(COG)类型或面板上芯片(COP)类型连接到诸如显示面板110的接合焊盘的导电焊盘,或者可以直接设置在显示面板110上。在一些实例中,源极-驱动器集成电路S-DIC可以被设置为集成到显示面板110中。此外,每个源极-驱动器集成电路S-DIC可以以膜上芯片(COF)类型来实施,其中源极-驱动器集成电路S-DIC被安装在连接到显示面板110的源极-电路膜上。

在下文中,为了便于描述和易于理解,数据驱动电路120被实施为一个源极-驱动器集成电路S-DIC,并且以玻璃上芯片(COG)类型或以面板上芯片(COP)类型连接到显示面板110。

栅极驱动电路130通过将扫描信号顺序地供应到多个栅极线GL来顺序地驱动多个栅极线GL。这里,栅极驱动电路130也可以被称为扫描驱动电路。

栅极驱动电路130可以包括移位寄存器、电平移位器等。

栅极驱动电路130可以以卷带自动接合(TAB)类型、玻璃上芯片(COG)类型或面板上芯片(COP)类型连接到诸如显示面板110的接合焊盘的导电焊盘,或者可以通过被实施成面板中栅极(GIP)类型而直接设置在显示面板110上。在一些实例中,栅极驱动电路130可以设置为集成到显示面板110中。此外,栅极驱动电路130可以以膜上芯片(COF)类型来实施,其中栅极驱动电路130通过被实施为多个栅极-驱动器集成电路G-DIC而被安装在连接到显示面板110的栅极-电路膜上。

在下文中,为了便于描述和易于理解,基于如下情况进行讨论,在所述情况中,栅极驱动电路130包括多个栅极驱动器,并且多个栅极驱动器通过被实施成面板中栅极(GIP)类型而被布置在显示面板110的非有源区域NA中。

根据控制器140的控制,栅极驱动电路130将具有导通电压电平或关断电压电平的扫描信号顺序地供应到多个栅极线GL。

当通过来自栅极驱动电路130的扫描信号断言特定的栅极线时,数据驱动电路120将从控制器140接收的图像数据DATA转换为具有模拟信号的形式的数据信号,并且将得到的数据信号供应到多个数据线DL。

根据驱动方案、面板设计方案等,数据驱动电路120可以位于但不限于面板110的仅一侧(例如,上侧、下侧、左侧或右侧)上,或在一些实施例中,数据驱动电路120可以位于但不限于面板110的两侧(例如,上侧和下侧、或左侧和右侧)上。

根据驱动方案、面板设计方案等,栅极驱动电路130可以位于但不限于面板110的仅一侧(例如,左侧、右侧、上侧或下侧)上,或在一些实例中,栅极驱动电路130可以位于但不限于显示面板110的两侧(例如,左侧和右侧、或上侧和下侧)上。

布置在显示面板110中的多个栅极线GL可以包括多个扫描线SCL和多个发光控制线EML等。多个扫描线SCL和多个发光控制线EML是用于将彼此不同类型的栅极信号(例如,扫描信号、发光控制信号)传递到彼此不同类型的晶体管(例如,扫描晶体管、发光控制晶体管)的栅极节点的线。

因此,栅极驱动电路130可以包括:多个扫描驱动器(图3中的GIP SCAN1、GIPSCAN2),所述多个扫描驱动器将扫描信号输出到多个扫描线SCL,扫描线SCL是一种类型的栅极线GL;以及多个发光控制驱动器(GIP EM1、GIP EM2),所述多个发光控制驱动器将发光控制信号输出到多个发光控制线EML,发光控制线EML是另一种类型的栅极线GL。

同时,根据本公开的实施例的显示设备100可以是诸如液晶显示器(LCD)的需要背光单元的非自发光显示器,或是诸如有机发光二极管(OLED)显示器、量子点显示器、微发光二极管(LED)显示器等的自发光显示器。

在根据本公开的实施例的显示设备100是OLED显示器的情况下,每个子像素SP可以包括OLED,其中OLED本身作为发光元件ED发光。在根据本公开的实施例的显示设备100是量子点显示器的情况下,每个子像素SP可以包括由量子点制成的发光元件ED,所述量子点是半导体晶体,其中半导体晶体本身发光。在根据本公开的实施例的显示设备100是微LED显示器的情况下,每个子像素SP可以包括微LED,其中微LED本身作为发光元件ED发光,并且所述微LED基于无机材料制成。

图2示出了根据本公开的一个实施例的施加到显示设备100的子像素SP的等效电路。

参考图2,在根据本公开的一个实施例的显示设备100是自发光显示器的情况下,每个子像素SP可以包括:发光元件ED,其中发光元件本身发光;两个或更多个晶体管(例如,驱动晶体管、扫描晶体管等),所述两个或更多个晶体管用于驱动发光元件ED;以及一个或更多个电容器(例如,存储电容器等)。

图2中的子像素SP的等效电路示出了子像素结构的示例,其中包括6个晶体管(T1~T6)和1个电容器Cst以用于驱动发光元件ED。图2的子像素SP被称为“6T(晶体管)1C(电容器)结构”。此外,图2所示的6T1C结构用作内部补偿使用的驱动电路,该电路能够补偿第二晶体管T2的阈值电压,以便将与数据信号DATA相对应的驱动电流准确地提供给发光元件ED。图2中的子像素SP的等效电路表示可能的电路的一个示例。因此,本公开的实施例不限于此,并且各种像素电路可以应用于显示设备100。

参考图2,为了驱动具有6T1C结构的子像素SP,多个栅极线GL可以布置在显示面板110中,例如,用于传递第一扫描信号SCAN1的多个第一扫描线SCL1、用于传递第二扫描信号SCAN2的多个第二扫描线SCL2、用于传递第一发光控制信号EM1的多个第一发光控制线EML1、和用于传递第二发光控制信号EM2的多个第二发光控制线EML2。

参考图2,每个子像素SP可以包括发光元件ED、第一到第六晶体管(T1~T6)和存储电容器Cst,并且包括四个节点(N1、N2、N3、N4)。

发光元件ED可以包括第一电极PE和第二电极CE,并且包括位于第一电极PE与第二电极CE之间的发光层EL。第一电极PE可以设置在每个子像素SP中,并且可以是被施加了每个子像素SP的唯一驱动电压的像素电极。第二电极CE可以为所有的子像素SP共同设置,并且可以是被施加了驱动所有的子像素SP所需的公共电压的公共电极。这里,公共电压可以是低电平电压VSS,例如接地电压等。第一电极PE可以是阳极电极(或阴极电极),并且第二电极CE可以是阴极电极(或阳极电极)。

例如,发光元件ED可以是有机发光二极管(OLED)显示器的有机发光二极管(OLED)、量子点显示器的量子点发光元件、微发光二极管(LED)显示器的微发光二极管(LED)等。

第四晶体管T4可以由第二发光控制信号EM2来控制,并且连接在用于传递驱动电压VDD的驱动电压线VDDL与第一节点N1之间。第四晶体管T4的导通可以使发光元件ED发光并且允许确定发光周期。

第三晶体管T3可以由第一扫描信号SCAN1来控制,并且连接在第一节点N1与第二节点N2之间。第二节点N2可以是第二晶体管T2的栅极节点。第三晶体管T2的导通可以使第二晶体管T2的阈值电压被采样。

第二晶体管T2可以由是其栅极节点的第二节点N2的电压来控制,并且电连接在第一节点N1与第三节点N3之间。在功能方面,第二晶体管T2可以是驱动晶体管。

第一晶体管T1可以由第二扫描信号SCAN2来控制,并且连接在数据线DL与第三节点N3之间。第一晶体管T1将数据信号VDATA提供给驱动晶体管的源极节点。

第五晶体管T5可以由第一发光控制信号EM1来控制,并且电连接在第四节点N4与第三节点N3之间。第四节点N4可以连接到发光元件ED的第一电极PE。当第五晶体管T5与第四晶体管T4一起导通时,发光元件ED可以发光。

第六晶体管T6可以由第一扫描信号SCAN1来控制,并且连接在用于传递初始化电压Vini的初始化电压线IVL与第四节点N4之间。第六晶体管T6的导通能够使初始化电压Vini被施加到连接到第四晶体管T4的发光元件ED的电极,从而使发光元件ED放电到初始化电压Vini。

存储电容器Cst可以连接在第二节点N2与第四节点N4之间。第二节点N2可以是作为驱动晶体管的第二晶体管T2的栅极节点,或是具有与第二晶体管T2的栅极节点相同的电状态的节点(电极图案或位置),并且第四节点N4可以是发光元件ED的第一电极PE,或是具有与发光元件ED的第一电极PE相同的电状态的节点(电极图案或位置)。存储电容器Cst可以将驱动晶体管的栅极电极中的电压维持在预定电平,使得驱动晶体管可以将恒定的驱动电流施加到发光元件ED。

存储电容器Cst可以是有意设计在晶体管外部的外部电容器,而不是内部电容器本身存在的寄生电容器(例如Cgs、Cgd)。

第一到第六晶体管(T1~T6)中的每一个可以是n型晶体管或p型晶体管。如果第一到第六晶体管(T1~T6)中的每一个是n型晶体管,用于导通第一到第六晶体管(T1~T6)中的每一个的栅极电压可以是高电平栅极电压,并且用于关断第一到第六晶体管(T1~T6)中的每一个的栅极电压可以是低电平栅极电压。在第一到第六晶体管(T1~T6)中的每一个是p型晶体管的情况下,用于导通第一到第六晶体管(T1~T6)中的每一个的栅极电压可以是低电平栅极电压,并且用于关断第一到第六晶体管(T1~T6)中的每一个的栅极电压可以是高电平栅极电压。在下文中,为了便于描述,基于n型晶体管进行讨论。

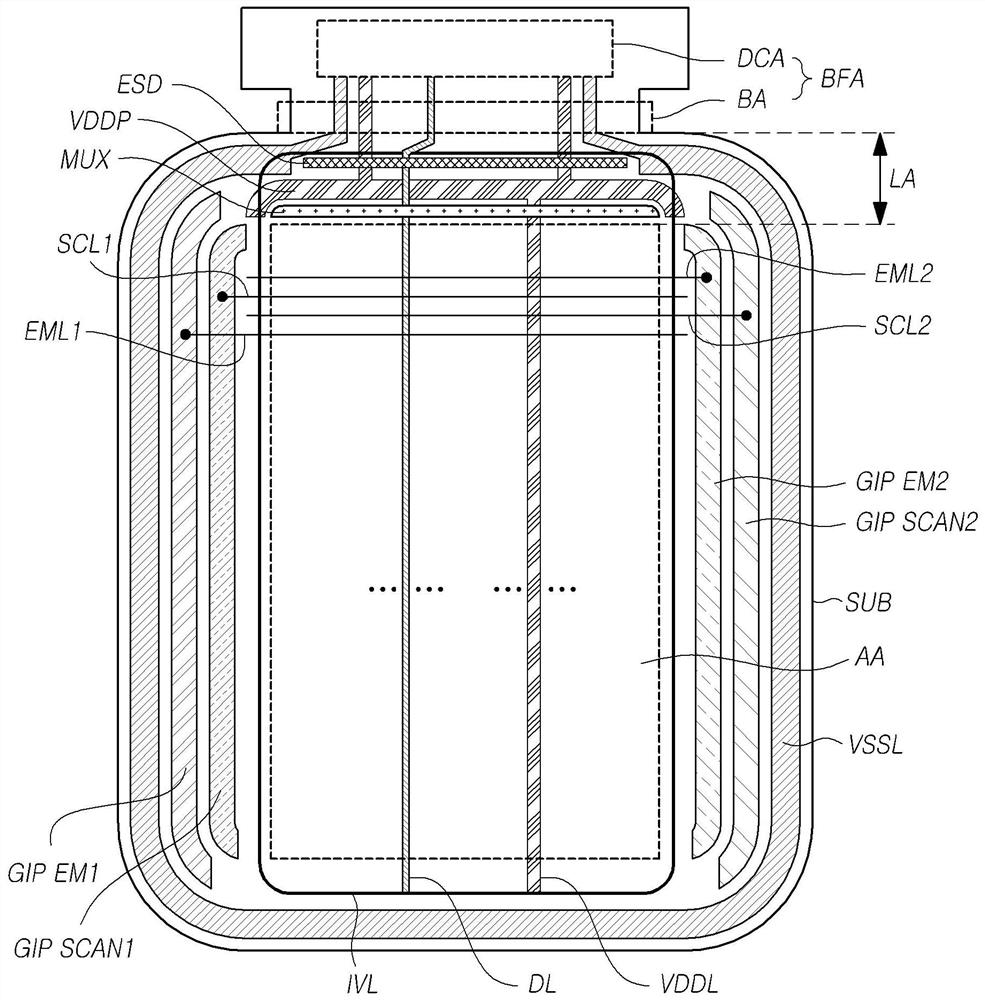

图3是示意性地示出了根据本公开的一个实施例的显示面板110的弯曲和接线结构的平面图。图4示出了根据本公开的一个实施例的显示面板110的弯曲和链接区域(BA和LA)和在与弯曲和链接区域相邻的区域中的弯曲和接线结构。

参考图3和图4,所有的线、所有的电极等形成在基板SUB之上。根据本公开的实施例的显示设备100中包括的基板SUB可以是可以弯曲的柔性基板。本文中,术语“弯曲”可以具有与“折叠”、“柔性”等相同的含义。参考图3和图4,基板SUB可以包括其中显示图像的有源区域AA和是有源区域AA外部的区域的非有源区域NA。多个子像素SP可以布置在有源区域AA中。

非有源区域NA可以包括:GIP区域GIPA,GIP类型的栅极驱动电路130(GIP SCAN1、GIP SCAN2、GIP EM1、GIP EM2)设置在所述GIP区域GIPA中;链接区域LA,数个类型的线穿过所述链接区域LA;折叠区域BFA,数据驱动电路120电连接到所述折叠区域BFA;等等。

例如,GIP区域GIPA可以位于有源区域AA的左边缘区域和/或右边缘区域外部的区域中。链接区域LA可以位于有源区域AA的上边缘区域(或下边缘区域)外部的区域中。折叠区域BFA可以是显示面板中比链接区域LA更外的边缘区域。印刷电路板可以与折叠区域BFA电连接。

如上所述,基板SUB可以包括可以弯曲和折叠的折叠区域BFA。当折叠区域BFA被折叠时,基板SUB可以位于未被折叠的一部分的下表面或底表面上。折叠区域BFA是非有源区域NA的一部分,并且可以包括:驱动电路区域DCA,数据驱动电路120与所述驱动电路区域DCA电连接,或数据驱动电路120位于所述驱动电路区域DCA中;以及弯曲区域BA,所述弯曲区域BA位于驱动电路区域DCA与有源区域AA之间,并且可以弯曲。

非有源区域NA的链接区域LA可以位于弯曲区域BA与有源区域AA之间。穿过链接区域LA的数个类型的信号线可以在穿过弯曲区域BA之后电连接到数据驱动电路120或印刷电路板,所述数据驱动电路120或印刷电路板位于驱动电路区域DCA中,或与驱动电路区域DCA连接。

参考图3和图4,用于将数据信号VDATA传递到多个子像素SP的多个数据线DL和用于将栅极信号传递到多个子像素的多个栅极线GL可以布置在基板SUB之上。

例如,可以在列方向上布置多个数据线DL,并且可以在行方向上布置多个栅极线GL。相反,可以在行方向上布置多个数据线DL,并且可以在列方向上布置多个栅极线GL。在下文中,为了便于描述,基于在列方向上布置多个数据线DL并且在行方向上布置多个栅极线GL的情况进行讨论。

由多个数据线DL的延伸而产生的或与相应数据线DL连接的多个数据链接线(DLL1~DLLn)可以在穿过链接区域LA和弯曲区域BA之后电连接到数据驱动电路120,所述数据驱动电路120与驱动电路区域DCA连接,或位于驱动电路区域DCA中。

在每个子像素SP具有如图2所示的6T1C结构的情况下,布置在显示面板110中的多个栅极线GL可以包括:多个第一扫描线SCL1,所述多个第一扫描线SCL1用于将第一扫描信号SCAN1传递到一个或多个子像素;多个第二扫描线SCL2,所述多个第二扫描线SCL2用于将第二扫描信号SCAN2传递到一个或多个子像素;多个第一发光控制线EML1,所述多个第一发光控制线EML1用于将第一发光控制信号EM1传递到一个或多个子像素;以及多个第二发光控制线EML2,所述多个第二发光控制线EML2用于将第二发光控制信号EM2传递到一个或多个子像素。

据此,栅极驱动电路130可以包括:多个第一扫描驱动器GIP SCAN1,所述多个第一扫描驱动器GIP SCAN1将相应的第一扫描信号SCAN1输出到多个第一扫描线SCL1;多个第二扫描驱动器GIP SCAN2,所述多个第二扫描驱动器GIP SCAN2将相应的第二扫描信号SCAN2输出到多个第二扫描线SCL2;多个第一发光控制驱动器GIP EM1,所述多个第一发光控制驱动器GIP EM1将相应的第一发光控制信号EM1输出到多个第一发光控制线EM1;以及多个第二发光控制驱动器GIP EM2,所述多个第二发光控制驱动器GIP EM2将相应的第二发光控制信号EM2输出到多个第二发光控制线EM2。即,多个第一扫描驱动器GIP SCAN1可以分别对应于多个第一扫描线SCL1;多个第二扫描驱动器GIP SCAN2可以分别对应于多个第二扫描线SCL2;多个第一发光控制驱动器GIP EM1可以分别对应于多个第一发光控制线EM1;并且多个第二发光控制驱动器GIP EM2可以分别对应于多个第二发光控制线EM2。

多个第一扫描驱动器GIP SCAN1、多个第二扫描驱动器GIP SCAN2、多个第一发光控制驱动器GIP EM1和多个第二发光控制驱动器GIP EM2可以以GIP类型来实施,并且可以设置在基板SUB的非有源区域NA中的GIP区域GIPA中。

多个第一扫描驱动器GIP SCAN1、多个第二扫描驱动器GIP SCAN2、多个第一发光控制驱动器GIP EM1和多个第二发光控制驱动器GIP EM2中的全部可以设置在有源区域AA的一个侧边缘区域外部的非有源区域NA的区域中,其位于非有源区域NA中。

在另一示例中,多个第一扫描驱动器GIP SCAN1、多个第二扫描驱动器GIP SCAN2、多个第一发光控制驱动器GIP EM1和多个第二发光控制驱动器GIP EM2中的一些可以设置在有源区域AA的左侧边缘区域外部的非有源区域NA的区域(或上侧边缘区域外部的非有源区域NA的区域)中,并且其中另一个可以设置在有源区域AA的右侧边缘区域外部的非有源区域NA的区域(或下侧边缘区域外部的非有源区域NA的区域)中。

例如,如图3所示,多个第一扫描驱动器GIP SCAN1和多个第一发光控制驱动器GIPEM1可以设置在位于有源区域AA的左侧边缘区域(或上侧边缘区域)外部的GIP区域GIPA中,并且多个第二扫描驱动器GIP SCAN2和多个第二发光控制驱动器GIP EM2可以设置在位于有源区域AA的右侧边缘区域(或下侧边缘区域)外部的GIP区域GIPA中。

参考图4,在m个第一扫描驱动器GIP SCAN1之中设置为最靠近链接区域LA和弯曲区域BA的第一扫描驱动器GIP SCAN1[1]以及在m个第一发光控制驱动器GIP EM1之中设置为最靠近链接区域LA和弯曲区域BA的第一发光控制驱动器GIP EM1[1]可以设置为彼此相邻。

同样地,在m个第一扫描驱动器GIP SCAN1之中设置为最远离链接区域LA和弯曲区域BA的第一扫描驱动器GIP SCAN1[m]和在m个第一发光控制驱动器GIP EM1之中设置为最远离链接区域LA和弯曲区域BA的第一发光控制驱动器GIP EM1[m]可以设置为彼此相邻。

为了便于描述,图4示出了位于有源区域AA的左侧边缘区域外部的GIP区域GIPA中的结构(GIP EM1、GIP SCAN1)。同样地,这种构造可以等同地施加到位于有源区域AA的右侧边缘区域外部的GIP区域GIPA中的结构(GIP EM2、GIP SCAN2)。

用于将数个类型的信号(CLK1、CLK2、VST、VGH、VGL等)传递到栅极驱动电路130的栅极驱动相关线(CL1、CL2、VSL、VGHL、VGLL等)可以穿过弯曲区域BA和链接区域LA,并且被布置成延伸到有源区域AA的左侧边缘区域或右侧边缘区域外部的区域。

例如,栅极驱动相关线(CL1、CL2、VSL、VGHL、VGLL等)可以包括:一个或多个高电平栅极电压线VGHL,所述一个或多个高电平栅极电压线VGH用于传递高电平栅极电压VGH;一个或多个低电平栅极电压线VGLL,所述一个或多个低电平栅极电压线VGLL用于传递低电平栅极电压VGL;多个时钟线(CL1、CL2等),所述多个时钟线用于传递多个时钟信号(CLK1、CLK2等);一个或多个起始线VSL,所述一个或多个起始线VSL用于传递一个或多个起始信号VST;等等。

根据图2的子像素结构,为了驱动一个或多个子像素SP,用于将驱动电压VDD传递到一个或多个子像素SP的多个驱动电压线VDDL、用于将初始化电压Vini传递到一个或多个子像素SP的多个初始化电压线IVL和用于将低电平电压VSS施加到每个子像素SP中的发光元件ED的第二电极CE的一个或多个低电平电压线VSSL还可以设置在基板SUB之上。

例如,多个驱动电压线VDDL和多个初始化电压线IVL可以布置在列方向上。

为了有效地将驱动电压VDD传递到多个驱动电压线VDDL,与多个驱动电压线VDDL整体形成或电连接到多个驱动电压线VDDL的驱动电压图案VDDP可以设置在链接区域LA中。

多个驱动电压线VDDL可以通过驱动电压图案VDDP穿过弯曲区域BA,并且电连接到设置在驱动电路区域DCA中或与驱动电路区域DCA连接的数据驱动电路120或印刷电路板。

多个初始化电压线IVL可以在有源区域AA中布置在行方向或列方向上。为了有效地传递初始化电压Vini,多个初始化电压线IVL可以位于非有源区域NA中,并且布置成包围有源区域AA的一个或多个边缘区域的全部或至少一部分。

多个初始化电压线IVL或多个初始化电压线IVL所连结到的至少一个线可以穿过弯曲区域BA,并且电连接到设置在驱动电路区域DCA中或与驱动电路区域DCA连接的数据驱动电路120或印刷电路板。为了有效地传递低电平电压VSS,一个或多个低电平电压线VSSL可以位于非有源区域NA中,并且布置成包围有源区域AA的边缘区域的全部或至少一部分。

此外,一个或多个低电平电压线VSSL可以穿过弯曲区域BA,并且电连接到设置在驱动电路区域DCA中或与驱动电路区域DCA连接的数据驱动电路120或印刷电路板。

根据本公开的一个实施例的显示设备100还可以包括用于在各种信号线中静电放电的静电放电电路ESD。静电放电电路ESD可以设置在链接区域LA中。

根据本公开的一个实施例的显示设备100还可以包括设置在非有源区域NA的链接区域LA中的数据分配电路MUX。

考虑到多个数据链接线(DLL1~DLLn)中的一个数据链接线,数据分配电路MUX可以将从布置在有源区域AA中的两个或更多个数据线DL中选择的一个数据线DL电连接到一个数据链接线。

据此,从数据驱动电路130输出的数据信号VDATA被供应到布置在非有源区域NA的链接区域LA中的多个数据链接线(DLL1~DLLn)。此外,由于数据分配电路MUX选择布置在有源区域AA中的多个数据线DL中的一些(例如,奇数编号的数据线组),并且将包括在所选择的数据线组中的数据线DL(n个数据线)电连接到多个数据链接线(DLL1~DLLn),因此,数据信号VDATA可以被输出到从多个数据线DL中选择的一些数据线组(例如,奇数编号的数据线组)。

此后,从数据驱动电路130输出的其他数据信号VDATA被供应到布置在非有源区域NA的链接区域LA中的多个数据链接线(DLL1~DLLn)。此外,由于数据分配电路MUX选择布置在有源区域AA中的多个数据线DL中的其他数据线(例如,偶数编号的数据线组),并且将包括在所选择的数据线组中的数据线DL(n个数据线)电连接到数据链接线(DLL1~DLLn),因此,数据信号VDATA可以被输出到从多个数据线DL中选择的其他数据线组(例如,偶数编号的数据线组)。

在这种情况下,可以在一个水平时间(1H)期间以时分方式驱动一些数据线组(例如,奇数编号的数据线组)和其他数据线组(例如,偶数编号的数据线组)。

上述的数据分配电路MUX被称为解复用器电路,并且在一些实例中,也被称为复用电路。

用于传递用于数据分配电路MUX的操作的控制信号(MUX_CON、B/R/G)的信号线可以在穿过弯曲区域BA之后设置在链接区域LA中。

在如上所述的显示面板110中,通过允许由柔性材料形成并且数据驱动电路120位于其中或与数据驱动电路120连接的基板SUB的部分(折叠区域BFA)被弯曲,基板SUB的对应部分可以被向后折叠。这种折叠部分(折叠区域BFA)是不能在其上显示图像的部分,并且该部分从显示设备100的前面不能看到。因此,通过利用如图3和图4中的弯曲结构和线布置结构,可以通过这种窄边框设计来显著减小显示设备100的边框尺寸,并且提供感觉到高美学满意度的设计。

图5示出了根据本公开的实施例的布置在显示面板110的弯曲区域BA中的信号线(BL1~BL4)中的异常。

参考图5,如上所述,各种信号线(BL1~BL4等)可以布置在弯曲区域BA中。穿过弯曲区域BA的信号线(BL1~BL4等)可以包括多个数据链接线(DLL1~DLLn)、高电平栅极电压线VGHL、低电平电压线VGLL、多个时钟线(CL1、CL2)、起始线VSL、驱动电压线VDDL、低电平电压线VSSL、初始化电压线IVL等。

参考图5,穿过弯曲区域BA的信号线(BL1~BL4等)可以形成为锯齿形图案以减少断裂。然而,当弯曲区域被弯曲时,穿过弯曲区域BA的一个或多个信号线(BL1~BL4等)可能会断裂(处于电开路状态)或与相邻的信号线短路。

在这种情况下,由于不能通过断裂(处于电开路状态)或短路的信号线(图5中的BL1)准确地传递信号,因此,由于驱动显示设备中的问题而可能无法正确显示图像,从而导致图像质量大幅劣化。

为了解决这种问题,在下文中,在穿过弯曲区域BA的一个或多个信号线中发生问题(例如,断裂、短路等)的状况下,将讨论用于检测这种问题的方法和装置。

在这种情况下,为了便于描述和易于理解,将基于穿过弯曲区域BA的数个类型的信号线之中的时钟线(CL1、CL2)和栅极驱动相关线的起始线VSL来进行讨论。图6示出了根据本公开的一个实施例的用于感测布置在显示面板110的弯曲区域BA中的信号线中异常的存在与否的传感器电路610和确定电路620。图7是示出了根据本公开的一个实施例的传感器电路610的感测操作的驱动时序图。图8示出了根据本公开的一个实施例的在执行传感器电路610的感测操作时,当第一信号线CL1处于正常状态时的传感器电路610的感测操作。

图9示出了根据本公开的一个实施例的在执行传感器电路610的感测操作时,当第一信号线CL1具有断裂时的传感器电路610的感测操作。此外,图10示出了根据本公开的一个实施例的在执行传感器电路610的感测操作时,在第一信号线CL1处于正常状态的状况下和在第一信号线CL1具有断裂的状况下的读出信号SEN,所述读出信号SEN由确定电路620基于传感器电路610的感测而产生。

在图6到图10中,为了便于描述和易于理解,基于穿过弯曲区域BA的3个信号线(CL1、CL2、VSL)来进行讨论。图6所示的传感器电路610包括用于感测穿过弯曲区域BA的3个信号线(CL1、CL2、VSL)中异常的存在与否。此后,将基于3个信号线(CL1、CL2、VSL)中的第一信号线CL1来进行讨论。与第一信号线CL1相关的技术规范可以等同地施加到其他信号线。

参考图6,根据本公开的实施例的显示设备100可以包括传感器电路610和确定电路620。传感器电路610和确定电路620可以通过读出线ROL彼此连接。

参考图6,传感器电路610设置在链接区域LA中,所述链接区域LA在弯曲区域BA与有源区域AA之间位于非有源区域NA中,并且传感器电路610可以感测在弯曲区域BA的第一信号线CL1中异常的存在与否。

参考图6,传感器电路610可以包括:感测参考信号线SRSL,所述感测参考信号线SRSL用于传递感测参考信号SRS;读出线ROL,所述读出线ROL用于将读出信号ROS传递到确定电路620;第一感测晶体管SENT1,所述第一感测晶体管SENT1包括栅极节点,所述栅极节点电连接到第一信号线CL1;漏极节点或源极节点,所述漏极节点或源极节点连接到感测参考信号线SRSL;以及源极节点或漏极节点,所述源极节点或漏极节点连接到读出线,等等。

确定电路620可以电连接到读出线ROL、通过读出线ROL接收读出信号ROS、并且基于读出信号ROS来确定在第一信号线CL1中异常的存在与否。

当确定第一信号线CL1处于异常状态时,确定电路620可以控制第一信号线CL1的标识信息或位置信息、或由所述确定产生的信息,以将其存储在存储器中或显示在屏幕上。

为此,显示设备100可以包括存储器,其中预先存储第一信号线的标识信息、位置信息和/或布置在显示面板110中的信号线上的类似信息。

参考图7,在弯曲区域BA的整个感测周期Tsen期间,感测参考信号SRS具有高电平电压HV。在未包括在弯曲区域BA的整个感测周期Tsen中的周期(例如,显示驱动周期)期间,感测参考信号SRS具有低电平电压LV。

在弯曲区域BA的整个感测周期Tsen期间,高电平电压HV被顺序地供应到信号线(CL1、CL2、VSL)以检查其中异常的存在与否。即,在弯曲区域BA的整个感测周期Tsen期间,感测周期(T1、T2、T3)被顺序地分配给相应的信号线(CL1、CL2、VSL)以检查异常的存在与否。图7示出了在感测周期(T1、T2、T3)之间存在空白周期。但是,在理想信号的情况下,可以忽略或消除这种空白周期。

在用于感测第一信号线CL1中异常的存在与否的第一感测周期T1期间,高电平电压HV被施加到第一信号线CL1,而低电平电压LV被施加到剩余的信号线(CL2、VSL)。

在用于感测第二信号线CL2中异常的存在与否的第二感测周期T2期间,高电平电压HV被施加到第二信号线CL2,而低电平电压LV被施加到剩余的信号线(CL1、VSL)。

在用于感测第三信号线VSL中异常的存在与否的第三感测周期T3期间,高电平电压HV被施加到第三信号线VSL,而低电平电压LV被施加到剩余的信号线(CL1、CL2)。

参考图7,在用于在弯曲区域BA的整个感测周期Tsen内感测第一信号线CL1中异常的存在与否的第一感测周期T1期间,具有用于导通第一感测晶体管SENT1的电压的导通电平的第一信号CLK1可以被施加到第一信号线CL1,并且具有高电平电压HV的感测参考信号SRS可以被施加到感测参考信号线SRSL。

这里,由于假设第一感测晶体管SENT1是n型晶体管,所以第一感测晶体管SENT1的电压的导通电平是高电平电压HV。如果第一感测晶体管SENT1是p型晶体管,第一感测晶体管SENT1的电压的导通电平可以是低电平电压LV。

参考图6,传感器电路610可以包括第二感测晶体管SENT2,所述第二感测晶体管SENT2包括:栅极节点,所述栅极节点连接到第二信号线CL2;漏极节点或源极节点,所述漏极节点或源极节点连接到感测参考信号线SRSL;以及源极节点或漏极节点,所述源极节点或漏极节点连接到读出线ROL。

此外,传感器电路610可以包括第三感测晶体管SENT3,所述第三感测晶体管SENT3包括:栅极节点,所述栅极节点连接到起始线VSL;漏极节点或源极节点,所述漏极节点或源极节点连接到感测参考信号线SRSL;以及源极节点或漏极节点,所述源极节点或漏极节点连接到读出线ROL。

第一到第三晶体管(SENT1、SENT2、SENT3)的相应漏极节点或源极节点可以共同地连接到感测参考信号线SRSL。此外,相应的第一到第三晶体管(SENT1、SENT2、SENT3)的源极节点或漏极节点可以共同地连接到读出线ROL。此外,第一到第三晶体管(SENT1、SENT2、SENT3)的相应栅极节点可以连接到需要检查异常的存在与否的信号线(CL1、CL2、VSL)。

例如,第一信号线CL1可以是用于将第一时钟信号CLK1传递到栅极驱动电路130的第一时钟线;第二信号线CL2可以是用于将第二时钟信号CLK2传递到栅极驱动电路130的第二时钟线;并且第三信号线VSL可以是用于将起始信号VST传递到栅极驱动电路130的起始线。

如上所述,用于感测第一信号线CL1中异常的存在与否的第一感测周期T1、用于感测第二信号线CL2中异常的存在与否的第二感测周期T2和用于感测第三信号线VSL中异常的存在与否的第三感测周期T3可以在彼此不同的时序处进行分配,并且可以不彼此重叠。

在第一感测周期Tl期间,具有第一感测晶体管SENT1的电压HV的导通电平的第一信号CLK1可以被施加到第一信号线CL1;具有用于关断第二感测晶体管SENT2的电压的关断电平的第二信号CLK2可以被施加到第二信号线CL2;具有用于关断第三感测晶体管SENT3的电压的关断电平的第三信号VST可以被施加到第三信号线VSL;并且具有高电平电压HV的感测参考信号SRS可以被施加到感测参考信号线SRSL。

在第二感测周期T2期间,具有第一感测晶体管SENT1的电压的关断电平的第一信号CLK1可以被施加到第一信号线CL1,具有第二感测晶体管SENT2的电压的导通电平的第二信号CLK2可以被施加到第二信号线CL2,具有第三感测晶体管SENT3的电压的关断电平的第三信号VST可以被施加到第三信号线VSL,并且具有高电平电压HV的感测参考信号SRS可以被施加到感测参考信号线SRSL。

在第三感测周期T3期间,具有第一感测晶体管SENT1的电压的关断电平的第一信号CLK1可以被施加到第一信号线CL1,具有第二感测晶体管SENT2的电压的关断电平的第二信号CLK2可以被施加到第二信号线CL2,具有第三感测晶体管SENT3的电压的导通电平的第三信号VST可以被施加到第三信号线VSL,并且具有高电平电压HV的感测参考信号SRS可以被施加到感测参考信号线SRSL。

图8和图9示出了在用于感测第一信号线CL1中异常的存在与否的第一感测周期T1期间的驱动。

图8示出了第一信号线CL1处于正常状态(情况1)的驱动。图9示出了第一信号线CL1处于异常状态(例如,断裂等)(情况2)的驱动。图10是示出了在两种情况(情况1和情况2)下由确定电路620基于传感器电路610检测到的读出信号ROS的时序图。

参考图8到图10,在用于感测第一信号线CL1中异常的存在与否的第一感测周期T1期间,当具有第一感测晶体管SENT1的电压的导通电平的第一信号CLK1被施加到第一信号线CL1时,取决于第一信号线CL1中是否存在断裂,第一感测晶体管SENT1可以被导通或关断。

参考图8,当第一信号线CL1处于正常状态(情况1)时,具有电压的导通电平的第一信号CLK1通过第一信号线CL1正常地施加到第一感测晶体管SENT1的栅极节点。据此,第一感测晶体管SENT1被导通。据此,第一感测晶体管SENT1可以将具有高电平电压HV的感测参考信号SRS传输到读出线ROL。

参考图10,确定电路620可以通过读出线ROL来读取具有高电平电压HV的感测参考信号SRS。当读出信号ROS对应于感测参考信号SRS时,确定电路620可以确定第一信号线CL1处于正常状态。在这种情况下,感测参考信号SRS和读出信号ROS具有高电平电压HV。

参考图9,当第一信号线CL1在弯曲区域BA中具有断裂时(情况2),即使具有电压的导通电平的第一信号CLK1被施加到第一信号线CL1,由于第一信号CLK1中的断裂,具有电压的导通电平的第一信号CLK1不能被正常地施加到第一感测晶体管SENT1的栅极节点。结果,第一感测晶体管SENT1处于关断状态。因此,第一感测晶体管SENT1可以不将具有高电平电压HV的感测参考信号SRS传输到读出线ROL。

参考图10,在第一感测周期T1期间,确定电路620不能通过读出线ROL读取具有高电平电压HV的感测参考信号SRS。当读出信号ROS不对应于感测参考信号SRS时,确定电路620可以确定第一信号线CL1处于异常状态(例如,断裂、短路等。)在这种情况下,感测参考信号SRS可以具有高电平电压HV,并且读出信号ROS可以处于非高电平状态,例如,具有低电平电压LV。

传感器电路610还可以包括:第一控制晶体管M1,所述第一控制晶体管M1由感测参考信号SRS控制,并且与低电平栅极电压线VGLL和读出线ROL连接;第二控制晶体管M2,所述第二控制晶体管M2的导通和关断由通过高电平栅极电压线VGHL传递的信号来控制;等等。读出线ROL可以布置成延伸到有源区域AA的侧边缘区域外部的区域(例如,GIP区域GIPA)。

读出线ROL可以包括位于链接区域LA中的第一部分(PART1)和位于有源区域AA的侧边缘区域外部的区域中的第二部分(PART2)。第二控制晶体管M2可以串联连接到读出线ROL,并且可以设置成与有源区域AA的侧边缘区域相邻并且在链接区域LA中。因此,在读出线ROL中,取决于第二控制晶体管M2的导通或关断,位于连接区域LA中的第一部分(PART1)和位于有源区域AA的侧边缘区域外部的区域中的第二部分(PART2)可以彼此连接或断开。

在读出线ROL中,位于链接区域LA中的第一部分(PART1)的端部NR1可以连接到第二控制晶体管M2的漏极节点或源极节点。此外,在读出线ROL中,位于有源区域AA的侧边缘区域外部的区域中的第二部分(PART2)的一个端部NR2可以连接到第二控制晶体管M2的未与读出线ROL的端部NR1连接的源极节点或漏极节点。

栅极驱动电路130设置在基板SUB之上,并且可以包括以面板中栅极(GIP)类型形成的多个栅极驱动器(GIP SCAN1、GIP SCAN2、GIP EM1、GIP EM2)。

在读出线ROL中,位于有源区域AA的侧边缘区域外部的区域(GIP区域GIPA)中的第二部分(PART2)的另一端部NE可以电连接到在多个栅极驱动器(GIP SCAN1、GIP SCAN2、GIPEM1、GIP EM2)之中设置为最远离弯曲区域BA的最后的栅极驱动器(GIP SCAN1[m]、GIPSCAN2[m]、GIP EM1[m]、GIP EM2[m])的输出端子。在显示驱动时间,随着第二控制晶体管M2导通,从而从最后的栅极驱动器输出的输出值通过读出线ROL被提供给确定电路620,栅极驱动器的缺陷可以通过确定最后的栅极驱动器的输出值中异常的存在与否来识别。由于通过接收前一栅极驱动器的输出信号来操作栅极驱动器,因此可以通过识别最后的栅极驱动器的输出信号来识别栅极驱动器中异常的存在与否。

考虑到第一和第二控制晶体管(M1、M2),在用于感测第一信号线CL1中异常的存在与否的第一感测周期T1期间,第一控制晶体管M1可以通过具有高电平电压HV的感测参考信号SRS来导通,并且将通过低电平栅极电压线VGLL传递的低电平栅极电压VGL传输到读出线ROL。

由于用于感测第一信号线CLl中异常的存在与否的第一感测周期Tl被初始化,施加到高电平栅极电压线VGHL的高电平栅极电压VGH从高电平电压HV变为低电平电压LV,并且因此,第二控制晶体管M2可以被关断。

这样,在包括第一感测周期Tl的整个感测周期Tsen期间,第二控制晶体管M2处于关断状态。因此,在读出线ROL中,位于链接区域LA中的第一部分(PART1)和位于有源区域AA的侧边缘区域外部的区域中的第二部分(PART2)彼此电断开。结果,在读出线ROL中,位于有源区域AA的侧边缘区域外部的区域中的第二部分(PART2)不影响感测。

此外,在包括第一感测周期T1的整个感测周期Tsen期间,第一控制晶体管M1处于导通状态。因此,常常通过第一控制晶体管M1将低电平栅极电压VGL施加到读出线ROL。因此,可以防止读出线ROL电浮动,并且使传感器电路610稳定地操作。然而,由于第一控制晶体管M1在感测周期Tsen期间连续导通,因此在感测感测参考信号SRS时负载可能增加;因此,传感器电路610可以省略第一控制晶体管M1。

参考图10,考虑到第一和第二控制晶体管(Ml、M2),当读出信号ROS对应于具有高电平电压HV的感测参考信号SRS时,确定电路620确定第一信号线CL1处于正常状态。

此外,当读出信号ROS对应于低电平栅极电压VGL时,确定电路620确定第一信号线CL1中存在断裂。在另一情况下,当第一信号线CL1短路时,第一信号线CL1中的负载增加;因此,低电平栅极电压VGL上升。考虑到这些操作,确定电路620可以识别出第一信号线CL1中的异常是断裂而不是短路。

在采用传感器电路610和确定电路620的情况下,可以识别出第一信号线CL1中的断裂存在于弯曲区域BA中,即,断裂的位置。这是因为设置传感器电路610的位置是紧邻弯曲区域BA的点。

由于从与弯曲区域BA相邻的点输入施加到感测晶体管(SENT1、SENT2、SENT3)的栅极节点的信号,并且还从与弯曲区域BA相邻的点输入施加到感测晶体管(SENT1、SENT2、SENT3)的漏极节点或源极节点的感测参考信号SRS,因此可以识别出在位于弯曲区域BA中的信号线中异常的存在与否。图11示出了根据本公开的一个实施例的在显示模式下驱动显示设备100时包括在传感器电路610中的感测参考信号SRS、第一控制晶体管M1和第二控制晶体管M2的状态。

图12示出了根据本公开的一个实施例的在显示模式下驱动显示设备100时传感器电路610的状态。

参考图11和图12,在用于显示图像的显示驱动周期期间,第一控制晶体管M1可以处于导通状态,并且第二控制晶体管M2可以处于关断状态。通过导通的第二晶体管M2,将位于链接区域中的部分(PART1)和位于读出线ROL的有源区域AA的侧边缘区域外部的部分(PART2)电连接。

此外,在用于显示图像的显示驱动时间,具有低电平电压的感测参考信号SRS可以被施加到感测参考信号线SRSL。

在第一信号线CL1是用于将时钟信号传递到栅极驱动电路130的时钟线的情况下,在一帧时间内的预确定时间(例如,扫描时序,此时,时钟信号是高电平电压),第一感测晶体管SENT1可以被导通;然而,由于感测参考信号SRS在显示驱动时间具有低电平电压LV,因此低电平电压LV被连续地提供给读出线ROL。

图13是示出了根据本公开的一个实施例的在显示设备100中设置了传感器电路610的部分的平面图。在下文中,将简短地进行或不重复给出对与图4中的构造相同的构造的讨论。

参考图13,一个或多个传感器电路(610)和一个或多个静电放电电路ESD可以设置在链接区域LA中。第一信号线CL1、读出线ROL和感测参考信号线SRSL可以连接到静电放电电路ESD。通过这样,通过防止在处理期间可能发生的静电、可能暂时地意外地产生的火花电压、等等,可以保护连接到这些线的栅极驱动电路130、确定电路620、子像素SP等。

参考图13,感测参考信号线SRSL可以仅连接到传感器电路610和静电放电电路ESD,并且可以不连接到GIP区域GIPA。

参考图13,用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一扫描驱动器(GIP SCAN1[1]~GIP SCAN1[m])中的所有或一个或多个的第一到第三信号线(CL1、CL2、VSL)以及读出线ROL在穿过弯曲区域BA和链接区域LA之后,被向上布置到GIP区域GIPA。

用于感测第一到第三信号线(CL1、CL2、VSL)中异常的存在与否的传感器电路610可以设置在链接区域LA中,所述第一到第三信号线(CL1、CL2、VSL)用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一扫描驱动器(GIP SCAN1[1]~GIP SCAN1[m])中的所有或一个或多个。传感器电路610可以连接到高电平栅极电压线VGHL和低电平栅极电压线VGLL。

用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一扫描驱动器(GIP SCAN1[1]~GIP SCAN1[m])中的所有或一个或多个的第一到第三信号线(CL1、CL2、VSL)在穿过传感器电路610,并且然后穿过静电放电电路ESD之后,连接到布置在GIP区域GIPA中的m个第一扫描驱动器(GIP SCAN1[1]~GIP SCAN1[m])中的所有或一个或多个。

读出线ROL可以在穿过传感器电路610,并且然后穿过静电放电电路ESD之后,连接到布置在GIP区域的m个第一扫描驱动器(GIP SCAN1[1]、……、GIP SCAN1[m])中的最后的扫描驱动器(GIP SCAN1[m])的输出端子。由此,传感器电路610可以在最后的扫描驱动器(GIP SCAN1[m])的输出端子处输出作为读出信号ROS的信号。确定电路620可以基于是感测信号SEN的读出信号ROS来检查在m个第一扫描驱动器(GIP SCAN1[1]、……、GIP SCAN1[m])中的第一扫描信号SCAN1是否被正常输出。

参考图13,用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一发光控制驱动器(GIP EM1[GIP EM1]、……、GIP EM1[m])中的所有或一个或多个的第一到第三信号线(CL1、CL2、VSL)以及读出线ROL在穿过弯曲区域BA和链接区域LA之后,被向上布置到GIP区域GIPA。

用于感测第一到第三信号线(CL1、CL2、VSL)中异常的存在与否的传感器电路610可以设置在链接区域LA中,所述第一到第三信号线(CL1、CL2、VSL)用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一发光控制驱动器(GIP EM1[1]、……、GIP EM1[m])中的所有或一个或多个。传感器电路610可以连接到高电平栅极电压线VGHL和低电平栅极电压线VGLL。

用于将第一到第三信号(CLK1、CLK2、VST)传递到m个第一发光控制驱动器(GIPEM1[1]、……、GIP EM1[m])中的所有或一个或多个的第一到第三信号线(CL1、CL2、VSL)在穿过传感器电路610,并且然后穿过静电放电电路ESD之后,连接到布置在GIP区域GIPA中的m个第一发光控制驱动器(GIP EM1[1]、……、GIP EM1[m])中的所有或一个或多个。

读出线ROL可以在穿过传感器电路610,并且然后穿过静电放电电路ESD之后,连接到布置在GIP区域中的m个第一发光控制驱动器(GIP EM1[1]、……、GIP EM1[m])中的最后的发光控制驱动器(GIP EM1[m])的输出端子。由此,传感器电路610可以在最后的发光控制驱动器(GIP EM1[m])的输出端子处输出作为读出信号ROS的信号。确定电路620可以基于是感测信号SEN的读出信号ROS来检查在m个第一发光控制驱动器(GIP EM1[1]、……、GIP EM1[m])中的第一发光控制信号EM1是否被正常输出。

图14示出根据本公开的一个实施例的用于感测布置在显示面板100的弯曲区域BA中的信号线中异常的存在与否的传感器电路640和确定电路620。图15是示出根据本公开的一个实施例的传感器电路640的感测操作的驱动时序图。由于在除了图14中所示的传感器电路640之外的配置中,图6中表示的配置可以同样地适用,因此,为了描述的方便,将简要地给出或省略重复的描述。

参考图14,传感器电路640可以包括:用于传递感测参考信号SRS的感测参考信号线SRSL、用于将读出信号ROS传递至确定电路620的读出线ROL、第一感测晶体管SENT1、第二感测晶体管SENT2、第三感测晶体管SENT、控制感测晶体管MS。

第一感测晶体管SENT1的栅极节点和第一感测晶体管SENT1的漏极或源极节点连接至第一信号线CL1,并且其余的源极或漏极节点连接至控制感测晶体管MS。第一感测晶体管SENT1可以感测第一信号线CL1中异常的存在与否。

第二感测晶体管SENT2的栅极节点和第二感测晶体管SENT2的漏极或源极节点连接至第二信号线CL2,并且其余的源极或漏极节点连接至控制感测晶体管MS。第二感测晶体管SENT2可以感测第二信号线CL2中异常的存在与否。

第三感测晶体管SENT3的栅极节点和第三感测晶体管SENT3的漏极或源极节点连接到起始线VSL,并且其余的源极或漏极节点连接到控制感测晶体管MS。第三感测晶体管SENT3可以感测起始线VSL中异常的存在与否。

控制感测晶体管MS的栅极节点连接至感测参考信号线SRSL,并且其源极或漏极节点连接至第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3,并且其剩余的漏极或源极节点通过读出线ROL连接到确定电路620。第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3通过控制感测晶体管MS共同连接到读出线ROL。

第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3电连接到信号线、感测参考信号线和读出线,并且可以感测信号线中异常的存在与否。

连接到读出线ROL的确定电路620可以从读出线ROL接收读出信号ROS,并基于读出信号ROS确定第一信号线CL1、第二信号线CL2或起始线VSL中异常的存在与否。

参考图15,感测参考信号SRS在弯曲区域BA的整个感测周期Tsen期间具有高电平电压HV,并且在除了整个感测周期Tsen之外的周期期间具有低电平电压LV。

在弯曲区域BA的整个感测周期Tsen期间,高电平电压HV顺序地提供给需要检查异常的存在与否的信号线(CL1、CL2、VSL)。因此,可以顺序地分配用于检查相应信号线(CL1、CL2、VSL)的相应感测周期(T1、T2、T3)。

在用于感测第一信号线CL1中异常的存在与否的第一感测周期Tl期间,高电平电压HV被施加到第一信号线CL1,而低电平电压LV被施加到其余的信号线(CL2、VSL)。

在用于感测第二信号线CL2中异常的存在与否的第二感测周期T2期间,高电平电压HV被施加到第二信号线CL2,而低电平电压LV被施加到其余的信号线(CL1、VSL)。

在用于感测起始线VSL中异常的存在与否的第三感测周期T3期间,高电平电压HV被施加至起始线VSL,而低电平电压LV被施加至其余的信号线(CL1、CL2)。

在第一感测周期Tl期间,由于第一信号CLK1具有高电平电压HV,第一感测晶体管SENT1变为导通。此外,由于感测参考信号SRS也具有高电平电压HV,控制感测晶体管MS也变为导通。

当第一信号线CL1处于正常状态时,施加到第一信号线CL1的高电平电压HV通过第一感测晶体管SENT1和控制感测晶体管MS被提供给读出线ROL。在这种情况下,确定电路620可以通过读出线ROL读出高电平电压HV,并且当识别出读出信号ROS对应于感测参考信号SRS时,确定第一信号线CL1处于正常状态。

在弯曲区域BA中的第一信号线CL1中存在断裂的情况下,即使当高电平电压HV被施加到第一信号线CL1时,由于第一信号线CL1中的断裂,高电平电压HV的第一信号CLK1也不能被正常施加到第一感测晶体管SENT1的栅极节点。据此,第一感测晶体管SENT1不能导通。尽管控制感测晶体管MS处于导通状态,但是由于第一感测晶体管SENT1处于关断状态,所以控制感测晶体管MS无法将高电平电压HV传递至读出线ROL。在这种情况下,由于确定电路620在第一感测周期T1期间不能通过读出线ROL读出高电平电压HV,所以确定电路620可以识别出读出信号ROS不对应于感测参考信号SRS,并确定第一信号线CL1处于异常状态。

在第二感测周期T2和第三感测周期T3期间,第二感测晶体管SENT2和第三感测晶体管SENT3的相应操作、以及用于感测信号线(CL2、VSL)处于正常还是异常状态的相应操作基本上等同于在第一感测周期T1中的操作;因此,为了描述的方便,将省略相关的讨论,在这种情况下,应当注意,第一感测晶体管SENT1可以改变为第二感测晶体管SENT2和第三感测晶体管SENT3,并且第一信号线CL1可以改变为第二信号线CL2和起始线VSL,并且第一信号CLK1可以改变为第二信号CLK2和起始信号VST。

使用传感器电路640和确定电路620,可以识别出信号线(CL1、CL2、VSL)中存在断裂或短路的位置是弯曲区域BA。这是因为设置传感器电路640的位置是穿过弯曲区域BA的与弯曲区域BA相邻的位置。

具体地,由于施加到感测晶体管(SENT1、SENT2、SENT3)的栅极节点的信号被施加到与弯曲区域BA相邻的位置,因此可以识别出在弯曲区域BA中信号线中异常的存在与否。

同时,在根据本公开的一个实施例的显示设备100中的显示驱动周期期间,由于感测参考信号SRS具有低电平电压LV,所以控制感测晶体管MS保持关断状态。因此,由于控制感测晶体管MS使信号线(CL1、CL2、VSL)不被电连接到读出线ROL,因此可以将相关的信号(CLK1、CLK2、VST)正常地输入到栅极驱动电路130。

图16示出根据本公开的一个实施例的用于感测布置在显示面板110的弯曲区域BA中的信号线中异常的存在与否的传感器电路660和确定电路620。由于图16中所示的用于传感器电路660的感测操作的驱动时序图基本上等同于图15的图示,参考图15进行相关讨论。由于图16中所示的传感器电路660是图14中所示的传感器电路640的变型,为了描述的方便,将简要进行或省略关于相关联的重复操作的讨论。

参考图16,传感器电路660可以包括:用于传递感测参考信号SRS的感测参考信号线SRSL、用于将读出信号ROS传递到确定电路620的读出线ROL、第一感测晶体管SENT1、第二感测晶体管SENT2、第三感测晶体管SENT3、控制感测晶体管MS。这里,尽管包括在传感器电路660中的晶体管被表示为n型晶体管,但是,本公开的实施例不限于此。

第一感测晶体管SENT1的栅极节点和第一感测晶体管SENT1的漏极或源极节点连接到第一信号线CL1,并且其余的源极或漏极节点连接到控制感测晶体管MS。第一感测晶体管SENT1可以感测第一信号线CL1中异常的存在与否。

第二感测晶体管SENT2的栅极节点和第二感测晶体管SENT2的漏极或源极节点连接到第二信号线CL2,并且其余的源极或漏极节点连接到控制感测晶体管MS。第二感测晶体管SENT2可以感测第二信号线CL2中异常的存在与否。

第三感测晶体管SENT3的栅极节点连接至感测参考信号线SRSL,并且第三感测晶体管SENT3的漏极或源极节点连接至起始线VSL,而其余的源极或漏极节点连接到控制感测晶体管MS。第三感测晶体管SENT3可以感测起始线VSL中异常的存在与否。由于第三感测晶体管SENT3的栅极节点连接至感测参考信号线SRSL,因此第三感测晶体管SENT3可以通过在感测周期Tsen期间维持导通状态,在除了用于感测起始线VSL中异常的存在与否的周期之外的周期期间,稳定地向读出线ROL提供低电平电压LV。因此,当除了由第三感测晶体管SENT3感测的信号线之外的其余信号线中的至少一个中存在异常时,确定电路620可以准确地确定信号线中异常的存在与否。当提供给信号线的信号具有彼此重叠的脉冲时,具体而言,当第一信号CLK1或第二信号CLK2在与起始信号VST重叠的同时具有高电平电压HV时,通过允许第三感测晶体管SENT3的栅极节点连接至感测参考信号线SRSL而不是起始线VSL,可以防止在提供给控制感测晶体管MS的信号之间发生干扰。第三感测晶体管SENT3可以被称为参考晶体管。

控制感测晶体管MS的栅极节点连接至感测参考信号线SRSL,并且其源极或漏极节点连接至第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3,其余的漏极或源极节点通过读出线ROL连接到确定电路620。第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3通过控制感测晶体管MS共同连接到读出线ROL。

第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3电连接到信号线、感测参考信号线和读出线,并且可以感测信号线中异常的存在与否。

连接到读出线ROL的确定电路620可以从读出线ROL接收读出信号ROS,并且基于读出信号ROS确定在第一信号线CL1、第二信号线CL2或起始线VSL中异常的存在与否。

参考图15,在弯曲区域BA的整个感测周期Tsen期间,感测参考信号SRS具有高电平电压HV。在除了弯曲区域BA的整个感测周期Tsen之外的周期期间,感测参考信号SRS具有低电平电压LV。

在弯曲区域BA的整个感测周期Tsen期间,高电平电压HV顺序地提供给需要检查异常的存在与否的信号线(CL1、CL2、VSL)。因此,可以顺序地分配用于检查相应信号线(CL1、CL2、VSL)的相应感测周期(T1、T2、T3)。

在用于感测第一信号线CL1中异常的存在与否的第一感测周期Tl期间,高电平电压HV被施加到第一信号线CL1,而低电平电压LV被施加到其余的信号线(CL2、VSL)。

在用于感测第二信号线CL2中异常的存在与否的第二感测周期T2期间,高电平电压HV被施加到第二信号线CL2,而低电平电压LV被施加到其余的信号线(CL1、VSL)。

在用于感测起始线VSL中异常的存在与否的第三感测周期T3期间,高电平电压HV被施加到起始线VSL,而低电平电压LV被施加到其余的信号线(CL1、CL2)。

在第一感测周期T1期间,由于第一信号CLK1具有高电平电压HV,第一感测晶体管SENT1变为导通。此外,由于感测参考信号SRS也具有高电平电压HV,控制感测晶体管MS和第三感测晶体管SENT3也变为导通。

当第一信号线CL1处于正常状态时,施加到第一信号线CL1的高电平电压HV通过第一感测晶体管SENT1和控制感测晶体管MS被提供给读出线ROL。在这种情况下,确定电路620可以通过读出线ROL读出高电平电压HV,并且当识别出读出信号ROS对应于感测参考信号SRS时,可以确定出第一信号线CL1处于正常状态。

在弯曲区域BA中的第一信号线CL1中存在断裂的情况下,即使当高电平电压HV被施加到第一信号线CL1时,由于第一信号线CL1中的断裂,高电平电压HV的第一信号CLK1也不能被正常施加到第一感测晶体管SENT1的栅极节点。据此,第一感测晶体管SENT1处于关断状态。尽管控制感测晶体管MS处于导通状态,由于第一感测晶体管SENT1处于关断状态,所以控制感测晶体管MS无法将高电平电压HV传递至读出线ROL。在这种情况下,由于第三感测晶体管SENT3处于导通状态,因此通过控制感测晶体管MS将低电平电压LV提供给读出线ROL。因此,确定电路620可以在第一感测周期T1期间通过读出线ROL读出低电平电压LV,识别出读出信号ROS与感测参考信号SRS不对应,并确定第一信号线CL1处于异常状态。

在第二感测周期T2期间,由于第二信号CLK2具有高电平电压HV,因此第二感测晶体管SENT2变为导通。此外,由于感测参考信号SRS也具有高电平电压HV,所以控制感测晶体管MS也变为导通。当第二信号线CL2处于正常状态并且弯曲区域BA中的第二信号线CL2中存在断裂时,传感器电路660和确定电路620的操作与第一感测周期T1中的那些基本相同;因此,为了描述的方便,省略了相关的讨论。

在第三感测周期T3期间,由于起始信号VST和感测参考信号SRS具有高电平电压HV,因此第三感测晶体管SENT3和控制感测晶体管MS变为导通。

当起始线VSL处于正常状态时,施加到起始线VSL的高电平电压HV通过第三感测晶体管SENT3和控制感测晶体管MS被提供到读出线ROL。在这种情况下,确定电路620可以通过读出线ROL读出高电平电压HV,并且当识别出读出信号ROS对应于感测参考信号SRS时,确定第一信号线CL1处于正常状态。

当在弯曲区域BA中的起始线VSL中存在断裂时,由于读出信号ROS具有高电平电压HV,因此第三感测晶体管SENT3变为导通。然而,即使将高电平电压HV施加到起始线VSL,由于起始线中的断裂,高电平电压HV的起始信号也不能正常地施加到第三感测晶体管SENT3的源极或漏极节点。结果,尽管控制感测晶体管MS处于导通状态,控制感测晶体管MS不能将高电平电压HV提供给读出线ROL。因此,确定电路620可以在第三感测周期T3期间识别出读出信号ROS不与感测参考信号SRS相对应,并且可以确定第三信号线CL3处于异常状态。

使用传感器电路660和确定电路620,可以识别出信号线(CL1、CL2、VSL)中存在断裂或短路的位置是弯曲区域BA。这是因为设置传感器电路660的位置是与弯曲区域BA相邻的位置。

具体地,由于施加到感测晶体管(SENT1、SENT2、SENT3)的栅极节点的信号被施加到与弯曲区域BA相邻的位置,因此可以识别出弯曲区域BA中的信号线中异常的存在与否。

同时,在根据本公开的一个实施例的显示设备100中的显示驱动周期期间,由于感测参考信号SRS具有低电平电压LV,因此控制感测晶体管MS和第三感测晶体管SENT3保持关断状态。因此,由于控制感测晶体管MS使信号线(CL1、CL2、VSL)不被电连接到读出线ROL,因此可以将相关的信号(CLK1、CLK2、VST)正常地输入到栅极驱动电路130。

图17示出根据本公开的一个实施例的用于感测布置在显示面板110的弯曲区域BA中的信号线中异常的存在与否的传感器电路680和确定电路620。由于图17中所示的用于传感器电路680的感测操作的驱动时序图基本上等同于图15的图示,参考图15进行相关讨论。由于图17中所示的传感器电路680是图14中所示的传感器电路640的变型,为了描述的方便,将简要进行或省略关于相关联的重复操作的讨论

参考图17,传感器电路680可以包括:用于传递感测参考信号SRS的感测参考信号线SRSL、用于将读出信号ROS传递到确定电路620的读出线ROL、第一感测晶体管SENT1、第二感测晶体管SENT2、第三感测晶体管SENT3和控制感测晶体管(MS1、MS2)。控制感测晶体管(MS1、MS2)可以包括第一控制感测晶体管MS1和第二控制感测晶体管MS2。这里,尽管包括在传感器电路680中的晶体管被表示为n型晶体管,但是,本公开的实施例不限于此。

第一感测晶体管SENT1的栅极节点和第一感测晶体管SENT1的漏极或源极节点连接到第一信号线CL1,并且其余的源极或漏极节点连接到控制感测晶体管(MS1、MS2)。第一感测晶体管SENT1可以感测第一信号线CL1中异常的存在与否。

第二感测晶体管SENT2的栅极节点和第二感测晶体管SENT2的漏极或源极节点连接到第二信号线CL2,并且其余的源极或漏极节点连接到控制感测晶体管(MS1、MS2)。第二感测晶体管SENT2可以感测第二信号线CL2中异常的存在与否。

第三感测晶体管SENT3的栅极节点和第三感测晶体管SENT3的漏极或源极节点连接到起始线VSL,并且其余的源极或漏极节点连接到第二控制感测晶体管MS2。第三感测晶体管SENT3可以感测起始线VSL中异常的存在与否。

第一控制感测晶体管MS1的栅极节点连接至感测参考信号线SRSL,并且第一控制感测晶体管MS1的源极或漏极节点连接至第一感测晶体管SENT1、第二感测晶体管SENT2、和第二控制感测晶体管MS2,并且第一控制感测晶体管MS1的其余的漏极或源极节点通过读出线ROL连接到确定电路620。

第二控制感测晶体管MS2的栅极节点连接至感测参考信号线SRSL,并且第二控制感测晶体管MS2的源极或漏极节点连接至第三感测晶体管SENT3,并且第二控制感测晶体管MS2的其余的漏极或漏极节点连接到第一控制感测晶体管MS1。

第一感测晶体管SENT1和第二感测晶体管SENT2通过第一控制感测晶体管MS1共同连接到读出线ROL。此外,第三感测晶体管SENT3通过第一控制感测晶体管MS2和第二控制感测晶体管MS1连接到读出线ROL。

第一感测晶体管SENT1、第二感测晶体管SENT2和第三感测晶体管SENT3电连接到信号线、感测参考信号线和读出线,并且可以感测信号线中异常的存在与否。

连接到读出线ROL的确定电路620可以从读出线ROL接收读出信号ROS,并且基于读出信号ROS确定第一信号线CL1、第二信号线CL2或起始线VSL中异常的存在与否。

参考图15,在弯曲区域BA的整个感测周期Tsen期间,感测参考信号SRS具有高电平电压HV,并且在除了整个感测周期Tsen之外的周期期间具有低电平电压LV。

在弯曲区域BA的整个感测周期Tsen期间,高电平电压HV顺序地提供给需要检查异常的存在与否的信号线(CL1、CL2、VSL)。因此,可以顺序地分配用于检查相应信号线(CL1、CL2、VSL)的相应感测周期(T1、T2、T3)。

在用于感测第一信号线CLl中异常的存在与否的第一感测周期Tl期间,高电平电压HV被施加到第一信号线CLl,而低电平电压LV被施加到其余的信号线(CL2、VSL)。

在用于感测第二信号线CL2中异常的存在与否的第二感测周期T2期间,高电平电压HV被施加到第二信号线CL2,而低电平电压LV被施加到其余的信号线(CL1、VSL)。

在用于感测起始线VSL中异常的存在与否的第三感测周期T3期间,高电平电压HV被施加到起始线VSL,而低电平电压LV被施加到其余的信号线(CL1、CL2)。

在第一感测周期Tl期间,由于第一信号CLK1具有高电平电压HV,因此第一感测晶体管SENT1变为导通。此外,由于感测参考信号SRS也具有高电平电压HV,因此第一控制感测晶体管MS1也变为导通。

当第一信号线CL1处于正常状态时,施加到第一信号线CL1的高电平电压HV通过第一感测晶体管SENT1和第一控制感测晶体管MS1被提供到读出线ROL。在这种情况下,确定电路620可以通过读出线ROL读出高电平电压HV,并且当识别出读出信号ROS对应于感测参考信号SRS时,确定第一信号线CL1处于正常状态。

在弯曲区域BA中的第一信号线CL1中存在断裂的情况下,即使当高电平电压HV被施加到第一信号线CL1时,由于第一信号线CL1中的断裂,高电平电压HV的第一信号CLK1也不能正常施加到第一感测晶体管SENT1的栅极节点。据此,第一感测晶体管SENT1不能导通。尽管第一控制感测晶体管MS1处于导通状态,但是由于第一感测晶体管SENT1处于关断状态,所以第一控制感测晶体管MS1不能将高电平电压HV传递至读出线ROL。在这种情况下,由于确定电路620在第一感测周期T1期间不能通过读出线ROL读出高电平电压HV,所以确定电路620可以识别出读出信号ROS不对应于感测参考信号SRS,并确定第一信号线CL1处于异常状态。

在第二感测周期T2期间,第二感测晶体管SENT2的操作和用于感测第二信号线CL2处于正常还是异常状态的操作基本上等同于第一感测周期T1中的操作;因此,为了描述的方便,将省略相关的讨论。在这种情况下,应当注意,第一感测晶体管SENT1可以改变为第二感测晶体管SENT2,并且第一信号线CL1可以改变为第二信号线CL2,并且第一信号CLK1可以改变为第二信号CLK2。

在第三感测周期T3期间,由于起始信号VST具有高电平电压HV,所以第三感测晶体管SENT3变为导通。此外,由于感测参考信号SRS也具有高电平电压HV,所以第一控制感测晶体管MS1和第二控制感测晶体管MS2也变为导通。

当起始信号线VSL处于正常状态时,施加到起始信号线VSL的高电平电压HV通过第三感测晶体管SENT3、第二控制感测晶体管MS2和第一控制感测晶体管MS1提供给读出线ROL。在这种情况下,确定电路620可以通过读出线ROL读出高电平电压HV,并且当识别出读出信号ROS对应于感测参考信号SRS时,确定开始信号线VSL处于正常状态。

在弯曲区域BA中的起始信号线VSL中存在断裂的情况下,即使当高电平电压HV被施加到起始信号线VSL时,由于起始信号线VSL中的断裂,高电平电压HV的起始信号VST也不能正常施加到第三感测晶体管SENT3的栅极节点。据此,第三感测晶体管SENT3不能导通。尽管第一控制感测晶体管MS1和第二控制感测晶体管MS2处于导通状态,但是由于第三感测晶体管SENT3处于关断状态,因此高电平电压HV不能被传递至读出线ROL。在这种情况下,由于确定电路620在第三感测周期T3期间不能通过读出线ROL读出高电平电压HV,所以确定电路620可以识别出读出信号ROS不对应于感测参考信号SRS,并确定起始信号线VSL处于异常状态。

使用传感器电路680和确定电路620,可以识别出信号线(CL1、CL2、VSL)中存在断裂或短路的位置是弯曲区域BA。这是因为设置传感器电路680的位置是穿过弯曲区域BA的与弯曲区域BA相邻的位置。

具体地,由于施加到感测晶体管(SENT1、SENT2、SENT3)的栅极节点的信号被施加到与弯曲区域BA相邻的位置,因此可以识别出弯曲区域BA中的信号线中异常的存在与否。

同时,在根据本公开的一个实施例的显示设备100中的显示驱动周期期间,由于感测参考信号SRS具有低电平电压LV,所以控制感测晶体管(MS1、MS2)保持关断状态。因此,由于控制感测晶体管(MS1、MS2)使信号线(CL1、CL2、VSL)不被电连接至读出线ROL,因此相关联的信号(CLK1、CLK2、VST)可以正常地输入到栅极驱动电路130。

例如,在显示驱动中,栅极驱动电路130可以由诸如彼此切换并且不具有其中高电平电压HV彼此重叠的第一信号CLK1和第二信号CLK2的周期的信号、以及具有其中起始信号VST的高电平电压HV与第一信号CLK1和第二信号CLK2的高电平电压HV重叠的周期的起始信号VST来操作。在这种情况下,如果不包括第二控制感测晶体管MS2,则由于重叠的信号被施加到连接在第一控制感测晶体管MS1和感测晶体管(SENT1、SENT2、SENT3)之间的节点,因此信号之间可能发生干扰,并且进而,这在驱动栅极驱动电路时引起问题。因此,通过将第二控制感测晶体管MS2设置在用于感测可能与另一信号重叠的起始信号VST的第三感测晶体管SENT3与第一控制感测晶体管MS1之间,可以防止信号彼此干扰,并且使栅极驱动电路能够正常操作。

另外,如图6所示,图14、图16和图17的读出线ROL可以包括位于链接区域LA中的部分(PART1)和位于有源区域AA的侧边缘区域之外的部分(PART2)。在另一实施例中,可以进一步包括控制晶体管,该控制晶体管串联连接至读出线ROL,并且可以在连接区域LA中的部分(PART1)与读出线ROL的有效区域AA的侧边缘区域之外的部分(PART2)之间连接或断开。该控制晶体管可以执行与参考图6讨论的第二控制晶体管M2相同的功能;因此,为了描述的方便,省略了相关的讨论。

此外,与上述实施例相关联的信号(CLK1、CLK2、VST)是输入到栅极驱动电路的信号;然而,本公开的实施例不限于此。根据栅极驱动电路的结构,可以改变或修改信号线,或者可以增加栅极驱动电路的数量。

根据本公开的实施例的显示设备可以描述如下。

根据本公开的一个方面,提供了一种显示设备,该显示设备包括:基板,该基板包括其中布置多个子像素并显示图像的有源区域、以及非有源区域,该非有源区域是有源区域外部的区域;将数据信号提供给多个子像素的数据驱动电路;将栅极信号提供给多个子像素的栅极驱动电路;以及感测连接到栅极驱动电路的信号线中异常的存在与否的传感器电路。此外,基板的非有源区域包括与数据驱动电路电连接的驱动电路区域、位于驱动电路区域和有源区域之间并且可以弯曲的弯曲区域、以及弯曲区域和有源区域之间的链接区域。传感器电路包括:提供感测参考信号的感测参考信号线;提供读出信号的读出线;以及电连接到至少一个信号线、感测参考信号线和读出线的感测晶体管。在这种情况下,传感器电路可以设置在链接区域中。因此,可以准确地识别出信号线的异常发生在何处,并校正相应的缺陷。

根据本公开的一个实施例,显示设备可以进一步包括确定电路,该确定电路电连接到读出线,从读出线接收读出信号,并基于读出信号确定信号线中异常的存在与否。此外,当确定信号线处于异常状态时,确定电路可以控制信号线的识别信息或位置信息或由确定产生的信息以存储在存储器中或显示在屏幕上。

在根据本公开的一个实施例的显示设备中,在用于感测信号线中异常的存在与否的感测周期期间,具有感测晶体管的电压的导通电平的信号可以施加到信号线,并且具有与电压的导通电平相同的电压的感测参考信号可以施加到感测参考信号线。

在根据本公开的一个实施例的显示设备中,在用于感测信号线中异常的存在与否的感测周期期间,当具有感测晶体管的电压的导通电平的信号施加到信号线时,取决于信号线中是否存在断裂,感测晶体管可以处于导通状态或关断状态。

在根据本公开的一个实施例的显示设备中,确定电路可以确定当读出信号ROS对应于感测参考信号时,相关联的信号线处于正常状态,以及当读出信号ROS与感测参考信号不对应时,信号线处于异常状态。

在根据本公开的一个实施例的显示设备中,传感器电路还可以包括由感测参考信号控制的控制感测晶体管。

在根据本公开的一个实施例的显示设备中,读出线可以被设置成延伸到有源区域的侧边缘区域之外,并且包括在链接区域中的一部分和在有源区域的侧边缘区域之外一部分。

在根据本公开的一个实施例的显示设备中,栅极驱动电路设置在基板上,并且包括面板内栅极(GIP)型的多个栅极驱动器,并且在有源区域的侧边缘区域之外的读出线的部分的端部可以电连接到在多个栅极驱动器中设置为最远离弯曲区域的最后的栅极驱动器的输出端子。

在根据本公开的一个实施例的显示设备中,控制感测晶体管可以在用于感测信号线中异常的存在与否的感测周期期间基于感测参考信号而导通,并且可以在显示驱动周期期间通过感测参考信号而关断。

根据本公开的一个方面,一种显示设备,包括:弯曲区域,其包括设置成穿过弯曲区域的信号线;连接到该信号线的传感器电路;以及基于通过传感器电路的感测获得的信息确定信号线中的异常的确定电路。此外,传感器电路包括连接到确定电路的读出线、提供用于比较由确定电路从传感器电路接收到的信息的感测参考信号的感测参考信号线、连接到信号线的感测晶体管、以及控制感测晶体管,其连接到感测参考信号线、读出线和感测晶体管。因此,可以准确地识别出信号线的异常发生在何处,并校正相应的缺陷。

在根据本公开的一个实施例的显示设备中,传感器电路可以包括两个或更多信号线和两个或更多感测晶体管,并且控制感测晶体管可以共同地连接到两个或更多感测晶体管。

此外,两个或更多感测晶体管可以在用于确定两个或更多信号线中异常的存在与否的感测周期期间顺序地导通。

在根据本公开的一个实施例的显示设备中,感测晶体管的栅极节点和感测晶体管的源极或漏极节点可以电连接到信号线,而不连接到感测晶体管的源极和漏极节点的信号线的节点可以连接到控制感测晶体管。

在根据本公开的一个实施例的显示设备中,两个或更多信号线可以包括具有(传递)具有彼此重叠的脉冲的相应信号的信号线;所述控制感测晶体管可以包括第一控制感测晶体管和第二控制感测晶体管;所述第一控制感测晶体管可以连接在连接到所述信号线之一的感测晶体管和所述读出线之间;所述第二控制感测晶体管可以连接在连接到所述信号线中的另一个的感测晶体管与所述第一控制感测晶体管之间。此外,第一控制感测晶体管和第二控制感测晶体管可以由感测参考信号控制,并且感测参考信号可以具有能够在用于感测信号线中异常的存在与否的感测周期期间导通第一控制感测晶体管和第二控制感测晶体管的电压的导通电平。

在根据本公开的一个实施例的显示设备中,传感器电路可以被设置为与弯曲区域相邻。

根据本公开的一个实施例的显示设备可以进一步包括静电放电电路,至少一个信号线、读出线和感测参考信号线连接到该静电放电电路。

在根据本公开的一个实施例的显示设备中,信号线可以比感测参考信号线长。

根据本公开的实施例,在通过将弯曲结构施加到显示面板来实施窄边框时,为了解决由于面板结构、面板制造工艺等中的一些限制而导致难以通过视觉检验或检验装备等来检查位于弯曲区域中的信号线中异常的存在与否的这种问题,可以提供能够准确地感测位于弯曲区域中的信号线中异常的存在与否的显示设备。

通过这些,可以提供显示设备100,所述显示设备100能够对在位于弯曲区域中的信号线中诸如断裂等的异常的存在与否执行准确的检查,并且因此,具有没有缺陷的正常弯曲结构。

此外,根据本公开的实施例,可以提供显示设备100,所述显示设备100能够检测出在制造面板之后将在弯曲区域BA中发生的信号线中的异常,并且因此,能够对异常采取动作。

根据本公开的实施例,可以提供一种显示设备,其能够识别出信号线中的异常是存在于弯曲区域中还是存在于除弯曲区域之外的另一区域中。

上述的本公开不限于上述的实施例和附图,而是可以以各种不同的形式来实施。对所述的实施例的各种修改、添加和替换对于本领域中的技术人员将是容易的,并且在不脱离本发明的精神和范围的情况下,本文中限定的一般原理可以施加到其他实施例和应用。本公开的保护范围应基于以下权利要求来解释,并且在其等同物的范围内的所有技术概念应被解释为包括在本公开的范围内。

此外,在以下权利要求中,不应将所使用的术语解释为将权利要求限制为说明书和权利要求中所公开的特定实施例,而应解释为包括所有可能的实施例以及这些权利要求有权享有的等同物的全部范围。因此,权利要求不受公开内容的限制。

- 具有稳定基座的装置、图像显示设备、装置安装基座、装置显示系统、图像显示设备安装基座、图像显示设备显示系统、及图像显示设备显示方法

- 显示设备中图像显示的方法、补偿显示设备的数据信号的数据信号补偿设备、以及显示设备