一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法

文献发布时间:2023-06-19 11:42:32

技术领域

本发明属于线上验证技术领域,涉及一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法。

背景技术

目前,在FPGA上进行算法项目开发面临着周期长、成本高、难度大的特点。FPGA的开发人员不仅需要了解底层硬件的实现方式,熟悉相关接口的传输协议,还需要设计和开发相对应的算法以满足项目的需求。因此接口开发人员和算法开发人员在大型项目研发中常常都是必须,但由此增加的研发成本和研发周期是巨大的。本发明为解决上述问题提出了一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法,通过实现底层硬件通信接口,并封装为统一的逻辑接口给用户,从而帮助普通用户快速搭建算法验证平台,使用户能够专注于算法的设计而无需关注底层硬件的具体实现方式。

发明内容

本发明针对现有技术的不足,提供一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法。该方法利用在远程服务器下外挂FPGA的方式实现,本发明的技术方案为一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法,包括以下步骤:

S1,用户在远程客户端通过SSH(Secure Shell,安全外壳协议)的方式连接至云端,使用SFTP(Secret File Transfer Protocol,安全文件传输协议)将测试用图像文件与待测试图像处理硬件逻辑HDL设计文件提交至FPGA云服务器;

S2,向用户提供已实现的接口逻辑网表文件;

S3,通过脚本建立工程、编译代码,综合生成可下载的比特流文件;

S4,用户编译驱动方法,服务器主机向FPGA传输待测图像数据;待测图像数据发送完后,发送写数据完成信号,等待FPGA处理完成;服务器主机收到FPGA处理完成信号后,启动读数据;读数据完成后,将图像数据重新写回图片,并使用SFTP从服务器上下载图片到本地主机查看。

优选地,所述向用户提供已实现的接口逻辑网表文件,其中已实现的接口逻辑网表文件对应的逻辑接口模块包括图像数据传输模块和图像数据存储模块,图像数据存储模块包含写图像数据控制模块和读图像数据控制模块,分别控制存储单元的读写。

优选地,所述图像数据存储模块采用片外存储单元,包括DDR3和/或DDR4。

优选地,所述图像数据传输模块包括面向外部接口的PCIe接口和面向用户逻辑模块的用户逻辑接口,其中PCIe接口利用AXI4/Avalon进行访问,用户逻辑接口采用数据包传输协议,包括xx_sop代表数据包起始信号,xx_eop代表数据包结束信号,xx_vld代表数据有效信号和xx_data代表图像数据。

优选地,所述通过脚本建立工程、编译代码,综合生成可下载的比特流文件,包括以下步骤:

S31,将用户的顶层模块usr_top通过局部综合的方式生成用户逻辑网表文件;

S32,将用户逻辑网表文件和已实现的接口逻辑网表文件进行验证,验证自定义用户逻辑接口信号是否匹配提前实现的接口逻辑模块内的信号;

S33,将用户逻辑网表文件和已实现的接口逻辑网表文件进行联合布局、布线生成比特流文件,再使用布局和布线工具生成可下载的比特流文件。

优选地,所述脚本包括:

脚本1:compile.sh将会首先调用EDA工具用于后续的综合、实现,接着读入creat_usr_project.tcl、run_usr_synth.tcl和generate_bit.tcl三个脚本;

脚本2:creat_usr_project.tcl该脚本将会导入用户的逻辑代码和ip,并建立用户工程usr_prj;

脚本3:run_usr_synth.tcl该脚本将编译和综合用户工程的代码,并生成用户逻辑网表文件;

脚本4:generate_bit.tcl首先该脚本会分别导入用户逻辑网表文件和已实现的接口逻辑网表文件,然后导入设计要求的约束文件;其中的约束文件包含物理约束和时序约束。

优选地,所述S4中驱动方法包括以下步骤:

S41,读入图片,并提取图像数据存至内存;

S42,打开PCIe设备配置接口描述符,通过单次读写回传数据检测PCIe是否正常工作;

S43,通过PCIe配置接口发送配置参数,配置参数包括图像宽度col和图像高度row;

S44,打开PCIe设备数据发送接口描述符,调用函数host_to_fpga()发送图像数据;图像数据发送完成后调用配置接口写数据函数write_axi_lite(),发送图像数据写完成信号;

S45,等待FPGA处理完成,并且每隔1s调用配置接口读数据函数read_axi_lite()判断FPGA是否处理完成;当读到FPGA处理完成信号后,打开PCIe设备数据接收接口描述符,调用函数fpga_to_host()读取处理后的图像数据;

S46,将接收到的图像数据写回图片,并下载到本地主机。

本发明的有益效果如下:

在基于FPGA的算法开发和验证中,采用底层接口逻辑和算法逻辑分开实现的方法有利于降低开发难度、缩短研发周期,也有利于普通用户快速构建自己的验证平台。同时,底层接口逻辑已经实现了PC到FPGA的数据传输,并且提供给用户统一的逻辑接口。这能够让用户更专注于算法的开发和验证,而无需关心底层硬件的具体实现方式。

附图说明

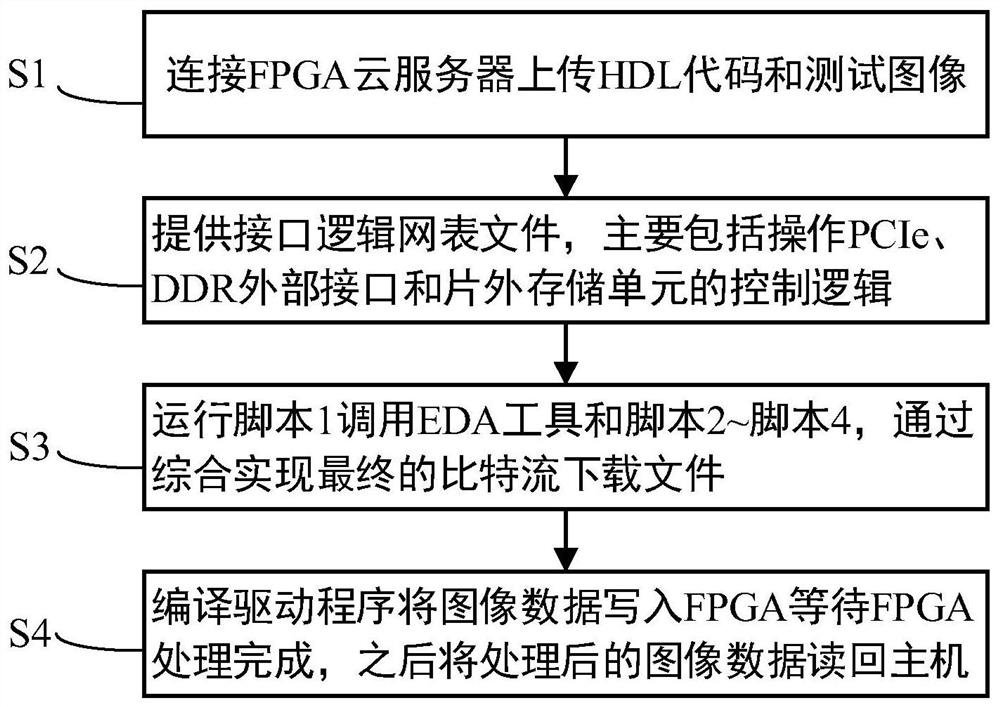

图1为本发明实施例的基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法的步骤流程图;

图2为本发明实施例的基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法的系统结构示意图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

相反,本发明涵盖任何由权利要求定义的在本发明的精髓和范围上做的替代、修改、等效方法以及方案。进一步,为了使公众对本发明有更好的了解,在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。

参见图1,为本发明实施例的本发明的技术方案为基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法的步骤流程图,结合图2的结构图,包括以下步骤:

S1:用户在远程客户端通过SSH的方式连接至云端,使用SFTP将测试用图像文件与待测试图像处理硬件逻辑HDL设计文件提交至FPGA云服务器。

S2:向用户提供已实现的接口逻辑网表文件,其中已实现的逻辑接口模块包括图像数据传输模块和图像数据存储模块。图像数据存储模块包含写图像数据控制模块21和读图像数据控制模块22,分别控制存储单元10的读写。图像数据存储模块使用片外存储单元,如DDR3、DDR4。图像数据传输模块包含面向外部接口的PCIe接口和面向用户逻辑模块的用户逻辑接口33。PCIe接口(包括配置接口32和数据接口31)利用AXI4/Avalon进行访问,用户逻辑接口33采用数据包传输协议,包括如下信号:xx_sop代表数据包起始信号,xx_eop代表数据包结束信号,xx_vld代表数据有效信号,xx_data代表图像数据。

S3:通过脚本建立工程、编译代码,综合生成可下载的比特流文件。首先,需要将用户的顶层模块usr_top通过局部综合的方式生成用户逻辑网表文件。然后,将用户逻辑网表文件和已实现的接口逻辑网表文件进行验证,验证用户逻辑接口33的接口信号是否匹配提前实现的接口逻辑模块34内的信号。最后,将用户逻辑网表文件和接口逻辑网表文件进行联合布局、布线生成比特流文件。其中用到的脚本主要包括如下四种:

脚本1:compile.sh将会首先调用EDA工具用于后续的综合、实现,接着读入creat_usr_project.tcl、run_usr_synth.tcl和generate_bit.tcl三个脚本。

脚本2:creat_usr_project.tcl该脚本将会导入用户的逻辑代码和ip,并建立用户工程usr_prj。

脚本3:run_usr_synth.tcl该脚本将编译和综合用户工程的代码,并生成用户逻辑网表文件。

脚本4:generate_bit.tcl首先该脚本会分别导入用户逻辑网表文件和已实现的接口逻辑网表文件,然后导入设计要求的约束文件。其中的约束文件包含物理约束和时序约束。最后使用布局和布线工具生成可下载的比特流文件。

S4:用户编译驱动方法,服务器主机向FPGA传输待测图像数据。待测图像数据发送完后,发送写数据完成信号,等待FPGA处理完成。服务器主机收到FPGA处理完成信号后,启动读数据。读数据完成后,将图像数据重新写回图片,并使用SFTP从服务器上下载图片到本地主机查看。

驱动方法主要包括以下步骤:

(1)读入图片,并提取图像数据存至内存。

(2)打开PCIe设备配置接口32描述符,通过单次读写回传数据检测PCIe是否正常工作。

(3)通过PCIe配置接口32发送配置参数,配置参数主要包括:图像宽度col、图像高度row,通过命令解析模块41向逻辑接口模块发送;

(4)打开PCIe设备数据发送接口(即数据接口31)描述符,调用函数host_to_fpga()发送图像数据;图像数据发送完成后调用配置接口32写数据函数write_axi_lite(),发送图像数据写完成信号。

(5)等待FPGA处理完成,并且每隔1s调用配置接口32读数据函数read_axi_lite()判断FPGA是否处理完成。当读到FPGA处理完成信号后,打开PCIe设备数据接收接口(即数据接口31)描述符,调用函数fpga_to_host()读取处理后的图像数据。

(6)将接收到的图像数据写回图片,并下载到本地主机。

所述参数配置、命令发送和接收的实现方式为:

使用PCIe的配置接口32,接口时序为AXI4/Avlon类型。主机Host将PCIe BAR地址空间映射到FPGA的配置寄存器,在主机侧读写相应的虚拟地址可以访问FPGA内部寄存器,从而实现主机和FPGA的参数配置、命令发送和接收。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

- 一种基于FPGA云的图像处理硬件逻辑HDL模块的线上验证方法

- 一种基于FPGA的以太网协议硬件逻辑处理结构