封装结构及其形成方法

文献发布时间:2023-06-19 12:13:22

技术领域

本发明涉及半导体技术领域,具体来说,涉及一种封装结构及其形成方法。

背景技术

在半导体技术中,内埋芯片于系统封装的应用已越来越广。然而,内埋芯片的散热需求也越来越高。

若要增加内埋芯片的散热能力,通常会于基板内设置大铜块或导入散热膏以期望热量从芯片背侧导出到封装件之外。如图1A所示,以设置导热膏12的实施例为例,在进行芯片接合时,可能因不平衡的作用力(如图1B)而造成芯片14有破裂18的风险,如图1B。此外,在接合芯片14之后,也有可能会发生芯片倾斜的问题。

发明内容

针对相关技术中的上述问题,本发明提出一种装结构及其形成方法,能够现有的芯片直接安装至散热元件时产生倾斜的问题。

本发明的技术方案是这样实现的:

根据本发明的一个方面,提供了一种封装结构,包括:介电材料,具有从介电材料的上表面凹进的空腔;散热元件,位于空腔内;芯片,位于介电材料和散热元件上方,并且芯片的至少部分底部与散热元件接触。

在一些实施例中,芯片横跨在空腔的上方。

在一些实施例中,介电材料中设置有线路结构。

在一些实施例中,芯片具有在长度方向上的中间段,散热元件包覆中间段的底部及侧面。

在一些实施例中,芯片具有在长度方向上的两个端部,两个端部的侧面直接接触介电材料且不接触散热元件。

在一些实施例中,散热元件在芯片的宽度方向上凸出于芯片。

在一些实施例中,封装结构还包括:粘合层,覆盖在介电材料和芯片上方,其中,散热元件与介电材料之间具有间隔,粘合层填充在间隔内。

在一些实施例中,空腔的侧壁为阶梯形。

在一些实施例中,散热元件完全填充空腔以具有阶梯形侧壁。

在一些实施例中,散热元件部分地填充空腔。

在一些实施例中,散热元件过填充空腔。

在一些实施例中,芯片具有在长度方向上的中间段,散热元件在中间段处具有最大宽度。

根据本发明的另一方面,提供了一种封装结构,包括:介电层,具有从介电层的上表面凹进的空腔;散热元件,位于空腔内;芯片,位于介电层和散热元件上方,并且芯片的至少部分底部与散热元件接触;电连接件,设置在芯片上;线路层,位于芯片上方,电连接件将芯片与线路层电连接。

在一些实施例中,介电层中设置有线路结构。

在一些实施例中,封装结构还包括:贯通孔,穿过介电层并电连接至线路层。

在一些实施例中,封装结构还包括:粘合层,覆盖在介电层和芯片上方,其中,散热元件与介电层之间具有间隔,粘合层填充在间隔内。

根据本发明的另一方面,提供了一种形成封装结构的方法,包括:形成从介电层的上表面凹进的空腔,并在空腔中填入散热材料;将芯片接合在介电层和散热元件上方,其中,芯片的至少部分底部与散热元件接触。

在一些实施例中,在形成空腔之间,还包括:在介电层中形成线路结构。

在一些实施例中,还包括:形成线路层;通过芯片上的电连接件将芯片与线路层接合。

在一些实施例中,在将芯片与线路层接合之后,还包括:形成穿过线路层并到达介电层中的线路的贯通孔;在贯通孔中填充导电材料。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1A和图1B是根据现有技术形成的封装结构的示意图。

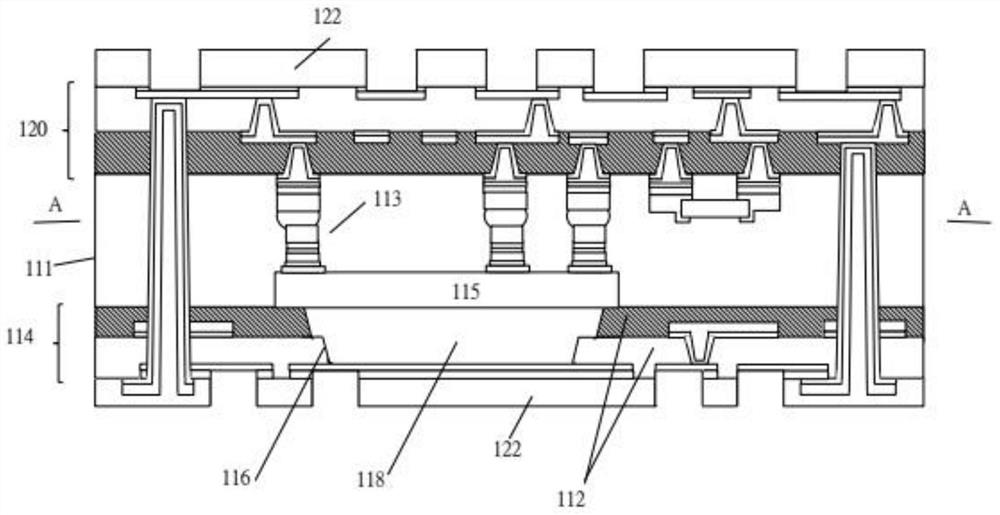

图2是根据本发明实施的封装结构的示意图。

图3A至图3D示出了根据本发明实施例的封装结构的各个不同截面的示意图。

图4A至图4W是形成根据本发明实施例的封装结构的各个阶段的示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员所获得的所有其他实施例,都属于本发明保护的范围。

根据本发明的实施例提供了一种封装结构。图2是根据本发明实施的封装结构的示意图。封装结构可以包括介电材料112。介电材料112可以是线路层114中的单个或多个介电层,在这样的实施例中,介电材料112中设置有线路结构。在其他实施例中,介电材料112也可以是封装结构中的其他部分处的介电材料。介电材料112具有从介电材料112的上表面凹进的空腔116。空腔116的侧壁可以为阶梯形。散热元件118位于空腔116内。散热元件118可以完全填充空腔116,以使得散热元件118相应地具有阶梯形侧壁。在一些实施例中,空腔116的底面面积与散热元件118的在俯视图中的面积之比在70%至90%的范围内。散热元件118的厚度可以在5微米至20微米的范围内。空腔116的长度或宽度在20微米至100微米的范围内。

芯片115位于介电材料112和散热元件118上方,并且芯片115的至少部分底部与散热元件118接触。芯片115横跨在空腔116的上方。散热元件118可以在芯片115的宽度方向上凸出于芯片115。在一些实施例中,散热元件118的材料可以包括:金属,例如Ag、Cu、Au、Al、Ni及其组合的合金;和/或非金属,例如Ta

本发明的上述技术方案,通过在介电材料112中形成一空腔116并将散热元件118填入其中,再将芯片115接合至与散热元件118接触,这样芯片115的水平面程度是由介电材料112的决定,便可解决现有的芯片115直接安装至散热元件118时产生倾斜的风险。

在图2所示的实施例中,芯片115由粘合层111围绕。粘合层111的材料包括有机物,例如NCP、NCF、ACP、ACF、PI、环氧树脂、树脂,、pp、ABF、胶。芯片115还通过其上方的连接件113(例如包括焊料)连接到粘合层111上方的另一线路层120连接。焊料掩模层122设置在线路层114和另一线路层120的暴露的表面处。贯穿孔穿过线路层和粘合层111连接到另一线路层120中的线路。线路层114和另一线路层120可以是RDL层。线路层114和另一线路层120的层数可以是任意数量,本发明对此不进行限定。应理解,除空腔116、散热元件118和芯片115的配置之外,封装结构也可以是其他任何可应用的结构。

图3A至图3D示出了根据本发明实施例的封装结构的各个不同截面的示意图。图3A是图2中的线A-A处的截面的俯视图。图3B、图3C和图3D分别是图3A中的线B-B、C-C和D-D处的截面图。

如图3A和图3B所示,芯片115具有在长度方向上的中间段(对应于图3A中的线B-B处)和两个端部(对应于图3A中的线D-D处),散热元件118包覆中间段的底部,还包覆中间段的部分侧面。即,在中间段处,散热元件118过填充空腔116而超过介电材料112的表面。散热元件118在芯片115的中间段的位置处具有最大宽度,并且在从中间段向端部延伸的方向上宽度逐渐减小。在图3B中,空腔116的侧壁的顶部超出芯片115的侧壁的距离可以在5微米至25微米之间的范围内。

如图3A和图3C所示,在中间段和端部之间的位置处(对应于图3A中的线C-C处),散热元件118不接触芯片115的侧面,而与芯片115的全部底面接触。如图3A和图3D所示,在芯片115的端部处,两个端部的侧面直接接触介电材料112且不接触散热元件118。并且此处散热元件118部分地填充空腔116,散热元件118与介电材料112之间具有间隔,从而覆盖芯片115的粘合层111可以填充在间隔内。

图4A至图4W是形成根据本发明实施例的封装结构的各个阶段的示意图。首先如图4A,提供第一载体401,第一晶种层402位于第一载体401上,第一光刻胶层403位于第一晶种层402上。在图4B中,对第一光刻胶层403进行图案化形成位于第一光刻胶层403中的第一开口404,并在第一开口404中形成第一金属层405。然后,去除第一光刻胶层403和位于第一光刻胶层403下方的第一晶种层402,并在保留的第一晶种层402和第一金属层405上形成第一介电层408,如图4C。

在图4D中,形成位于第一介电层408中的第二开口409,并在第一介电层408上和第二开口409内形成第二晶种层410,在第二晶种层410上形成第二光刻胶层412。第二开口409中的一个对应于后续形成的空腔。在图4E中,形成位于第二光刻胶层412中的第三开口414,并在第三开口414中形成第二金属层415。然后,去除第二光刻胶层412和位于第二光刻胶层412下方的第二晶种层410,如图4F。在图4G中,在保留的第二晶种层410和第二金属层415上形成第二介电层416。从而形成电路层114。

在图4H中,形成位于第一介电层408和第二介电层416中的空腔116。空腔116包括上述形成的一个第一介电层中408的第二开口409。在图4I中,在空腔116中填入散热元件118。

接下来,如图4J所示,可以通过与图4A至图4F类似的步骤,在第二载体421上形成图案化的第三晶种层422和第三金属层423、覆盖第三晶种层422和第三金属层423且具有第三开口424的第三介电层425、图案化的第四晶种层426和第四金属层428。在图4K中,在第三介电层上方形成第四介电层429,第四介电层429具有暴露下方的第四金属层428的第四开口431。第五晶种层432形成在第四介电层429上方和第四开口428内。在图4L中,在第五晶种432上形成具有第五开口433的第三光刻胶层434。在第五开口433内形成用于形成连接件的多个层。去除第三光刻胶层434和位于第三光刻胶434下方的第五晶种层432,从而形成另一线路层120和位于另一线路层120上的连接件113,如图4M。然后在连接件113上方接合器件435。

然后如图4N所示,在图4I得到的结构上将芯片115附接至散热元件118。芯片上方还设置有多个连接件113。在图4O中,通过粘合层111将图4N中的结构与图4M中的结构接合。在图4P中,去除第一载体401。在图4Q中,形成穿过线路层114、粘合层111并到达另一线路层120中的线路的贯通孔442,并且形成第六晶种层443。在图4R中,在线路层114上方和贯通孔442内形成暴露出贯通孔442的图案化的第四光刻胶层445,以在贯通孔内共形地形成第五金属层446。去除第四光刻胶层445和位于第四光刻胶层445下方的第六晶种层,如图4S。在图4T中,形成焊料掩模层122,焊料掩模层122具有暴露下方的线路的开口452。然后,将得到的结构翻转,并去除第二载体421,如图4U。在图4V中,在另一线路层120上形成另一焊料掩模层122,另一焊料掩模层122具有暴露下方的另一线路层120的线路的开口453。在图4W中,通过蚀刻工艺,将由焊料掩模层122、122中的开口452、453暴露的晶种层去除,形成了封装结构。

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法

- 芯片封装结构及芯片封装结构及其形成方法