半导体存储装置

文献发布时间:2023-06-19 09:44:49

本申请享受2018年4月23日申请的日本国特许申请编号2018-082281以及2018年12月5日申请的日本国特许申请编号2018-228246的优先权的利益,该日本国特许申请的全部内容被援用在本申请中。

技术领域

本实施方式一般涉及半导体存储装置。

背景技术

闪速存储器的存储容量伴随着技术改良而增大。伴随于此,如可移动(removable)存储卡那样的半导体存储装置的数据传送量增大,数据传送时间也增大。

若半导体存储装置的通信接口高速化,则能够缩短数据传送时间。

现有技术文献

专利文献1:日本特开2009-259207号公报

附图说明

图1是表示第1实施方式涉及的存储卡的例示性俯视图。

图2是表示第1实施方式的存储卡的例示性侧视图。

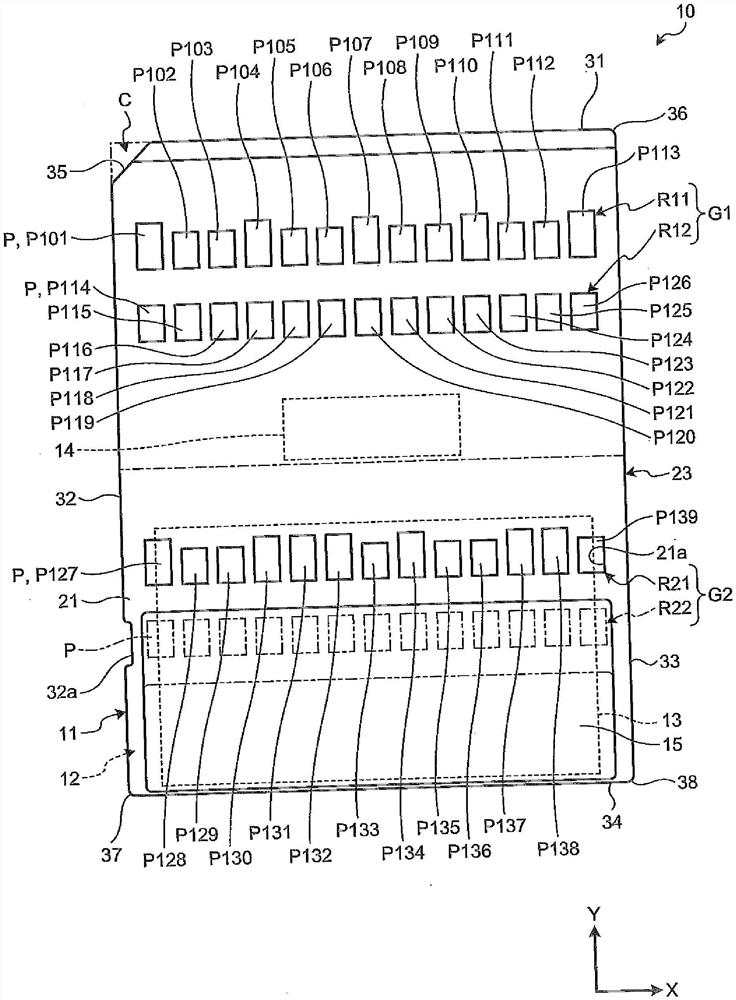

图3是表示第1实施方式的多个端子的信号分配的一个例子的例示性表。

图4是示意性地表示第1实施方式的存储卡的布线的例示性俯视图。

图5是概略地表示第1实施方式的存储卡的结构的第1例的例示性框图。

图6是概略地表示第1实施方式的存储卡的结构的第2例的例示性框图。

图7是表示第1实施方式的存储卡的电源检查序列(sequence)中的主机设备的动作的例示性流程图。

图8是表示第1实施方式的电源规格信息的一个例子的例示性表。

图9是表示第1实施方式的存储卡的电源检查序列中的第1例的例示性时序图。

图10是表示第1实施方式的存储卡的电源检查序列中的第2例的例示性时序图。

图11是表示第1实施方式的存储卡的电源检查序列中的第3例的例示性时序图。

图12是表示第2实施方式涉及的存储卡的例示性俯视图。

图13是表示第3实施方式涉及的存储卡的例示性俯视图。

图14是表示第3实施方式的存储卡的例示性侧视图。

图15是表示第3实施方式的变形例涉及的存储卡的例示性俯视图。

图16是表示第3实施方式的多个端子的信号分配的一个例子的例示性表。

图17是概略地表示第3实施方式的存储卡的结构的第1例的例示性框图。

图18是概略地表示第3实施方式的存储卡的结构的第2例的例示性框图。

图19是表示第3实施方式的存储卡的电源检查序列中的主机设备的动作的例示性流程图。

图20是表示第3实施方式的电源规格信息的一个例子的例示性表。

图21是表示第3实施方式的存储卡的电源检查序列中的第1例的例示性时序图。

图22是表示第3实施方式的存储卡的电源检查序列中的第2例的例示性时序图。

图23是表示第3实施方式的存储卡的电源检查序列中的第3例的例示性时序图。

图24是表示第3实施方式的存储卡的电源检查序列中的第4例的例示性时序图。

图25是表示第3实施方式的存储卡的温度检查顺序中的卡控制器的动作的例示性流程图。

图26是表示第4实施方式涉及的存储卡的例示性俯视图。

具体实施方式

根据实施方式,半导体存储装置具备壳体、存储器、控制器以及多个端子。所述壳体具有第1面、位于所述第1面的相反侧的第2面、在第1方向上延伸的第1端缘、位于所述第1端缘的相反侧并在所述第1方向上延伸的第2端缘、在与所述第1方向交叉的第2方向上延伸的第1侧缘以及形成所述第1端缘与所述第1侧缘之间的缺口的第1角部。所述存储器设置于所述壳体的内部。所述控制器设置于所述壳体的内部,对所述存储器进行控制。所述多个端子包括被使用于传输信号的多个信号端子,在所述第1面露出。所述多个端子形成至少一个第1列和至少一个第2列。所述至少一个第1列分别包括在距所述第1端缘比距所述第2端缘近的位置相互隔着间隔而在所述第1方向上排列的所述多个端子,在所述多个端子形成多个所述第1列的情况下,相互隔着间隔而在所述第2方向上排列。所述至少一个第2列分别包括在距所述第2端缘比距所述第1端缘近的位置相互隔着间隔而在所述第1方向上排列的所述多个端子,在所述多个端子形成多个所述第2列的情况下,相互隔着间隔而在所述第2方向上排列。

以下参照附图对实施方式涉及的半导体存储装置进行详细的说明。此外,并不是由这些实施方式限定本发明。

(第1实施方式)

以下,参照图1~图11对第1实施方式进行说明。此外,在本说明书中,关于实施方式涉及的构成要素以及该要素的说明,有时记载为多个表现。被采用了多个表现的构成要素以及说明也可以被采用未记载的其他表现。进一步,未被采用多个表现的构成要素以及说明也可以被采用未记载的其他表现。

图1是表示第1实施方式涉及的存储卡10的例示性俯视图。图2是表示第1实施方式的存储卡10的例示性侧视图。存储卡10是半导体存储装置的一个例子,例如也可以被称为可移动介质和可移动存储卡。

如各附图所示,在本说明书中定义X轴、Y轴以及Z轴。X轴、Y轴以及Z轴相互正交。X轴沿着存储卡10的宽度。Y轴沿着存储卡10的长度。Z轴沿着存储卡10的厚度。

存储卡10具有壳体11、基板12、闪速存储器13、卡控制器14以及保护片15。闪速存储器13是存储器的一个例子。卡控制器14是控制器的一个例子。

存储卡10和壳体11例如形成为在Y轴方向上延伸的大致矩形的板状。Y轴方向是存储卡10和壳体11的长边(长尺寸)方向,包括Y轴的正方向(Y轴的箭头表示的方向)和Y轴的负方向(Y轴的箭头的相反方向)。Y轴方向是第2方向的一个例子。

如图2所示,壳体11为板状,具有第1面21、第2面22以及外缘23。第1面21和第2面22形成为在Y轴方向上延伸的大致四边形(矩形)形状。即,Y轴方向也为第1面21和第2面22的长边方向。在本实施方式中,存储卡10、壳体11、第1面21以及第2面22的形状分别表现为矩形形状,但也可以采用其他表现。

第1面21是朝向Z轴的正方向(Z轴的箭头朝向的方向)的大致平坦的面。如图2所示,第2面22是位于第1面21的相反侧、朝向Z轴的负方向(Z轴的箭头的相反方向)的大致平坦的面。

外缘23设置在第1面21与第2面22之间,与第1面21的边缘和第2面22的边缘连接。如图1所示,外缘23具有第1边缘31、第2边缘32、第3边缘33、第4边缘34、第1角部35、第2角部36、第3角部37以及第4角部38。

第1边缘31在X轴方向上延伸,朝向Y轴的正方向。X轴方向是存储卡10、壳体11、第1面21以及第2面22的短边(短尺寸)方向,包括X轴的正方向(X轴的箭头表示的方向)和X轴的负方向(X轴的箭头的相反方向)。X轴方向是第1方向的一个例子。

第2边缘32在Y轴方向上延伸,朝向X轴的负方向。在第2边缘32设置有凹部32a。此外,也可以省略凹部32a。有时在供存储卡10插入的连接器设置有嵌于凹部32a的凸部。在该情况下,该凸部能够使设置有凹部32a的存储卡10插入到连接器,并且,能够防止没有凹部32a的存储卡10被插入到连接器。任何存储卡10都能够插入到没有凸部的连接器。这样,连接器能够基于凹部32a来对存储卡10的种类进行识别。另外,连接器能够基于存储卡10的凹部32a的位置和连接器的上述凸部的位置来对更多的存储卡10的种类进行识别。第3边缘33位于第2边缘32的相反侧并在Y轴方向上延伸,朝向X轴的正方向。第4边缘34位于第1边缘31的相反侧并在X轴方向上延伸,朝向Y轴的负方向。

第2边缘32和第3边缘33各自的长度比第1边缘31和第4边缘34各自的长度长。第1边缘31和第4边缘34形成大致矩形的存储卡10的短边,第2边缘32和第3边缘33形成大致矩形的存储卡10的长边。

第1角部35是第1边缘31与第2边缘32之间的角部分,将第1边缘31的X轴的负方向上的端部和第2边缘32的Y轴的正方向上的端部连接。第1边缘31的X轴的负方向上的端部是第1边缘的一方的端部的一个例子。第2边缘32的Y轴的正方向上的端部是第2边缘的端部的一个例子。

第1角部35在第1边缘31的X轴的负方向上的端部与第2边缘32的Y轴的正方向上的端部之间呈直线状延伸。在X轴方向上,第1边缘31的X轴的负方向上的端部与第2边缘32之间的距离为1.1mm。在Y轴方向上,第2边缘32的Y轴的正方向上的端部与第1边缘31之间的距离为1.1mm。

通过第1边缘31与第2边缘32的角被设定为所谓的C1.1的斜倒角,从而设置第1角部35。根据其他表现,第1角部35形成第1边缘31与第2边缘32之间的缺口C。

在本实施方式中,第1角部35在沿着相互正交的方向延伸的第1边缘31与第2边缘32的角部分形成大致三角形的缺口C。但是,缺口C不限于该例子。第1角部35例如也可以形成相比于本实施方式而向壳体11的内侧凹陷的大致四边形的缺口C。

第2角部36是第1边缘31与第3边缘33之间的角部分,将第1边缘31的X轴的正方向上的端部和第3边缘33的Y轴的正方向上的端部连接。第1边缘31的X轴的正方向上的端部是第1边缘的另一方的端部的一个例子。第3边缘33的Y轴的正方向上的端部是第3边缘的端部的一个例子。

第2角部36在第1边缘31的X轴的正方向上的端部与第3边缘33的Y轴的正方向上的端部之间呈圆弧状延伸。第2角部36呈正圆的圆弧状延伸,但也可以呈椭圆的圆弧状延伸。

呈圆弧状延伸的第2角部36的半径为0.2mm。通过第1边缘31与第3边缘33的角被设定为所谓的R0.2的圆倒角,从而设置第2角部36。这样,第1角部35的形状与第2角部36的形状互不相同。

第3角部37将第2边缘32的Y轴的负方向上的端部与第4边缘34的X轴的负方向上的端部连接。第4角部38将第3边缘33的Y轴的负方向上的端部与第4边缘34的X轴的正方向上的端部连接。第3角部37和第4角部38分别呈半径为0.2mm的圆弧状延伸。

存储卡10、壳体11、第1面21以及第2面22的Y轴方向上的长度被设定为大约18±0.1mm,X轴方向上的长度被设定为大约14±0.1mm。即,Y轴方向上的第1边缘31与第4边缘34之间的距离被设定为大约18±0.1mm,X轴方向上的第2边缘32与第3边缘33之间的距离被设定为大约14±0.1mm。此外,存储卡10、壳体11、第1面21以及第2面22的X轴方向和Y轴方向上的长度不限于该例子。

如图2所示,壳体11还具有倾斜部39。倾斜部39为第1面21与第1边缘31之间的角部分,在第1面21的Y轴的正方向上的端部与第1边缘31的Z轴的正方向上的端部之间呈直线状延伸。

如图1所示,基板12、闪速存储器13以及卡控制器14设置在壳体11的内部。基板12、闪速存储器13以及卡控制器14既可以容纳于箱型的壳体11,也可以埋入于壳体11。

基板12例如为印制电路板(PCB)。此外,基板12也可以是其他种类的基板。闪速存储器13和卡控制器14安装于基板12。

闪速存储器13是能够存储信息的非易失性存储器,例如为NAND型闪速存储器。此外,闪速存储器13也可以是如NOR型那样的其他闪速存储器。存储卡10例如也可以具有层叠的多个闪速存储器13。

卡控制器14能够对闪速存储器13和包括该闪速存储器13的存储卡10的整体进行控制。例如,卡控制器14能够进行向闪速存储器13的读/写控制以及与外部的通信控制。该通信控制包括与PCIe(Peripheral Component Interconnect express)标准(以下简称为PCIe)对应的协议控制。此外,卡控制器14也可以经由对闪速存储器13进行控制的其他电子部件来间接地对闪速存储器13进行控制。

保护片15贴附于第1面21。保护片15例如封住露出于第1面21的测试用的端子。此外,保护片15不限于该例子。

存储卡10还具有多个端子P。在本实施方式中,存储卡10具有26个端子P。此外,端子P的数量不过是一个例子,不限于该例子。即,端子P的数量既可以比26个少,也可以比26个多。多个端子P例如设置于基板12。多个端子P为贴附于第1面21的金属板。在本实施方式中,第2面22不设置端子P,例如可以被利用为印刷面、散热面。

在本实施方式中,多个端子P排列为两列,形成第1列R1和第2列R2。此外,多个端子P也可以排列为三列以上,形成多个第2列R2。

13个端子P相互隔着间隔而排列在X轴方向上,形成第1列R1。以下,有时将形成第1列R1的13个端子P分别地称为端子P1~P13。此外,形成第1列R1的端子P的数量不限于13个。形成第1列R1的端子P从最靠近第2边缘32的端子P1开始依次排列到最靠近第3边缘33的端子P13。

端子P1~P13在第1边缘31的附近沿着该第1边缘31而在X轴方向上排列。端子P1~P13以及由端子P1~P13形成的第1列R1离开第1边缘31。但是,第1列R1与第1边缘31之间的距离比第1列R1与第4边缘34之间的距离短。此外,端子P1~P13以及第1列R1也可以与第1边缘31相邻。

13个端子P相互隔着间隔而在X轴方向上排列,形成第2列R2。以下,有时将形成第2列R2的13个端子P分别地称为端子P14~P26。此外,形成第2列R2的端子P的数量不限于13个。另外,形成第2列R2的端子P的数量既可以比形成第1列R1的端子P的数量多,也可以比形成第1列R1的端子P的数量少。形成第2列R2的端子P从最靠近第2边缘32的端子P14开始依次排列到最靠近第3边缘33的端子P26。

形成第2列R2的多个端子P与第1列R1相比,排列在距第1边缘31远的位置。因此,第2列R2与第1列R1相比,距第1边缘31远。第1列R1和第2列R2隔着间隔而在Y轴方向上排列。

如上述那样,多个端子P在X轴方向上排列。在该情况下,一个端子P的至少一部分在Y轴方向上位于相邻的其他端子P的Y轴的正方向上的端部与Y轴的负方向上的端部之间的区域。在第1列R1和第2列R2各自中,一个端子P既可以相比于其他端子P的Y轴的正方向上的端部而向Y轴的正方向伸出,也可以相比于其他端子P的Y轴的负方向上的端部而向Y轴的负方向伸出。即,各端子P的位置也可以在Y轴方向上错开。通过将相同的列R1、R2的各端子P的Y轴的负方向上的端部对齐,能够在使连接器的接触位置在Y轴方向上对齐了的情况下使各端子P的电气特性相似。

多个端子P也可以具有互不相同的形状。例如,在第1列R1中,端子P1、P4、P7、P10、P13的形状与端子P2、P3、P5、P6、P8、P9、P11、P12的形状互不相同。进一步,在第2列R2中,端子P14、P17、P18、P19、P21、P24、P25的形状与端子P15、P16、P20、P22、P23、P26的形状互不相同。进一步,在本实施方式中,在第1列R1和第2列R2各自中,多个端子P之间的距离大致为一定。但是,多个端子P之间的距离也可以不同。在沿Y轴方向安装的连接器中,作为存储卡10的电源端子、接地端子的端子P1、P4、P7、P10、P13、P14、P17、P18、P19、P21、P24、P25被设定为比作为信号端子的端子P2、P3、P5、P6、P8、P9、P11、P12、P15、P16、P20、P22、P23、P26长。由此,连接器与电源端子以及接地端子最先接触,因此,在电气上变得稳定,能够避免对信号端子给与电应力。当在对卡控制器14供给电源之前电压被施加于信号端子时,会对后述的接口电路51的输入缓存施加电应力。

对多个端子P分配在遵循预定的接口标准的通信中所使用的信号。但是,也可以对多个端子P分配在遵循多个接口标准的通信中所使用的信号。

图3是表示第1实施方式的多个端子P的信号分配的一个例子的例示性表。如图3所示,在本实施方式中,对第1列R1的多个端子P分配在PCIe的数据通信中所使用的信号。在PCIe中,能够在数据的通信中使用差分数据信号对。

在第1列R1中,对端子P1、P4、P7、P10、P13分配接地电位的接地(GND),对端子P2、P3、P8、P9分配接收差分信号PERp0、PERn0、PERp1、PERn1,对端子P5、P6、P11、P12分配发送差分信号PETp0、PETn0、PETp1、PETn1。

端子P1、P4、P7、P10、P13是接地端子的一个例子。接收差分信号PERp0、PERn0、PERp1、PERn1和发送差分信号PETp0、PETn0、PETp1、PETn1是信号和差分数据信号的一个例子。端子P2、P3、P5、P6、P8、P9、P11、P12是信号端子、第1信号端子以及差分数据信号端子的一个例子。

被分配了接收差分信号PERp0、PERn0的一对端子P2、P3位于两个端子P1、P4之间,由两个端子P1、P4包围。被分配了发送差分信号PETp0、PETn0的一对端子P5、P6位于两个端子P4、P7之间,由两个端子P4、P7包围。

被分配了接收差分信号PERp1、PERn1的一对端子P8、P9位于两个端子P7、P10之间,由两个端子P7、P10包围。被分配了发送差分信号PETp1、PETn1的一对端子P11、P12位于两个端子P10、P13之间,由两个端子P10、P13包围。

在PCIe中进行数据的串行传输,但为了使得能在接收电路生成时钟、并避免因在数据中相同的逻辑电平连续而电压电平偏向高电平或者低电平,被按某单位进行编码。编码使用8B10B、128b/130b等的方式。能够通过该编码使数据传输时的平均信号电压电平为通用电压附近,能够减少从接收阈值电平的偏移。另外,通过接收侧根据数据的变化点生成接收时钟,能够生成追随于数据的时间性的变动的接收时钟,因此,能够实现稳定的数据接收。即使是在多个通道(差分数据信号的向上向下的对)间存在偏移的情况下,通过分别按通道独立地构成接收电路来使接收数据的开始位置对齐,能够消除通道间偏离。

例如,PCIe 3.0的情况下的最大传送速度为每1个通道2G字节/秒(向上向下的合计)。在PCIe中,能够由一组发送差分信号PETp0、PETn0和接收差分信号PERp0、PERn0构成1个通道。另外,在PCIe中,能够由一组发送差分信号PETp1、PETn1和接收差分信号PERp1、PERn1进一步构成1个通道。这样,对形成第1列R1的多个端子P分配2个通道,因此,能够使PCIe的通道数量增大,能够使数据传送速度提高。

在PCIe中,能够在初始化时对多个通道结构进行识别,用多个通道传送一个数据。此外,在主机设备不支持(对应)多个通道的情况下,存储卡10能够在1个通道模式下进行动作。

端子P2、P3、P5、P6、P8、P9、P11、P12进行遵循PCIe的差分数据信号的传输,能够进行双向通信。端子P2、P3、P5、P6、P8、P9、P11、P12传输频率为GHz频带的差分数据信号。

在PCIe的通信控制中所使用的控制信号被分配给第2列R2的多个端子P。在第2列R2中,对端子P14、P17分配GND,对端子P15、P16分配参考差分时钟信号REFCLKp、REFCLKn,对端子P18、P19分配第2电源(功率轨(power rail))PWR2,对端子P20分配复位信号PERST#,对端子P21分配第1电源(功率轨)PWR1,对端子P22分配功率管理控制信号CLKREQ#,对端子P23、P26分配控制信号CNTA、CNTB,对端子P24、P25分配第3电源(功率轨)PWR3。

端子P15、P16、P20、P22、P23、P26是信号端子和第2信号端子的一个例子。端子P15、P16是差分时钟信号端子的一个例子。端子P20、P22、P23、P26是单端信号端子的一个例子。端子P20、P22是边带信号端子的一个例子。端子P18、P19、P21、P24、P25是电源端子的一个例子。端子P18、P19是第2电源端子的一个例子。P21是第1电源端子的一个例子。端子P24、P25是第3电源端子的一个例子。通过设置多个端子P来作为电源端子,电流分散,在平均每一个端子中流动的电流变小,能够减小由在从电源电路到电源端子之间存在的电阻成分导致的下降电压。

参考差分时钟信号REFCLKp/n由两条构成差分时钟信号。通过从主机设备向端子P15、P16传输频率为MHz频带的时钟信号,存储卡10能够使与安装有该存储卡10的主机设备的同步变得容易。这样,通过端子P15、P16使用于传输的时钟信号的频率比端子P2、P3、P5、P6、P8、P9、P11、P12使用于传输的差分数据信号的频率低,并设为接近正弦波的波形,能够降低EMI的产生。

主机设备例如是如个人计算机那样的信息处理装置、便携电话机、数字相机、拍摄装置、如平板计算机和/或智能手机那样的便携终端、游戏设备、如车辆导航系统那样的车载终端或者其他装置。

存储卡10用PLL振荡电路使所接收到的参考差分时钟倍增来生成位(bit,比特)时钟。与位时钟同步地从发送差分信号PETp0、PETn0、PETp1、PETn1输出数据。从接收差分信号PERp0、PERn0、PERp1、PERn1读入的数据与位时钟同步地对齐来作为一个数据。也即是,能够通过根据所述代码生成的接收时钟来使暂时接收到的数据与参考差分时钟进行再同步。

复位信号PERST#能够用于主机设备对PCIe的通信中所使用的总线进行复位。通过PCIe的复位解除的定时规定来规定PCIe差分通道的初始化开始定时。该复位信号PERST#能够在产生错误时等主机设备进行存储卡10的再初始化时进行使用。

功率管理控制信号CLKREQ#可以作为用于从功率节省模式恢复的时钟来使用。在功率节省模式中,通过使在数据传送中所使用的高频位时钟停止,能够减少功耗。

控制信号CNTA、CNTB能够用于对各种功能进行控制。例如如后述的那样,能够使用控制信号CNTB以判别PCIe的初始化是需要电源电压PWR3、还是需要电源电压PWR2、或者是能够仅用电源电压PWR1进行动作。

复位信号PERST#、功率管理控制信号CLKREQ#以及控制信号CNTA、CNTB是单端信号。另外,复位信号PERST#和功率管理控制信号CLKREQ#是PCIe的边带信号。

通过存储卡10支持PCIe的通信,能够使用PCIe的标准的物理层(PHY:PhysicalLayer)。因此,能够谋求用于提高存储卡10的数据传送速度的设计的容易化和开发成本的降低。

进一步,通过存储卡10支持PCIe的通信,能够在PCIe的数据链层采用NVMe(NonVolatile Memory express)。因此,能够使数据传送时的开销降低,能够使数据传送效率提高。

主机设备能够向端子P21供给作为第1电源的电源电压PWR1。电源电压PWR1在本实施方式中被设定为3.3V。电源电压标记表示中央值,容许某程度的电压变动幅度。电源电压PWR1例如可以被设定在2.5V以上且3.3V以下的范围内,但不限定于该例子。

主机设备能够向端子P18、P19供给作为第2电源的电源电压PWR2。电源电压PWR2是第2电源电压的一个例子。电源电压PWR2在本实施方式中被设定为1.8V。即,电源电压PWR2为电源电压PWR1以下。电源电压PWR2例如可以被设定在1.2V以上且1.8V以下的范围内,但不限于该例子。

主机设备能够向端子P24、P25供给作为第3电源的电源电压PWR3。电源电压PWR3是第1电源电压的一个例子。电源电压PWR3在本实施方式中被设定为1.2V。即,电源电压PWR3为电源电压PWR2以下。电源电压PWR3不限于该例子。

图4是示意性地表示第1实施方式的存储卡10的布线的例示性俯视图。如图4所示,卡控制器14位于第1列R1与第2列R2之间。此外,卡控制器14也可以配置在其他位置,例如位于第1列R1所包括的端子P的Y轴的正方向上的端部与第2列R2所包括的端子P的Y轴的负方向上的端部之间。另外,卡控制器14也可以配置为:第2列R2所包括的端子P位于该卡控制器14的Y轴的正方向上的端部与Y轴的负方向上的端部之间。

卡控制器14具有多个连接端子CP。多个连接端子CP是被分配了接收差分信号PERp0、PERn0、PERp1、PERn1以及发送差分信号PETp0、PETn0、PETp1、PETn1的卡控制器14的端子。多个连接端子CP设置在卡控制器14的一部分的边14a,位于第1列R1与第2列R2之间。连接端子CP优选配置为该连接端子CP与端子P之间的布线不交叉。

存储卡10还具有多条布线W、多个接地面(Ground plane)41、多条电源布线42以及多个ESD保护二极管43。为了说明,图4示意性地将卡控制器14、端子P、布线W、接地面41、电源布线42、ESD保护二极管43表示于同一平面。另外,为了说明,图4对接地面41和电源布线42标上阴影线。

在本实施方式中,多个端子P被分配为使得多条布线W、多个接地面41以及多条电源布线42互不重叠。因此,布线W、接地面41、电源布线42以没有过孔的方式被高效地进行布线。

多条布线W包括将卡控制器14的连接端子CP与端子P2、P3、P5、P6、P8、P9、P11、P12连接的布线W2、W3、W5、W6、W8、W9、W11、W12。进一步,多条布线W包括将卡控制器14与端子P15、P16、P20、P22、P23、P26连接的布线W15、W16、W20、W22、W23、W26。

布线W2、W3、W5、W6、W8、W9、W11、W12的长度被设定为相互相等。进一步,布线W2、W3、W5、W6、W8、W9、W11、W12相对于经过端子P7的中心来在Y轴方向上延伸的中心轴Ax被配置为镜面对称。因此,布线W2、W3、W5、W6、W8、W9、W11、W12的设计变得容易。另外,布线W15、W16的长度被设定为相互相等。

布线W2、W3、W5、W6、W8、W9、W11、W12布线为等长,消除线间偏离。为了调整长度,需要使布线弯曲,但通常难以用平滑的曲线引出图案,因此,在改变布线方向时,多个部位弯曲为45°,而不是90°。布线W的宽度在弯曲部分稍微会变宽,会引起特性阻抗的变化,会从那里产生噪声。相比于90°,45°时的宽度的变动少,因此,能抑制噪声的产生。

多个接地面41包围布线W2、W3、W5、W6、W8、W9、W11、W12、W15、W16。根据其他表现,布线W2、W3、W5、W6、W8、W9、W11、W12、W15、W16在多个接地面41之间通过。由此,能够按各差分信号确保返回路径,能减少差分信号间的相互干扰,工作信号电平稳定化。

电源布线42连接于端子P18、P19、P21、P24、P25。电源布线42的宽度比布线W的宽度宽。因此,能够在电源布线42中流动的电流变大,并且,能高效地进行经由了电源布线42的散热。另外,存储卡10能从多个端子P进行散热。

在主机电源输出与存储卡端子之间存在布线、连接器的电阻成分、电感成分,因此,会产生电压降。在电源电压的容许变动范围相对于电源电压为一定比例的情况下,电压越低,容许电压变动幅度越小。因此,由于存在所述电压降,所以电源电压越低则越难以对电源电压进行控制以使得从主机设备到卡端子的电源电压收于容许电压变动幅度内。

另一方面,若为同一基板、同一连接器,则主机设备的连接器、包括电源布线42的布线的电阻值与电压无关地为相同的电阻值。因此,当电源电压低时,能够在一个端子P流动的电流值变小。

在本实施方式中,电源电压PWR2在两个端子P18、P19中流动。进一步,电源电压PWR3在两个端子P24、P25中流动。这样,通过对多个端子P18、P19、P24、P25分配电流,平均每一个端子P的电流值被减小,能够减小由电源布线42、主机设备的连接器的电阻成分引起的下降电压。因此,主机设备容易使电源电压收于容许电压变动幅度内。进一步,通过电源电压PWR2、PWR3设定为相同的电压,能够供给更大的电流。

另外,通常PWR1为3.3V±5%、PWR2为1.8V±5%,但如上述的那样,也可以为:电源电压PWR1被设定在如2.5-5%~3.3V+5%那样在下侧更宽的电压范围内,电源电压PWR2被设定在如1.2-5%~1.8V+5%那样在下侧更宽的电压范围内。由此,能够降低电压来减少功耗。

ESD保护二极管43将布线W2、W3、W5、W6、W8、W9、W11、W12各自与接地面41连接。ESD保护二极管43配置在端子P与连接端子CP之间,对从端子P2、P3、P5、P6、P8、P9、P11、P12侵入的静电进行吸收。

通过多个连接端子CP位于第1列R1与第2列R2之间,布线W2、W3、W5、W6、W8、W9、W11、W12能够设定为:不绕过其他布线和/或其他部件、不在第2列R2所包括的多个端子P之间通过。因此,能够缩短布线W2、W3、W5、W6、W8、W9、W11、W12的长度,并且,能够有效地配置ESD保护二极管43。在本实施方式中,ESD保护二极管43被配置在第1列R1所包括的端子P的附近。

存储卡10安装于主机设备的连接器。例如,存储卡10通过被插入到推拉类型的连接器的插槽,从而被安装于该连接器。此外,存储卡10也可以安装于其他类型的连接器。

本实施方式的存储卡10被从设置有缺口C的图1的第1边缘31插入到连接器的插槽。由此,在存储卡10安装于了连接器的状态下,第1边缘31与第4边缘34相比,位于连接器的靠进深侧的位置。

通过第1角部35在第1边缘31与第2边缘32之间形成缺口C,防止存储卡10被表里颠倒地插入到连接器的插槽。例如,当存储卡10被以正确的朝向插入到连接器的插槽时,用缺口C避开连接器内部的部件。另一方面,当存储卡10被表里颠倒地插入到连接器的插槽时,连接器内部的部件例如与第2角部36干涉,会妨碍存储卡10完全插入。另外,在Y轴方向上反向地将存储卡10从第4边缘插入到了连接器时,存储卡10也同样地无法安装于连接器。通过X轴方向上的边缘和Y轴方向上的边缘在形成于第1边缘31与第3边缘33之间的第2角部36附近紧贴于连接器,能够减少连接器与存储卡10的旋转方向上的错开。

当存储卡10被插入到连接器时,连接器的引线架与多个端子P分别接触。在存储卡10设置有倾斜部39,存储卡10的前端为锥状。因此,引线架能够被倾斜部39进行引导,例如,能减少引线架与壳体11之间的摩擦。因此,能抑制引线架的镀层剥离,连接器的耐磨耗性提高。

当引线架与端子P接触时,主机设备的控制器(以下称为主机控制器)和存储卡10的卡控制器14经由主机设备的布线、存储卡10的布线W而电连接。

如用于安装到主机设备的基板的连接器的端子那样的、连接器的主机控制器侧的连接点,一般设置在连接器的插槽的进深侧(图1的上方向)。因此,形成第1列R1的端子P和引线架的接触点与主机控制器之间的布线的长度容易被设为更短。另一方面,例如由于要绕过第1列R1,因此,形成第2列R2的端子P和引线架的接触点与主机控制器之间的布线的长度容易变得更长。

在本实施方式的存储卡10中,在到主机控制器为止的布线长更短的第1列R1包括进行高速的差分数据信号的传输的端子P2、P3、P5、P6、P8、P9、P11、P12。由此,主机设备的物理层(PHY)与存储卡10的物理层(PHY)变近,容易在存储卡10的差分数据信号的传输中确保信号完整性。

图5是概略地表示第1实施方式的存储卡10的结构的第1例的例示性框图。卡控制器14具有接口电路(I/F)51、物理层及存储器控制器52、两个调节器(regulator)53、54以及电源检查电路55。卡控制器14的物理层及存储器控制器52在图5中表示为一个框,并且,以下也一体地进行说明。

I/F51能够应对单端信号。在I/F51例如设置有输入缓存和输出缓存。能够从端子P20、P22、P23对输入缓存输入复位信号PERST#、功率管理控制信号CLKREQ#以及控制信号CNTA。输出缓存能够通过端子P22、P26输出对于功率管理控制信号CLKREQ#的响应和控制信号CNTB。

物理层及存储器控制器52能够应对差分信号。在物理层及存储器控制器52设置有接收器和发送器。能够对接收器输入接收差分信号PERp0、PERn0、PERp1、PERn1。发送器能够输出发送差分信号PETp0、PETn0、PETp1、PETn1。

物理层及存储器控制器52和电源检查电路55连接于I/F51。物理层及存储器控制器52连接于闪速存储器13。在卡控制器14,除了PCIe的物理层之外,也可以设置PCIe的数据链层和事务(transaction)层。

物理层及存储器控制器52能够进行串行/并行变换、并行/串行变换以及数据的符号化等。该符号化是如下处理:在数据的0或者1连续时,从所述8B10B、128b/130b等的代码中置换为0的总数和1的总数相同或者接近、且0或者1不连续某数量以上的符号。通过该符号化,能够使平均信号电压电平为通用电压附近,能够抑制从接收阈值电平的偏移。另外,当反复传送同一符号模式时,特定频率的高次谐波会变大,但通过切换为模式不同的多个符号以使得不成为重复模式,能够使得特定频率的高次谐波不变大。也即是,能够抑制EMI(Electro Magnetic Interference,电磁干扰)的产生。

此外,在PCIe的事务层中,能够对数据进行封包、对包头附加命令等。在PCIe的数据链层中,能够对从事务层接受到的包附加序列编号、附加CRC(Cyclic RedundancyCheck,循环冗余校验)码。序列编号能够使用于包的送达确认等。

当从主机设备向存储卡10发送串行的接收差分信号PERp0、PERn0、PERp1、PERn1时,用接收器变换为并行数据的接收信号。当向发送器发送并行数据的发送信号时,该发送信号被变换为串行的发送差分信号PETp0、PETn0、PETp1、PETn1,并被发送给主机设备。

电源电压PWR1被供给至闪速存储器13和卡控制器14。在本实施方式中,电源电压PWR1被使用于如闪速存储器13的读/写那样的闪速存储器13的动作。

如上述那样,电源电压PWR1为电源电压PWR2以上且电源电压PWR3以上。电源电压PWR1能够满足闪速存储器13的写入电压。

在主机设备和存储卡10以3.3V信号电压相连接的情况下,对I/O电源使用电源电压PWR1。即使在如图5的例子那样主机设备和存储卡10以1.8V信号电压相连接的情况下,电源电压PWR1也可以被作为I/O电源来使用。由此,存储卡10实现高耐压化,卡输入电路得到保护。例如当电源电压PWR1被设定为2.5V时,存储卡10可以设为2.5V耐压,若电源电压PWR1被设定为3.3V,则存储卡10可以设为3.3V耐压。

电源电压PWR2被供给至闪速存储器13和卡控制器14。在本实施方式中,电源电压PWR2被作为逻辑电路的电源来使用。另外,电源电压PWR2也被作为闪速存储器13与卡控制器14之间的接口电压来使用。

在主机设备和存储卡10以1.8V信号电压相连接的情况下,也可以对I/O电源使用电源电压PWR2。在该情况下,存储卡10可以被设为1.8V耐压。

电源电压PWR3被供给至卡控制器14。在本实施方式中,电源电压PWR3被作为差分信号电路的物理层(PHY)、模拟电路的电源来使用。

一般而言,对进行模拟动作的差分信号电路使用噪声少的电源,与数字电源分离。在本实施方式中,从主机设备供给的电源电压PWR3需要为足够稳定化而噪声少的电源。

如上所述,在存储卡10中,为了降低噪声、电源变动的影响,三个电源电压PWR1、PWR2、PWR3被相分离地进行供给。即,根据用途来分开使用三个电源电压PWR1、PWR2、PWR3。

图6是概略性地表示第1实施方式的存储卡10的结构的第2例的例示性框图。如图6所示,电源电压PWR2也可以被供给至调节器53、54。进一步,被分配了电源电压(第3电源)PWR3的端子P24、P25也可以被设为接地电平。这是使用以电源电压PWR1和电源电压PWR2这两个电源进行动作的存储卡10的情况。

如图6的例子那样,调节器54生成比所输入的电源电压PWR2低的电源电压Vlogic。该电源电压Vlogic也可以代替电源电压PWR2而被供给至闪速存储器13和卡控制器14的物理层及存储器控制器52。电源电压Vlogic被作为逻辑电路的电源来使用,并且,也被作为闪速存储器13与卡控制器14之间的接口电压来使用。通过降低接口电压,能够在闪速存储器13与卡控制器14之间高速地进行数据传送,功耗也被降低。一般而言,信号电压低时能够缩短信号的上升/下降时间,因此,能够进行高速的数据传输。

如图6的例子那样,当端子P24、P25被接地连接时,调节器53从被输入的电源电压PWR2生成比该电源电压PWR2低的电源电压PWR3。在由于环境等的理由而难以从主机设备供给稳定的电源电压PWR3的情况下,通过使用由调节器53生成的电源电压PWR3,能够消除问题。

电源电压PWR3、Vlogic都是从电源电压PWR2生成的。电源电压PWR3和电源电压Vlogic既可以是彼此相同的电压,也可以是互不相同的电压,但为了使得电源分离而相互不影响,用各自分开的调节器53和调节器54来生成电源电压。另外,通过使用LDO(Low DropOut,低压差)来作为调节器53、54,能够降低由输入输出电压差引起的白费(无谓)的功耗。

如由图6的虚线所示,也可以为:调节器53从电源电压PWR1生成电源电压PWR3,调节器54从电源电压PWR1生成电源电压Vlogic。即,若存在电源电压PWR1,则存储卡10能够进行动作。

如上所述,存储卡10能够利用施加于端子P18、P19、P21、P24、P25的电源电压PWR1、电源电压PWR1、PWR2、或者电源电压PWR1、PWR2、PWR3进行动作。存储卡10也可以为:能够根据施加于端子P18、P19、P21、P24、P25的电源电压PWR1、PWR2、PWR3的组合,对电源模式进行切换。

主机设备通过以下的电源检查序列取得保存于闪速存储器13的存储卡10的电源规格信息13a,由此能够应对存储卡10的电源结构。电源规格信息13a例如包括电源电压PWR1、PWR2、PWR3的电压范围、最大电流(连续)以及峰值电流(100μ秒区间)。

图7是表示第1实施方式的存储卡10的电源检查序列中的主机设备的动作的例示性流程图。在主机设备从闪速存储器13取得电源规格信息13a之前,进行PCIe的初始化。因此,主机设备在电源检查序列中判定是否能够以所供给的电源电压PWR1、PWR2、PWR3的组合开始初始化。

如图7所示,主机设备向被插入到连接器的插槽的存储卡10的端子P18、P19供给(施加)电源电压PWR2(S1)。

如图5所示,对电源检查电路55输入电源电压PWR2。电源检查电路55在能够通过所施加的电源电压PWR2开始PCIe的初始化的情况下,驱动为CNTB=High(高电平)。设想为:在该时间点未供给PWR1,但在开始初始化之前供给PWR1。

电源检查电路55在无法通过所施加的电源电压PWR2开始PCIe的初始化的情况下,设为保持CNTB=Low(低电平)不变。

主机设备在经过一定时间Tpok后(S2),对控制信号CNTB的电平进行检查(S3)。电源检查电路55能够在时间Tpok的期间将控制信号CNTB的电平从Low切换为High。因此,主机设备在经过时间Tpok后进行一次的控制信号CNTB的电平的检查即可。在保持CNTB=Low不变的情况下(S3:否),主机设备向存储卡10的端子P24、P25供给(施加)电源电压PWR3(S4)。

电源检查电路55在能够通过所施加的电源电压PWR3开始PCIe的初始化的情况下,驱动为CNTB=High。设想为:在该时间点未供给PWR1,但在开始初始化之前供给PWR1。另一方面,电源检查电路55在无法通过所施加的电源电压PWR3开始PCIe的初始化的情况下,设为保持CNTB=Low不变。例如,电源检查电路55在能够通过电源电压PWR1开始PCIe的初始化的情况下,设为保持CNTB=Low不变。

主机设备在经过一定时间Tpok后(S5),对控制信号CNTB的电平进行检查(S6)。在保持CNTB=Low不变的情况下(S6:否),主机设备按与施加相反的顺序使电源电压PWR3为断开(off)(S7),使电源电压PWR2为断开(S8)。在该例子中,使卡不使用的电源断开,但卡的未使用电源也可以保持接通的状态不变。

在控制信号CNTB的电平检查时为CNTB=High的情况下(S3:是、S6:是)、或者使电源电压PWR2为断开的情况下(S8),主机设备向存储卡10的端子P21供给(施加)电源电压PWR1(S9)。也即是,在开始初始化之前,电源电压PWR1总是被供给。

如上述那样,在未对端子P21施加电源电压PWR1的情况下,输出到端子P26的控制信号CNTB被使用于电源检查电路55的结果的输出。当电源检查电路55检测到电源电压PWR1时,存储卡10能够将向端子P26所输出的CNTB切换为其他用途的输出信号。另外,控制信号CNTB被以电源电压PWR2的信号电压进行输出,因此,在电源检查序列中,最先施加电源电压PWR2。

接着,主机设备执行PCIe的训练序列(S10)。通过该训练序列,进行物理层的检测、物理层的训练等,主机设备和存储卡10能够进行通信,成为能够进行MMIO寄存器读出的状态。

图8是表示第1实施方式的电源规格信息13a的一个例子的例示性表。图8所例示的电源规格信息13a是作为电源要求规格所记载的寄存器信息,如上述那样包括电源电压PWR1、PWR2、PWR3的电压范围、最大电流(连续)以及峰值电流(例如100μ秒区间)。

最大电流(连续)是在存储卡10的存储器访问时所被使用的连续电流值。主机设备的电源电路被要求连续地供给该电流值。

峰值电流(100μ秒区间)例如是在以100μ秒区间进行了测定的情况下所流动的峰值电流值,受到主机设备的电源设定下的耦合电容器的容量、电源电路的响应特性的影响。主机设备的电源电路被要求能够供给该峰值电流。

电压范围是电源电压被容许变动的范围。主机设备的电源电路被要求:即使存在布线、连接器的下降电压,也保持电压以使得端子P处的电源电压落在该电压范围内。

进一步,电源规格信息13a包括表示是否由调节器53生成电源电压PWR3的信息。如上述那样,调节器53在未对端子P24、P25施加电源电压PWR3的情况下,能够从电源电压PWR2生成电源电压PWR3。此外,存储卡10即使具有调节器53,也可以使用已施加于端子P24、P25的电源电压PWR3。

如图7所示,主机设备从闪速存储器13读出电源规格信息13a(S11)。电源规格信息13a例如配置在MMIO上所映射的NVMe寄存器的Vendor Specific区域,经由物理层及存储器控制器52被以差分数据信号进行输出。主机设备通过对差分数据信号进行解码,在系统存储器上复原电源规格信息13a。

主机设备对所读出的电源规格信息13a的电源要求规格和该主机设备的电源电路规格进行比较,判断存储卡10是否能够使用(S12)。在主机设备满足全部的电源要求规格的情况下(S12:是),主机设备安装了用于访问闪速存储器13的足够的电源电路,因此,判断为存储卡10能够使用(S13)。

在主机设备不满足电源要求规格的情况下(S12:否),主机设备判断是否能够进行电源电压PWR1、PWR2、PWR3的调解(调停)(S14)。例如在电源电压PWR1不足的情况下,若通过用由PCIe定义的Slot Power Limit(插槽功率限制)对最大电力进行限制而能够使用存储卡10(S14:是),则主机设备进行该调解(S15),判断为存储卡10能够使用(S13)。另一方面,在无法调解的情况下(S14:否),主机设备不使用存储卡10(S16)。

存储卡10能够安装多个电力模式。例如,如上述那样,存储卡10能够安装SlotPower Limit(最大功耗的上限设定功能)。

主机设备根据电源能力,用PCIe包(packet)对存储卡10设定能够使用的SlotPower Limit。例如如图8所示,本实施方式的存储卡10是支持了三个Slot Power Limit的例子。此外,存储卡10不限于该例子。峰值电流不依赖于Slot Power Limit,因此,成为共用的设定。

Slot Power Limit A的功耗比Slot Power Limit B的功耗大。另外,Slot PowerLimit B的功耗比Slot Power Limit C的功耗大。功耗越大,性能越高。在主机设备的电源电路不满足Slot Power Limit A的情况下,通过设定为Slot Power Limit B,主机设备能够使用存储卡10。Slot Power Limit的选择项例如由其他PCIe寄存器提供。

图9是表示第1实施方式的存储卡10的电源检查序列中的第1例的例示性时序图。以下,参照图7和图9对电源检查序列中的第1例进行说明。该第1例涉及的存储卡10能够通过使用电源电压PWR3来开始PCIe的初始化。另外,在图9中,对与图7的各动作对应的定时赋予与该图7对应的标号。

首先,主机设备向存储卡10的端子P18、P19供给电源电压PWR2(S1)。存储卡10的初始化使用电源电压PWR3,因此,即使经过一定时间Tpok(S2),控制信号CNTB的电平也保持Low不变(S3:否)。因此,主机设备向存储卡10的端子P24、P25供给电源电压PWR3(S4)。

通过供给电源电压PWR3,成为CNTB=High。因此,在经过一定时间Tpok后(S5),在CNTB的电平检查时成为CNTB=High(S6:是),因此,主机设备向端子P21供给电源电压PWR1(S9)。也即是,主机能够识别为是需要3个电源的存储卡10。

图10是表示第1实施方式的存储卡10的电源检查序列中的第2例的例示性时序图。以下,参照图7和图10对电源检查序列中的第2例进行说明。该第2例涉及的存储卡10能够通过调节器53从电源电压PWR2生成电源电压PWR3,能够通过使用电源电压PWR2来开始PCIe的初始化。

首先,主机设备向存储卡10的端子P18、P19供给电源电压PWR2(S1)。通过被供给电源电压PWR2,成为CNTB=High。因此,在经过一定时间Tpok后(S2),在CNTB的电平检查时成为CNTB=High(S3:是),因此,主机设备向端子P21供给电源电压PWR1(S9)。时间Tpok例如被设定为足够让调节器53所生成的电源电压PWR3稳定的时间。也即是,主机能够识别为是需要PWR1和PWR2这两个电源的存储卡10。

图11是表示第1实施方式的存储卡10的电源检查序列中的第3例的例示性时序图。以下,参照图7和图11对电源检查序列中的第3例进行说明。该第3例涉及的存储卡10能够通过调节器53从电源电压PWR1生成电源电压PWR3,能够通过使用电源电压PWR1来开始PCIe的初始化。

首先,主机设备向存储卡10的端子P18、P19供给电源电压PWR2(S1)。存储卡10的初始化使用电源电压PWR1,因此,即使经过一定时间Tpok(S2),控制信号CNTB的电平也保持Low不变(S3:否)。

主机设备向存储卡10的端子P24、P25供给电源电压PWR3(S4)。即使经过一定时间Tpok(S5),控制信号CNTB的电平也保持Low不变(S6:否)。因此,主机设备使电源电压PWR3(S7)、电源电压PWR2断开(S8),向端子P21供给电源电压PWR1(S9)。也即是,主机能够识别为是需要PWR1这一个电源的存储卡10。当被供给电源电压PWR1时,存储卡10中,电源检查电路55的输出被切断,不向被分配了控制信号CNTB的端子P26进行输出,但控制信号CNTB可以作为其他用途的信号来使用。

为了对闪速存储器13进行高速访问,有时使用大的电流。但是,通过PCIe的初始化所消耗的电流比用于进行高速访问的电流少就可以了。因此,即使安装最低限度的电源,也能够读出所述电源规格信息13a。

在以上的电源检查序列中,存储卡10的卡控制器14判定是否能够利用施加于端子P18、P19、P21、P24、P25的电源电压PWR1、PWR2、PWR3进行基于差分数据信号的PCIe的初始化,从端子P26输出判定结果。进一步,闪速存储器13中,当基于差分数据信号的PCIe的初始化完成时,记录于该闪速存储器13的电源规格信息13a成为能够读出。

通过以上的电源检查序列,即使混合存在具有各自不同的电源规格的多个种类的存储卡10,主机设备也能够识别该电源规格。此外,通过预先确定存储卡10和所对应的主机设备的电源规格,能够省略电源检查序列。

主机设备例如具有对存储卡10相对于连接器的插拔进行检测的功能。在该情况下,主机设备在检测到存储卡10向连接器的插入之后将电源接通,当检测到从连接器拔下了存储卡10时,使电源断开。因此,存储卡10能够省略关于热插拔的功能。

在以上说明的第1实施方式涉及的存储卡10中,壳体11具有在X轴方向上延伸的第1边缘31、在与X轴方向交叉的Y轴方向上延伸的第2边缘32以及形成第1边缘31与第2边缘32之间的缺口C的第1角部35。形成缺口C的第1角部35例如被使用于防止存储卡10插反。因此,在存储卡10例如被插入到推拉类型的连接器的情况下,存储卡10被从第1边缘31插入到连接器。并且,多个端子P相互隔着间隔而在X轴方向上排列来形成第1列R1,并且,多个端子P在与第1列R1相比、距第1边缘31远的位置,相互隔着间隔而在X轴方向排列来形成第2列R2。这样,通过多个端子P形成多个列R1、R2,本实施方式的存储卡10能够使通信接口高速化。

一般而言,越是连接器的进深侧,被插入到了连接器的存储卡10的端子P与主机控制器之间的布线的长度越短。即,第1列R1所包括的端子P与主机控制器之间的布线的长度比第2列R2所包括的端子P与主机控制器之间的布线的长度短。因此,第1列R1所包括的被使用于传输信号的端子P2、P3、P5、P6、P8、P9、P11、P12比第2列R2所包括的被使用于传输信号的端子P15、P16、P20、P22、P23、P26容易确保信号完整性。例如,通过使第1列R1所包括的被使用于传输信号的端子P的数量比第2列R2所包括的被使用于传输信号的端子P的数量多、在差分信号的传输中使用第1列R1所包括的端子P,本实施方式的存储卡10能够使通信接口高速化。

第1列R1所包括的端子P2、P3、P5、P6、P8、P9、P11、P12的数量比第2列R2所包括的端子P15、P16、P20、P22、P23、P26的数量多。由此,本实施方式的存储卡10能够使通信接口高速化。

进一步,多个端子P形成第1列R1和第2列R2。由此,与将多个端子P排列为一列的情况相比,即使为在第1边缘31的附近排列了更多的被使用于传输信号的端子P2、P3、P5、P6、P8、P9、P11、P12,也能够确保端子P的所希望的大小、多个端子P的所希望的间隔。

被使用于传输频率比端子P15、P16、P20、P22、P23、P26的信号的频率高的信号的端子P2、P3、P5、P6、P8、P9、P11、P12包括于第1列R1。由此,本实施方式的存储卡10能够使通信接口高速化。

通过增加差分数据信号端子、增加通道数量,本实施方式的存储卡10能够使通信接口高速化。

形成第1列R1的多个端子P包括被分配了差分数据信号的端子P2、P3、P5、P6、P8、P9、P11、P12。另一方面,形成第2列R2的多个端子P包括:被分配了频率比差分数据信号的频率低的差分时钟信号的端子P15、P16;被分配了单端信号的端子P20、P22、P23、P26;以及被分配了电源的端子P18、P19、P21、P24、P25。由此,在第1列R1中,能够使能高速地传输信号的端子P2、P3、P5、P6、P8、P9、P11、P12的数量更多,本实施方式的存储卡10能够使通信接口高速化。

形成第1列R1的多个端子P包括被分配了差分数据信号的多个通道的端子P2、P3、P5、P6、P8、P9、P11、P12。由此,本实施方式的存储卡10能够使通信接口高速化。

多对的端子P2、P3、P5、P6、P8、P9、P11、P12分别位于多个端子P1、P4、P7、P10、P13中的两个之间。由此,能够按各差分信号确保返回路径,减少差分信号间的相互干扰,工作信号电平得到稳定化。

端子P20、P22被分配PCIe标准的边带信号。由此,在第1列R1中,能够使能高速地传输信号的端子P2、P3、P5、P6、P8、P9、P11、P12的数量更多,本实施方式的存储卡10能够使通信接口高速化。

端子P21被分配第1电源PWR1。端子P18、P19被分配电压为第1电源PWR1以下的第2电源PWR2。端子P24、P25被分配电压为第2电源PWR2以下的第3电源PWR3。由此,能够根据用途来分开使用第1~第3电源PWR1、PWR2、PWR3,存储卡10的适应性(灵活性)提高。进一步,电压越低,电源电压变动的容许值越小,因此,减少了在一个端子P中流动的电流值为好,但通过设置有多个端子P18、P19和多个端子P24、P25,电流值被分散,平均每一端子的电流值变小,电压变动得到抑制。

调节器53在被分配了电源电压PWR3的第3电源PWR3的端子P24、P25已接地连接的情况下,从施加于被分配了电源电压PWR2的第2电源PWR2的端子P18、P19的电源电压PWR2生成电源电压PWR3。由此,本实施方式的存储卡10能够支持PWR1、PWR2的两电源结构的主机设备和PWR1、PWR2、PWR3的三电源结构的主机设备中的任何设备。

卡控制器14判定是否能够利用施加于端子P18、P19、P21、P24、P25的电源电压PWR1、PWR2、PWR3进行基于差分数据信号的初始化,从被分配了控制信号CNTB的端子P26输出判定结果。闪速存储器13中,当基于差分数据信号的初始化完成时,存储于该闪速存储器13的电源规格信息13a变为能够读出。主机设备通过对电源规格信息13a与该主机设备的电源规格进行比较,能够判断存储卡10是否能使用。由此,即使混合存在具有多个种类的电源结构的存储卡10,主机设备也能够对存储卡10的电源规格进行识别。

至少卡控制器14的一部分的边14a位于第1列R1与第2列R2之间,并且,在边14a具有通过布线W连接于第1列R1所包括的端子P2、P3、P5、P6、P8、P9、P11、P12的连接端子CP。由此,能够设定为不存在布线W绕过其他布线和/或其他部件、在第2列R2所包括的多个端子P之间通过的情况。因此,例如在布线W设置ESD保护二极管43变得容易,并且,能够缩短第1列R1所包括的端子P2、P3、P5、P6、P8、P9、P11、P12与连接端子CP之间的布线W的长度。

存储卡10的X轴方向上的长度为14±0.1mm,Y轴方向上的长度为18±0.1mm。一般而言,microSD卡的尺寸为11mm×15mm。即,本实施方式的存储卡10比microSD卡大。因此,存储卡10例如能够搭载如大型的三维闪速存储器那样的、难以搭载于microSD卡的存储容量和尺寸大的存储器,例如能够应对由技术进步实现的将来的闪速存储器13的尺寸大型化。进一步,存储卡10比microSD卡大,比标准的SD存储卡小。因此,存储卡10对于主机设备来说不会过大,并且,也容易进行相对于主机设备的连接器的插拔。

壳体11还具有位于第2边缘32的相反侧并在Y轴方向上延伸的第3边缘33、和第1边缘31与第3边缘33之间的第2角部36。第1角部35的形状与第2角部36的形状互不相同。由此,能抑制存储卡10的插反。

第1角部35在第1边缘31的一方的端部与第2边缘32的端部之间呈直线状延伸,形成所谓的被进行了C1.1的斜倒角的部分。第2角部36在第1边缘31的另一方的端部与第3边缘33的端部之间呈圆弧状延伸,形成所谓的被进行了R0.2的圆倒角的部分。存储卡10有时在第2角部36抵接于连接器的状态下被插入到该连接器。在该情况下,能够减小X轴方向上的存储卡10的位置错开。

(第2实施方式)

以下,参照图12对第2实施方式进行说明。此外,在以下的实施方式的说明中,具有与已经说明过的构成要素同样的功能的构成要素被标记与该已经描述的构成要素相同的标号,有时还省略说明。另外,被标记了相同的标号的多个构成要素不限于全部功能和性质是共同的,也可以具有与各实施方式相应的不同的功能和性质。

图12是表示第2实施方式涉及的存储卡10的例示性俯视图。如图12所示,第2实施方式涉及的卡控制器14层叠于闪速存储器13。

闪速存储器13重叠于第2列R2所包括的端子P。根据其他表现,闪速存储器13配置为:第2列R2所包括的端子P位于该闪速存储器13的Y轴的正方向上的端部与Y轴的负方向上的端部之间。另一方面,闪速存储器13相对于第1列R1所包括的端子P离开。

卡控制器14位于第1列R1与第2列R2之间。因此,与第1实施方式同样地,卡控制器14的多个连接端子CP也位于第1列R1与第2列R2之间。布线W将连接端子CP与第1列R1所包括的端子P连接。

如以上说明的第2实施方式的存储卡10那样,卡控制器14也可以层叠于闪速存储器13。通过闪速存储器13相对于第1列R1离开且连接端子CP位于第1列R1与第2列R2之间,能抑制布线W的长度变长。

(第3实施方式)

以下,参照图13~图25对第3实施方式进行说明。图13是表示第3实施方式涉及的存储卡10的例示性俯视图。图14是表示第3实施方式的存储卡10的例示性侧视图。存储卡10是半导体存储装置的一个例子。

存储卡10具有壳体11、基板12、非易失性存储器13、卡控制器14以及保护片15。非易失性存储器13是存储器的一个例子。卡控制器14是控制器的一个例子。

存储卡10和壳体11例如形成为在Y轴方向上延伸的大致矩形的板状。Y轴方向是存储卡10和壳体11的长边方向。Y轴方向是第2方向的一个例子。

如图14所示,壳体11为板状,具有第1面21、第2面22以及外缘23。第1面21和第2面22形成为在Y轴方向上延伸的大致四边形(矩形)形状。即,Y轴方向也是第1面21和第2面22的长边方向。在本实施方式中,存储卡10、壳体11、第1面21以及第2面22的形状分别被表现为矩形形状,但也可以采用其他表现。

第1面21是朝向Z轴的正方向的大致平坦的面。如图14所示,第2面22是位于第1面21的相反侧、朝向Z轴的负方向的大致平坦的面。

外缘23设置在第1面21与第2面22之间,连接于第1面21的边缘和第2面22的边缘。如图13所示,外缘23具有第1边缘31、第2边缘32、第3边缘33、第4边缘34、第1角部35、第2角部36、第3角部37以及第4角部38。第1边缘31是第1端缘的一个例子。第2边缘32是第1侧缘的一个例子。第3边缘33是第2侧缘的一个例子。第4边缘34是第2端缘的一个例子。

第1边缘31在X轴方向上延伸,朝向Y轴的正方向。X轴方向是存储卡10、壳体11、第1面21以及第2面22的短边方向,包括X轴的正方向和X轴的负方向。X轴方向是第1方向的一个例子。

第2边缘32在Y轴方向上延伸,朝向X轴的负方向。在第2边缘32设置有凹部32a。此外,也可以省略凹部32a。有时在供存储卡10插入的连接器设置有嵌于凹部32a的凸部。在该情况下,该凸部使得设置有凹部32a的存储卡10能够插入到连接器,并且,能够防止没有凹部32a的存储卡10被插入到连接器。任何存储卡10都能够插入到没有凸部的连接器。这样,连接器能够基于凹部32a来对存储卡10的种类进行识别。另外,连接器能够基于存储卡10的凹部32a的位置和连接器的上述凸部的位置来对更多的存储卡10的种类进行识别。第3边缘33位于第2边缘32的相反侧并在Y轴方向上延伸,朝向X轴的正方向。第4边缘34位于第1边缘31的相反侧并在X轴方向上延伸,朝向Y轴的负方向。

第2边缘32和第3边缘33各自的长度比第1边缘31和第4边缘34各自的长度长。第1边缘31和第4边缘34形成大致矩形的存储卡10的短边,第2边缘32和第3边缘33形成大致矩形的存储卡10的长边。

第1角部35为第1边缘31与第2边缘32之间的角部分,将第1边缘31的X轴的负方向上的端部与第2边缘32的Y轴的正方向上的端部连接。第1边缘31的X轴的负方向上的端部是第1边缘的一方的端部的一个例子。第2边缘32的Y轴的正方向上的端部是第2边缘的端部的一个例子。

第1角部35在第1边缘31的X轴的负方向上的端部与第2边缘32的Y轴的正方向上的端部之间呈直线状延伸。在X轴方向上,第1边缘31的X轴的负方向上的端部与第2边缘32之间的距离为1.1mm。根据其他表现,在X轴方向上,第1边缘31的X轴的负方向上的端部与第1边缘31的延长线和第2边缘32的延长线的交点之间的距离为1.1mm。

在Y轴方向上,第2边缘32的Y轴的正方向上的端部与第1边缘31之间的距离为1.1mm。根据其他表现,在Y轴方向上,第2边缘32的Y轴的正方向上的端部与第1边缘31的延长线和第2边缘32的延长线的交点之间的距离为1.1mm。

通过第1边缘31与第2边缘32的角被设定为所谓的C1.1的斜倒角,设置第1角部35。根据其他表现,第1角部35形成第1边缘31与第2边缘32之间的缺口C。

在本实施方式中,第1角部35在沿相互正交的方向延伸的第1边缘31和第2边缘32的角部分形成大致三角形的缺口C。但是,缺口C不限于该例子。第1角部35例如也可以形成相比于本实施方式而向壳体11的内侧凹陷的大致四边形的缺口C。

第2角部36是第1边缘31与第3边缘33之间的角部分,将第1边缘31的X轴的正方向上的端部与第3边缘33的Y轴的正方向上的端部连接。第1边缘31的X轴的正方向上的端部是第1边缘的另一方的端部的一个例子。第3边缘33的Y轴的正方向上的端部是第3边缘的端部的一个例子。

第2角部36在第1边缘31的X轴的正方向上的端部与第3边缘33的Y轴的正方向上的端部之间呈圆弧状延伸。第2角部36呈正圆的圆弧状延伸,但也可以呈椭圆的圆弧状延伸。

呈圆弧状延伸的第2角部36的半径为0.2mm。通过第1边缘31和第3边缘33的角被设定为所谓的R0.2的圆倒角,设置第2角部36。这样,第1角部35的形状与第2角部36的形状互不相同。

第3角部37将第2边缘32的Y轴的负方向上的端部与第4边缘34的X轴的负方向上的端部连接。第4角部38将第3边缘33的Y轴的负方向上的端部与第4边缘34的X轴的正方向上的端部连接。第3角部37和第4角部38分别呈半径为0.2mm的圆弧状延伸。

存储卡10、壳体11、第1面21以及第2面22的Y轴方向上的长度被设定为大约18±0.1mm,X轴方向上的长度被设定为大约14±0.1mm。即,Y轴方向上的第1边缘31与第4边缘34之间的距离被设定为大约18±0.1mm,X轴方向上的第2边缘32与第3边缘33之间的距离被设定为大约14±0.1mm。此外,存储卡10、壳体11、第1面21以及第2面22的X轴方向和Y轴方向上的长度不限于该例子。

如图14所示,壳体11还具有倾斜部39。倾斜部39是第1面21与第1边缘31之间的角部分,在第1面21的Y轴的正方向上的端部与第1边缘31的Z轴的正方向上的端部之间呈直线状延伸。

如图13所示,基板12、非易失性存储器13以及卡控制器14设置在壳体11的内部。基板12、非易失性存储器13以及卡控制器14既可以容纳于箱型的壳体11,也可以埋入于壳体11。

基板12例如为PCB。此外,基板12也可以为其他种类的基板。闪速存储器13和卡控制器14安装于基板12。

非易失性存储器13为非易失性即可,不依赖于存储器的种类,但代表性的非易失性存储器为闪速存储器。因此,以后称为闪速存储器13。闪速存储器13是能够存储信息的非易失性存储器,例如是NAND型闪速存储器。此外,闪速存储器13也可以是如NOR型那样的其他闪速存储器。存储卡10例如也可以具有层叠的多个闪速存储器13。

卡控制器14能够对闪速存储器13以及包括该闪速存储器13的存储卡10的整体进行控制。例如,卡控制器14能够进行向闪速存储器13的读/写控制以及与外部的通信控制。该通信控制包括与PCIe对应的协议控制。此外,卡控制器14也可以经由对闪速存储器13进行控制的其他电子部件来间接地对闪速存储器13进行控制。

保护片15贴附于第1面21。保护片15例如封住露出在第1面21的测试用的端子。此外,保护片15不限于该例子。

存储卡10还具有多个端子P。在本实施方式中,存储卡10具有39个端子P。此外,端子P的数量不过是一个例子,不限于该例子。即,端子P的数量既可以比39个少,也可以比39个多。多个端子P例如设置于基板12。多个端子P是贴附于第1面21的金属板。在本实施方式中,第2面22不设置端子P,例如能够被利用为印刷面、散热面。

本实施方式的多个端子P形成被分为第1组群G1和第2组群G2的多个列。第1组群G1包括第1列R11、R12。第2组群G2包括第2列R21。即,多个端子P排列为三列,形成第1列R11、R12以及第2列R21。

第1组群G1包括至少一个第1列(R11、R12)。即,第1组群G1既可以包括一个第1列(R11或者R12),也可以包括比两个多的第1列(R11、R12、……)。

第2组群G2包括至少一个第2列(R21)。即,第2组群G2既可以包括一个第2列(R21),也可以包括比两个多的第2列(R21、R22、……)。

图15是表示第3实施方式的变形例涉及的存储卡10的例示性俯视图。如图15所示,变形例的存储卡10也可以具有排列为两列来形成第1列R11和第2列R21的26个端子P。即,第1组群G1也可以具有一个第1列R11,省略第1列R12。

如图13所示,第1列R11包括在距第1边缘31比距第4边缘34近的位置相互隔着间隔而在X轴方向上排列的13个端子P。以下,有时将形成第1列R11的、第1列R11所包含的13个端子P分别地称为端子P101~P113。此外,形成第1列R11的端子P的数量不限于13个。形成第1列R11的端子P从最靠近第2边缘32的端子P101开始依次排列到最靠近第3边缘33的端子P113。

端子P101~P113在第1边缘31的附近沿着该第1边缘31在X轴方向上排列。端子P101~P113以及由端子P101~P113形成的第1列R11从第1边缘31稍微离开。但是,第1列R11与第1边缘31之间的距离比第1列R11与第4边缘34之间的距离短。此外,端子P101~P113以及第1列R11也可以与第1边缘31相邻。

第1列R12包括在距第1边缘31比距第4边缘34近的位置相互隔着间隔而在X轴方向上排列的13个端子P。以下,有时将形成第1列R12的、第1列R12所包含的13个端子P分别地称为端子P114~P126。此外,形成第1列R12的端子P的数量不限于13个。另外,形成第1列R12的端子P的数量既可以比形成第1列R11的端子P的数量多,也可以比形成第1列R11的端子P的数量少。形成第1列R12的端子P从最靠近第2边缘32的端子P114开始依次排列到最靠近第3边缘33的端子P126。

形成第1列R12的多个端子P排列在与第1列R11相比、离第1边缘31远的位置。因此,第1列R12比第1列R11离第1边缘31远。第1列R11和第1列R12隔着预定的短的间隔而在Y轴方向上排列。

第2列R21包括在距第4边缘34比距第1边缘31近的位置相互隔着间隔而在X轴方向上排列的13个端子P。以下,有时将形成第2列R21的、第2列R21所包含的13个端子P分别地称为端子P127~P139。此外,形成第2列R21的端子P的数量不限于13个。另外,形成第2列R21的端子P的数量既可以比分别形成第1列R11和第1列R12的端子P的数量多,也可以比分别形成第1列R11和第1列R12的端子P的数量少。形成第2列R21的端子P从最靠近第2边缘32的端子P127开始依次排列到最靠近第3边缘33的端子P139。

形成第2列R21的多个端子P处于距第4边缘34比距第1边缘31近的位置。根据其他表现,形成第2列R21的多个端子P配置在Y轴方向上的存储卡10和壳体11的中心线(由单点划线表示)与第4边缘34之间。因此,第1列R12与第2列R21之间的间隔宽。在本实施方式中,形成第2列R21的多个端子P从中心线离开。

如上述那样,第2组群G2也可以还包括由双点划线表示的第2列R22。在该情况下,第2列R21和第2列R22隔着预定的短的间隔而在Y轴方向上排列。

如上述那样,多个端子P在X轴方向上排列。在第2边缘32与第3边缘33之间的长度为一定的情况下,X轴方向上的相邻的端子P之间的距离例如根据端子P的数量来决定。进一步,在X轴方向上排列的端子P的最大数量通过X轴方向上的相邻的端子P之间的最小距离来决定。X轴方向上的多个端子P之间的距离既可以是均等的,也可以不同。在本实施方式中,第1列R11、R12以及第2列R21各自的端子P的数量相同。因此,全部端子P之间的距离为一定。

Y轴方向上的端子P的长度例如被设定为最大长度与最小长度之间的长度,该最大长度和最小长度是被决定为使得存储卡10与用于该存储卡10的连接器能够进行连接的长度。在第1列R11、R12以及第2列R21各自中,端子P排列为该端子P的Y轴的负方向上的端部对齐。

PCIe Gen4为16GT/s的低比特率,因此,需要通过尽量减少焊盘(pad)面积来减少静电电容而使频率特性提高。另一方面,焊盘面积越小,与机械性有关的制造容易性越低,因此,需要能够容许制造上的偏差、卡/连接器接触点位置的偏差的大小的焊盘面积。因此,焊盘的最小长度由电气特性和机械性的技术水平的权衡来决定。本卡形状因数中,采用了根据现状的安装技术的最小间隔能够配置的、能够在一列安装PCIe-2通道的焊盘数量13条。

当多个端子P的X轴方向和Y轴方向上的长度被设定为大致相同时,能够使多个端子P的电气特性相似。在本实施方式中,第1列R11中的全部信号用的端子P和第1列R12中的全部端子P的Y轴方向和X轴方向上的长度越小,则在电气特性上越好,该长度被设定为机械技术水平下的最小长度。由此,形成第1列R11、R12的多个端子P的电气特性提高,并且,设置第1列R11、R12的区域的面积变小。

另外,在本实施方式中,在第1列R11和第2列R21的数据传送用的端子P中,端子P的Y轴方向上的长度被设定为相同。由此,能够使第1列R11和第1列R12的数据传送用的端子P的电气特性相似。进一步,一个端子P也可以相比于其他端子P的Y轴的正方向上的端部而在Y轴的正方向上伸出。例如通过电源用的端子P和GND用的端子P比数据传送用的端子P伸出,在将存储卡110沿着Y轴正方向插入的横插(横向插入)连接器的情况下,电源用以及GND用的端子P比数据传送用的端子P先接触连接器的引线架。由此,主机设备的GND电平和存储卡10的GND电平成为等效,能够使卡控制器14的电气电平稳定。通过第1列R11和第2列R21的端子P中的、电源用的端子P和GND用的端子P在Y轴方向上被设定得长,例如在如图15那样多个端子P排列为两列的情况下,存储卡10能够在推推(push-push)类型、推拉(push-pull)类型等的横插连接器中进行使用。

在第1列R11、R12中,除了信号用的端子P以外的端子P仅为GND用的端子P。因此,若第1列R11的GND用的端子P先接触连接器的引线架,则不需要增长第1列R12的GND用的端子P。因此,能够缩短第1列R12的全部端子P的Y轴方向上的长度。由此,能够缩短第1列R11、R12的间隔。

多个端子P也可以具有互不相同的形状。例如,在第1列R11中,端子P101、P104、P107、P110、P113的形状与端子P102、P103、P105、P106、P108、P109、P111、P112的形状互不相同,但也可以相同。进一步,在第2列R21中,端子P127、P130、P131、P132、P134、P137、P138的形状与端子P128、P129、P133、P135、P136、P139的形状互不相同,但也可以相同。

在本实施方式中,在第1列R11、R12以及第2列R21各自中,多个端子P之间的距离大致为一定。但是,多个端子P之间的距离也可以不同。

在沿Y轴方向安装的连接器中,作为存储卡10的电源端子、接地端子的端子P101、P104、P107、P110、P113、P127、P130、P131、P132、P134、P137、P138被设定为比作为信号端子的端子P102、P103、P105、P106、P108、P109、P111、P112、P128、P129、P133、P135、P136、P139稍长。由此,连接器与电源端子以及接地端子最先接触,因此,电气方面变得稳定,能够避免对信号端子给与电应力。在电源被供给至卡控制器14之前向信号端子施加电压时,会对后述的接口电路51的输入缓存施加电应力。

对多个端子P分配在遵循预定的接口标准的通信中所使用的信号。但是,也可以对多个端子P分配在遵循多个接口标准的通信中所使用的信号。

图16是表示第3实施方式的多个端子P的信号分配的一个例子的例示性表。如图16所示,在本实施方式中,对第1组群G1的第1列R11和第1列R12的多个端子P分配在PCIe的数据通信中所使用的信号。在PCIe中,能够在数据通信中使用差分数据信号对。

在第1列R11中,对端子P101、P104、P107、P110、P113分配接地电位的接地(GND),对端子P102、P103、P108、P109分配接收差分信号PERp0、PERn0、PERp1、PERn1,对端子P105、P106、P111、P112分配发送差分信号PETp0、PETn0、PETp1、PETn1。

在第1列R12中,对端子P114、P117、P120、P123、P126分配接地电位的接地(GND),对端子P115、P116、P121、P122分配接收差分信号PERp2、PERn2、PERp3、PERn3,对端子P118、P119、P124、P125分配发送差分信号PETp2、PETn2、PETp3、PETn3。

端子P101、P104、P107、P110、P113、P114、P117、P120、P123、P126是接地端子的一个例子。端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125是信号端子、第1信号端子以及差分数据信号端子的一个例子。接收差分信号PERp0、PERn0、PERp1、PERn1、PERp2、PERn2、PERp3、PERn3和发送差分信号PETp0、PETn0、PETp1、PETn1、PETp2、PETn2、PETp3、PETn3是信号和差分数据信号的一个例子。

被分配了接收差分信号PERp0、PERn0的一对端子P102、P103位于两个端子P101、P104之间,由两个端子P101、P104包围。被分配了发送差分信号PETp0、PETn0的一对端子P105、P106位于两个端子P104、P107之间,由两个端子P104、P107包围。

被分配了接收差分信号PERp1、PERn1的一对端子P108、P109位于两个端子P107、P110之间,由两个端子P107、P110包围。被分配了发送差分信号PETp1、PETn1的一对端子P111、P112位于两个端子P110、P113之间,由两个端子P110、P113包围。

被分配了接收差分信号PERp2、PERn2的一对端子P115、P116位于两个端子P114、P117之间,由两个端子P114、P117包围。被分配了发送差分信号PETp2、PETn2的一对端子P118、P119位于两个端子P117、P120之间,由两个端子P117、P120包围。

被分配了接收差分信号PERp3、PERn3的一对端子P121、P122位于两个端子P120、P123之间,由两个端子P120、P123包围。被分配了发送差分信号PETp3、PETn3的一对端子P124、P125位于两个端子P123、P126之间,由两个端子P123、P126包围。

在PCIe中,进行数据的串行传输,但为了使得能够在接收电路生成时钟、并避免因在数据中相同的逻辑电平连续而电压电平偏向高电平或者低电平,被按某单位来进行编码。编码使用8B10B、128b/130b等方式。能够通过该编码使平均信号电压电平为通用电压附近,能够抑制从接收阈值电平的偏移。另外,接收侧通过根据数据的变化点而生成接收时钟,能够生成追随了数据的时间性的变动的接收时钟,因此,能够实现稳定的数据接收(被称为CDR:Clock Data Recovery(时钟数据恢复)的技术)。即使是在多个通道(差分数据信号的向上向下的对)之间存在偏移的情况下,也能够通过在各个通道独立地构成接收电路而将并行化后的接收数据的开始位置对齐,来消除通道间偏离。

例如,PCIe 3.0的情况下的最大传送速度为平均每1个通道2G字节/秒(向上向下的合计)。在PCIe中,能够由一组发送差分信号PETp0、PETn0和接收差分信号PERp0、PERn0构成1个通道。另外,在PCIe中,能够由一组发送差分信号PETp1、PETn1和接收差分信号PERp1、PERn1进一步构成1个通道。同样地,能够由一组发送差分信号PETp2、PETn2和接收差分信号PERp2、PERn2构成1个通道,能够由一组发送差分信号PETp3、PETn3和接收差分信号PERp3、PERn3进一步构成1个通道。

如上述那样,对形成第1列R11的多个端子P分配2个通道,对形成第1列R12的多个端子P分配2个通道。根据其他表现,形成第1列R11、R12的多个端子P包括被分配给差分数据信号的多个通道的多对的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125。因此,能够使PCIe的通道数量增大,能够使数据传送速度提高。

在PCIe中,能够在初始化时对多个通道结构进行识别,将一个数据分配至多个通道来进行传送。此外,在主机设备不支持多个通道的情况下,存储卡10也能够在单通道模式下、或者如上述4个通道中的2个通道那样使用了一部分的多个通道的模式下,进行动作。

端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125进行遵循PCIe的差分数据信号的传输,能够通过发送端子和接收端子成对的结构进行双向通信。端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125能够传输频率为GHz频带的差分数据信号。

PCIe的差分数据信号以外的控制信号被分配给第2列R21的多个端子P。在第2列R21中,对端子P127、P130分配GND,对端子P128、P129分配参考差分时钟信号REFCLKp、REFCLKn,对端子P131、P132分配第2电源(功率轨)PWR2,对端子P133分配复位信号PERST#,对端子P134分配第1电源(功率轨)PWR1,对端子P135分配时钟控制信号CLKREQ#,对端子P136、P139分配控制信号CNTA、CNTB,对端子P137、P138分配第3电源(功率轨)PWR3。

端子P128、P129、P133、P135、P136、P139是信号端子和第2信号端子的一个例子。端子P128、P129是差分时钟信号端子的一个例子。端子P133、P135是单端信号端子的一个例子,并且是边带信号端子的一个例子。端子P131、P132、P134、P137、P138是电源端子的一个例子。端子P131、P132是第2电源端子的一个例子。P134是第1电源端子的一个例子。端子P137、P138是第3电源端子的一个例子。由于使用连接器而存在接触电阻,存在依赖于长的布线的长度的布线电阻。如后述那样,通过施加于多个电源端子的电压不同、且设置多个端子P来作为电源端子,电流分散,在平均每一个端子中流动的电流变小,能够减小由存在于从电源电路到电源端子之间的电阻成分引起的下降电压。

PCIe参考差分时钟信号REFCLKp/n由2条构成差分时钟信号。通过从主机设备向端子P128、P129传输频率为MHz频带的时钟信号,存储卡10不需要安装高精度的时钟发送器,能够使与安装了该存储卡10的主机设备的同步变得容易。另外,通过降低端子P128、P129使用于传输的时钟信号的频率,使之为接近正弦波的波形,能够降低EMI的产生。存储卡10通过用PLL电路使所接收到的时钟倍增,生成端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125使用于传输的差分数据信号的高的频率。

主机设备例如是如个人计算机那样的信息处理装置、便携电话机、数字相机、拍摄装置、如平板计算机和/或智能手机那样的便携终端、游戏设备、如车辆导航系统那样的车载终端或者其他装置。

存储卡10用PLL振荡电路使所接收的参考差分时钟倍增来生成位时钟。与位时钟同步地从发送差分信号PETp0、PETn0、PETp1、PETn1、PETp2、PETn2、PETp3、PETn3输出数据。从接收差分信号PERp0、PERn0、PERp1、PERn1、PERp2、PERn2、PERp3、PERn3输入的数据通过根据所接收到的所述代码模式生成的接收时钟(所述CDR)来被暂时进行采样,各通道的数据被对齐来作为并行数据。能够使该数据再同步于根据参考差分时钟生成的内部时钟。与对串行数据进行了并行变换后的数据位数相应地,内部时钟被设定为比所述位时钟低的频率。例如,在使用8B10B编解码器(codec)的情况下,在将以串行方式接收到的10位代码对齐为了1字节(8位)并行数据时,内部时钟相对于位时钟成为1/10的频率。

复位信号PERST#能够用于主机设备对在PCIe的通信中所使用的存储器设备进行启动和复位。通过PCIe的复位解除的定时规定来规定PCIe差分通道的初始化开始定时。在嵌入式存储器的情况下,规定了从电源接入到复位解除为止的时间,因此,存储卡10准备为成为能够在该时间内进行初始化的状态。但是,在可移动存储器的情况下,需要也考虑存储卡10和连接器稳定地成为嵌合状态的时间来决定复位解除定时。该复位信号PERST#能够在主机设备在产生了无法用通常的恢复协议进行恢复的错误时等进行存储卡10的再初始化时加以使用。

时钟控制信号CLKREQ#是对主机要求供给参考差分时钟的控制信号。该信号在电源被接入到存储卡10之后暂时被设定为High电平(由于开路漏极,因此,在上拉时为High),在存储卡10内部的电源电压稳定且存储卡10成为了能够接收时钟的阶段中被驱动为Low电平。主机当检测到CLKREQ#成为了Low电平时,开始参考时钟的供给。另外,主机能够使用该信号来作为对存储卡10向功率节省模式的转变和从功率节省模式的恢复进行控制的信号。该功率节省模式是在PCIe中被称为L1 PM Substate的功能。存储卡10能够在处于不进行存储器访问的空闲状态时,通过进入功率节省模式来降低PHY的功耗。在功率节省模式下,主机能够使PCIe参考差分时钟信号REFCLKp/n停止,另外,存储卡10也具有能够切断PHY的通用电源的模式,能够大幅地降低功耗。

复位信号PERST#和时钟控制信号CLKREQ#为单端信号,被定义为PCIe的边带信号。

通过存储卡10支持PCIe的通信,能够使用PCIe的标准的物理层(PHY)。因此,能够谋求用于提高存储卡10的数据的传送速度的设计的容易化和开发成本的降低。

进一步,存储卡10可以采用NVMe来作为PCIe上的协议。NVMe是协议被标准化的,因此,在与NVMe对应的主机设备中,存储卡10能够仅通过连接来进行使用。另外,NVMe在闪速存储器13进行最佳的控制,能够通过在系统存储器上制作队列来登记多个命令,能够通过多事务处理来减少数据传送时的开销。另外,通过使用PCIe的主(master)传送功能进行数据传送,能够使数据传送效率提高。

主机设备能够向端子P134供给作为第1电源的电源电压PWR1。电源电压PWR1在本实施方式中被设定为3.3V。电源电压标记表示上侧的标准值,是绝大部分的闪速存储器支持的动作电压。在闪速存储器支持宽的动作电压范围的情况下,容许以更低的电压进行动作。电源电压PWR1例如可以被设定在2.5V以上且3.3V以下的范围内,但不限于该例子。该2.5V以上且3.3V以下的电压范围并不意味着动态的变动,电源电压PWR1稳定地使用该电压范围内的某电压。

主机设备能够向端子P131、P132供给作为第2电源的电源电压PWR2。电源电压PWR2是第2电源电压的一个例子。电源电压PWR2在本实施方式中被设定为1.8V。即,电源电压PWR2为电源电压PWR1以下。在不使用后述的电源电压PWR3的情况下,电源电压PWR2例如可以被设定在1.2V以上且1.8V以下的范围内,但不限于该例子。

主机设备能够向端子P137、P138供给作为第3电源的电源电压PWR3。电源电压PWR3是第1电源电压的一个例子。电源电压PWR3在本实施方式中被设定为1.2V以下。即,电源电压PWR3为电源电压PWR2以下。电源电压PWR3不限于该例子。

在存储卡10中,电源电压PWR3不是必需的。通过在存储卡10的内部从电源电压PWR2生成电源电压PWR3,能够使得不需要电源电压PWR3。在该情况下,主机供给电源电压PWR1和电源电压PWR2这两个电源即可。

如图13所示,卡控制器14位于第1列R11、R12与第2列R21之间。此外,卡控制器14也可以配置在其他位置,例如位于第1列R11所包括的端子P的Y轴的正方向上的端部与第2列R21所包括的端子P的Y轴的负方向上的端部之间。另外,卡控制器14也可以配置为:使得第2列R21所包括的端子P位于该卡控制器14的Y轴的正方向上的端部与Y轴的负方向上的端部之间。

与第1实施方式同样地,卡控制器14具有图4所示的多个连接端子CP。多个连接端子CP设置于卡控制器14的一部分的边14a,位于第1列R11与第2列R21之间。连接端子CP例如能够配置为:使得该连接端子CP与端子P之间的布线不交叉。

在本实施方式中,当设想为设计最适于本形状因数的卡控制器时,在将分配给多个端子P的信号连接于卡控制器14的情况下,当尽量使布线的特性阻抗为一定时,频率特性变好。因此,通过分配卡控制器14的信号端子以使得图4所示的多条布线W、多个接地面41以及多个电源布线42互相不重叠且使得布线W、电源布线42能够以没有过孔的方式高效地进行布线,能够抑制特性阻抗变动。进一步,通过设为左右对称,容易使特性一致,图案设计也变得容易。

布线W2、W3、W5、W6、W8、W9、W11、W12将卡控制器14的连接端子CP与端子P102、P103、P105、P106、P108、P109、P111、P112连接。

布线W2、W3、W5、W6、W8、W9、W11、W12的长度被设定为相互相等。进一步,布线W2、W3、W5、W6、W8、W9、W11、W12相对于经过端子P107的中心并在Y轴方向上延伸的中心轴Ax而设置为镜面对称。因此,布线W2、W3、W5、W6、W8、W9、W11、W12的设计变得容易。另外,布线W15、W16的长度被设定为相互相等。

布线W2、W3、W5、W6、W8、W9、W11、W12被布线为等长来减少线间偏离。为了调整长度,布线被弯曲,但由于通常难以用平滑的曲线引出图案,因此,在改变布线方向时,在多个部位弯曲为45°,而不是90°。当以90°进行了弯曲时,布线W的宽度在弯曲部分稍稍变宽,引起特性阻抗的变化,会产生噪声。与90°相比,45°时的宽度的变动少,因此,能抑制噪声的产生。

多个接地面41包围布线W2、W3、W5、W6、W8、W9、W11、W12。由此,能够按各差分信号来确保返回路径,降低差分信号间的相互干扰,工作信号电平得以稳定化。

电源布线42连接于端子P131、P132、P134、P137、P138。通过电源布线42的宽度比布线W的宽度宽,能降低电源布线42的电阻,并且,能高效地进行经由了电源布线42的散热。另外,存储卡10能够从多个端子P向连接器进行散热。

在主机电源输出与存储卡端子之间存在布线、连接器的电阻成分、电感成分,因此,会产生电压降。在电源电压的容许变动范围相对于电源电压为一定的比例的情况下(例如+/-5%),电压越低,容许电压变动幅度越小。因此,由于存在所述电压降,所以电源电压越低,越难以对电源电压进行控制以使从主机设备到卡端子的电源电压收于容许电压变动幅度内。

另一方面,若为同一基板、同一连接器,则主机设备的连接器、包括电源布线42的布线的电阻值与电压无关地为相似的电阻值。因此,当电源电压低时,能够在一个端子P流动的电流值变小。

在本实施方式中,电源电压PWR2在两个端子P131、P132中流动。进一步,电源电压PWR3在两个端子P137、P138中流动。这样,通过对多个端子P131、P132、P137、P138分配电流,平均每一个端子P的电流值大致成为一半,由此能够减小由电源布线42、主机设备的连接器的电阻成分引起的下降电压。因此,主机设备容易使电源电压收于容许电压变动幅度内。进一步,通过将电源电压PWR2、PWR3设定为相同的电压,能够供给更大的电流。

连接器的电阻成分例如包括接点电阻和接触电阻,通过减小电阻,能够增大在存储卡10中流动的电流。接点电阻(contact lead resistance)由接点长度、粗度、材质等决定,接点接触电阻(contact resistance)由压力、接触点的形状、粗度、材质等决定。

另外,通常,电源电压PWR1为3.3V±5%,电源电压PWR2为1.8V±5%,但如上述那样,也可以为:电源电压PWR1如2.5V-5%~3.3V+5%那样被设定为在下侧更宽的电压范围,电源电压PWR2如1.2V-5%~1.8V+5%那样被设定为在下侧更宽的电压范围。由此,能够降低电压来减少功耗。

ESD保护二极管43将布线W2、W3、W5、W6、W8、W9、W11、W12各自与接地面41连接。ESD保护二极管43配置在端子P与连接端子CP之间,对从端子P102、P103、P105、P106、P108、P109、P111、P112侵入的静电进行吸收。

当多个连接端子CP位于第1列R11与第1列R12之间时,布线W2、W3、W5、W6、W8、W9、W11、W12能够设定为:不会绕过其他布线和/或其他部件、不会在第1列R12所包括的多个端子P之间通过。因此,能够缩短布线W2、W3、W5、W6、W8、W9、W11、W12的长度,并且,能够有效地配置ESD保护二极管43。在本实施方式中,ESD保护二极管43配置在第1列R11所包括的端子P的附近。

存储卡10安装于主机设备的连接器。例如,存储卡10通过被插入到推推类型、推拉类型的连接器的插槽,而被安装于该连接器。此外,存储卡10也可以安装于如铰合(hinge)类型连接器那样的其他类型的连接器。

本实施方式的存储卡10被从设置有缺口C的图13的第1边缘31插入到连接器的插槽。由此,在存储卡10安装于连接器的状态下,第1边缘31与第4边缘34相比,位于连接器的靠进深的位置。

通过第1角部35在第1边缘31与第2边缘32之间形成缺口C,能防止存储卡10被表里颠倒地插入到连接器的插槽。例如,当存储卡10被以正确的朝向插入到连接器的插槽时,用缺口C避开连接器内部的部件。另一方面,当存储卡10被表里颠倒地插入到连接器的插槽时,连接器内部的部件例如会与第2角部36干涉,妨碍存储卡10完全插入。另外,在Y轴方向上反向地将存储卡10从第4边缘插入到了连接器时,存储卡10也同样地无法安装于连接器。通过在形成于第1边缘31与第3边缘33之间的第2角部36附近,X轴方向的边缘和Y轴方向的边缘紧贴于连接器,能够减少连接器与存储卡10的旋转方向上的错开。

如图14所示,当存储卡10被插入到连接器时,连接器的引线架101、103接触于形成第1列R11和第2列R21的多个端子P的各个。引线架101、103延伸的方向例如配置在主机的布线成为最短的方向。在该情况下,在存储卡10被插入到连接器时,会在引线架101、103容易弯曲的方向上施加力。在存储卡10设置有倾斜部39,存储卡10的前端为锥状。因此,引线架101、103能够被倾斜部39引导,例如能减少引线架101、103与壳体11之间的摩擦,也能减小要使引线架弯曲的力。进一步,能抑制引线架101、103的镀层剥离,连接器的耐磨耗性提高。在引线架102的方向上,弯曲的力小,但难以从连接器引出大量的信号,主机的布线会变长。因此,引线架102的安装可以为可选的。

例如在铰合类型连接器中,引线架102分别接触于形成第1列R12的多个端子P。另外,在图15的变形例的存储卡10中,引线架102接触于壳体11的第1面21。通过引线架102接触于端子P或者第1面21,连接器与存储卡10的接触点增加。因此,存储卡10的热会向连接器传导,存储卡10容易被冷却。

当引线架101、102、103接触于端子P时,主机设备的控制器(以下称为主机控制器)与存储卡10的卡控制器14经由主机设备的布线、存储卡10的布线W而电连接。

如用于安装于主机设备的基板的连接器的端子那样的、连接器的主机控制器侧的连接点,一般设置在连接器的插槽的进深侧(图13的上方向)。因此,形成第1列R11的端子P以及引线架101的接触点与主机控制器之间的布线的长度容易被设为更短。另一方面,形成第2列R21的端子P以及引线架103的接触点与主机控制器之间的布线的长度,例如由于绕过第1列R11,因此容易变得更长。

在本实施方式的存储卡10中,到主机控制器为止的布线长度更短的第1列R11、R12包括进行高速的差分数据信号的传输的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125。由此,主机设备的物理层(PHY)与存储卡10的物理层(PHY)变近,在存储卡10的差分数据信号的传输中,容易确保信号完整性。

图17是概略性地表示第3实施方式的存储卡10的结构的第1例的例示性框图。卡控制器14具有接口电路(I/F)51、物理层及存储器控制器52、两个调节器53、54以及电源检查电路55。卡控制器14的物理层及存储器控制器52在图17中表示为一个框,并且,在以下也一体地进行说明。

I/F51能够应对单端信号。在I/F51例如设置输入缓存和输出缓存。复位信号PERST#是输入信号,在端子P133配置输入缓存。CLKREQ#是双向信号,在端子P135配置输入缓存和开路漏极的输出缓存。该信号由主机上拉为High电平。存储卡10通过将该信号不驱动为Low,从而成为输入状态。另外,在主机不将该信号驱动为Low时(High电平),存储卡10能够设为能由该存储卡10控制信号电平的输出状态。

物理层及存储器控制器52能够应对差分信号。在物理层及存储器控制器52设置接收器和发送器。对接收器能够输入接收差分信号PERp0、PERn0、PERp1、PERn1、PERp2、PERn2、PERp3、PERn3。发送器能够输出发送差分信号PETp0、PETn0、PETp1、PETn1、PETp2、PETn2、PETp3、PETn3。

物理层及存储器控制器52和电源检查电路55连接于I/F51。物理层及存储器控制器52连接于闪速存储器13。在卡控制器14,除了PCIe的物理层之外,也可以设置PCIe的数据链层和事务层。

物理层及存储器控制器52能够进行串行/并行变换、并行/串行变换以及数据的符号化等。该符号化是如下处理:在数据的0或者1连续时,从所述8B10B、128b/130b等的代码中置换为0的总数和1的总数相同或者接近的值、且0或者1不连续某数量以上的符号。通过该符号化,能够使数据传输时的平均信号电压电平为通用电压附近,能够抑制从接收阈值电平的偏移。另外,当反复传送同一符号模式时,特定频率的高次谐波会变大,但通过切换为模式不同的多个符号以使得不成为重复模式,能够使得特定频率的高次谐波不变大。也即是,能够抑制EMI的产生。

此外,在PCIe的事务层中,能够对数据进行封包来进行收发、进行消息收发。在PCIe的数据链层中,能够对从事务层接受到的包附加序列编号、附加CRC码。序列编号能够用于包的送达确认等。

PCIe可以由多个通道构成,但对主机和存储卡10进行了连接的各通道被独立地进行初始化。仅使用初始化完成而能够进行通信的通道。在本实施例的情况下,使用最大4个通道,但也可以仅使用1个通道或者2个通道。

1个通道PERp0、PERn0、PETp0、PETn0、或者、

PERp1、PERn1、PETp1、PETn1

2个通道PERp0、PERn0、PETp0、PETn0、

PERp1、PERn1、PETp1、PETn1

4个通道PERp0、PERn0、PETp0、PETn0、

PERp1、PERn1、PETp1、PETn1、

PERp2、PERn2、PETp2、PETn2、

PERp3、PERn3、PETp3、PETn3

对于数据的顺序,根据能够通信的通道数量来以字节为单位分配为通道编号的顺序。

当从主机设备向存储卡10发送串行的接收差分信号PERp0、PERn0、PERp1、PERn1、PERp2、PERn2、PERp3、PERn3时,按各通道的接收器来以字节为单位变换为并行数据。当向各通道的发送器发送字节单位的并行数据时,该数据被变换为串行的发送差分信号PETp0、PETn0、PETp1、PETn1、PETp2、PETn2、PETp3、PETn3,并被发送给主机设备。

电源电压PWR1被供给至闪速存储器13和卡控制器14。在本实施方式中,电源电压PWR1主要被使用于如闪速存储器13的读/写那样的闪速存储器13的动作。通过使电源电压PWR1升压,生成闪速存储器13的写入电压。另外,电源电压PWR1也可以使用于其他用途。如上述那样,电源电压PWR1为电源电压PWR2以上、且为电源电压PWR3以上。

在主机设备与存储卡10以3.3V信号电压相连接的情况下,在I/O电源使用电源电压PWR1。即使是在如图17的例子那样、主机设备与存储卡10以1.8V信号电压相连接的情况下,电源电压PWR1也可以被作为I/O电源来使用。由此,存储卡10实现高耐压化,卡输入电路得到保护。例如当电源电压PWR1被设定为2.5V时,存储卡10能够设为2.5V耐压,若电源电压PWR1被设定为3.3V,则存储卡10能够设为3.3V耐压。

电源电压PWR2被供给至闪速存储器13和卡控制器14。在本实施方式中,电源电压PWR2被作为逻辑电路的电源来使用。另外,电源电压PWR2也被作为闪速存储器13与卡控制器14之间的接口电压来使用。低的信号电压时能够设为更高速的接口,因此,虽未图示,但也可以将电源电压PWR3作为闪速存储器13与卡控制器14之间的接口电压来使用。

在主机设备与存储卡10以1.8V信号电压相连接的情况下,也可以在I/O电源使用电源电压PWR2。在该情况下,存储卡10能设为1.8V耐压。

电源电压PWR3被供给至卡控制器14。在本实施方式中,电源电压PWR3被作为差分信号电路的物理层(PHY)、模拟电路的电源来使用。

一般而言,对进行模拟动作的差分信号电路使用噪声少的电源,与数字电源相分离。在本实施方式中,从主机设备供给的电源电压PWR3是足够稳定的噪声少的电源。

如上所述,在存储卡10中,为了降低噪声、电源变动的影响,三个电源电压PWR1、PWR2、PWR3被分离地进行供给。即,根据用途来分开使用三个电源电压PWR1、PWR2、PWR3。此外,电源电压PWR1、PWR2、PWR3不限定于上述例子,也可以以其他方式进行使用。

图18是概略性地表示第3实施方式的存储卡10的结构的第2例的例示性框图。如图18所示,电源电压PWR2也可以被供给至调节器53、54。通过使被分配了电源电压(第3电源)PWR3的端子P137、P138为接地电平,由调节器53生成电源电压PWR3。这是使用以电源电压PWR1和电源电压PWR2这两个电源进行动作的存储卡10的情况。

如图18的例子那样,调节器54生成比所输入的电源电压PWR2低的电源电压Vlogic。该电源电压Vlogic代替电源电压PWR2而被供给至闪速存储器13和卡控制器14的物理层及存储器控制器52。电源电压Vlogic也能够被作为逻辑电路的电源来使用、并且被作为闪速存储器13与卡控制器14之间的接口电压来使用。通过降低接口电压,能够在闪速存储器13与卡控制器14之间高速地进行数据传送,也能降低功耗。一般而言,信号电压低时能够缩短信号的上升/下降时间,因此,能够进行高速的数据传输。

在难以从主机设备供给稳定的电源电压PWR3的情况下,通过使用由调节器53生成的电源电压PWR3,能够消除问题。如图18的例子那样,当端子P137、P138为接地连接时,调节器53从所输入的电源电压PWR2生成比该电源电压PWR2低的电源电压PWR3。在如图17那样主机供给了电源电压PWR3的情况下,存储卡10也能够不使用调节器53,而是进行切换以使得使用从主机供给的电源电压PWR3。

电源电压PWR3、Vlogic都是从电源电压PWR2生成的。电源电压PWR3和电源电压Vlogic既可以是相互相同的电压,也可以是相互不同的电压,但为了使得电源分离而相互不影响,用分别的调节器53和调节器54来生成电源电压。另外,通过使用LDO(Low DropOut)来作为调节器53、54,能够降低由输入输出电压差导致的白费的功耗。

如由图18的虚线所示,也可以为:调节器53从电源电压PWR1生成电源电压PWR3,调节器54从电源电压PWR1生成电源电压Vlogic。即,在该情况下,只要存在电源电压PWR1,存储卡10就能够进行动作。

如上所述,存储卡10能利用施加于端子P131、P132、P134、P137、P138的电源电压PWR1、PWR2或电源电压PWR1、PWR2、PWR3进行动作。存储卡10也可以为:能够根据施加于端子P131、P132、P134、P137、P138的电源电压PWR1、PWR2、PWR3的组合来对电源模式进行切换。

主机设备通过根据以下的电源检查序列来取得保存于闪速存储器13的存储卡10的电源规格信息13a,能够与存储卡10的电源结构相对应。电源规格信息13a例如包括电源电压PWR1、PWR2、PWR3的电压范围、最大电流(连续)以及峰值电流(100μ秒区间)。

图19是表示第3实施方式的存储卡10的电源检查序列中的主机设备的动作的例示性流程图。在主机设备从闪速存储器13取得电源规格信息13a之前,进行PCIe的初始化。因此,主机设备在电源检查序列中判定是否能够用所供给的电源电压PWR1、PWR2、PWR3的组合来开始初始化。

如图19所示,主机设备向被插入到了连接器的插槽的存储卡10的端子P134供给(施加)电源电压PWR1(S101),向端子P131、P132供给(施加)电源电压PWR2(S102)。

如图17所示,对电源检查电路55输入电源电压PWR1、PWR2。电源检查电路55在能够利用所施加的电源电压PWR1、PWR2来使用存储卡10的情况下,驱动为CLKREQ#=Low。另一方面,电源检查电路55在无法利用所施加的电源电压PWR1、PWR2使用卡的情况下,设为保持CLKREQ#=High不变。

如图19所示,主机设备在经过一定时间Tpok后(S103),对CLKREQ#的电平进行检查(S104)。电源检查电路55能够在时间Tpok的期间将CLKREQ#的电平从High切换为Low。因此,主机设备在经过时间Tpok后检查一次CLKREQ#的电平即可。在保持CLKREQ#=High不变的情况下(S104:否),主机设备向存储卡10的端子P137、P138供给(施加)电源电压PWR3(S105)。

电源检查电路55在能够利用所施加的电源电压PWR1、PWR2、PWR3来使用存储卡10的情况下,驱动为CLKREQ#=Low。另一方面,电源检查电路55在无法利用所施加的电源电压PWR1、PWR2、PWR3来使用卡的情况下,设为保持CLKREQ#=High不变。

主机设备在经过一定时间Tpok后(S106),对CLKREQ#的电平进行检查(S107)。在保持CLKREQ#=High不变的情况下(S107:否),主机设备使电源电压PWR1、PWR3断开(S108)。

主机设备在经过一定时间Tpok后(S109),对CLKREQ#的电平进行检查(S110)。在保持CLKREQ#=High不变的情况下(S110:否),主机设备不使用存储卡10(S111)。

具有特殊的电源规格信息13a等的需要读出该信息的卡,被设计为能够仅用电源电压PWR2来进行PCIe的初始化。只要是寄存器访问的程度,卡就能够以低功耗进行动作,即使仅是PWR2的电力供给,也能够足以进行初始化。仅是PWR2的话,无法从存储器读出电源规格信息13a,因此,在第一次被施加了PWR1的时间点,卡控制器被设计为从存储器读出电源规格信息13a并将其记录于卡控制器内部的存储器。

这样的卡在仅被施加电源电压PWR2的情况下(S108),电源检查电路55驱动为CLKREQ#=Low。由于能够仅用电源电压PWR2来进行PCIe的初始化而读出寄存器值,因此,主机设备如后述那样读出电源规格信息13a,判断是否能够供给存储卡10需要的其他电源电压。

在控制信号CLKREQ#的电平检查时为CLKREQ#=Low的情况下(S104:是,S107:是,S110:是),主机设备开始PCIe的初始化(S112、S113、S114)。S112、S113、S114是PCIe的标准通电序列。当CLKREQ#=Low时,主机设备供给差分时钟REFCLK(S112),在预定的定时(TPVPGL)使复位信号PERST#为High(S113)。

接着,主机设备执行PCIe的训练序列(S114)。通过该训练序列进行物理层的检测、物理层的动作参数的调整等,主机设备和存储卡10成为能够通信,成为MMIO寄存器能读出的状态。上述初始化包括该训练序列。

图20是表示第3实施方式的电源规格信息13a的一个例子的例示性表。图20所例示的电源规格信息13a是作为电源要求规格所记载的寄存器信息,如上述那样包括电源电压PWR1、PWR2、PWR3的电压范围、最大电流(连续)以及峰值电流(例如100μ秒区间)。

最大电流(连续)是在存储卡10的存储器访问时所使用的连续电流值。主机设备的电源电路被要求连续地供给该电流值。

峰值电流(100μ秒区间)例如为在100μ秒区间进行了测定的情况下流动的峰值电流值,是决定主机设备的电源设计中的耦合电容器的容量、必要的电源电路的响应特性的一个参数。主机设备的电源电路被要求能够供给该峰值电流。

电压范围包含电源电压被容许变动的范围。主机设备的电源电路被要求即使存在布线、连接器的下降电压也保持电压以使得端子P处的电源电压落入该电压范围。

进一步,电源规格信息13a包括表示是否通过调节器53从电源电压PWR2生成电源电压PWR3的信息。如上述那样,调节器53能够在对端子P137、P138未施加电源电压PWR3的情况下从电源电压PWR2生成电源电压PWR3。此外,存储卡10也可以为:即使具有调节器53,也使用施加于端子P137、P138的电源电压PWR3。

如图19所示,主机设备判断是否能够省略以后的检查(S115)。例如,在S104、S107中为CLKREQ#=Low的情况下,当主机设备安装了足以用于访问闪速存储器13的电源电路时,主机设备使以后的检查为能够省略(S115:是),判断为存储卡10能够使用(S116)。

在不能省略检查的情况下(S115:否),主机设备从闪速存储器13读出电源规格信息13a(S117)。电源规格信息13a例如配置在MMIO上所映射的NVMe寄存器的VendorSpecific区域,经由物理层及存储器控制器52而载于包中以差分数据信号来进行输出。主机设备通过进行差分数据信号的解码,对包进行复原来取得电源规格信息13a。

主机设备对所读出的电源规格信息13a的电源要求规格和该主机设备的电源电路规格进行比较,判断存储卡10是否能够使用(S118)。在主机设备满足全部的电源要求规格的情况下(S118:是),主机设备安装了足以用于访问闪速存储器13的电源电路,因此,判断为存储卡10能够使用(S116)。

在主机设备不满足电源要求规格的情况下(S118:否),主机设备判断是否能够进行电源电压PWR1、PWR2、PWR3的调解(S119)。例如,在电源电压PWR1不足的情况下,主机设备若通过按由PCIe定义的功率状态(Power State)限制最大电力而能够使用存储卡10(S119:是),则进行该调解(S121),判断为存储卡10能够使用(S116)。另一方面,在无法调解的情况下(S119:否),主机设备不使用存储卡10(S120)。

另外,作为电源电压PWR1、PWR2、PWR3的调解,也可以具有降低电压的过程。例如,在电源规格信息13a中,施加了3.3V的电源电压PWR1能够以2.5V进行动作的情况下,主机设备能够通过使电源电压PWR1下降到2.5V来降低功耗,能够调解到存储卡10的电源要求与主机设备的电源能力一致的位置。

存储卡10能够安装多个电力模式。例如如上述那样,存储卡10能够安装多个功率状态或者功率限制。

作为功率状态,在PCIe中定义了DPA(Dynamic Power Allocation,动态功率分配),在NVMe中定义了DPS(Dynamic Power State,动态功率状态),哪个都可以使用。

主机设备根据电源能力,用PCIe包或者NVMe命令来对存储卡10设定能够使用的功率状态。例如如图20所示,本实施方式的存储卡10是支持了三个功率状态的例子。此外,存储卡10不限于该例子。峰值电流为瞬间的电流值,不是恒定电流,不依赖于功率状态,因此,为共用的设定。

功率状态A的功耗比功率状态B的功耗大。另外,功率状态B的功耗比功率状态C的功耗大。功耗越大,性能越高。在主机设备的电源电路不满足功率状态A时,通过设定为功率状态B,主机设备能够使用存储卡10。功率状态的选择项例如由其他PCIe寄存器或者NVMe命令来提供。

通过PCIe的初始化,决定PCIe总线性能,由此,决定存储卡10的最大性能,决定存储卡10的最大功耗。因此,通过存储卡10根据PCIe的初始化结果和从主机设备供给的电源电压值来改变功率状态的设定,主机设备能够对存储卡10的功耗进行控制。

存储卡10也可以与第1实施方式同样地使用功率限制(Slot Power Limit)来代替功率状态。

图21是表示第3实施方式的存储卡10的电源检查序列中的第1例的例示性时序图。以下,参照图19和图21对电源检查序列中的第1例进行说明。另外,该第1例涉及的存储卡10在图21中对与图19的各动作对应的定时赋予与该图19对应的标号。主机设备与存储卡10之间的接口使用基于电源电压PWR2的信号电压,因此,主机设备至少供给存储卡10的电源电压PWR2的范围内的电压。

首先,主机设备向存储卡10的端子P134供给电源电压PWR1(S101),向端子P131、P132供给电源电压PWR2(S102)。电源电压PWR3被设定为接地电平。存储卡10的初始化使用电源电压PWR3,因此,即使经过一定时间Tpok(S103),控制信号CLKREQ#的电平也保持High不变(S104:否)。因此,主机设备向存储卡10的端子P137、P138供给电源电压PWR3(S105)。

通过被供给电源电压PWR3,成为CLKREQ#=Low。因此,在经过一定时间Tpok后(S106),在CLKREQ#的电平检查时成为CLKREQ#=Low(S107:是),因此,主机设备能够识别为是需要3个电源的存储卡10。在从CLKREQ#=Low起经过Tck时间后,从主机设备供给差分参考时钟(S112)。另外,在经过TPVPGL时间后,复位信号PERST#被从Low无效(deassert)为High(S113)。

图22是表示第3实施方式的存储卡10的电源检查序列中的第2例的例示性时序图。以下,参照图19和图22对电源检查序列中的第2例进行说明。该第2例涉及的存储卡10能够通过调节器53从电源电压PWR1或者PWR2生成电源电压PWR3,能够仅用电源电压PWR1和PWR2来开始PCIe的初始化。

首先,主机设备向端子P134供给电源电压PWR1(S101),向存储卡10的端子P131、P132供给电源电压PWR2(S102)。通过被供给电源电压PWR1和PWR2,成为CLKREQ#=Low。因此,在经过一定时间Tpok后(S103),在CLKREQ#的电平检查时成为CLKREQ#=Low(S104:是),因此,主机设备能够识别为是需要PWR1和PWR2这两个电源、不需要PWR3的存储卡10。

图23是表示第3实施方式的存储卡10的电源检查序列中的第3例的例示性时序图。以下,参照图19和图23对电源检查序列中的第3例进行说明。

首先,主机设备向存储卡10的端子P134供给电源电压PWR1(S101),对端子P131、P132供给电源电压PWR2(S102)。即使经过一定时间Tpok(S103),控制信号CLKREQ#的电平也保持High不变(S104:否)。

主机设备对存储卡10的端子P137、P138供给电源电压PWR3(S105)。即使经过一定时间Tpok(S106),控制信号CLKREQ#的电平也保持High不变(S107:否)。因此,主机设备识别为该第3例涉及的存储卡10需要相对于电源电压PWR1、PWR2、PWR3而以不同于标准的电源电压进行动作。作为一个例子,存在如下情况:在某高性能的存储卡10在标准电源电压下该存储卡10的功耗过大时,降低电源电压来使用成为前提。

主机设备通过使电源电压PWR1、PWR3断开(off)而仅施加PWR2(S108),若能够进行PCIe的初始化,则成为CLKREQ#=Low。主机设备在经过一定时间Tpok后(S109),在CLKREQ#的电平检查时成为CLKREQ#=Low(S110:是),因此,执行PCIe的初始化(S112、S113、S114)。

如上述那样,第3例涉及的存储卡10以特殊的电源电压进行动作,因此,主机设备不省略检查(S115:否),读出电源规格信息13a(S117)。第3例的卡能够仅用电源电压PWR2来进行PCIe的初始化,电源规格信息13a成为能够读出。在电源规格信息13a的读出中使用电源电压PWR1的情况下,在S101中供给电源电压PWR1,因此,主机设备也可以在电源电压PWR1被断开之前读出电源规格信息13a。主机设备暂时漏过电源电压PWR2,按照电源规格信息13a供给电源电压PWR1、PWR2、PWR3的电压,从最初起执行通电序列。此外,例如在主机设备预先识别了所使用的存储卡10的电源规格的情况下,即使是以特殊的电源电压进行动作的存储卡10,也可以省略检查(S115:是)。

图24是表示第3实施方式的存储卡10的电源检查序列中的第4例的例示性时序图。第4例是一般的PCIe的通电序列。如图24所示,主机设备从最初起供给存储卡10能够动作的三个电源电压PWR1、PWR2、PWR3。在该情况下表示:与是否使用电源电压PWR3无关,省略检查,输出CLKREQ#=Low,能够进行存储器访问。由此,得到与一般的PCIe的通电序列的互换性。

另外,存在如下情况:在如仅以特定的主机设备与特定的存储卡10的组合进行使用那样的环境中,主机设备预先识别了存储卡10的电源规格。在该情况下,主机设备也可以不执行电源检测序列而从最初起施加所需要的所有电源电压来开始初始化。在该情况下,也通过成为CLKREQ#=Low来表示能够进行存储器访问。

有时为了高速访问闪速存储器13而使用大的电流。但是,由PCIe的初始化消耗的电流比用于高速访问的电流少就可以了。因此,安装最低限度的电源电流,也能够读出所述电源规格信息13a。主机设备能够根据所述电源规格信息13a来得到最适于存储卡10的电源电压PWR1、PWR2、PWR3的信息。

在以上的电源检查序列中,存储卡10的卡控制器14判定是否能够通过施加于端子P131、P132、P134、P137、P138的电源电压PWR1、PWR2、PWR3的组合来进行基于差分数据信号的存储器访问,从端子P135输出判定结果。进一步,闪速存储器13当基于差分数据信号的PCIe的初始化完成时,记录于该闪速存储器13的电源规格信息13a成为能够读出。另外,存储卡10的卡控制器14根据施加于端子P131、P132、P134、P137、P138的电源电压PWR1、PWR2、PWR3的组合和PCIe的初始化的结果来对存储器访问性能进行控制,对功率状态信息进行变更。

通过以上的电源检查序列,即使混合存在具有各个电源规格的多个种类的存储卡10,主机设备也能够识别该电源规格。此外,通过预先确定存储卡10和所对应的主机设备的电源规格,能够省略电源检查序列。

存储卡10不支持热插拔,因此,在主机设备、连接器采用应对方法。存储卡10的更换在存储卡10的电源断开的状态下进行。

主机设备使用存储卡10向连接器的插入检测来进行控制,以使得在安装了存储卡10之后接入电源。另外,当在向存储卡10供给着电源的期间拔下存储卡10时会发生数据丢失,因此,通过连接器具有锁定功能,能够防止其发生。在更换存储卡10的情况下,主机设备进行存储卡10的关断(shutdown)处理,在关断处理完成后停止电源供给,解除连接器的锁定功能。由此,能够抑制存储卡10的不小心的取下,保护存储卡10的数据。

在存储卡10的更换总是在电源断开的状态下进行的主机系统的情况下,不需要对存储卡10的插拔进行检测的功能。连接器具有能够检测是否安装着存储卡10的信号即可。该主机系统通过用电源接入后的存储卡10的初始化来对PCIe PHY的存在进行确认,也能够对存储卡10的存在进行判定。

图25是表示第3实施方式的存储卡10的温度检查序列中的卡控制器14的动作的例示性流程图。例如,在主机设备的散热机构的设计中,有时使用存储卡10的温度的信息。为了该设计,卡控制器14如以下说明的那样根据要求来向主机设备发送与存储卡10的温度有关的信息。

如图25所示,卡控制器14判断是否接到来自主机设备的温度信息的读出要求(S201)。在主机设备的散热机构的设计中,例如使用存储卡10为最大性能(performance)状态(最大功耗状态)的情况下的存储卡10的表面温度。因此,主机设备例如在卡控制器14对闪速存储器13连续地进行着写入(write)的情况下、或者连续地进行着读出(read)的情况下,向存储卡10发送读出要求。

卡控制器14当接收到来自主机设备的温度信息的读出要求时(S201:是),读入设置于存储卡10的温度传感器111的值(S202)。例如温度传感器111的值表示卡控制器14的结(junction)温。

如图17和图18所示,温度传感器111作为不同于卡控制器14的部件设置于存储卡10。温度传感器111例如搭载于卡控制器14的上侧的面或者下侧的面。卡控制器14例如经由温度传感器接口(I/F)读取温度传感器111的值。

此外,温度传感器111也可以设置在卡控制器14的内部。例如,温度传感器111也可以是使用内置于卡控制器14的电阻来作为半导体温度传感器的部件。温度传感器111通过配置在卡控制器内的最发热的电路附近,能够检测控制器的结温。当卡控制器14接收到温度信息的读出要求时,卡控制器14的CPU通过读出表示半导体温度传感器的值的寄存器的值,能够取得结温的信息。

上述的半导体温度传感器的电阻值伴随着温度变化而变化。通过预先测定温度与电阻值之间的特性,能够反向地根据电阻值计算温度。因此,卡控制器14通过测定半导体温度传感器的电阻值,能够变换为结温。

不限于电阻,温度传感器111也可以是:特性因温度变化而变化的其他元件被作为半导体传感器来使用的部件。被作为半导体传感器来利用的元件例如在流动了一定的电流的情况下,两端的电位差与温度相应地变化。因此,使用预先基于实际测量来算出的该元件的温度-电压特性,能够根据元件的两端的电位差算出温度。

在上述元件被作为半导体传感器来利用的情况下,例如测定电压的A/D转换器连接于该元件。基于A/D转换器所测定的电压值和元件的温度-电压特性,算出卡控制器14的结温。卡控制器14的CPU能够经由寄存器读出所算出的结温的信息。

接着,卡控制器14将从温度传感器111读入的结温变换为存储卡10的表面温度(S203)。结温和存储卡10的表面温度例如根据描述于固件的变换表或者变换式来进行变换。

上述固件保存于闪速存储器13、或者卡控制器14的非易失性存储器。在存储卡10接受了电源供给时,卡控制器14的CPU将所保存的固件读出到卡控制器14的存储器并加以执行。

卡控制器14使用保存于闪速存储器13、或者卡控制器14的非易失性存储器的变换表或者变换式,将结温变换为存储卡10的表面温度。变换表和变换式例如通过在存储卡10的出厂前实际测量最大性能状态(最大功耗状态)的结温和表面温度、并根据该实际测量结果算出结温与表面温度的关系来进行制作。另外,变换表和变换式例如也可以通过基于闪速存储器13的种类及结构、卡控制器14的配置以及壳体11的材料的计算来制作。在实际测量中,通常测定卡控制器14附近的表面温度。

接着,卡控制器14将存储卡10的表面温度的信息作为温度信息的读出要求的响应来发送给主机设备(S204)。此外,卡控制器14既可以发送表面温度和结温,也可以仅发送某一方的温度。

主机设备的表面温度的读出要求例如是:包括对存储卡10要求包含温度信息的S.M.A.R.T.(Self-Monitoring Analysis and Reporting Technology,自动监视分析及报告技术)信息的字段的命令。

在存储卡10与主机设备的连接遵循NVMe的情况下,主机设备例如使用描述于NVMExpress Revision 1.3的SMART/Health Information命令,来作为要求S.M.A.R.T.信息的命令。存储卡10也可以对于该命令,向主机设备通知:将结温设定于CompositeTemperature字段、将根据结温变换得到的存储卡10的表面温度设定于预留区域(Reservearea)的响应。

在存储卡10与主机设备的连接遵循SMBus的情况下,例如主机设备对被分配给SMBus的特定地址的信息读出命令进行分配而发送给存储卡10。存储卡10对于该命令,向主机设备送回将温度信息保存在了预定区域的响应。在该情况下,端子P136(CONTA)、端子P139(CONTB)被分配为双线式的SMBus接口信号,存储卡10也可以使用端子P136、P139从主机设备接收表面温度的读出要求,发送存储卡10的表面温度信息。

通过以上的温度检查序列,存储卡10的温度信息被提供给主机设备。所提供的温度信息例如能够利用于主机设备的散热机构的特性解析、主机设备的散热机构的确认。

存储卡10的温度检查序列不限于上述的例子。例如,温度传感器111也可以测定闪速存储器13表面的温度。在该情况下,卡控制器14也可以将从温度传感器111取得的温度信息作为闪速存储器13的结温来变换为存储卡10的表面温度。该情况下的表面温度表示闪速存储器13附近的表面温度。

在以上说明的第3实施方式涉及的存储卡10中,壳体11具有在X轴方向上延伸的第1边缘31、位于第1边缘31的相反侧并在X轴方向上延伸的第4边缘34、在与X轴方向交叉的Y轴方向上延伸的第2边缘32以及形成第1边缘31与第2边缘32之间的缺口C的第1角部35。形成缺口C的第1角部35例如被用于防止存储卡10插反。因此,在存储卡10例如被插入到推拉类型的连接器的情况下,存储卡10被从第1边缘31插入到连接器。并且,多个端子P形成相互隔着间隔而在Y轴方向上排列的第1列R11、R12和第2列R21。第1列R11、R12分别包括在距第1边缘31比距第4边缘34近的位置相互隔着间隔而在X轴方向上排列的多个端子P。第2列R21分别包括在距第4边缘34比距第1边缘31近的位置相互隔着间隔而在X轴方向上排列的多个端子P。这样,通过多个端子P形成多个列(R11、R12、R21),本实施方式的存储卡10能够使通信接口高速化。

一般而言,越是连接器的进深侧,被插入到了连接器的存储卡10的端子P与主机控制器之间的布线的长度越短。即,第1列R11、R12所包括的端子P与主机控制器之间的布线的长度,比第2列R21所包括的端子P与主机控制器之间的布线的长度短。因此,第1列R11、R12所包括的被用于传输信号的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125比第2列R21所包括的被用于传输信号的端子P128、P129、P133、P135、P136、P139容易确保信号完整性。例如,通过使第1列R11、R12所包括的被用于传输信号的端子P的数量比第2列R21所包括的被用于传输信号的端子P的数量多、使得第1列R11、R12所包括的端子P被用于传输差分信号,本实施方式的存储卡10能够使通信接口高速化。

第1列R11、R12所包括的信号端子(端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125)的数量比第2列R21所包括的信号端子(端子P128、P129、P133、P135、P136、P139)的数量多。由此,本实施方式的存储卡10能够使通信接口高速化。

另外,通过第1列R11、R12被同时用于数据传送,本实施方式的存储卡10能够使通信接口高速化。

进一步,多个端子P形成第1列R11、R12和第2列R21。由此,与将全部端子P排列为一列的情况相比,能够确保端子P的所希望的大小、多个端子P的所希望的间隔。

被用于传输频率比端子P128、P129、P133、P135、P136、P139的信号的频率高的信号的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P120、P121、P124、P125包含于第1列R11、R12。由此,本实施方式的存储卡10能够使通信接口高速化。

通过增加被分配给了差分数据信号的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P120、P121、P124、P125而增加通道数量,本实施方式的存储卡10能够使通信接口高速化。

形成第1列R11、R12的多个端子P包括被分配给差分数据信号的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125。另一方面,形成第2列R21的多个端子P包括:被分配给频率比差分数据信号低的差分时钟信号的端子P128、P129;被分配给单端信号的端子P133、P135、P136、P139;以及被分配给电源的端子P131、P132、P134、P137、P138。由此,在第1列R11、R12中,能够通过能高速地传输信号的端子P102、P103、P105、P106、P108、P109、P111、P112、P115、P116、P118、P119、P121、P122、P124、P125来使通道数量更多,本实施方式的存储卡10能够使通信接口高速化。

形成第1列R11的多个端子P包括被分配给了差分数据信号的两个通道的端子P102、P103、P105、P106、P108、P109、P111、P112。形成第1列R12的多个端子P包括被分配给了差分数据信号的两个通道的端子P115、P116、P118、P119、P121、P122、P124、P125。由此,本实施方式的存储卡10能够使通信接口高速化。

被分配给了差分数据信号的多对端子P102、P103、P105、P106、P108、P109、P111、P112分别位于被分配给了接地的多个端子P101、P104、P107、P110、P113中的两个之间。由此,能够按差分信号来确保返回路径,减少差分信号间的相互干扰,工作信号电平得以稳定化。

被分配给了差分数据信号的多对端子P115、P116、P118、P119、P121、P122、P124、P125分别位于被分配给了接地的多个端子P114、P117、P120、P123、P126中的两个之间。由此,能够按差分信号来确保返回路径,减少差分信号间的相互干扰,工作信号电平得以稳定化。

端子P134被分配给第1电源PWR1。端子P131、P132被分配给电压为第1电源PWR1以下的第2电源PWR2。端子P137、P138被分配给电压为第2电源PWR2以下的第3电源PWR3。由此,能够根据用途来分开使用第1至第3电源PWR1、PWR2、PWR3,存储卡10的灵活性提高。进一步,电压越低,电源电压变动的容许值越小,因此,减小在一个端子P中流动的电流值为好,通过设置多个端子P131、P132和多个端子P137、P138,电流值被分散,平均每一个端子的电流值变小,电压变动得到抑制。

调节器53在被分配给了电源电压PWR3的第3电源PWR3的端子P137、P138接地连接了的情况下,从对被分配给了电源电压PWR2的第2电源PWR2的端子P131、P132所施加的电源电压PWR2或者对被分配给了电源电压PWR1的第1电源PWR1的端子P134所施加的电源电压PWR1,生成电源电压PWR3。由此,本实施方式的存储卡10能够支持PWR1、PWR2的两电源结构的主机设备和PWR1、PWR2、PWR3的三电源结构的主机设备中的任何设备。

卡控制器14判定是否能够通过施加于端子P131、P132、P134、P137、P138的电源电压PWR1、PWR2、PWR3的组合来进行基于差分数据信号的存储器访问,从被分配给了CLKREQ#的端子P135输出判定结果。闪速存储器13在能够进行基于差分数据信号的存储器访问的情况下,存储于该闪速存储器13的电源规格信息13a成为能够读出。主机设备通过对电源规格信息13a和该主机设备的电源规格进行比较,能够判断存储卡10是否能够使用。由此,即使混合存在具有多个种类的电源结构的存储卡10,主机设备也能够识别存储卡10的电源规格。

至少卡控制器14的一部分的边14a位于第1列R11、R12与第2列R21之间,并且,能够将通过布线W连接于第1列R11所包括的端子P102、P103、P105、P106、P108、P109、P111、P112的连接端子CP配置于边14a。对于第1列R12,也同样地能够将通过布线W连接于其所包括的端子P115、P116、P118、P119、P121、P122、P124、P125的连接端子CP配置于边14a。由此,能够实现:不存在布线W绕过其他布线和/或其他部件、在第2列R21所包括的多个端子P之间通过的情况的布线。因此,例如在布线W设置ESD保护二极管43变得容易,并且,能够缩短第1列R11所包括的端子P102、P103、P105、P106、P108、P109、P111、P112、第1列R12所包括的端子P115、P116、P118、P119、P121、P122、P124、P125与连接端子CP之间的布线W的长度。

存储卡10的X轴方向上的长度为14±0.1mm,Y轴方向上的长度为18±0.1mm。一般而言,microSD卡的尺寸为11mm×15mm。即,本实施方式的存储卡10比microSD卡大。因此,存储卡10例如能够搭载如大型的三维闪速存储器那样的难以搭载于microSD卡的存储容量和尺寸大的存储器芯片,例如能够应对由技术进步带来的将来的闪速存储器13的芯片尺寸的大型化。进一步,存储卡10比microSD卡大,比标准的SD存储卡小。因此,存储卡10对于主机设备来说不会过大,并且,也容易进行向主机设备的连接器的插拔。

壳体11还具有位于第2边缘32的相反侧并在Y轴方向上延伸的第3边缘33、和第1边缘31与第3边缘33之间的第2角部36。第1角部35的形状与第2角部36的形状互不相同。由此,能抑制存储卡10插反。

第1角部35在第1边缘31的一方的端部与第2边缘32的端部之间呈直线状延伸,形成进行了所谓的C1.1的斜倒角的部分。第2角部36在第1边缘31的另一方的端部与第3边缘33的端部之间呈圆弧状延伸,形成进行了所谓的R0.2的圆倒角的部分。存储卡10有时在第2角部36抵接于连接器的状态下被插入到该连接器。在该情况下,能够减小X轴方向上的存储卡10的位置错开。

第1列R11、R12配置在第1边缘31的附近。第2列R21位于距第4边缘34比距第1边缘31近的位置。即,第1列R11、R12位于Y轴方向上的存储卡10和壳体11的中心线与第1边缘31之间,第2列R21位于上述中心线与第4边缘34之间。因此,通过连接器的引线架101、102、103作用于存储卡10的压力在上述中心线与第1边缘31之间的区域和上述中心线与第4边缘34之间的区域被均匀化,存储卡10在连接器内会更稳定。

X轴方向上的端子P的宽度和相邻的端子P之间的距离为能够形成连接器的端子、能够形成基板的占用空间(footprint)的最小尺寸。因此,第1列R11、R12和第2列R21的端子P的数量为相同的13个。第1列R11包括PCIe的2个通道,第1列R12也包括PCIe的2个通道。形成第1列R11和第2列R21的图15的存储卡10能够使用PCIe的2个通道。形成第1列R11、R12和第2列R21的图13的存储卡10能够使用PCIe的4个通道,能够进行高速化。

作为主机设备,可以构成仅使用第1列R11的第1主机设备和使用第1列R11以及第1列R12的第2主机设备。第1主机设备以及第2主机设备和图13的存储卡10以及图15的存储卡10,能够以全部主机设备与存储卡10的组合来进行使用。

另外,各PCIe通道至少具有Gen.3的性能,能够支持Gen.4的性能。主机设备具有宽泛的通信速度的选择项,能够选择最适于应用(application)的性能且功耗最少的总线性能。

在第1主机设备或者图15的存储卡10的情况下,第1列R12不被用于通信。但是,能够通过引线架102使存储卡10进行散热。引线架102无论是与第1列R12的端子P接触,还是与壳体11的第1面21接触,都能够使存储卡10进行散热。第1主机设备也可以具有散热专用的电连接于接地的引线架102。

通过在第2列R21下配置闪速存储器13,第2列R21能够被用于闪速存储器13的散热。例如,与第2列R21接触的引线架103使闪速存储器13进行散热。

如上所述,不仅是在连接器中与第2面22接触的散热机构,与第1面21接触的大量的引线架101、102、103也能够利用于存储卡10的散热。通过从第1面21和第2面22这两方进行散热,存储卡10的散热能力和散热效果提高。

在各个第1列R11、R12中,端子P的距第1边缘31远的一侧的端部在Y轴方向上对齐于同一位置。与第1列R12相比、距第1边缘31近的第1列R11所包括的信号用的端子P102、P103、P105、P106、P108、P109、P111、P112各自的Y轴方向上的长度,比接地用的端子P101、P104、P107、P110、P113各自的Y轴方向上的长度短,并且,第1列R12所包括的端子P114~P126各自的Y轴方向上的长度相等。由此,在存储卡10沿着Y轴方向被插入到主机设备的连接器时,接地用的端子P101、P104、P107、P110、P113、P127、P130和电源用的端子P131、P132、P134、P137、P138比信号用的端子P102、P103、P105、P106、P108、P109、P111、P112、P128、P129、P133、P135、P136、P139先接触连接器的引线架。因此,主机设备的GND电平和存储卡10的GND电平成为等效,能够使卡控制器14的电气上的电平稳定。进一步,第1列R11的接地用的端子P101、P104、P107、P110、P113先接触连接器的引线架,因此,不需要增长第1列R12的接地用的端子P。因此,能够缩短第1列R12的全部端子P的Y轴方向上的长度,能够缩短第1列R11、R12的间隔。因此,能够增宽第1列R12与第2列R21的间隔,能够确保对在图14的相互相反的方向上延伸的引线架102、103进行配置的区域。

关于第2列R21、R22所包括的端子P的形状和长度,由于该端子P使用的信号的频率低,因此,能够任意地进行设定。例如,如图13和图15所示,在多个端子P形成多个第2列R21、R22的情况下,在各个第2列R21、R22中,端子P的距第1边缘31远的一侧的端部在Y轴方向上对齐于同一位置。进一步,与第2列R22相比、距第1边缘31近的第2列R21所包括的信号用的端子P128、P129、P133、P135、P136、P139各自的Y轴正方向上的长度,被设为比接地用的端子P127、P130以及电源用的端子P131、P132、P134、P137、P138各自的Y轴方向上的长度短。

在Y轴方向上,第2列R22所包括的信号用的端子P的长度也可以比第2列R22所包括的电源用以及接地用的端子P的长度短。另外,在第2列R22包括电源用的端子P的情况下,该电源用的端子P也可以是与第2列R21所包括的电源用的端子P相同的形状。

第1列R11、R12所包括的信号用的端子P的X轴方向上的各自的长度相等。由此,能够使第1列R11、R12所包括的信号用的端子P的电气特性相似。

在X轴方向上,第1列R11、R12所包括的信号用的端子P的长度与接地用的端子P的长度也可以不同。在该情况下,例如在X轴方向上,信号用的端子P各自的长度被设为相互相等,接地用的端子P各自的长度被设为相互相等。此外,X轴方向上的端子P的长度不限于该例子。

以上,对存储卡10的一个形状因数进行了说明。但是,存储卡10的形状因数也可以相对于以上说明的存储卡10的形状因数,保持形成第1列R11和第2列R21的端子P的位置不变地使外形和端子P的数量扩张。

例如,存储卡10的外形能够在X轴方向、Y轴方向以及Z轴方向中的至少一个方向上进行扩大。在外形扩大了的存储卡10的形状因数中,形成第1列R11、R12的端子P的数量能够被扩张。例如,第1列R11、R12所包括的端子P的数量可以被设定为比13个多。另外,多个端子P可以形成比两个多的第1列R11、R12、R13、R14、……。

扩张后的第1列R13、R14、……,相对于第1列R11、R12,既可以在Y轴的负方向上排列,也可以在Y轴的正方向上排列。在第1列R13、R14、……相对于第1列R11、R12而在Y轴的负方向上排列的情况下,第1列R13、R14、……所包括的端子P的形状与第1列R12所包括的端子P的形状相同。

在外形扩大后的存储卡10的形状因数中,形成第2列R21、R22的端子P的数量也可以被扩张。例如,多个端子P可以形成比两个多的第2列R21、R22、R23、R24、……。扩张后的第2列R23、R24、……所包括的端子P的形状可以被任意地进行设定。

一个形状因数涉及的存储卡10例如也可以通过使用适配器,使得能够由用于更大的形状因数涉及的存储卡10的连接器进行使用。在该连接器和用于上述一个形状因数涉及的存储卡10的连接器中,引线架101、102、103的相对位置相同。

(第4实施方式)

以下,参照图26对第4实施方式进行说明。图26是表示第4实施方式涉及的存储卡10的例示性俯视图。如图26所示,第4实施方式涉及的卡控制器14层叠于闪速存储器13。

闪速存储器13与第2列R21所包括的端子P重叠。根据其他表现,闪速存储器13能够配置为:使得第2列R21所包括的端子P位于该闪速存储器13的Y轴的正方向上的端部与Y轴的负方向上的端部之间。另一方面,闪速存储器13的芯片面积根据存储器容量而不同,存在靠近第1列R11、R12所包括的端子P的情况和离开第1列R11、R12所包括的端子P的情况。

卡控制器14位于第1列R11、R12与第2列R21之间。因此,与第3实施方式同样地,卡控制器14的多个连接端子CP也能够配置在第1列R11、R12与第2列R21之间。布线W将连接端子CP和第1列R11所包括的端子P连接。

如以上说明的第4实施方式的存储卡10那样,卡控制器14也可以层叠于闪速存储器13。通过闪速存储器13位于离开第1列R11、R12的位置且连接端子CP位于第1列R11、R12与第2列R21之间,能抑制卡控制器14的布线W的长度变长。

根据以上说明的至少一个实施方式,壳体具有在第1方向上延伸的第1边缘、在与第1方向交叉的第2方向上延伸的第2边缘以及形成第1边缘与第2边缘之间的缺口的第1角部。形成缺口的第1角部例如被用于防止半导体存储装置插反。因此,在半导体存储装置例如被插入到推拉类型的连接器的情况下,半导体存储装置被从第1边缘插入到连接器。并且,多个端子相互隔着间隔在第1方向上排列而形成第1列,并且,在与第1列相比、距第1边缘远的位置相互隔着间隔在第1方向上排列而形成至少一个第2列。通过多个端子形成多个列,本实施方式的半导体存储装置能够使通信接口高速化。

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,并不是意在限定发明的范围。这些新的实施方式能够以其他各种各样的方式来实施,能够在不脱离发明的宗旨的范围内进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围、宗旨内,并且,包含在权利要求书记载的发明及其等同的范围内。

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统