移位寄存器电路和包括该移位寄存器电路的发光显示装置

文献发布时间:2023-06-19 11:42:32

技术领域

本公开涉及移位寄存器电路和包括该移位寄存器电路的发光显示装置。

背景技术

随着信息技术的进步,作为用户和信息之间的连接介质的显示装置的市场已经增长。因此,越来越多地使用诸如发光显示(LED)装置、量子点显示(QDD)装置和液晶显示(LCD)装置的各种类型的显示装置。

上述显示装置包括:包括子像素的显示面板、输出用于驱动显示面板的驱动信号的驱动电路、以及生成要提供给显示面板或驱动器电路的电源的电源。

如果将驱动信号(例如,扫描信号和数据信号)提供给子像素,则这种显示装置可以以形成在显示面板中的子像素透射光或直接发射光的方式来显示图像。

同时,在上述显示装置当中,发光显示装置在诸如快速响应速度、高亮度和宽视角的电学和光学特性以及使得显示装置能够实现为柔性类型的机械特性方面具有优点。然而,发光显示装置需要改进显示面板的结构和驱动方法,因此将需要相关的连续研究。

发明内容

本公开是鉴于上述问题而提出的,并且本公开的目的是提供一种移位寄存器电路和包括该移位寄存器电路的发光显示装置,其中,即使电路被实现为基于共用移位寄存器的节点的电路输出多个扫描信号,也提高了电路的驱动稳定性,并且产生了均匀的输出。

本公开的另一个目的是提供一种移位寄存器电路和包括该移位寄存器电路的发光显示装置,其中,基于输出多个扫描信号的电路来实现窄边框。

除了如上所述的本公开的目的之外,本领域技术人员将从本公开的以下描述中清楚地理解本公开的另外的目的和特征。

根据本公开的一个方面,可以通过提供包括移位寄存器和信号输出电路的移位寄存器电路来实现上述和其它目的,所述信号输出电路包括通过与所述移位寄存器连接而操作以分别输出J个扫描信号的J个扫描信号输出电路(J是2或更大的整数)。所述J个扫描信号输出电路共用所述移位寄存器的第一QB节点和第二QB节点、所述移位寄存器的公共输出端子、以及第一电压线,基于所述第一QB节点的电位、所述第二QB节点的电位、通过所述公共输出端子输出的公共输出信号、通过所述第一电压线传送的第一电压、以及通过第I时钟信号线传送的第I时钟信号进行操作,并且通过分别被分开的输出端子输出所述J个扫描信号。

所述J个扫描信号输出电路可以包括:第一晶体管,其基于所述第一电压而导通,输出所述公共输出信号;第二晶体管,其基于所述公共输出信号而导通,基于所述第I时钟信号输出扫描高电压的所述J个扫描信号;第三晶体管,其基于所述移位寄存器的所述第一QB节点的所述电位而导通,基于第二电压输出扫描低电压的所述J个扫描信号;以及第四晶体管,其基于所述移位寄存器的所述第二QB节点的所述电位而导通,基于所述第二电压输出扫描低电压的所述J个扫描信号。

所述J个扫描信号输出电路可以包括:第一晶体管,其具有连接到所述第一电压线的栅极电极和连接到所述移位寄存器的所述公共输出端子的第一电极;第二晶体管,其具有连接到所述第一晶体管的第二电极的栅极电极、连接到所述第I时钟信号线的第一电极、以及连接到输出端子的第二电极;第三晶体管,其具有连接到所述移位寄存器的所述第一QB节点的栅极电极、连接到所述输出端子的第一电极、以及连接到第二电压线的第二电极;以及第四晶体管,其具有连接到所述移位寄存器的所述第二QB节点的栅极电极、连接到所述输出端子的第一电极、以及连接到所述第二电压线的第二电极。

根据本公开的另一方面,可以通过提供一种发光显示装置来实现上述和其它目的,该发光显示装置包括:显示面板,该显示面板显示图像;以及信号输出电路,其连接到所述显示面板的扫描线,包括移位寄存器和通过与所述移位寄存器连接而操作以分别输出J个扫描信号的J个扫描信号输出电路(J是2或更大的整数),其中,所述J个扫描信号输出电路共用所述移位寄存器的第一QB节点和第二QB节点、所述移位缓存器的公共输出端子、以及第一电压线,基于所述第一QB节点的电位、所述第二QB节点的电位、通过所述公共输出端子输出的公共输出信号、通过所述第一电压线传送的第一电压、以及第I时钟信号进行操作,并且通过被分别分开的输出端子输出所述J个扫描信号。

所述J个扫描信号输出电路可以包括:第一晶体管,其基于所述第一电压而导通,输出所述公共输出信号;第二晶体管,其基于所述公共输出信号而导通,基于所述第I时钟信号输出扫描高电压的所述J个扫描信号;第三晶体管,其基于所述移位寄存器的所述第一QB节点的所述电位而导通,基于第二电压输出扫描低电压的所述J个扫描信号;以及第四晶体管,其基于所述移位寄存器的所述第二QB节点的所述电位而导通,基于所述第二电压输出扫描低电压的所述J个扫描信号。

所述J个扫描信号输出电路可以包括:第一晶体管,其具有连接到所述第一电压线的栅极电极和连接到所述移位寄存器的所述公共输出端子的第一电极;第二晶体管,其具有连接到所述第一晶体管的第二电极的栅极电极、连接到第I时钟信号线的第一电极、以及连接到输出端子的第二电极;第三晶体管,其具有连接到所述移位寄存器的所述第一QB节点的栅极电极、连接到所述输出端子的第一电极、以及连接到第二电压线的第二电极;以及第四晶体管,其具有连接到所述移位寄存器的所述第二QB节点的栅极电极、连接到所述输出端子的第一电极、以及连接到所述第二电压线的第二电极。

所述J个扫描信号输出电路可以包括:第一扫描信号输出电路,其被导通以对应于第一节点的电位,输出第一扫描信号;第二扫描信号输出电路,其被导通以对应于第二节点的电位,输出第二扫描信号;第三扫描信号输出电路,其被导通以对应于第三节点的电位,输出第三扫描信号;以及第四扫描信号输出电路,其被导通以对应于第四节点的电位,输出第四扫描信号,并且所述第一节点至所述第四节点可以顺序地充电以高电压。

根据本公开的实施方式,即使电路被实现为基于共用所述移位寄存器的节点的电路来输出多个扫描信号,也可以防止出现所述节点的电压降(可以防止共用节点的负载增加),从而可以提高所述电路的驱动稳定性,并且可以产生均匀的输出。此外,由于当实现用于输出所述扫描信号的所述电路时可以显著地减少所使用的晶体管的数量,因此即使添加补偿电路以增加电路的驱动稳定性、可靠性和寿命,也可以实现窄边框。

除了如上所述的本公开的效果之外,本领域技术人员将从本公开的上述描述中清楚地理解本公开另外的优点和特征。

附图说明

从下面结合附图进行的详细描述中,将更加清楚地理解本公开的上述及其它目的、特征及其它优点,在附图中:

图1是示出根据本公开的实施方式的有机电致发光显示装置的框图;

图2是示出了图1所示的子像素的示意图;

图3是示出根据本公开的实施方式的包括补偿电路的子像素的等效电路;

图4和图5是可基于图3中的子像素实现的像素的示例性视图;

图6是示出根据本公开的实施方式的面板内选通类型的扫描驱动器的布置示例的视图;

图7是示出与面板内选通类型的扫描驱动器相关的装置的第一示意性示例性视图;

图8是示出与面板内选通类型的扫描驱动器相关的装置的第二示意性示例性视图;

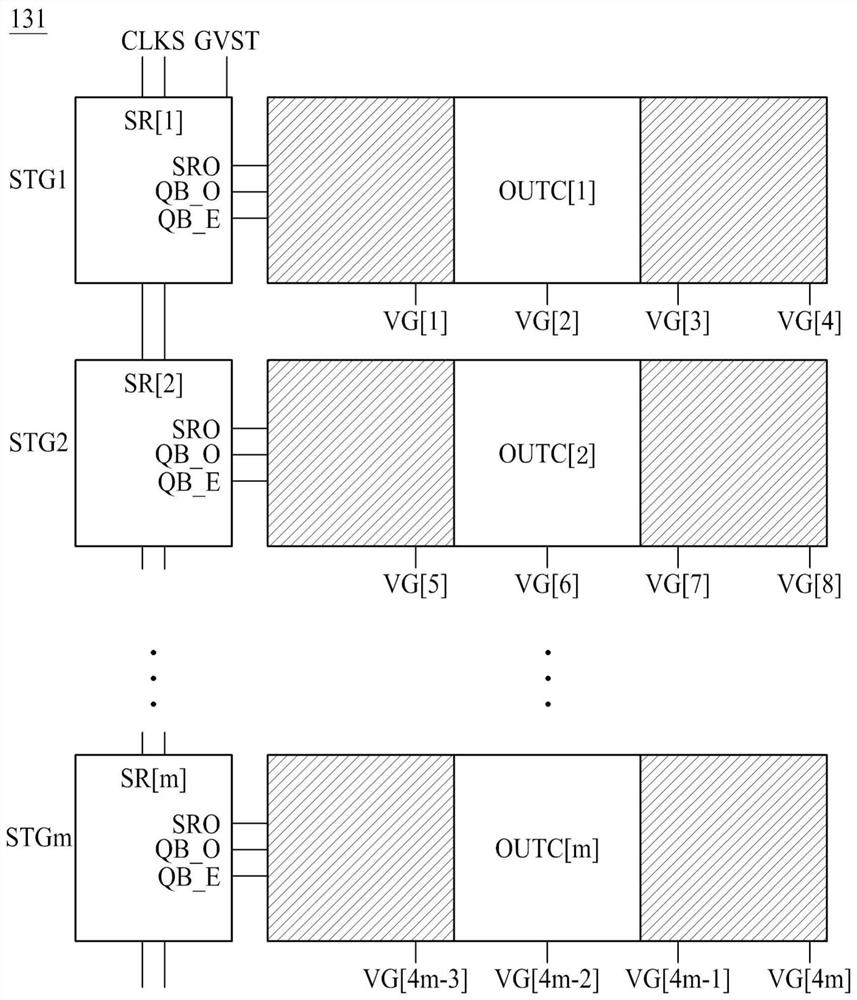

图9是示出根据本公开的实施方式的移位寄存器电路的视图;

图10是示出根据本公开的实施方式的移位寄存器电路的特性的视图;

图11是示出根据本公开的实施方式的移位寄存器电路的信号输出电路的详细电路图;

图12是示出根据本公开的实施方式的信号输出电路的操作的视图;

图13是示出根据本公开的实施方式的驱动信号输出电路所需的时钟信号的波形;

图14是示出根据本公开的实施方式的信号输出电路的节点电压和输出电压的视图;以及

图15和图16是示出根据本公开的实施方式的信号输出电路的优点的视图。

具体实施方式

在下文中,将参照附图描述用于实施本公开的细节。

根据本公开的显示装置可以实现为但不限于电视机、视频播放器、个人计算机(PC)、家庭影院、汽车电气装置、智能电话等。发光显示装置可实现为发光显示(LED)装置、量子点显示(QDD)装置和液晶显示(LCD)装置等。在下文中,为了便于描述,将描述用于通过直接发光来显示图像的发光显示装置作为示例。发光显示装置可以基于无机发光二极管或有机发光二极管来实现。在下文中,为了便于描述,将基于有机发光二极管给出描述。

此外,稍后将描述的装置包括N型薄膜晶体管作为示例,但是也可以实现为P型薄膜晶体管或者可以实现为其中N型和P型薄膜晶体管共存的类型。薄膜晶体管可以是包括栅极、源极和漏极的三电极装置。源极是向薄膜晶体管提供载流子的电极。在薄膜晶体管中,载流子开始从源极流动。漏极是将载流子从薄膜晶体管供应到外部的电极。即,在薄膜晶体管中,载流子从源极流向漏极。

在N型薄膜晶体管中,由于载流子是电子,因此源极电压低于漏极电压,使得电子从源极流向漏极。在N型薄膜晶体管中,由于电子从源极流向漏极,所以电流从漏极流向源极。与N型薄膜晶体管不同,在P型薄膜晶体管中,由于载流子是空穴,因此源极电压高于漏极电压,以使空穴从源极流向漏极。在P型薄膜晶体管中,由于空穴从源极流向漏极,所以电流从源极流到漏极。然而,薄膜晶体管的源极和漏极可以根据所施加的电压而改变。在这点上,在下面的描述中,源极和漏极中的任何一个将被称为第一电极,而另一个被称为第二电极。

图1是示出根据本公开的实施方式的有机电致发光显示装置的框图,图2是示出了图1所示的子像素的示意图。

如图1和图2中所示,根据本公开实施方式的电致发光显示装置包括图像供应器110、定时控制器120、扫描驱动器130、数据驱动器140、显示面板150和电源180。

图像供应器110(或主机系统)将各种驱动信号与外部供应的图像数据信号或存储在内部存储器中的图像数据信号一起输出。图像供应器110可以将数据信号和各种驱动信号供应到定时控制器120。

定时控制器120输出用于控制扫描驱动器130的操作定时的选通定时控制信号GDC、用于控制数据驱动器140的操作定时的数据定时控制信号DDC、以及各种同步信号(垂直同步信号Vsync和水平同步信号Hsync)。

定时控制器120将从图像供应器110供应的数据信号DATA与数据定时控制信号DDC一起供应到数据驱动器140。定时控制器120可以以集成电路(IC)的形式形成,然后封装在印刷电路板上,但不限于此。

扫描驱动器130响应于从定时控制器120提供的栅极定时控制信号GDC而输出扫描信号(或扫描电压)。扫描驱动器130通过扫描线GL1至GLm将扫描信号提供给包括在显示面板150中的子像素。扫描驱动器130可以以IC(集成电路)的形式形成,或者可以以GIP(面板内选通)的形式直接形成在显示面板150上,但是不限于此。

数据驱动器140响应于从定时控制器120提供的数据定时控制信号DDC对数据信号DATA进行采样和锁存,并且基于伽马参考电压将数字型数据信号转换为模拟型数据电压。

数据驱动器140通过数据线DL1至DLn向包括在显示面板150中的子像素输出数据电压。数据驱动器140可以以IC的形式形成并封装在显示面板150或印刷电路板上,但不限于此。

电源180基于外部提供的外部输入电压输出高电位的第一面板电源EVDD和低电位的第二面板电源EVSS。电源180可以生成并输出驱动扫描驱动器130所需的电压或驱动数据驱动器140所需的电压(漏极电压或半漏极电压)以及第一面板电源EVDD和第二面板电源EVSS。

显示面板150响应于从包括扫描驱动器130和数据驱动器140的驱动器输出的扫描信号、包括数据电压的驱动信号以及从电源180输出的第一面板电源EVDD和第二面板电源EVSS来显示图像。显示面板150的子像素直接发光。

显示面板150可以基于诸如玻璃、硅和聚酰亚胺的具有刚性或柔性的基板来制造。发射光的子像素可以构成包括红色、绿色和蓝色的像素或者包括红色、绿色、蓝色和白色的像素。

例如,一个子像素SP包括像素电路,该像素电路包括开关晶体管SW、驱动晶体管、存储电容器和有机发光二极管。由于在有机电致发光显示装置中使用的子像素SP直接发光,所以其电路结构复杂。此外,存在用于补偿向有机发光二极管提供驱动电流的驱动晶体管和发射光的有机发光二极管的退化的各种补偿电路。因此,以块的形式示出了包括在子像素SP中的像素电路PC。

同时,在上述描述中,单独地设置定时控制器120、扫描驱动器130和数据驱动器140。然而,定时控制器120、扫描驱动器130和数据驱动器140中的一个或更多个可以根据发光显示装置的实现方式集成在一个IC中。

图3是示出包括根据本公开实施方式的补偿电路的子像素的等效电路,图4和图5是可以基于图3中的子像素实现的像素的示例性视图。

如图3所示,包括补偿电路的子像素包括开关晶体管SW、感测晶体管ST、驱动晶体管DT、电容器CST和有机发光二极管OLED。

开关晶体管SW的栅极电极连接到第1A扫描线GL1a,开关晶体管SW的第一电极连接到第一数据线DL1,并且开关晶体管SW的第二电极连接至驱动晶体管DT的栅极电极。驱动晶体管DT的栅极电极连接到电容器CST,驱动晶体管DT的第一电极连接到第一面板电源线EVDD,并且驱动晶体管DT的第二电极连接到有机发光二极管OLED的阳极电极。

电容器CST的第一电极连接到驱动晶体管DT的栅极电极,并且电容器CST的第二电极连接至有机发光二极管OLED的阳极电极。有机发光二极管OLED的阳极电极连接到驱动晶体管DT的第二电极,并且有机发光二极管OLED的阴极电极连接到第二面板电源线EVSS。感测晶体管ST的栅极电极连接到第1B扫描线GL1b,感测晶体管ST的第一电极连接到感测线VREF,并且感测晶体管ST的第二电极连接至作为感测节点的有机发光二极管OLED的阳极电极。

感测晶体管ST是为了补偿驱动晶体管DT和有机发光二极管OLED的劣化或阈值电压而添加的补偿电路。感测晶体管ST通过限定在驱动晶体管DT和有机发光二极管OLED之间的感测节点来获得感测值。从感测晶体管ST获得的感测值通过感测线VREF传送到设置在子像素外部的外部补偿电路。

连接到开关晶体管SW的栅极电极的第1A扫描线GL1a和连接到感测晶体管ST的栅极电极的第1B扫描线GL1b可以彼此分离或者公共连接。栅极电极公共连接结构可以减少所使用的扫描线的数量,结果,可以避免由于增加补偿电路而导致的开口率的降低。

如图4和图5中所示,包括根据本公开的实施方式的补偿电路的第一子像素SP1至第四子像素SP4可被定义为构成一个像素。此时,第一子像素SP1至第四子像素SP4可以以发射红色、绿色、蓝色和白色的顺序设置,但是不限于此。

如在图4的第一示例中所示,包括补偿电路的第一子像素SP1至第四子像素SP4可以连接以共用一条感测线VREF,并且分别连接到第一数据线DL1至第四数据线DL4。

如图5的第二示例中所示,包括补偿电路的第一子像素SP1至第四子像素SP4可以连接以共用一条感测线VREF,并且公共地成对地连接到一条数据线。例如,第一子像素SP1和第二子像素SP2可以共用第一数据线DL1,第三子像素SP3和第四子像素SP4可以共用第二数据线DL2。

然而,图4和图5示出了两个示例,但是本公开可应用于具有上文未描述的另一结构的子像素的显示面板。此外,本公开可应用于在子像素中具有补偿电路的结构或在子像素没有补偿电路的结构。

图6是示出根据本公开的实施方式的面板内选通类型的扫描驱动器的布置示例的视图,图7是示出与面板内选通类型的扫描驱动器相关的装置的第一示意性示例性视图,图8是示出面板内选通类型的扫描驱动器相关的装置的第二示意性示例性视图。

如图6中所示,面板内选通类型的扫描驱动器130a和130b被设置在显示面板150的非显示区域NA中。扫描驱动器130a和130b可以设置在显示面板150的左侧和右侧的非显示区域NA中,如图6中的(a)所示。此外,扫描驱动器130a和130b可以设置在显示面板150的上侧和下侧的非显示区域NA中,如图6中(b)所示。

尽管在以上作为示例的描述中,扫描驱动器130a和130b成对地设置在被布置在显示区域AA的左侧和右侧或上侧和下侧的非显示区域NA中,但是扫描驱动器130a和130b中的一个可以设置在左侧、右侧、上侧或下侧,并且本公开不限于此。

如图7中所示,面板内选通类型的扫描驱动器130可以包括移位寄存器电路131和电平移位器135。电平移位器135基于从定时控制器120输出的信号生成并输出多个时钟信号Gclk和开始信号Gvst。可以以诸如2相、4相和8相的K相(K是2或更大的整数)的形式生成并输出多个时钟信号。

移位寄存器电路131基于从电平移位器135输出的信号Gclk和Gvst进行操作,并且输出能够导通或关断形成在显示面板中的晶体管的扫描信号Scan[1]至Scan[m]。移位寄存器电路131以薄膜的形式通过面板内选通的方式形成在显示面板上。因此,移位寄存器电路131(即,图6中的130a和130b对应于131)可以是扫描驱动器130中的、形成显示面板上的部分。

与移位寄存器电路131不同,电平移位器135以IC的形式形成。如图7所示,可以以单独的IC的形式设置电平移位器135,并且如图8所示,电平移位器135可以被包括在电源180或另一装置中。

图9是示出根据本公开的实施方式的移位寄存器电路的视图,图10是示出根据本公开的实施方式的移位寄存器电路的特性的视图,图11是示出根据本公开的实施方式的移位寄存器电路的信号输出电路的详细电路图。

如图9中所示,移位寄存器电路131包括多个级STG1至STGm。多个级STG1至STGm具有所述级彼此依赖的连接结构,并且接收至少一个前端或后端的输出信号作为输入信号。移位寄存器电路131的级STG1至STGm分别包括移位寄存器SR[1]至SR[m]和信号输出电路OUTC[1]至OUTC[m]。

例如,第一级STG1包括第一移位寄存器SR[1]和第一信号输出电路OUTC[1],第二级STG2包括第二移位寄存器SR[2]和第二信号输入电路OUTC[2],第M级STGm包括第M移位寄存器SR[m]和第M信号输出电路OUTC[m]。

移位寄存器SR[1]至SR[m]分别具有公共输出端子SRO、第一QB节点QB_O和第二QB节点QB_E。信号输出电路OUTC[1]至OUTC[m]中的每一个都具有多个输出端子。信号输出电路OUTC[1]至OUTC[m]分别连接到移位寄存器SR[1]至SR[m]的公共输出端子SRO、第一QB节点QB_O和第二QB节点QB_E。

移位寄存器SR[1]至SR[m]的第一QB节点QB_O和第二QB节点QB_E的电位由基于通过时钟信号线CLKS施加的电压和时钟信号操作的多个晶体管控制。信号输出电路OUTC[1]至OUTC[m]基于移位寄存器SR[1]至SR[m]的第一QB节点QB_O和第二QB节点QB_E的电位来操作,并且通过J个输出端子分别输出J个扫描信号(J是2或更大的整数)。此时,移位寄存器SR[1]至SR[m]中的第一移位寄存器SR[1]基于通过开始信号线GVST施加的开始信号开始进行操作,并且另外的第二移位寄存器SR[2]至第M移位寄存器SR[m]基于前端的输出信号开始操作。

第一信号输出电路OUTC[1]基于从第一移位寄存器SR[1]的公共输出端子SRO输出的公共输出信号(公共输出电压)以及第一QB节点QB_O和第二QB节点QB_E的电位进行操作,并且通过第一输出端子VG[1]至第四输出端子VG[4]输出第一扫描信号至第四扫描信号。第二信号输出电路OUTC[2]基于从第二移位寄存器SR[2]的公共输出端子SRO输出的公共输出信号以及第一QB节点QB_O和第二QB节点QB_E的电位进行操作,并且通过第五输出端子VG[5]至第八输出端子VG[8]输出第五扫描信号至第八扫描信号。第M信号输出电路OUTC[m]基于从第M移位寄存器SR[m]的公共输出端子SRO输出的公共输出信号以及第一QB节点QB_O和第二QB节点QB_E的电位进行操作,并且通过第(4M-3)输出端子VG[4m-3]至第4M输出端子VG[4m]来输出第(4M-3)扫描信号至第4M扫描信号。

如图10所示,包括在第一级STG1中的第一信号输出电路OUTC[1]通过第一输出端子VG[1]至第四输出端子VG[4]输出第一描信号Vg[1]至第四扫描信号Vg[4]。包括在第M级STGm中的第M信号输出电路OUTC[m]通过第(4M-3)输出端子VG[4m-3]至第4M输出端子VG[4m]来输出第(4M-3)扫描信号VG[4m-3]至第4M扫描信号VG[4m]。

将从包括在第一级STG1中的第一信号输出电路OUTC[1]输出的第一扫描信号Vg[1]提供给布置在第一水平行中的第一子像素PXL[1],将第二扫描信号Vg[2]提供给布置在第二水平行中的第二子像素PXL[2],将第三扫描信号Vg[3]提供到布置在第三水平行中的第三子像素PXL[3],并且将第四扫描信号Vg[4]提供给布置在第四水平行中的第四子像素PXL[4]。

从以上示例将会意识到,根据实施方式的移位寄存器电路131从一个级输出可以驱动布置在多个水平行中的子像素的多个扫描信号。另一方面,通用的移位寄存器电路从一个级仅输出可以驱动布置在一个水平行中的子像素的一个扫描信号。

因此,根据实施方式的移位寄存器电路131也可以从一个级而不是从四个级输出总共四个扫描信号。由于根据实施方式的移位寄存器电路131还可以基于共用移位寄存器的节点的电路来输出多个扫描信号,所以可以显著地减少所使用的晶体管的数量。由于与现有情况相比,根据实施方式的移位寄存器电路131可以显著地减少所使用的晶体管的数量,所以即使添加补偿电路以增加电路的驱动稳定性、可靠性和寿命,也可以实现窄边框。即使根据实施方式的移位寄存器电路131被实现为输出多个扫描信号,也可以避免节点的电压降(可以避免共用节点的负载增加),从而可以提高电路的驱动稳定性并且可以产生均匀的输出。

为此,包括在每一级中的信号输出电路包括总共四个扫描信号输出电路。每个扫描信号输出电路基于从包括在一个级中的一个移位寄存器的公共输出端子SRO输出的公共输出信号以及第一QB节点QB_O和第二QB节点QB_E的电位来操作。每个扫描信号输出电路包括总共第一至第四晶体管。总共四个晶体管可被定义为缓冲晶体管。

如图11所示,包括在第I级中的信号输出电路OUTC[i]包括顺序地输出第一扫描信号至第四扫描信号的第一扫描信号输出电路至第四扫描信号输出电路。

第一扫描信号输出电路包括第A1晶体管TA1、第B1晶体管TB1、第C1晶体管TC1和第D1晶体管TD1。第A1晶体管TA1的栅极电极连接到第一电压线VDD,第A1晶体管TA1的第一电极连接到包括在第I级中的第I移位寄存器SR[i]的公共输出端子SRO,第A1晶体管TA1的第二电极连接到第一节点Q’i。第B1晶体管TB1的栅极电极连接到第一节点Q’i,第B1晶体管TB1的第一电极连接到第I时钟信号线Clki,并且第B1晶体管TB1的第二电极连接到第一扫描信号输出电路的输出端子VG[i]。第C1晶体管TC1的栅极电极连接至第I级中包括的第I移位寄存器SR[i]的第一QB节点QB_O,第C1晶体管TC1的第一电极连接至第一扫描信号输出电路的输出端子VG[i],并且第C1晶体管TC1的第二电极连接到第二电压线VSS。第D1晶体管TD1的栅极电极连接至第I级中包括的第I移位寄存器SR[i]的第二QB节点QB_E,第D1晶体管TD1的第一电极连接至第一扫描信号输出电路的输出端子VG[i],并且第D1晶体管TD1的第二电极连接到第二电压线VSS。

第二扫描信号输出电路包括第A2晶体管TA2、第B2晶体管TB2、第C2晶体管TC2和第D2晶体管TD2。第A2晶体管TA2的栅极电极连接到第一电压线VDD,第A2晶体管TA1的第一电极连接到包括在第I级中的第I位移位寄存器SR[i]的公共输出端子SRO,并且第A2晶体管TA2的第二电极连到第二节点Q’i+1。第B2晶体管TB2的栅极电极连接到第二节点Q’i+1,第B2晶体管TB2的第一电极连接到第(I+1)时钟信号线Clki+1,并且第B2晶体管TB2的第二电极连接到第二扫描信号输出电路的输出端子VG[i+1]。第C2晶体管TC2的栅极电极连接至第I级中包括的第I移位寄存器SR[i]的第一QB节点QB_O,第C2晶体管TC2的第一电极连接至第二扫描信号输出电路的输出端子VG[i+1],并且第C2晶体管TC2的第二电极连接到第二电压线VSS。第D2晶体管TD2的栅极电极连接至第I级中包括的第I移位寄存器SR[i]的第二QB节点QB_E,第D2晶体管TD2晶体管的第一电极连接至第二扫描信号输出电路的输出端子VG[i+1],并且第2晶体管TD2的第二电极连接到第二电压线VSS。

第三扫描信号输出电路包括第A3晶体管TA3、第B3晶体管TB3、第C3晶体管TC3和第D3晶体管TD3。第A3晶体管TA3的栅极电极连接到第一电压线VDD,第A3晶体管TA3的第一电极连接到包括在第I级中的第I位移位寄存器SR[i]的公共输出端子SRO,并且第A3晶体管TA3的第二电极连接至第三节点Q’i+2。第B3晶体管TB3的栅极电极连接到第三节点Q’i+2,第B3晶体管TB3的第一电极连接到第(I+2)时钟信号线Clki+2,并且第B3晶体管TB3的第二电极连接到第三扫描信号输出电路的输出端子VG[i+2]。第C3晶体管TC3的栅极电极连接到第I级中包括的第I移位寄存器SR[i]的第一QB节点QB_O,第C3晶体管TC3的第一电极连接到第三扫描信号输出电路的输出端子VG[i+2],并且第C3晶体管TC3的第二电极连到第二电压线VSS。第D3晶体管TD3的栅极电极连接至第I级中包括的第I移位寄存器SR[i]的第二QB节点QB_E,第D3晶体管TD3的第一电极连接至第三扫描信号输出电路的输出端子VG[i+2],并且第D3晶体管TD3的第二电极连接到第二电压线VSS。

第四扫描信号输出电路包括第A4晶体管TA4、第B4晶体管TB4、第C4晶体管TC4和第D4晶体管TD4。第A4晶体管TA4的栅极电极连接到第一电压线VDD,第A4晶体管TA4的第一电极连接到包括在第I级中的第I位移位寄存器SR[i]的公共输出端子SRO,并且第A4晶体管TA4的第二电极连接至第四节点Q’i+3。第B4晶体管TB4的栅极电极连接到第四节点Q’i+3,第B4晶体管TB4的第一电极连接到第(I+3)时钟信号线Clki+3,并且第B4晶体管TB4的第二电极连接到第四扫描信号输出电路的输出端子VG[i+3]。第C4晶体管TC4的栅极电极连接到第I级中包括的第I移位寄存器SR[i]的第一QB节点QB_O,第C4晶体管TC4的第一电极连接到第四扫描信号输出电路的输出端子VG[i+3],并且第C4晶体管TC4的第二电极连到第二电压线VSS。第D4晶体管TD4的栅极电极连接到第I级中包括的第I移位寄存器SR[i]的第二QB节点QB_E,第D4晶体管TD4的第一电极连接到第四扫描信号输出电路的输出端子VG[i+3],并且第D4晶体管TD4的第二电极连到第二电压线VSS。

图12是示出根据本公开的实施方式的信号输出电路的操作的视图,图13是示出根据本公开的实施方式的驱动信号输出电路所需的时钟信号的波形,图14是示出根据本公开的实施方式的信号输出电路的节点电压和输出电压的视图,图15和图16是示出根据本公开的实施方式的信号输出电路的优点的视图。

如图12至图14中所示,根据本公开的实施方式的第I级的信号输出电路OUTC[i]包括总共四个信号输出电路。需要总共四个4相时钟信号Clk1至Clk4和1相进位时钟信号CarClk1以驱动信号输出电路。示出了8相时钟信号Clk1至Clk8和4相进位时钟信号Car Clk1至Car Clk4。这是因为已经示出了信号类型,其需要四个时钟信号和一个进位时钟信号用于一个级以驱动总共四个级。此时,针对重叠逻辑高的1/2时段将8相时钟信号Clk1至Clk8和4相进位时钟信号Car Clk1至Car Clk4生成为重叠,使得从四个信号输出电路中的每一个输出期望数量的扫描信号。所述逻辑高的重叠时段是至少一个水平时段或更多。

因此,第一时钟信号Clk1和第二时钟信号C1k2具有重叠1/2时段的逻辑高,第二时钟信号CLk2和第三时钟信号Clk3具有重叠1/2时段的逻辑高,第三时钟信号Clk3和第四时钟信号Clk4具有重叠1/2时段的逻辑高,第四时钟信号Clk4和第五时钟信号Clk5具有重叠1/2时段的逻辑高,第五时钟信号Clk5和第六时钟信号Clk6具有重叠1/2时段的逻辑高,第六时钟信号Clk6和第七时钟信号Clk7具有重叠1/2时段的逻辑高,并且第七时钟信号Clk7和第八时钟信号Clk8具有重叠1/2时段的逻辑高。第一进位时钟信号Car Clk1和第二进位时钟信号Car Clk2具有重叠1/2时段的逻辑高,第二进位时钟脉冲信号Car Clk2和第三进位时钟脉冲信号Cal Clk3具有重叠1/2时段的逻辑高,并且第三进位时钟信号Car Clk3和第四进位时钟信号Car Clk4具有重叠1/2时段的逻辑高。

同时,当从特定移位寄存器输出扫描信号时,4相进位时钟信号Car Clk1至CarClk4应当继续保持逻辑高。因此,当移位寄存器以1:4(移位寄存器的数量:扫描线的数量)的形式共用时,移位寄存器应当包括用于输出相应扫描信号的时钟信号定时(扫描clk定时)。即,进位时钟信号的宽度(进位clk时间宽度)可被设置为扫描信号的输出缓冲器的电荷裕度(扫描缓冲器电荷裕度)+用于输出扫描信号的时钟信号定时(扫描clk定时)+复位裕度。在图14中,第I位移位寄存器SR[i]的Q节点的逻辑高维持时段和进位时钟信号Car Clk1的逻辑低维持时段可以彼此相等,以保持用于输出多个扫描信号的时钟信号的定时。

以下,将参照图11至图14来描述从第I级的信号输出电路OUTC[i]中所包括的第一至第四扫描信号输出电路输出总共4个扫描信号的情况。然而,在下面的描述中,将基于在以逻辑高的电压对第I移位寄存器SR[i]的Q节点充电之后,通过Q节点的公共输出端子SRO输出公共输出信号,来描述第I级的信号输出电路OUTC[i]的操作。作为参考,如果以逻辑高的电压对Q节点充电,则第I移位寄存器SR[i]可以通过公共输出端子SRO输出逻辑高的公共输出信号,并且如果以逻辑高的电压对QB节点充电,则第I移位寄存器SR[i]可以通过公共输出端子SRO来输出逻辑低的公共输入信号。

如图11至图14中所示,如果第A1晶体管TA1和第B1晶体管TB1导通,则包括在第I级的信号输出电路OUTC[i]中的第一扫描信号输出电路会通过其输出端子VG[i]输出扫描高电压的第一扫描信号Vg[i]。如果第A1晶体管TA1导通,则以高电压对第一节点Q’i充电。此时,由于自举,第一节点Q’i的高电压具有高电压电平。

当第一节点Q’i的电位变为高电压时,第B1晶体管TB1导通。当第B1晶体管TB1导通时,基于第一时钟信号Clki提供的扫描高电压的第一扫描信号Vg[i]被输出到第一扫描信号输出电路的输出端子VG[i]。另一方面,如果第C1晶体管TC1或第D1晶体管TD1导通,则输出基于第二电压提供的扫描低电压的第一扫描信号Vg[i]。

如果第A2晶体管TA2和第B2晶体管TB2导通,则包括在第I级的信号输出电路OUTC[i]中的第二扫描信号输出电路通过其输出端子VG[i+1]输出扫描高电压的第二扫描信号Vg[i+1]。如果第A2晶体管TA2导通,则以高电压对第二节点Q’i+1充电。此时,由于自举,第二节点Q’i+1的高电压具有高电压电平。当第二节点Q’i+1的电位变为高电压时,第B2晶体管TB2导通。当第B2晶体管TB2导通时,基于第二时钟信号Clki+1提供的扫描高电压的第二扫描信号Vg[i+1]被输出到第二扫描信号输出电路的输出端子VG[i+1]。另一方面,如果第C2晶体管TC2或第D2晶体管TD2导通,则输出基于第二电压提供的扫描低电压的第二扫描信号Vg[i+1]。

如果第A3晶体管TA3和第B3晶体管TB3导通,则包括在第I级的信号输出电路OUTC[i]中的第三扫描信号输出电路通过其输出端子VG[i+2]输出扫描高电压的第三扫描信号Vg[i+2]。如果第A3晶体管TA3导通,则以高电压对第三节点Q’i+2充电。此时,由于自举,第三节点Q’i+2的高电压具有高电压电平。当第三节点Q’i+2的电位变为高电压时,第B3晶体管TB3导通。当第B3晶体管TB3导通时,基于第三时钟信号Clki+2提供的扫描高电压的第三扫描信号Vg[i+2]被输出到第三扫描信号输出电路的输出端子VG[i+2]。另一方面,如果第C3晶体管TC3或第D3晶体管TD3导通,则输出基于第二电压提供的扫描低电压的第三扫描信号Vg[i+2]。

如果第A4晶体管TA4和第B3晶体管TB3导通,则包括在第I级的信号输出电路OUTC[i]中的第四扫描信号输出电路通过其输出端子VG[i+3]输出扫描高电压的第四扫描信号Vg[i+3]。如果第A4晶体管TA4导通,则以高电压对第四节点Q’i+3充电。此时,由于自举,第四节点Q’i+3的高电压具有高电压电平。当第四节点Q’i+3的电位变为高电压时,第B4晶体管TB4导通。当第B4晶体管TB4导通时,基于第四时钟信号Clki+3提供的扫描高电压的第四扫描信号Vg[i+3]被输出到第四扫描信号输出电路的输出端子VG[i+3]。另一方面,如果第C4晶体管TC4或第D4晶体管TD4导通,则输出基于第二电压提供的扫描低电压的第四扫描信号Vg[i+3]。

在上述描述中,用于第一节点Q’i至第四节点Q’i+3的自举意味着根据施加到第B1晶体管TB1至第B4晶体管TB4的电极的电压,由于存在于第B1晶体管TB1至第B4晶体管的每一个的栅极电极与源极电极之间的寄生电容的耦合而引起的电压上升。

同时,在上述描述中,第一输出晶体管T1和第二输出晶体管T2被示出为包括在第I级中的第I移位寄存器SR[i]向其输出第一驱动电压VDD和公共输出信号的元件中的一些元件。在这种情况下,第一输出晶体管T1和第二输出晶体管T2可以被定义为用于生成来自包括在第I级中的第I移位寄存器SR[i]的输出信号的缓冲器。

同时,基于如下内容示例性地示出了第一输出晶体管T1:其栅极电极连接到进位信号输出端子Car,其第一电极连接到第一电压线VDD,并且其第二电极连接到第二输出晶体管T2的栅极电极。此外,基于如下内容示例性地示出了第二输出晶体管T2:其栅极电极连接到第一输出晶体管T1的第二电极,其第一电极连接到进位时钟信号线Car Clk,并且其第二电极公共地连接到扫描信号输出电路的第A1晶体管TA1至第A4晶体管TA4的第一电极。然而,第一输出晶体管T1和第二输出晶体管T2的结构和连接关系仅是示例性的,并且本公开可以以各种方式修改而不限于以上示例。

从图11至图14将意识到,在包括在第I级的信号输出电路OUTC[i]中的第一至第四扫描信号输出电路的第一节点Q’i到第四节点Q’i+3中充电的高电压由于时钟信号而顺序地产生,同时在某一时段内彼此交叠。结果,从包括在第I级的信号输出电路OUTC[i]中的第一至第四扫描信号输出电路的输出端子VG[i]至VG[i+3]输出的扫描高电压也顺序地生成,同时彼此交叠达某一时段(例如,1/2时段)。

如图15和图16所示,根据本公开的实施方式的第I级的信号输出电路OUTC[i]即使被实现为输出多个扫描信号也可以防止节点的电压降发生(防止共用节点的负载增加),由此,可以提高电路的驱动稳定性,并且可以产生均匀的输出(由于提高了共用节点的电压,因此可以提高输出缓冲器的能力)。

这从图15中的实验示例和实施方式中的移位寄存器的Q节点电压与图16中的实验示例和实施方式中的信号输出电路的Q’节点电压之间的比较中注意到。

实验示例是包括在扫描信号输出电路中的第一晶体管(图11中的TA1至TA4)共用移位寄存器的Q节点电压的结构,并且该实施方式是包括在扫描信号输出电路中的第一晶体管(图11中的TA1至TA4)共用移位寄存器的公共输出信号的结构。

将从图15中的比较中意识到,如果扫描信号输出电路被实现为与实验示例一样共用移位寄存器的Q节点电压,则可能由于Q节点的线负载增量而出现节点电压降。然而,如果扫描信号输出电路被实现为与实施方式一样共用移位寄存器的公共输出信号,则由于不共用Q节点,因此不会引起Q节点的线负载增量,由此不会出现节点下降电压。

此外,将从图16中的比较中意识到,如果扫描信号输出电路被实现为与实验示例一样共用移位寄存器的Q节点电压,则可能发生每个扫描信号输入电路的Q’节点中充电的电压的偏差。这是因为基于Q节点的线负载增量的电压降可能是如图15中的实验示例中所描述的那样引起的,并且Q’节点可能受到电压的影响,使得难以进行均匀充电。

然而,如果与实施方式一样,将扫描信号输出电路实现为共用移位寄存器的输出信号,则由于不发生每个扫描信号输入电路的Q’节点中充电的电压的偏差,因此可以产生并保持均匀的输出。这是因为如图15中的实施方式中所述,不共用可能引起电压降的Q节点,并且可以通过使用移位寄存器的输出信号来排除Q节点的线节点增量。

如上所述,根据本公开的实施方式,即使电路被实现为基于共用所述移位寄存器的节点的电路来输出多个扫描信号,也可以防止出现所述节点的电压降(可以防止共用节点的负载增加),从而可以提高所述电路的驱动稳定性,并且可以产生均匀的输出。此外,由于当实现用于输出所述扫描信号的所述电路时可以显著地减少所使用的晶体管的数量,因此即使添加补偿电路以增加电路的驱动稳定性、可靠性和寿命,也可以实现窄边框。

对于本领域技术人员来说显而易见的是,上面描述的本公开不受上述实施方式和附图的限制,并且可以在不脱离本公开的精神或范围的情况下对本公开进行各种替换、修改和变型。因此,本公开的范围由所附权利要求限定,并且旨在从权利要求的含义、范围和等同概念得到的所有变型或修改都落在本发明的范围内。

根据以上详细描述,可以对实施方式进行这些和其它改变。通常,在所附权利要求中,所使用的术语不应被解释为将权利要求限制为在说明书和权利要求书中公开的特定实施方式,而应解释为包括所有可能的实施方式以及这些权利要求所赋予的等同范围的全部范围。因此,权利要求不受本公开的限制。

- 移位寄存器电路和包括该移位寄存器电路的发光显示装置

- 单位移位寄存器电路、移位寄存器电路、单位移位寄存器电路的控制方法以及显示装置