具有裸片以执行刷新操作的设备

文献发布时间:2023-06-19 09:24:30

本案是分案申请。该分案的母案是申请日为2016年05月17日、申请号为201680012281.X、发明名称为“具有裸片以执行刷新操作的设备”的发明专利申请案。

本申请案主张2015年5月18日申请的序列号为14/714,962的美国申请案的优先权的权益,所述美国申请案的全部内容以引用的方式并入本文中。

技术领域

本申请涉及半导体设备,特别是具有裸片以执行刷新操作的设备。

背景技术

例如DRAM(动态随机存取存储器)的一些半导体装置执行刷新操作以恢复存储器单元中的电荷以维持逻辑数据的经储存状态。一般来说,在周期性基础上或在命令基础上针对DRAM的单个裸片执行刷新操作。当涉及多个裸片时,操作更复杂,使得电流消耗及稳定性变得更难以控制。

发明内容

根据本发明的第一方面,一种设备包含:接口芯片,其包含产生原始时钟信号的振荡器;第一存储器芯片,其包含经配置以响应于原始时钟信号而接收第一时钟信号的第一端子、被供应第一控制信号的第二端子、及当第一控制信号在作用中时响应于第一时钟信号而经受数据刷新操作的第一存储器单元;及第二存储器芯片,其包含经配置以响应于原始时钟信号而接收第二时钟信号的第三端子、被供应第二控制信号的第四端子、及当第二控制信号在作用中时响应于第二时钟信号而经受数据刷新操作的第二存储器单元。

根据本发明的第二方面,一种设备包含:芯片堆叠结构,其包含彼此上下堆叠的第一存储器芯片及第二存储器芯片;及接口芯片,其耦合到芯片堆叠结构。第一存储器芯片包含第一端子及第二端子及多个第一存储器单元。第二存储器芯片包含第三端子、第四端子及第五端子。第一存储器芯片及第二存储器芯片彼此上下堆叠,使得第一存储器芯片的第二端子电连接到第二存储器芯片的第五端子。接口芯片包含第六端子、第七端子及第八端子且耦合到芯片堆叠结构,使得接口芯片的第六端子、第七端子及第八端子电连接到第二存储器芯片的第三端子、第四端子及第五端子,第二端子耦合到第一存储器芯片的第一命令解码器电路,且第四端子耦合到第二存储器芯片的第二命令解码器电路。第一命令解码器电路及第二命令解码器电路彼此独立工作。

根据本发明的第三方面,一种设备包含:接口芯片,其包含振荡器电路以提供振荡器信号;第一存储器芯片,在其上响应于在第一节点处供应的第一刷新启用信号及在第二节点处供应的第一振荡器启用信号而执行第一刷新操作;第二存储器芯片,在其上响应于在第三节点处供应的第二刷新启用信号及在第四节点处供应的第二振荡器启用信号而执行第二刷新操作。第一节点及第三节点经配置以从接口芯片彼此独立接收第一刷新启用信号及第二刷新启用信号。第二节点及第四节点经配置以基于振荡器信号在彼此不同的时序中接收第一振荡器启用信号及第二振荡器启用信号,使得即使当第一节点及第三节点同时接收第一刷新启用信号及第二刷新启用信号时,仍在彼此不同的时序中执行第一刷新操作及第二刷新操作。

附图说明

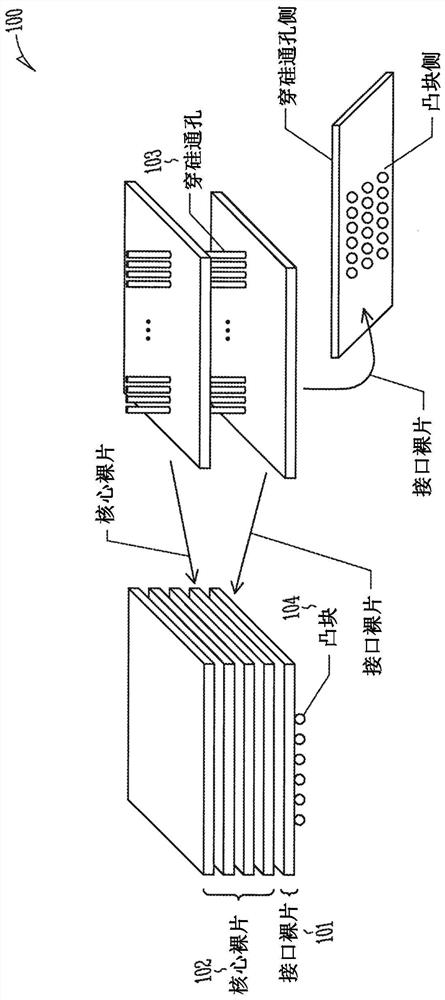

图1说明根据第一实施例的高带宽存储器的实例。

图2说明根据第一实施例的具有高带宽存储器及图形处理单元的实例结构。

图3说明根据第一实施例的接口裸片的电路的实例。

图4说明根据第二实施例的高带宽存储器的实例。

图5说明根据第二实施例的自刷新时序的实例。

图6说明根据第二实施例的自刷新时序的另一实例。

图7说明根据第一实施例的高带宽存储器的实例。

图8说明根据第三实施例的高带宽存储器的第三实例。

图9说明根据第一实施例的自刷新时序的实例。

图10说明根据第一实施例的核心裸片的实例。

图11说明根据第一实施例的核心裸片中的自刷新波形的实例。

图12说明根据第四实施例的高带宽存储器的第四实例。

图13说明根据第五实施例的高带宽存储器的第五实例。

具体实施方式

以下描述包含说明性设备,所述设备包含体现所揭示的标的物的半导体装置(电路、系统及类似者)及过程(例如,时序、波形及类似者)。在以下描述中,出于解释的目的,阐述许多具体细节以提供标的物的各种实施例的理解。

图1说明根据第一实施例的高带宽存储器(HBM)的实例。HBM 100可包含接口裸片101、接口裸片101上方的核心裸片的堆叠102、用于将核心裸片102彼此连接的穿硅通孔(TSV)103、及凸块垫104,且HBM 100可包含例如在下文中通过参考图7、8、12及13解释的高带宽存储器。

在一些实施例中,凸块垫104可包含微凸块104且可接收来自主机控制器(未展示)的信号。接口裸片101可缓冲从凸块104到TSV 103的信号。在一些实施例中,核心裸片102可包含存储器单元,而接口裸片101可不包含任何存储器单元。在一些实施例中,核心裸片102可包含一或多个命令解码器(例如命令解码器116,如图7中展示)。

在一些实施例中,接口裸片101可分成一些独立通道。这些通道可彼此独立。HBM100可具有宽数据接口,所述宽数据接口可以高速度及低电力消耗执行操作。可在HBM 100中执行自刷新操作。

图2说明根据第一实施例的包含HBM 100及图形处理单元(GPU)105的实例结构200。在一些实施例中,再驱动器106可安置于HBM 100与GPU 105之间以驱动信号。结构200可称为半导体装置、设备或系统,其是由控制器(未展示)或处理器(未展示)经由连接部分而存取。连接部分可为凸块、球或焊球。图3说明根据第一实施例的接口裸片101的电路的实例。在一些实施例中,接口裸片101的电路可包含存储器内建自测试(BIST)电路107以测试核心裸片102、内部电路108(如例如图4中展示)及输入缓冲器109以接收来自对应微凸块104的信号且将信号传达到对应TSV 103。

图4说明根据第二实施例的HBM 400的第一实例。如图4中展示,HBM 400可包含通过TSV 403而彼此连接的接口裸片401及核心裸片的堆叠402(例如核心裸片402A及核心裸片402B)。

在一些实施例中,接口裸片401可包含凸块(例如凸块A及凸块B),及内部电路408(其可具有接收器(Rx)410、发射器(Tx)411、收发器(Tx Rx)412、逻辑413及缓冲器414)。

在一些实施例中,核心裸片402A可包含定位于DRAM存储器阵列415中的存储器单元、命令解码器416、自刷新振荡器417及数据控制器418。类似地,核心裸片402B可包含定位于DRAM存储器阵列415中的存储器单元、命令解码器416、自刷新振荡器417及数据控制器418。核心裸片402A及核心裸片402B可分别按命令操作且因此可彼此独立工作。

图5说明根据第二实施例的在如图4中展示的核心A及核心B两者在自刷新状态中时的自刷新时序的实例。图6说明根据第二实施例的在如图4中展示的核心A在自刷新状态中且如图4中展示的核心B不在自刷新状态中时的自刷新时序的另一实例。在图5及图6中,self_osc表示自刷新振荡器信号,ACT表示主动命令(其可由GPU提供),WR表示WRITE信号且RD表示READ信号。

DRAM裸片402A具有自刷新功能且DRAM裸片402B也具有刷新功能。刷新功能可称为DRAM的自刷新模式。在自刷新模式中,DRAM可自动刷新存储器单元数据,且可激活DRAM中的全部存储器库以刷新存储器库的存储器单元数据。

在第二实施例中,两个裸片402A及402B的刷新操作彼此独立执行,且因此所述两个刷新操作有时可同时出现,其在图5中可指示为相同时序。因此,两个裸片402A及402B的刷新操作的相同时序中的消耗电流可变得高于刷新操作的不同时序中的消耗电流。可以说,第二实施例HBM中的峰值电流有时可能在相同时序刷新操作中变得高。HBM的DRAM裸片可同时消耗大量电力且因此可引发电力噪声,这可能影响自刷新功能的完整性。

图7说明根据第一实施例的HBM 700的实例。上文中的解释可至少部分适用及/或相同于第一实施例,且因此为了简洁起见,省略一些共同解释。举例来说,此处可根据第一实施例提及上文中展示的配置。

如图7中展示,HBM 700可包含通过TSV 703而彼此连接的接口裸片701及核心裸片的堆叠702(包含至少两个裸片,例如核心裸片702A及核心裸片702B)。

在一些实施例中,接口裸片701可包含凸块(例如凸块A及凸块B),及内部电路708。接口裸片701的内部电路708可包含自刷新振荡器717、接收器710、发射器711、收发器712、逻辑713及缓冲器714。

此处,在一些实施例中,自刷新振荡器717可定位于接口裸片701中且可共同结合核心裸片702A及核心裸片702B两者工作。相比之下,在图4中,自刷新振荡器427未定位于接口裸片401中且定位于裸片401A及402B中的每一者中。因此,在第二实施例中,刷新操作可彼此独立工作。根据第一实施例,自刷新振荡器717共同于包含裸片702A及702B的裸片的堆叠那样配置。

在一些实施例中,例如当HBM 700不在复位状态中时可根据复位信号激活自刷新振荡器717。

在一些实施例中,核心裸片702A可包含定位于DRAM存储器阵列715中的存储器单元、命令解码器716、数据控制器718及延迟调整电路719A。类似地,核心裸片702B可包含定位于DRAM存储器阵列715中的存储器单元、命令解码器716、数据控制器718及延迟调整电路719B。核心裸片702A及核心裸片702B可分别按命令操作且因此可彼此独立工作。

此处,根据第一实施例,核心裸片702A的延迟调整电路719A及核心裸片702B的延迟调整电路719B彼此串联耦合。在此布置中,延迟调整电路719A的延迟量可经配置为与延迟调整电路719B的延迟量相同,且延迟调整电路719A及719B可经配置为彼此相同。

根据第一实施例,归因于延迟调整电路(例如延迟调整电路719A及延迟调整电路719B),通道的刷新时序可能不同,且因此可减小相关联的半导体装置的峰值电流消耗。

图8说明根据第三实施例的HBM 800的第三实例。如图8中展示,HBM 800可包含通过TSV 803而彼此连接的接口裸片801及核心裸片的堆叠(包含至少两个裸片,例如核心裸片802A及核心裸片802B)。上文中的解释可至少部分适用及/或相同于第三实施例,且因此为了简洁起见,省略一些共同解释。举例来说,此处可根据第三实施例提及上文中展示的配置。

在一些实施例中,接口裸片801可包含凸块(例如凸块A及凸块B),及内部电路808。接口裸片801的内部电路可包含自刷新振荡器817、接收器810、发射器811、收发器812、逻辑813及缓冲器814。

在一些实施例中,核心裸片802A可包含定位于DRAM存储器阵列815中的存储器单元、命令解码器816、数据控制器818及延迟调整电路819A。类似地,核心裸片802B可包含定位于DRAM存储器阵列815中的存储器单元、命令解码器816及数据控制器818及延迟调整电路819B。核心裸片802A及核心裸片802B可分别按命令操作且因此可彼此独立工作。

根据第二实施例,核心裸片802A的延迟调整电路819A及核心裸片802B的延迟调整电路819B彼此并联耦合。在此布置中,延迟调整电路819A的延迟量可与延迟调整电路819B的延迟量不同,且延迟调整电路819A及819B可经配置为彼此不同。

根据第二实施例,归因于延迟调整电路819(例如延迟调整电路819A及延迟调整电路819B),通道的刷新时序可不同,且因此可减小相关联的半导体装置的峰值电流消耗。

图9说明根据第一实施例的自刷新时序的实例。还可根据其它实施例提及图9中的时序。

如图9中展示,例如归因于延迟调整电路819A及819B,可在不同时序值处执行对核心裸片802A及核心裸片802B的两个自刷新操作。

根据实施例,两个自刷新振荡器信号SELF_OSC_A及SELF_OSC_B是从一个自刷新振荡器信号SELF_OSC_IF共同产生且所述两个自刷新振荡器信号SELF_OSC_A及SELF_OSC_B经触发且激活为在不同时序中是高的。因此,可防止堆叠中的裸片的同时自刷新操作且HBM的自刷新操作中的峰值电流可被缓解且变得低于第二实施例。

图10说明根据第一实施例的核心裸片102的实例。还可根据其它实施例提及图10中展示的配置。

如图10中展示,核心裸片102(例如,核心裸片802A,如图8中展示)可包含命令解码器116及延迟调整电路119。当任何通道在自刷新模式中时,自刷新振荡器信号可被驱动到核心裸片102。核心裸片102中的延迟调整电路119可改变核心裸片102的每一通道中的自刷新时序。

图11说明根据第一实施例的核心裸片102中的刷新波形的实例。还可根据其它实施例提及图11中的波形。

在图11中,“self_en”表示自刷新进入信号,其可由GPU提供。“self_exit”表示自刷新退出信号,其可由GPU提供。“self_st”表示自刷新状态信号,其可从“self_en”上升且从“self_en”下降。“self_osc”表示自刷新振荡器信号。“ref_go”表示刷新开始信号。“soak”表示从“ref_go”的上升边缘产生的信号。“soak”信号可来自存储器阵列区域,且可指示可以结束刷新操作。“ref_state”表示刷新命令(状态)信号,其可进入存储器阵列区域。刷新操作可从“ref_state”的上升边缘起始且可在“ref_state”的下降边缘处结束。

图12说明根据第四实施例的HBM 1200的实例。上文中的解释可至少部分适用及/或相同于第四实施例,且因此为了简洁起见,省略一些共同解释。举例来说,此处可根据第四实施例提及上文中展示的配置。

如图12中展示,HBM 1200可包含通过TSV 1203而彼此连接的接口裸片1201及核心裸片的堆叠(例如核心裸片1202A及核心裸片1202B)。

在一些实施例中,接口裸片1201可包含凸块(例如凸块A及凸块B),及内部电路1208。接口裸片1201的内部电路1208可包含自刷新振荡器1217、延迟调整电路1219A、延迟调整电路1219B、接收器1210、发射器1211、收发器1212、逻辑1213及缓冲器1214。延迟调整电路1219A可从(例如)自刷新振荡器1217接收“self_osc”信号。

此处,根据第四实施例,延迟调整电路1219A及延迟调整电路1219B定位于接口裸片1201中。相比之下,延迟调整电路1219A及延迟调整电路1219B未定位于接口裸片1201中且分别定位于核心裸片中。

根据第四实施例,延迟调整电路1219A可耦合到核心裸片1202A。延迟调整电路1219B可耦合于延迟调整电路1219A与核心裸片1202B之间,且因此延迟调整电路1219B可与延迟调整电路1219A串联耦合。在此布置中,可减小每一核心裸片(例如核心裸片1202A及核心裸片1202B)中的电路布局面积。

在一些实施例中,核心裸片1202A可包含定位于DRAM存储器阵列1215中的存储器单元、命令解码器1216及数据控制器1218。类似地,核心裸片1202B可包含定位于DRAM存储器阵列1215中的存储器单元、命令解码器1216及数据控制器1218。核心裸片1202A及核心裸片1202B可分别按命令操作且因此可彼此独立工作。

图13说明根据第五实施例的HBM 1300的第五实例。上文中的解释可至少部分适用及/或相同于第五实施例,且因此为了简洁起见,省略一些共同解释。举例来说,此处可根据第五实施例提及上文中展示的配置。

如图13中展示,HBM 1300可包含通过TSV 1303而彼此连接的接口裸片1301及核心裸片的堆叠(例如核心裸片1302A及核心裸片1302B)。

在一些实施例中,接口裸片1301可包含凸块(例如凸块A及凸块B),及内部电路1308。接口裸片1301的内部电路1308可包含自刷新振荡器1317、延迟调整电路1319A、延迟调整电路1319B、接收器1310、发射器1311、收发器1312、逻辑1313及缓冲器1314。

此处,根据第四实施例,延迟调整电路1319A及延迟调整电路1319B定位于接口裸片1301中。相比之下,延迟调整电路1319A及延迟调整电路1319B未定位于接口裸片1301中且分别定位于核心裸片中。

根据第四实施例,延迟调整电路1319A及延迟调整电路1319B彼此并联耦合且可从(例如)自刷新振荡器1317接收“self_osc”信号。延迟调整电路1319A耦合于自刷新振荡器1317与核心裸片1302A之间。延迟调整电路1319B耦合于自刷新振荡器1317与核心裸片1302B之间。

在一些实施例中,核心裸片1302A可包含定位于DRAM存储器阵列1315中的存储器单元、命令解码器1316及数据控制器1318。类似地,核心裸片1302B可包含定位于DRAM存储器阵列1315中的存储器单元、命令解码器1316及数据控制器1318。核心裸片1302A及1302B可分别按命令操作且因此可彼此独立工作。

在一些实施例中,接口裸片1301的延迟调整电路1319A可经由元件(例如串联的接口裸片1301的发射器111、TSV 1303、核心裸片1302A的接收器1310及核心裸片1302A的逻辑1313)耦合到核心裸片1302A的DRAM存储器阵列1315。类似地,接口裸片1301的延迟调整电路1319B可经由元件(例如串联的接口裸片1301的发射器1311、TSV 1303、核心裸片1302A的接收器1310及核心裸片1302A的逻辑1313)耦合到核心裸片1302B的DRAM存储器阵列1315。

在此布置中,设备在接口裸片中可仅具有一或多个自刷新振荡器且可减小设备的电力消耗。

提供本发明的摘要以符合37C.F.R.§1.72(b),其需要将允许读者快速确定技术揭示内容的性质的摘要。其在了解摘要将不用于解释或限制权利要求书的范围或意义的情况下提交。另外,在前述实施方式中,可见出于简化本发明的目的在单个实施例中将多种特征集合在一起。因此,借此将所附权利要求书并入实施方式中,其中每一权利要求独立地作为单独实施例。