用于调整受害者数据的设备和方法

文献发布时间:2023-06-19 09:26:02

技术领域

本公开总体上涉及半导体装置,并且更具体地涉及半导体存储器装置。具体地,本公开涉及如动态随机存取存储器(DRAM)等易失性存储器。

背景技术

信息可以以物理信号(例如,电容元件上的电荷)的形式存储在存储器的单独存储器单元上。存储器可以是易失性存储器,并且物理信号可能随时间的推移而衰减(这可能使存储在存储器单元中的信息退化或破坏)。可能需要通过例如重写信息以将物理信号恢复为初始值来周期性地刷新存储器单元中的信息。

随着存储器组件的大小减小,存储器单元的密度已经大大增加。通常,存储器单元布置成包含一系列被称为字线的行和被称为位线的列的阵列。在周期性地刷新一或多条字线的存储器单元以保持存储在存储器单元中的数据的情况下,可以执行自动刷新操作。对特定存储器单元或存储器单元组(如字线)的重复存取可能使附近的存储器单元(例如,相邻字线)中的数据退化的速率增加。这种重复存取通常被称为“行锤击”。为了保持附近的存储器单元中的数据,可能需要以比自动刷新操作的速率高的速率刷新附近的存储器单元的字线。

发明内容

一方面,本申请提供了一种设备,所述设备包括:堆栈,所述堆栈被配置成存储:对应于多条字线的多个行地址;以及与所述多个行地址中的每个行地址相关联的受害者数据,其中所述受害者数据对应于与所述多个行地址相关联的多条被存取字线中的每条被存取字线的至少一条受害者字线,其中所述受害者数据指示所述至少一条受害者字线是否已经修复;反向加扰器,所述反向加扰器被配置成提供与刷新地址或被存取行地址中的至少一个相关联的攻击者行地址;以及受害者数据逻辑电路,所述受害者数据逻辑电路被配置成调整与所述多个行地址中的与所述攻击者行地址相匹配的行地址相关联的所述受害者数据。

另一方面,本申请提供了一种设备,所述设备包括:反向加扰器,所述反向加扰器被配置成提供与刷新地址或被存取行地址中的至少一个相关联的攻击者行地址;受害者数据逻辑电路,所述受害者数据逻辑电路被配置成将受害者标志设置成经刷新状态,其中所述受害者标志与和所述攻击者行地址匹配的行地址相关联;以及地址加扰器,所述地址加扰器被配置成当所述受害者标志处于未修复状态时,基于所述行地址提供至少一个受害者地址,其中所述至少一个受害者地址用于在目标刷新操作期间刷新受害者字线。

又另一方面,本申请提供了一种方法,所述方法包括:将行地址存储在寄存器中;将受害者数据设置成第一值,其中所述受害者数据与所述寄存器中的所述行地址相关联;基于与刷新操作或存取操作相关联的第二行地址计算至少一个攻击者行地址;将所述行地址与所述至少一个攻击者行地址进行比较;以及如果所述行地址与所述至少一个攻击者行地址匹配,则将所述受害者数据设置成第二值。

附图说明

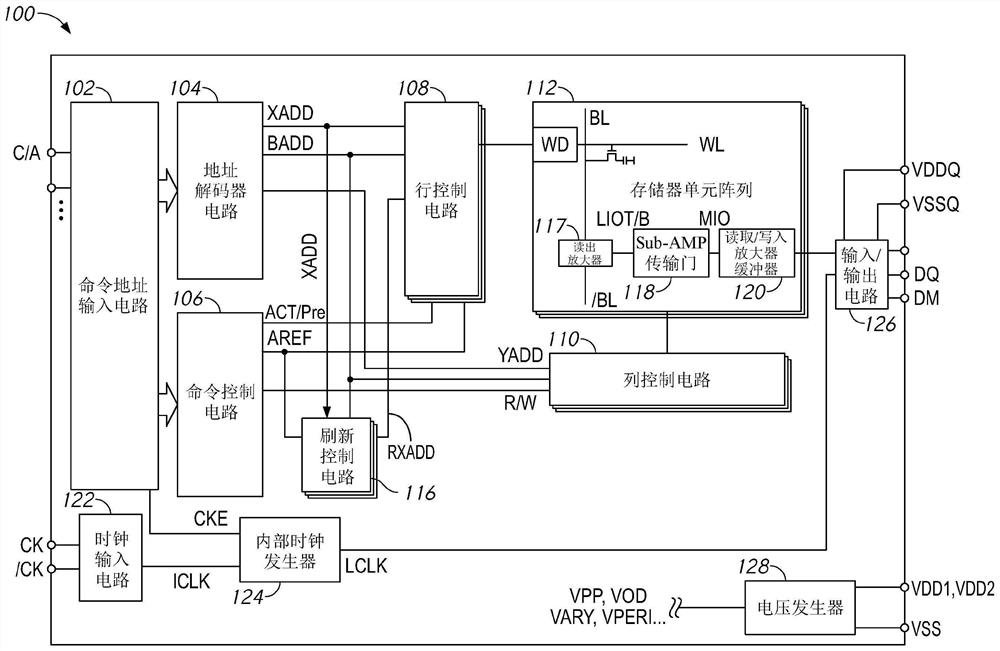

图1是根据本公开的实施例的半导体装置的框图。

图2是根据本公开的实施例的刷新控制电路的框图。

图3是根据本公开的实施例的攻击者行检测器电路的框图。

图4是根据本公开的实施例的内容可寻址存储器单元的示意图。

图5是根据本公开的实施例的反向加扰器和攻击者行检测器电路的一部分的框图。

图6是根据本公开的实施例的方法的流程图。

具体实施方式

以下对某些实施例的描述本质上仅是示范性的,并且并非旨在限制本公开的范围或其应用或用途。在以下对本发明系统和方法的实施例的详细描述中,对附图进行了参考,所述附图形成所述详细描述的一部分,并且在附图中通过图示示出了可以实践所描述的系统和方法的具体实施例。足够详细地对这些实施例进行了描述以使本领域的技术人员能够实践当前公开的系统和方法,并且应理解的是,在不背离本公开的精神和范围的情况下,可以利用其它实施例并且可以做出结构改变和逻辑改变。此外,为了清楚起见,当某些特征对本领域的技术人员来说是显而易见的时,将不会讨论对所述特征的详细描述,以便不模糊对本公开的实施例的描述。因此,以下详细描述不应视为具有限制性,并且本公开的范围仅由所附权利要求限定。

存储器装置可以包含存储器单元的阵列。存储器单元可以存储信息(例如,以一或多个位的形式),并且可以被组织在字线(行)和位线(列)的交叉点处。多条字线和位线可以组织成存储器组。存储器装置可以包含多个不同的存储器组。存储器装置可以接收可以一或多个命令信号,所述一或多个命令信号指示一或多个存储器封装的组中的一或多个组中的操作。存储器装置可以进入刷新模式,在所述刷新模式下,存储器组中的一或多个存储器组中的字线被刷新。

存储器单元中的信息可能随时间推移而衰减。存储器单元可以逐行(例如,逐字线)刷新以保持存储器单元中的信息。在刷新操作期间,一或多个行中的信息可以重写回到相应的字线以恢复信息的初始值。对给定字线(例如,攻击者字线)的重复存取可能使一或多个物理上相邻的字线(例如,受害者字线)中的信息衰减的速率增加。在一些应用中,受害者字线可以被认为是物理上邻近攻击者字线的字线。例如,受害者字线可以定位在攻击者字线的任一侧上(例如,R+1和R-1)。在一些实施例中,邻近相邻字线的字线(例如,R+2和R-2)也可以被视为受害者字线。因此,在一些实施例中,每个攻击者地址可能存在四个受害者地址。在一些应用(如字线密集间隔开的存储器)中,更远的字线可以被认为是受害者字线(例如,R+3、R-3、R+4、R-4等)。

可以跟踪对存储器的不同字线的存取以确定字线是否是攻击者字线。被存取字线和/或攻击者字线的行地址可以存储在存储器中的寄存器或其它存储装置中。如果确定某一字线是攻击者字线,则可以至少部分地基于攻击者字线的行地址确定受害者字线。在一些实施例中,可以以目标(或“行锤击”)刷新操作的一部分的形式刷新受害者字线(例如,R+1、R-1、R+2和R-2)。用于保持受害者字线中的数据的目标刷新操作也可以被称为“修复(healing)”受害者字线。目标刷新操作可以保持受害者字线中的数据,但是目标刷新操作可能窃取将以其它方式用于自动刷新操作的时隙,从而降低自动刷新操作的速率。当目标刷新操作使自动刷新率降低时,可能在未受行锤击影响的存储器单元中发生数据退化。提高自动刷新率以补偿目标刷新可能使存储器使用较多电力和/或增加存储器存取操作(例如,读取、写入)之间的延迟。因此,期望减少不必要的目标刷新操作。

尽管与受害者字线相关联的被存取字线被称为攻击者字线,但是所述被存取字线仅是疑似攻击者字线和/或被视为用于对受害者字线进行抢占式修复的攻击者字线的字线。然而,为了简单起见,与受害者字线和/或在目标刷新操作期间刷新的字线相关联的任何字线都可以在本文中被称为攻击者字线。

虽然跟踪对不同字线的存取,但是通常不会跟踪与被存取字线相关联的受害者字线有关的数据。当未跟踪有关单独受害者字线的信息时,可能无法辨别哪些受害者字线已经被刷新。因此,可能提供与攻击者字线相关联的所有受害者字线以供刷新,从而确保所有受害者字线均被刷新。在一些应用中,这可能需要刷新四条字线(例如,R+1、R-1、R+2、R-2),这可能需要从自动刷新操作中“窃取”四次或四次以上刷新。可能令人期望的是,减小不必要的目标刷新操作的数量,以减少对自动刷新率的影响(例如,增加周期性目标刷新操作之间的时段)和/或存储器装置的功耗。

在具有行锤击管理能力的一些存储器中,可以存储与被存取字线相关联的行地址。另外,可以存储与被存取字线相关联的受害者字线的数据并且可以使所述数据与所存储的行地址相关联。

正如一条攻击者字线可以具有多个受害者一样,一条受害者字线可以是多于一条攻击者字线的受害者。例如,如果一对字线通过单条字线彼此分离,则中间的字线可以是相邻字线两者的受害者字线。因此,受害者字线可以与多个被存取行地址的受害者数据相关联。因此,可以基于受害者字线与所述多个被存取行地址的关联性而多次刷新受害者字线。然而,可能不需要多次刷新受害者字线。也就是说,受害者字线可能由于与不同的被存取行地址相关联的“副本”受害者数据而经历不必要的刷新操作。

此外,作为受害者的字线也可以是被存取字线。对字线进行存取会使存储在字线中的数据被检索并且重写到字线。因此,类似于刷新操作,对字线进行存取会“修复”存储在字线中的数据。因此,在被存取之后,可能不需要通过目标刷新操作刷新受害者字线以保持数据。

本公开涉及用于调整与被存取行地址相关联的受害者字线数据的设备和方法。一种设备可以包含“反向加扰器”,所述反向加扰器接收刷新地址或被存取行地址并且计算可能是对应于与刷新地址或被存取地址相关联的字线的攻击者字线的字线的行地址。换句话说,反向加扰器可以计算可能使与刷新地址或被存取行地址相对应的字线成为受害者字线的所有字线的行地址。可以对所计算的行地址的受害者数据进行调整,使得受害者数据反映通过一或多种机制(例如,目标刷新、自动刷新、存取)对受害者字线进行的“修复”(例如,保持存储在字线中的数据)。本文中所描述的调整受害者数据可以减少一些应用中的不必要的刷新操作的数量。

图1是示出了根据本公开的至少一个实施例的半导体装置的整体配置的框图。半导体装置100可以是如DRAM装置等集成在单个半导体芯片上的半导体存储器装置。

半导体装置100包含存储器阵列112。在一些实施例中,存储器阵列112可以包含多个存储器组。每个存储器组包含多条字线WL、多条位线BL和/BL和布置在所述多条字线WL与所述多条位线BL和/BL的交叉点处的多个存储器单元MC。对字线WL的选择由行控制电路108执行,并且对位线BL和/BL的选择由列控制电路110执行。在一些实施例中,存储器组中的每个存储器组可以有一个行控制电路108和一个列控制电路110。

位线BL和/BL耦合到相应的读出放大器(SAMP)117。来自位线BL和/BL的读取数据由读出放大器SAMP 117放大,并且通过互补本地数据线(LIOT/B)、传输门(TG)118和互补主数据线(MIO)传送到读取/写入放大器120。相反,从读取/写入放大器120输出的写入数据通过互补主数据线MIO、传输门118和互补本地数据线LIOT/B传送到读出放大器117,并且写入在耦合到位线BL和/BL的存储器单元MC中。

半导体装置100可以采用多个外部端子,所述多个外部端子包含耦合到命令和地址总线以接收命令和地址的命令和地址(C/A)端子、用于接收时钟CK和/CK的时钟端子、用于提供数据的数据端子DQ和用于接收电源电位VDD、VSS、VDDQ和VSSQ的电源端子。

为时钟端子供应向时钟输入电路122提供的外部时钟CK和/CK。外部时钟可以是互补的。时钟输入电路122基于CK和/CK时钟生成内部时钟ICLK。向命令控制电路106和内部时钟发生器电路124提供ICLK时钟。内部时钟发生器电路124基于ICLK时钟提供各种内部时钟LCLK。LCLK时钟可以用于对各种内部电路的操作进行定时。向输入/输出电路126提供内部数据时钟LCLK,以对包含在输入/输出电路126中的电路的操作进行定时,例如向数据接收器提供所述内部数据时钟以对写入数据的接收进行定时。

可以为C/A端子供应存储器地址。供应给C/A端子的存储器地址通过命令/地址输入电路102传送到地址解码器电路104。地址解码器电路104接收地址,并且将经解码的行地址XADD供应给行控制电路108并且将经解码的列地址YADD供应给列控制电路110。行地址XADD可以用于指定存储器阵列112的一或多条字线WL并且列地址YADD可以指定存储器阵列112的一或多条位线BL。地址解码器电路104还可以提供指定存储器的特定组的组地址BADD。可以向行控制电路108和/或列控制电路110提供组地址BADD以将存取操作定向到所述组中的一或多个组。可以为C/A端子供应命令。命令的实例包含用于控制各种操作的定时的定时命令、用于存取存储器的存取命令(如用于执行读取操作的读取命令和用于执行写入操作的写入命令)以及其它命令和操作。存取命令可以与一或多个行地址XADD、列地址YADD和/或组地址BADD相关联以指示要存取的一或多个存储器单元。

命令可以通过命令/地址输入电路102以内部命令信号的形式提供给命令控制电路106。命令控制电路106包含用于对内部命令信号进行解码以生成用于执行操作的各种内部信号和命令的电路。例如,命令控制电路106可以提供用于选择字线的行命令信号和用于选择位线的列命令信号。

装置100可以接收作为行激活命令ACT的存取命令。当接收到行激活命令ACT时,行地址XADD与行激活命令ACT一起及时供应。

装置100可以接收作为读取命令的存取命令。当接收到读取命令时,组地址BADD和列YADD地址与读取命令一起及时供应,从存储器阵列112中对应于行地址XADD和列地址YADD的存储器单元中读取读取数据。读取命令由命令控制电路106接收,所述命令控制电路提供内部命令,使得来自存储器阵列112的读取数据提供给读取/写入放大器120。读取数据通过输入/输出电路126从数据端子DQ输出到外部。

装置100可以接收作为写入命令的存取命令。当接收到写入命令时,组地址和列地址与写入命令一起及时供应,向数据端子DQ供应的写入数据写入到存储器阵列112中对应于行地址和列地址的存储器单元。写入命令由命令控制电路106接收,所述命令控制电路提供内部命令,使得写入数据由输入/输出电路126中的数据接收器接收。还可以向外部时钟端子提供写入时钟以对由输入/输出电路126的数据接收器对写入数据进行的接收进行定时。写入数据可以通过输入/输出电路126供应给读取/写入放大器120,并且通过读取/写入放大器120供应给存储器阵列112以写入到存储器单元MC中。

装置100还可以接收使所述装置执行刷新操作的命令。刷新信号AREF可以是在命令控制电路106接收到指示刷新模式的信号时激活的脉冲信号。在一些实施例中,刷新命令可以在外部发出到存储器装置100。在一些实施例中,刷新命令可以由装置的组件周期性地生成。在一些实施例中,当外部信号指示刷新进入命令时,也可以激活刷新信号AREF。刷新信号AREF可以在命令输入之后立即激活一次,并且此后可以以期望的内部定时循环激活。因此,刷新操作可以自动继续。自刷新退出命令可以使刷新信号AREF的自动激活停止并返回到空闲(IDLE)状态。

刷新控制电路116将刷新行地址RXADD供应给行控制电路108,所述行控制电路可以刷新由刷新行地址RXADD指示的一或多条字线WL。刷新控制电路116可以基于刷新信号AREF控制刷新操作的定时。在一些实施例中,响应于AREF的激活,刷新控制电路116可以生成对泵浦信号的一或多次激活,并且可以为泵浦信号的每次激活(例如,每次泵浦)生成并提供刷新地址RXADD。

一种类型的刷新操作可以是自动刷新操作。响应于自动刷新操作,存储器组可以刷新存储器的字线或字线组,并且然后可以响应于下一个自动刷新操作而刷新存储器组的下一条字线或下一个字线组。刷新控制电路116可以以刷新地址RXADD的形式提供指示存储器组中的字线或字线组的自动刷新地址。刷新控制电路116可以生成刷新地址RXADD序列,使得自动刷新操作可以随时间推移循环通过存储器组的所有字线WL。刷新操作的定时可以使得每条字线以至少部分地基于存储器单元中的数据退化的正常速率(例如,自动刷新率)的频率刷新。

另一种类型的刷新操作可以是目标刷新操作。如前所述,对存储器的特定字线(例如,攻击者字线)的重复存取可能使相邻字线(例如,受害者字线)中的衰减速率由于例如字线之间的电磁耦合而增加。在一些实施例中,受害者字线可以包含物理上邻近攻击者字线的字线。在一些实施例中,受害者字线可以包含进一步远离攻击者字线的字线。如果在受害者字线的下一个自动刷新操作之前未对所述受害者进行刷新,则受害者字线中的信息可能以使得数据可能丢失的速率衰减。为了防止信息丢失,可能需要标识攻击者字线并且然后执行目标刷新操作,其中与一或多条相关联的受害者字线相关联的刷新地址RXADD被刷新。

刷新控制电路116可以以刷新地址RXADD的形式选择性地输出目标刷新地址(例如,受害者行地址)或自动刷新地址(automatic refresh address)(例如,自动刷新地址(auto-refresh address))。自动刷新地址可以来自基于对自动刷新信号AREF的激活而提供的地址序列。刷新控制电路116可以以通过AREF确定的速率循环通过自动刷新地址序列。在一些实施例中,自动刷新地址序列可以通过更新(例如,递增)前一个自动刷新地址的一或多个部分来生成。

刷新控制电路116还可以基于存储器阵列112中的附近的地址(例如,对应于攻击者字线的攻击者行地址)的存取模式确定目标刷新地址,所述目标刷新地址是需要刷新的地址(例如,对应于受害者字线的受害者行地址)。刷新控制电路116可以选择性地使用装置100的一或多个信号来计算刷新地址RXADD。例如,刷新地址RXADD可以基于地址解码器电路104提供的行地址XADD计算。刷新控制电路116可以接收地址解码器电路104提供的行地址XADD的当前值并且基于接收到的地址中的一或多个地址确定目标刷新地址。

刷新地址RXADD可以与基于对刷新信号AREF的定时的定时一起提供。刷新控制电路116可以具有对应于AREF的定时的时隙,并且可以在每个时隙期间提供一或多个刷新地址RXADD。在一些实施例中,可以在原本将在其它方面分配给自动刷新地址的时隙中发出目标刷新地址(例如,“窃取”)。在一些实施例中,可以为目标刷新地址保留某些时隙。这些时隙可以被称为目标刷新时隙。为目标刷新地址保留的时隙之间的时间段可以被称为目标刷新率或窃取率。当分配给目标刷新的时隙的数量增加时,窃取率增加,并且有效的自动刷新率降低。在一些实施例中,分配给目标刷新的时隙的数量是恒定的。在一些实施例中,刷新控制电路116可以确定是否提供目标刷新地址、是否在所述时隙期间不提供地址或是否在所述时隙期间反而提供自动刷新地址。因此,在一些实施例中,窃取率可以不随时间推移而保持恒定。

刷新控制电路116可以接收地址解码器电路104提供的行地址XADD并且可以基于行地址XADD确定哪些字线正被锤击。刷新控制电路116可以基于行地址XADD对字线的存取进行计数并且可以基于存取的计数(例如,达到阈值)确定哪些字线是攻击者。行地址XADD和存取计数值可以由刷新控制电路116存储。在一些实施例中,刷新控制电路116可以进一步存储与和对应于行地址XADD的字线相关联的受害者字线相关联的受害者数据。例如,可以存储R+1、R-1、R+2和/或R-2的标志。这些可以被称为受害者标志。当存储行地址XADD时,可以将受害者数据设置成第一值(例如,可以将受害者标志设置成第一逻辑电平)。在一些实施例中,一旦受害者字线已经刷新(例如,修复),就可以将与受害者字线相关联的受害者数据设置成第二值(例如,将受害者标志设置成第二逻辑电平)。

在一些实施例中,当存取计数值达到阈值时,可以通过刷新控制电路116计算与和行地址XADD相关联的字线的受害者字线相关联的一或多个受害者行地址。所计算的受害者行地址可以至少部分地基于受害者数据。例如,如果存取计数值达到阈值,并且所有受害者行的受害者数据等于第一值,则可以确定与作为与行地址XADD相关联的字线的受害者的字线相对应的所有受害者行地址。在另一个实例中,如果仅一些受害者数据等于第一值,则仅确定与和等于第一值的受害者数据相关联的字线相对应的受害者行地址。可以不确定等于第二状态的受害者数据的受害者行地址。在一些实施例中,可以向目标地址队列提供受害者行地址以在目标刷新时隙(例如,顺序的目标刷新时隙)期间进行刷新。在刷新受害者字线之后,可以将与那些字线相关联的受害者数据设置成第二值。继续这个实例,可以减小或复位(例如,设置成零)与行地址XADD相关联的存取计数值。

在一些实施例中,刷新控制电路116可以确定受害者字线是否已经通过目标刷新、自动刷新和/或存储器存取操作(例如,读取、写入)“修复”并且因此调整与受害者字线相关联的受害者数据。例如,在一些实施例中,刷新控制电路116可以基于刷新地址RXADD和/或行地址XADD计算攻击者行地址。攻击者行地址可以对应于与刷新地址RXADD或行地址XADD相关联的受害者字线的攻击者字线。可以所计算的攻击者行地址与所存储的行地址进行比较。如果在所存储的行地址之间存在一或多个匹配,则可以将对应于与RXADD和/或XADD相关联的字线的受害者数据设置成第二(例如,经修复)值。在一些实施例中,可以将自动刷新和/或XADD与受害者数据(如队列中的要刷新的受害者行地址)进行比较。如果受害者行地址中的一个受害者行地址与自动刷新地址和/或XADD匹配,则将所述受害者地址从队列中移除。因此,所移除的受害者行地址将不会在目标刷新操作中刷新。因此,由于与RXADD和XADD相关联的字线与多条攻击者字线存在关联性或当所述字线通过其它机制(例如,存取操作、自动刷新)修复时,可以不多次刷新所述字线。

为电源端子供应电源电位VDD和VSS。电源电位VDD和VSS供应给内部电压发生器电路128。内部电压发生器电路128基于供应给电源端子的电源电位VDD和VSS生成各种内部电位VPP、VOD、VARY、VPERI等。内部电位VPP主要在行解码器电路108中使用,内部电位VOD和VARY主要在存储器阵列118中包含的读出放大器SAMP中使用,并且内部电位VPERI在许多外围电路块中使用。

还为电源端子供应电源电位VDDQ和VSSQ。电源电位VDDQ和VSSQ供应给输入/输出电路126。在本公开的实施例中,供应给电源端子的电源电位VDDQ和VSSQ可以与供应给电源端子的电源电位VDD和VSS的电位相同的电位。在本公开的另一个实施例中,供应给电源端子的电源电位VDDQ和VSSQ可以与供应给电源端子的电源电位VDD和VSS的电位不同的电位。供应给电源端子的电源电位VDDQ和VSSQ用于输入/输出电路122,使得由输入/输出电路126产生的电源噪声不会传播到其它电路块。

图2是根据本公开的实施例的刷新控制电路的框图。在一些实施例中,一些或所有组件(例如,刷新控制电路216和行解码器电路208)可以对应于存储器的特定组,并且这些组件可以针对存储的组的每个组重复。因此,在一些实施例中,可以存在多个刷新控制电路216和行解码器电路208。为简洁起见,将仅描述单个组的组件。在一些实施例中,刷新控制电路216可以包含在图1所示的刷新控制电路116中。在一些实施例中,行解码器电路208可以包含在行控制电路108中。

DRAM接口226可以向地址刷新控制电路216和行解码器电路208提供一或多个信号。刷新控制电路216可以包含攻击者行检测器电路230(例如,AGR行检测器)、行锤击刷新(RHR)状态控制236、刷新地址发生器234和反向加扰器246。DRAM接口226可以提供一或多个控制信号(如自动刷新信号AREF)和行地址XADD。

DRAM接口226可以表示向组218的组件提供信号的一或多个组件。在一些实施例中,DRAM接口226可以表示耦合到半导体存储器装置(例如,图1的装置100)的存储器控制器。在一些实施例中,DRAM接口226可以表示如图1的命令地址输入电路102、地址解码器电路104和/或命令控制电路106等组件。DRAM接口226可以提供行地址XADD、自动刷新信号AREF、激活信号ACT和预充电信号Pre。自动刷新信号AREF可以是可以指示何时发生自动刷新操作的周期信号。可以提供激活信号ACT以激活存储器的给定组。行地址XADD可以是包含多个位(其可以串行或并行传输)的信号并且可以对应于存储器组(例如,通过ACT/Pre激活的存储器组)的特定行。

AGR行检测器230可以接收当前行地址XADD。在一些实施例中,AGR行检测器230可以存储行地址XADD的当前值,和/或基于一或多个先前存储的行地址确定当前行地址XADD是否是攻击者地址。例如,在一些实施例中,AGR行检测器230可以基于接收到行地址XADD的次数(例如,存取对应字线的次数)确定行地址是否是攻击者地址。在其它实施例中,AGR行检测器230可以确定存取计数值最高的行地址是攻击者行地址,而无论存取计数值如何。AGR行检测器230可以进一步存储与所存储的行地址相关联的受害者字线的受害者数据。例如,AGR行检测器230可以存储与每条受害者字线相关联的标志。AGR行检测器230可以以匹配地址HitXADD的形式向刷新地址发生器232提供所述地址中的一或多个地址。匹配地址HitXADD可以表示攻击者字线。在一些实施例中,AGR行检测器230可以进一步提供如一或多个标志FLAG等将更详细地描述的与匹配地址HitXADD相关联的受害者数据。

行地址XADD可以在DRAM接口226将存取操作(例如,读取和写入操作)定向到存储器单元阵列(例如,图1的存储器单元阵列118)的不同行时发生变化。在一些实施例中,AGR行检测器230可以存储每个接收到的行地址XADD。在其它实施例中,AGR行检测器230可以响应于采样定时发生器(未示出)提供的有效采样信号而存储接收到的行地址。在一些实施例中,采样信号可以是脉冲信号。也就是说,所述采样信号可以转变为有效状态并且在一段时间(例如,一半时钟周期、一个时钟周期)之后回到非有效状态。采样发生器可以定期、随机或伪随机地改变采样信号的脉冲之间的时间间隔。

RHR状态控制236可以控制对目标刷新操作的定时。RHR状态控制236可以提供行锤击刷新信号RHR以指示应发生目标刷新(例如,刷新与所标识攻击者行相对应的受害者行)。RHR状态控制236还可以提供内部刷新信号IREF,以指示应发生自动刷新。响应于RHR的激活,刷新地址发生器232可以提供刷新地址RXADD,所述刷新地址可以是自动刷新地址或可以是与对应于匹配地址HitXADD的攻击者字线的受害者字线相对应的一或多个受害者地址。受害者行地址可以至少部分地基于AGR行检测器230提供的受害者标志FLAG。行解码器电路208可以响应于刷新地址RXADD和行锤击刷新信号RHR而执行目标刷新操作。行解码器电路208可以基于刷新地址RXADD和内部刷新信号IREF而执行自动刷新操作。在一些实施例中,行解码器电路208可以接收DRAM接口226提供的自动刷新信号AREF,并且可以不使用内部刷新信号IREF。

RHR状态控制236可以接收自动刷新信号AREF并且可以提供行锤击刷新信号RHR和内部刷新信号IREF。可以周期性地生成自动刷新信号AREF并且所述自动刷新信号可以用于控制刷新操作的定时。存储器装置可以执行自动刷新操作序列以周期性地刷新存储器装置的行。可以生成RHR信号以指示应刷新特定目标行地址而不是来自自动刷新地址序列的地址。例如,如果与行地址XADD相关联的存取计数值已经达到或超过阈值。RHR状态控制236可以使用内部逻辑以提供RHR信号。在一些实施例中,RHR状态控制236可以基于某一数量的AREF激活(例如,每第4次AREF激活)提供RHR信号。RHR状态控制236还可以提供内部刷新信号IREF,所述内部刷新信号可以指示应发生自动刷新。在一些实施例中,信号RHR和IREF可以被生成为使得所述信号不同时有效(例如,不会同时处于高逻辑电平)。

现在关注刷新地址发生器232,刷新地址发生器232可以包含自动刷新地址发生器234(AREF地址发生器)、地址加扰器238、目标地址队列240、多路复用器242和控制逻辑电路244。在一些实施例中,刷新地址发生器232可以进一步包含反向加扰器246。刷新地址发生器232基于匹配地址HitXADD以刷新地址RXADD的形式提供自动刷新地址Pre_RXADD或受害者地址HitXADD2。

AREF地址发生器234响应于刷新信号AREF而生成自动刷新地址Pre_RXADD。自动刷新地址Pre_RXADD可以是地址序列的要以自动刷新操作的一部分的形式刷新的一部分。AREF地址发生器234可以响应于有效刷新信号AREF而将当前自动刷新地址Pre_RXADD更新为序列中的下一个地址。还向AREF地址发生器234提供来自RHR状态控制236的命令信号RHR。当命令信号RHR有效时,可以控制AREF地址发生器234停止更新自动刷新地址Pre_RXADD,即使在一些实施例中,自动刷新信号AREF有效,也是如此。如本文中所描述的,因为有效命令信号RHR指示要进行目标刷新操作而不是自动刷新操作,所以这使自动刷新操作在目标刷新被执行时暂停,并且在命令信号RHR无效时重新开始。然而,如将更详细地描述的,在一些实施例中,目标地址队列240提供的有效空(Empty)信号可以覆盖命令信号RHR以阻止暂停自动刷新操作。

地址加扰器238基于AGR行检测器230标识的攻击者行地址(例如,与高于阈值的计数值相关联的行地址XADD)和受害者数据(如AGR行检测器230提供的受害者标志FLAG)的状态计算要刷新的一或多个地址。可以以输入形式向地址加扰器238提供匹配地址HitXADD和受害者数据。地址加扰器238可以响应于这些输入而提供目标刷新地址HitXADD1。目标刷新地址HitXADD1可以是可能受与匹配地址HitXADD相对应的存储器位置的重复激活的影响的存储器位置(例如,字线)的地址。换句话说,匹配地址HitXADD可以是“攻击者”地址,并且目标刷新地址HitXADD1可以是“受害者”地址。可以使用不同的计算来生成不同的受害者地址作为目标刷新地址HitXADD1。

地址加扰器238可以采用不同的计算以基于受害者数据(如受害者标志FLAG)的状态确定受害者行地址。在一个实例中,可以将第一计算用于与和与匹配地址HitXADD相关联的攻击者字线具有第一物理关系(例如,物理上邻近攻击者字线)的受害者字线相对应的处于第一状态的受害者标志。可以将第二计算用于与和与匹配地址HitXADD相关联的攻击者字线具有第二物理关系(例如,物理上邻近与攻击者字线物理上相邻的受害者字线)的受害者字线相对应的处于第一状态的受害者标志。计算可以提供与和对应于匹配地址HitXADD的字线具有已知物理关系(例如,空间关系)的字线相对应的目标刷新地址HitXADD1。在本公开的一些实施例中,例如,当仅一个受害者标志处于第一(例如,未修复)状态时,计算可以产生单个目标刷新地址HitXADD1。在本公开的其它实施例中,例如,当多个受害者标志处于第一状态时,计算可以产生目标刷新地址HitXADD1序列。在一些实施例中,地址加扰器238可以不计算与和经修复状态(例如,第二逻辑电平)相关联的受害者数据(例如,受害者标志)相关联的受害者字线的受害者行地址。

在一个实施例中,第一计算可以使地址加扰器238输出与邻近对应于匹配地址HitXADD的字线的字线相对应的地址(例如,HitXADD1=HitXADD+/-1)。第二计算可以使地址加扰器238输出与邻近对应于地址HitXADD+/-1的字线的字线相对应的地址(例如,HitXADD1+/-2)。在其它示例实施例中,其它计算是可能的。例如,第一计算可以基于与匹配地址HitXADD1的物理关系,而第二计算可以基于与通过第一计算提供的一或多个地址的物理关系。在一些实施例中,可以向目标地址队列240提供地址加扰器238计算的目标地址HitXADD1。

目标地址队列240可以从地址加扰器238接收目标刷新地址HitXADD1并且基于目标刷新地址HitXADD1提供目标刷新地址HitXADD2。目标地址队列240可以存储从地址加扰器238接收到的一或多个目标刷新地址HitXADD1。在一些实施例中,目标地址队列240可以将受害者行地址HitXADD1与存储在队列中的当前受害者行地址进行比较。如果受害者行地址HitXADD1已经处于队列中,则不添加受害者行地址HitXADD1。在目标刷新时隙之间,多个行地址的存取计数值可以符合或超过阈值。此外,每个行地址可以与多个受害者行地址相关联。在一些实施例中,受害者行地址(例如,HitXADD1)可以存储在目标地址队列240中以供在顺序的目标刷新时隙期间进行刷新。在一些实施例中,目标地址队列240可以是“先进先出”队列。在一些实施例中,目标地址队列240可以包含多个寄存器。然而,可以使用其它存储结构。在一些实施例中,目标地址队列240可以具有指向要以目标刷新地址HitXADD2的形式输出的受害者行地址的指针。响应于有效命令信号RHR,可以使指针递增到队列中的下一个受害者行地址,并且可以以HitXADD2的形式输出下一个受害者行地址。在一些实施例中,一旦以HitXADD2的形式提供了存储在寄存器中的受害者行地址,目标地址队列240就可以清除寄存器。在一些实施例中,目标地址队列240可以使用标志来指示已经以HitXADD2的形式提供了受害者行地址。清除寄存器和/或设置标志可以允许目标地址队列240确定寄存器何时可用于重写和/或队列何时为空。还可以使用用于控制队列和确定队列的状态的其它技术。如果目标地址队列240确定受害者行地址队列为空,则目标地址队列240可以激活Empty信号。

多路复用器242接受AREF地址发生器234提供的自动刷新地址Pre_RXADD和目标地址队列240提供的目标刷新地址HitXADD2并且以刷新地址RXADD的形式将其输出。多路复用器242可以基于命令信号RHR和Empty信号在两个刷新地址之间进行选择。向控制逻辑电路244提供命令信号RHR和Empty,并且将输出提供给多路复用器242以控制对以刷新地址RXADD的形式提供Pre_RXADD或HitXADD2地址的选择。如果命令信号RHR有效并且Empty无效,则控制逻辑电路244输出第一逻辑电平。多路复用器242响应于第一逻辑电平而输出目标地址HitXADD2。如果命令信号RHR无效,则控制逻辑电路244可以输出第二逻辑电平,而无论Empty信号如何。多路复用器242响应于第二逻辑电平而输出自动刷新地址Pre_RXADD。如果命令信号RHR有效,但Empty信号有效(例如,目标地址队列240为空),则控制逻辑电路244可以输出第二逻辑电平并且多路复用器242可以输出自动刷新地址Pre_RXADD。如前所述,因为有效Empty命令可以覆盖提供给AREF地址发生器234的命令信号RHR,所以提供当前Pre_RXADD。因此,如果没有受害者行需要刷新,则可以执行自动刷新操作,即使在目标刷新间隔期间,也是如此。然而,在其它实施例中,如果受害者行地址不可用,则刷新地址发生器232可以不提供刷新地址RXADD,并且在目标刷新时隙期间可以不执行刷新操作。

经过刷新的字线(例如,对应于刷新地址RXADD的字线)可以是多条攻击者字线的潜在受害者。例如,两条潜在攻击者字线可以在经过刷新的字线的相对侧直接相邻。如果在AGR行检测器230中存储了对应于两条攻击者字线的行地址,则可能存在与和两个行地址相关联的经过刷新的字线相对应的受害者数据。例如,给定字线可以与一个行地址的R+1受害者标志和另一个行地址的R-1受害者标志相关联。因此,如果经过刷新的字线基于与一个行地址相关联的受害者数据进行刷新并且基于与另一个行地址相关联的受害者数据再次刷新,则刷新字线的频率可以超过所需频率。在一些应用中,这可能使窃取率被设置为高于所需值的值。

此外,类似于经过刷新的字线,被存取字线可以是与存储在AGR行检测器230中的行地址相对应的一或多条字线的受害者。当字线在存储器存取操作(例如,激活、读取、写入)期间被存取时,字线中的数据也会被刷新。因此,在一些情况下,如果存取对应于行地址XADD的字线并且随后基于与存储在AGR行检测器230中的行地址相关联的受害者数据对其进行刷新,则尽管存取操作使对刷新操作的需要无实际意义,也刷新被存取字线。在一些应用中,这可能使窃取率被设置为高于所需值的值。

在一些实施例中,刷新地址发生器232可以包含用于确定与刷新地址RXADD或被存取行地址XADD相关联的潜在攻击者行地址(例如,攻击者行地址)的反向加扰器246。也就是说,刷新地址发生器232可以确定物理上邻近字线(例如,RXADD+1和RXADD-1或XADD+1和XADD-1)的攻击者字线和/或与字线的物理上相邻的字线物理上相邻的字线(例如,RXADD+2和RXADD-2或XADD+2和XADD-2)。所计算的攻击者行地址AXADD可以提供给AGR行检测器230并且可以将其与存储在AGR行检测器230中的行地址XADD进行比较。如果攻击者行地址AXADD匹配,则可以将与匹配行地址XADD相关联的合适的受害者数据(例如,受害者标志)设置成指示受害者字线已经修复(和/或不再需要刷新)的状态。这可以减少对作为与存储在AGR行检测器230中的行地址相对应的一或多条字线的受害者的受害者字线的不必要刷新。

可以将不同的计算用于生成不同的攻击者行地址AXADD。在本公开的一些实施例中,计算可以产生攻击者地址AXADD。在本公开的其它实施例中,计算可以产生攻击者行地址AXADD序列。换句话说,反向加扰器246可以确定可以使对应于RXADD或XADD的字线成为受害者字线的所有字线的行地址。

在一些实施例中,反向加扰器246和地址加扰器238可以具有相同或类似的电路系统。例如,反向加扰器246和地址加扰器238两者均基于字线之间的物理关系计算行地址。然而,提供给地址加扰器238和反向加扰器246的输入地址是不同的,如上文所述。在未在图2中示出的一些实施例中,可以使用单个地址加扰器。可以使用另外的控制逻辑以在输入(例如,HitXADD、RXADD、XADD)与输出(例如,AGR行检测器、目标地址队列)之间切换。

在一些实施例中,反向加扰器246可以只接收刷新地址RXADD或被存取行地址XADD以计算攻击者行地址AXADD。虽然这些实施例提供的用于调整AGR行检测器230中的受害者数据的反馈可能较少,但是只计算刷新地址RXADD或被存取行地址XADD的攻击者行地址AXADD可以减少计算和/或比较的次数,这进而可以减少功耗和/或计算时间。

在一些实施例中,除存储在AGR行检测器230中的受害者数据之外或代替所述受害者数据,可以调整刷新控制电路216中的其它受害者数据。例如,受害者数据可以包含受害者行地址。在一些实施例中,可以调整存储在目标地址队列240中的受害者行地址。在一些实施例中,目标地址队列240可以接收自动刷新地址Pre_RXADD和/或被存取行地址XADD。目标地址队列240可以将自动刷新地址Pre_RXADD和/或行地址XADD与存储在队列中的受害者行地址比较。如果存在匹配,则可以从队列中移除受害者行地址,因为与受害者行地址相关联的受害者字线已经通过存取或自动刷新操作修复。因此,通过移除受害者行地址,受害者数据调整成指示与受害者行地址相关联的受害者字线已经修复。

在一些应用中,调整存储在目标地址队列240中的受害者行地址可以是有利的,因为不需要对攻击者行地址进行“反向”计算。然而,在一些应用中,调整AGR行检测器230中的受害者数据可以是有利的,因为这可以减少地址加扰器238执行的不必要的受害者行地址计算。在一些应用中,可能有利的是,调整目标地址队列240中的受害者数据和AGR行检测器中的受害者数据以减少不必要的目标刷新操作。

行解码器电路208可以基于接收到的信号和地址对存储器阵列(未示出)执行一或多个操作。例如,响应于激活信号ACT和行地址XADD(以及IREF和RHR处于低逻辑电平),行解码器电路208可以指示对指定行地址XADD的一或多个存取操作(例如,读取操作)。响应于RHR信号有效,行解码器电路208可以对刷新地址RXADD进行刷新。

图3是根据本公开的实施例的攻击者行检测器(例如,AGR行检测器)300的框图。在一些实施例中,AGR行检测器300可以包含在图2的AGR行检测器230中。AGR行检测器300可以包含堆栈310。在一些实施例中,堆栈310可以是内容可寻址存储器(CAM)地址堆栈,然而,在其它实施例中,可以使用其它类型的数据存储装置。堆栈310可以包含多个寄存器302,所述多个寄存器中的每个寄存器可以具有对应的字段304、306和308。每个字段304、306和308可以包含一或多个位。每个字段中的位的数量可以至少部分地基于要存储在字段中的数据的类型。虽然图3中的实例示出了堆栈310中的八个寄存器302,但是应当理解,堆栈可以包含更少或更多的寄存器。例如,堆栈310可以具有一百个寄存器。在另一个实例中,堆栈310可以具有四百个寄存器。在图3中所示的实施例中,每个寄存器302包含被配置成存储行地址(RowADD0-7)的字段304、被配置成存储存取计数值(ACntVal0-7)的字段306、被配置成存储受害者数据(如图3中所示出的实例中的一或多个受害者标志(Vflags0-7))的字段308。在其它实施例中,可以使用更多或更少的字段。例如,可以使用多个字段来存储行地址的不同部分。

字段304可以接收行地址XADD。在一些实施例中,字段304可以从地址解码器电路(如图1中所示出的地址解码器电路104)接收行地址XADD。存储行地址的字段304可以耦合到刷新地址发生器(未在图3中示出)(如图2中所示出的刷新地址发生器234),并且向地址发生器提供匹配地址HitXADD。用于存储受害者标志的字段308可以具有作为与存储在字段304中的行地址相对应的字线的潜在受害者的每条受害者字线的标志(例如,位)。例如,字段308可以具有对应于R+1、R-1、R+2和R-2受害者字线的四个标志。在其它实例中,字段308可以具有对应于R+1和R-1的两个标志。可以使用其它数量的位,例如,每个标志可以包含两个位,其中第一位指示修复状态(例如,修复或未修复)并且第二位指示相关联字线的接近度(例如,R+/1或R+/-2)。在一些实施例中,用于存储受害者标志的字段308还可以耦合到刷新地址发生器并且向刷新地址发生器提供受害者标志VFLAG。存储存取计数值的字段306可以耦合到可以通过计数器加扰器314耦合到指针316的比较器电路312。

在一些实施例中,每次提供行地址XADD时,可以将当前行地址XADD与字段304进行比较。在其它实施例中,如前所述,堆栈310可以响应于采样信号(未示出)而存储行地址XADD,而不是存储接收到的每个行地址XADD。在这些实施例中,仅将在采样信号有效时接收到的行地址XADD与字段304进行比较。如果当前行地址XADD已经存储在寄存器302之一中,则可以调整(例如,增加)字段306中的存取计数值。如果当前行地址XADD尚未存储在寄存器302之一中,则可以在字段304中将所述行地址添加到寄存器302。如果存在开放式寄存器(例如,没有行地址的寄存器),则可以将行地址XADD存储在开放式寄存器中。如果不存在开放式寄存器,则与最低计数值相关联的寄存器302(如由指针316指示的)可以将其行地址替换为当前行地址XADD。在将新的行地址写入到寄存器302时,可以将受害者标志设置成指示尚未刷新任何相关联受害者字线的第一状态并且在一些实施例中,可以将计数器复位到初始值(例如,0)。

受害者字线可以是基于多条攻击者字线的受害者,因此,在刷新受害者字线时,所述受害者字线可以与寄存器302中的多个受害者标志相关联。在一些应用中,计算攻击者行地址以及将所述攻击者行地址与存储在寄存器302中的行地址进行比较可以减少冗余的受害者行刷新。在一些实施例中,堆栈310可以接收攻击者行地址AXADD。攻击者行地址AXADD可以至少部分地基于刷新地址RXADD或接收到的行地址XADD。在一些实施例中,攻击者行地址AXADD可以对应于可以使对应于RXADD或XADD的字线受害的字线。可以将攻击者行地址AXADD与字段304进行比较。如果攻击者行地址AXADD与所存储的行地址中的任何行地址都不匹配,则堆栈310不采取行动。如果攻击者行地址AXADD与一或多个行地址匹配,则可以将存储在字段308中的一或多个合适的受害者标志或设置成指示受害者字线已经通过受害者数据逻辑电路318修复的状态,如将参考图5更详细地描述的。

在一些实施例中,比较器电路312可以将字段306中的存取计数值与阈值进行比较以确定行地址的存取计数值是否已匹配或超过阈值(例如,1,000、2,000、3,000)。在一些实施例中,比较器电路312可以进一步比较存取计数值以确定哪个行地址与最低存取计数值相关联。可以向计数器加扰器314提供与最小计数值和满足或超过阈值的计数值相对应的字段306,所述计数器加扰器可以将高于阈值字段和最小计数值字段与其相应的相关联行地址字段304进行匹配。指针316可以指向字段304中与等于或高于阈值的计数值相关联的行地址并且可以指向与字段306中的最小计数值相关联的字段304。可以使用一或多个阈值指针以便以HitXADD的形式向刷新地址发生器提供一或多个对应的行地址并且以VFLAG的形式向其提供对应的受害者标志。当基于地址HitXADD执行目标刷新操作时,可以将一些或所有受害者标志设置成指示已经刷新对应的受害者字线的第二状态。如果将所有受害者标志设置成第二状态(例如,已经刷新所有受害者字线),则可以复位存取计数值。当接收到新的行地址XADD并且不存在用于将所述新的行地址存储在其中的开放式寄存器302时,可以使用最小计数值指针以覆写寄存器302。

在其它实施例中,比较器电路312可以比较计数值以确定哪个行地址与最高存取计数值相关联。可以向计数加扰器314提供对应于最高计数值的字段306,所述计数器加扰器可以将最高计数值字段与其相关联行地址字段304进行匹配。最高计数值指针316可以用于以HitXADD的形式向刷新地址发生器提供对应的行地址并且以VFLAG的形式向其提供对应的受害者标志。

图4是根据本公开的实施例的内容可寻址存储器(CAM)单元的图。在一些实施例中,CAM单元400可以包含在堆栈中,如图3中所示出的堆栈310。在一些实施例中,CAM单元400可以包含在寄存器中,如图3中所示出的寄存器302。在一些实施例中,CAM单元400可以包含在图2中的目标地址队列240中。例如,目标地址队列240可以包含用于存储受害者行地址的堆栈,所述堆栈可以包含一或多个寄存器。寄存器可以包含多个CAM单元400。寄存器可以包含针对存储在寄存器中的每个位的一个CAM单元。例如,寄存器可以包含针对行地址的每个位、存取计数值的每个位和每个标志位的一个CAM单元。堆栈可以包含包括CAM单元的多个寄存器。

CAM单元400包含锁存器部分402和比较器部分404。CAM单元400通常可以使用电压来表示各个位的值。CAM单元400可以包含承载表示所述位的逻辑值的电压的导电元件(例如,节点、导电线)。例如,高逻辑电平可以由第一电压(例如,系统电压,如VPERI)来表示,而低逻辑电平可以由第二电压(例如,接地电压,如VSS)来表示。

锁存器部分402包含第一晶体管406,所述第一晶体管具有耦合到提供电压VPERI的节点的源极,所述电压可以表示高逻辑电平。第一晶体管406具有耦合到具有表示信号Q的值的电压的节点417的漏极和耦合到具有表示互补信号QF的值的电压的节点419的栅极。信号Q表示存储在锁存器部分402中的位的逻辑电平。第一晶体管406可以是p型晶体管。锁存器部分402还包含第二晶体管407,所述第二晶体管具有耦合到提供VPERI的节点的源极、耦合到节点417的栅极和耦合到节点419的漏极。第二晶体管407可以是p型晶体管。

锁存器部分402包含第三晶体管408,所述第三晶体管具有耦合到节点417的漏极、耦合到节点419的栅极和耦合到提供接地电压VSS的节点的源极,所述接地电压表示低逻辑电平。第三晶体管408可以是n型晶体管。锁存器部分402包含第四晶体管409,所述第四晶体管具有耦合到节点419的漏极、耦合到节点417的栅极和耦合到提供接地电压VSS的节点的源极。第四晶体管409可以是n型晶体管。晶体管406和408可以形成反相器电路并且晶体管407和409可以形成另一个反相器电路,并且两个反相器电路彼此交叉耦合。

在操作中,第一、第二、第三和第四晶体管406-409可以工作以存储所存储信号Q和QF的值。晶体管406-409可以一起工作以将承载Q的节点417和承载QF的节点619耦合到提供与信号Q和QF的值相关联的系统电压(例如,VPERI或VSS)的节点。例如,如果所存储信号Q处于高逻辑电平,则反相信号QF处于低逻辑电平。第一晶体管406可以是有效的,并且VPERI可以耦合到节点417。第二晶体管407和第三晶体管408可以是无效的。第四晶体管409可以是有效的并且可以将VSS耦合到节点419。这可以使节点417保持处于VPERI的电压(其表示高逻辑电平),并且使节点419保持处于VSS的电压(其表示低逻辑电平)。在另一个实例中,如果所存储信号Q处于低逻辑电平,则反相信号QF处于高逻辑电平。第一晶体管406和第四晶体管409两者均可以是无效的。第二晶体管407可以是有效的并且可以将VPERI耦合到节点419。第三晶体管408也可以是有效的并且可以将VSS耦合到节点417。以这种方式,所存储信号Q和QF可以耦合到对应于其当前逻辑电平的相应系统电压,这可以维持所存储位的当前逻辑值。

锁存器部分402还包含第五晶体管410和第六晶体管411。当写入信号Write有效时,晶体管410和411可以充当开关,所述开关可以将承载输入数据D的信号线和承载反相输入数据DF的信号线耦合到分别承载Q和QF的节点417和419。第五晶体管410具有耦合到承载Write信号的线的栅极、耦合到信号D的漏极和耦合到节点419的源极。第六晶体管411具有耦合到Write信号的栅极、耦合到信号DF的漏极和耦合到节点419的源极。因此,当Write信号处于高电平(例如,处于如VPERI等电压)时,晶体管410和411可以是有效的,并且信号D和DF的电压可以耦合到分别承载Q和QF的节点417和419。

在一些实施例中,第一到第六晶体管406-411的大小通常可以全都彼此相同。

CAM单元400还包含比较器部分404。比较器部分404可以将信号Q和QF与信号X_Compare和XF_Compare进行比较。信号X_Compare可以表示提供给比较器部分404的外部位的逻辑电平。如果信号Q与信号X_Compare之间(并且因此QF与XF_Compare之间)不存在匹配,则比较器部分404可以将BitMatch信号的状态从第一逻辑电平(例如,高逻辑电平)改变为第二逻辑电平(例如,低逻辑电平)。例如,如果所存储位和外部位不匹配,则比较器部分404可以将接地电压VSS耦合到承载信号BitMatch的信号线。在一些实施例中,如果所存储位与外部位之间存在匹配,则比较器部分404可以不进行任何动作。在一些实施例中,可以在比较操作之前将信号BitMatch预先充电到与高逻辑电平相关联的电压(例如,VPERI)。

比较器部分包含第七晶体管412、第八晶体管413、第九晶体管414和第十晶体管415。第七晶体管412包含耦合到信号BitMatch的漏极、耦合到节点417(例如,信号Q)的栅极和耦合到第九晶体管414的漏极的源极。第九晶体管414还具有耦合到信号XF_Compare的栅极和耦合到提供接地电压VSS的信号线的源极。

第八晶体管413具有耦合到信号BitMatch的漏极、耦合到节点419(例如,信号QF)的栅极和耦合到第十晶体管415的漏极的源极。第十晶体管具有耦合到信号X_Compare的栅极和耦合到接地电压VSS的源极。

因为信号Q与信号QF互补,所以比较器部分402可以通过以下进行操作:将外部信号X_Compare与信号QF进行比较以观察所述信号是否匹配,并且将反相外部信号XF_Compare与所存储信号Q进行比较以观察所述信号是否匹配。如果所述信号不匹配,则这可以指示信号X_Compare与信号Q不匹配并且信号XF_Compare与信号QF不匹配,并且因此外部位与相关联的所存储位不匹配。

比较器部分404可以使用相对少的组件,因为所述比较器部分将信号BitMatch从已知状态(例如,预先充电的高逻辑电平)改变为低逻辑电平。因此,可以不需要包含另外的组件(例如,另外的晶体管)来将信号BitMatch的逻辑电平从低改变为高,或从未知电平改变为低或高。比较器部分404可以利用这一点来提供动态逻辑。例如,比较器部分404具有两个部分(例如,晶体管412/414和晶体管414/415),如果所存储位与外部位之间不存在匹配,则所述两个部分中的任一部分可以将信号BitLine耦合到电压VSS。因为在某一时间所述部分中只有一个部分有效,所以只有信号Q或QF的状态需要通过有效部分进行检查。所述部分中的任一部分同样能够将信号BitMatch改变为低逻辑电平。

在示例操作中,如果所存储信号Q处于高逻辑电平(并且因此信号QF为低)并且外部信号X_Compare也为高(并且信号XF_Compare为低),则外部信号可以与所存储信号匹配,并且晶体管412和415可以在晶体管414和413无效时有效。这可以阻止接地电压VSS耦合到信号BitMatch。如果信号X_Compare为低(例如,如果不存在匹配),则外部信号可以与所存储信号不匹配,并且晶体管412和414可以在晶体管413和415无效时有效。同时有效的晶体管412和414可以将接地电压VSS耦合到信号BitMatch。

在另一示例操作中,如果所存储信号Q为低(并且因此信号QF为高),则晶体管412可以在晶体管413有效时无效。如果外部信号X_Compare为低(并且XF_Compare为高),则外部信号可以与所存储位匹配,并且晶体管414在晶体管415无效时有效。如果信号X_Compare为高(并且信号XF_Compare为低),则外部信号可以与所存储位不匹配并且晶体管414可以在晶体管415有效时无效。因此,信号BitMatch可以通过有效晶体管413和415耦合到接地电压VSS。

在一些实施例中,比较器部分404的晶体管412-415的大小通常可以全都彼此相同。在一些实施例中,比较器部分404的晶体管412-415的大小可以与锁存器部分402的晶体管406-411的大小不同。

如先前所讨论的,一条字线可以是多条攻击者字线的受害者。例如,受害者字线可能由于对受害者字线的任一侧上的相邻攻击者字线的行锤击而成为受害者。因此,受害者字线可能是两条不同的攻击者字线的受害者。在另一个实例中,受害者字线还可能由于对邻近在任一侧与受害者字线相邻的字线的攻击者字线的行锤击而成为受害者。因此,受害者字线可以是四条不同的攻击者字线的潜在受害者。然而,即使受害者字线可能由于多条字线上的并发或几乎并发(例如,同时或几乎同时)的行锤击而成为受害者,受害者字线也可能只需要“修复”(例如,刷新)一次以保持受害者字线中的数据。此外,如果在存储器操作期间,如在读取或写入操作期间对受害者字线进行存取,则存取可以修复受害者字线。

如参考图3所描述的,被存取行地址和与被存取字线的受害者字线相对应的受害者标志一起存储在堆栈中。因为受害者字线可能是多条被存取字线的受害者,所以堆栈可以包含对应于同一受害者字线的多个受害者标志。例如,在受害者字线的任一侧物理上相邻的被存取字线的行地址两者都将具有对应于存储在堆栈中的受害者字线的受害者标志。当确定行地址中的一个行地址是攻击者行时,可以刷新受害者字线并且可以复位其与所述行地址相关联的受害者标志。然而,如果确定行地址中的另一个行地址也是攻击者行,则可以再次刷新受害者字线并且可以复位其与另一个行地址相关联的受害者标志。在一些情况下,因为由于第一受害者行而最近刷新了受害者行,所以对受害者行的二次刷新可能是不必要的。

存储在堆栈(如图3中的堆栈310)中的受害者数据可以仅反映受到目标刷新操作的影响的受害者字线的数据。如果在存储器操作或自动刷新操作期间对受害者字线进行存取,则可以不复位堆栈中的受害者标志,因为对受害者字线的存取与来自堆栈的匹配地址HitXADD不相关联。因此,可以在由于受害者字线与存储在堆栈中的一或多个行地址通过受害者标志的关联性而被存取之后刷新被存取受害者字线。类似于上文,在已经对受害者字线进行存取之后对受害者字线进行的这些随后的刷新对于保持受害者行中的数据而言可能是不必要的。

图5是根据本公开的实施例的反向加扰器500和攻击者行检测器504的一部分的框图。在一些实施例中,反向加扰器500可以包含在图2中所示出的反向加扰器246中。攻击者行检测器504的所述部分可以包含在图3中的攻击者行检测器300和/或图2中所示出的攻击者行检测器230中。在一些实施例中,反向加扰器500可以通过基于对受害者字线的刷新和/或存取调整与受害者字线(例如,受害者标志)相关联的数据来减少对受害者字线的不必要刷新。

反向加扰器500可以接收行地址XADD和/或刷新地址RXADD。在一些实施例中,行地址XADD可以从地址解码器电路(如图1中所示出的地址解码器电路104)接收。在一些实施例中,刷新地址可以从刷新地址发生器(如图2中所示出的刷新地址发生器232)接收。在一些实施例中,反向加扰器500可以具有一或多个攻击者行地址发生器502。在一些实施例中,攻击者行地址发生器502的数量可以基于要针对与行地址XADD和/或刷新地址RXADD相关联的受害者字线确定的攻击者字线的数量。在未在图5中示出的一些实施例中,反向加扰器500可以包含两组攻击者行地址发生器502。一组可以接收刷新地址RXADD并且另一组可以接收行地址XADD。

每个攻击者行地址发生器502可以确定与和刷新地址RXADD和/或行地址XADD相关联的受害者字线具有不同的物理关系的一条攻击者字线的行地址(AXADD0-3)。在图5中所示出的实例中,反向加扰器500包含四个用于计算受害者字线的R+/-1和R+/-2攻击者字线的行地址的攻击者行地址发生器502。在其它实例中,可以包含更多或更少的攻击者行地址发生器502。在一些实施例中,所生成的攻击者行地址的数量可以基于地址加扰器(如图2中所示出的地址加扰器238)生成的受害者行的数量。例如,如果地址加扰器计算受害者行地址R+/-1和R+/-2,则攻击者行地址发生器502可以计算攻击者行地址R+/-1和R+/-2。

攻击者行地址发生器502可以以各种方式确定攻击者行地址。例如,在一些实施例中,攻击者行发生器502可以参考查找表以确定与行地址XADD和/或刷新地址RXADD相关联的攻击者行地址。在另一个实例中,在一些实施例中,攻击者行发生器502可以包含用于执行受害者行地址与攻击者行地址之间的转换的逻辑门或其它电路组件。转换可以基于存储器的设计中物理字线位置与行地址之间的关系。每个攻击者行地址发生器502可以输出攻击者行地址AXADD0-3。在一些实施例中,可以如图5所示在单独的输出线上提供攻击者行地址。在其它实施例中,可以在单条输出线上串行地提供攻击者行地址。尽管图5中示出为四个单独的模块,但是在一些实施例中,攻击者行地址发生器502可以是能够计算所有四个攻击者行地址并且在单独的输出线或单条输出线上提供攻击者行地址的单个组件。

可以向攻击者行检测器电路504提供反向加扰器500计算的所有攻击者行地址AXADD0-3。具体地,可以将攻击者行地址AXADD0-3与存储在堆栈的地址字段506中的行地址进行比较。在一些实施例中,可以顺序(例如,串行)地将每个攻击者行地址AXADD0-3与存储在地址字段506中的行地址进行比较。在其它实施例中,可以同时(例如,并行)地将所有攻击者行地址与存储在地址字段506中的行地址进行比较。如果攻击者行地址AXADD0-3与地址字段506中的所存储行地址之间不存在匹配,则攻击者行检测器504不会采取进一步的行动。如果攻击者行地址AXADD0-3中的一或多个攻击者行地址与地址字段506中的一或多个行地址之间存在图5中示出为MatchADD的匹配,则激活匹配信号Match0-3并且将所述匹配信号提供给受害者数据逻辑电路508。为了简单起见,在图5中所示出的实例中,仅示出了一个匹配地址MatchADD。然而,如所提及的,多个攻击者行可以在地址字段506中具有多个匹配。

尽管图5中示出为单条线,但是匹配信号Match0-3可以在单独的线上传输。例如,用于匹配信号Match0、Match1、Match2和Match3的单独的线。每个匹配信号可以对应于特定的攻击者行地址。例如,Match0可以对应于AXADD0,Match1可以对应于AXADD1等。当攻击者行地址AXADD0-3与行地址MatchADD匹配时,可以激活对应的匹配信号。例如,如果AXADD2与MatchADD匹配,则可以激活Match2。在一些实施例中,信号Reg0-N可以提供对堆栈中的哪个寄存器包含匹配地址MatchADD的指示,可以提供给受害者数据逻辑电路508。在一些实施例中,可以在单独的线上提供信号Reg0-N和匹配信号Match0-3。在其它实施例中,可以在同一条线上提供所述指示和与有效信号串行的对应匹配信号。

响应于有效匹配信号和寄存器指示,受害者数据逻辑电路508可以调整受害者数据以指示对应的受害者字线已经修复。例如,受害者数据逻辑电路508可以将存储在与行地址MatchADD相关联的受害者标志字段510中的合适的受害者标志V0-3设置成已修复状态(例如,复位、设置成第二状态)。继续以上实例,当受害者数据逻辑电路508接收到有效Match2信号时,受害者数据逻辑电路508可以将存储在受害者标志字段510中的受害者标志V2设置成已修复状态。例如,如果受害者标志V2是指示与受害者标志相关联的字线尚未修复的“1”,则受害者数据逻辑电路508可以将受害者标志V2改变为指示与受害者标志相关联的字线已经修复的“0”。因此,在一些实施例中,在对与RXADD或XADD相对应的字线进行刷新或存取时,可以调整与攻击者行检测器504中的字线相关联的所有受害者标志以指示字线中的数据已经修复。在一些实施例中,这可以减少对与RXADD和XADD相对应的字线的不必要刷新。

虽然图2、3和5中所描述的实例将所存储的受害者数据称作包含一或多个位的受害者标志,但是可以使用其它形式的受害者数据。例如,可以使用的不同的数值来指示与每个所存储行地址相关联的受害者字线的已修复或未修复状态。

图6是根据本公开的实施例的方法的流程图600。在框602处,可以执行“将行地址存储在寄存器中”的步骤。在一些实施例中,行地址可以是与存储器存取操作一起接收的地址。寄存器可以包含在刷新控制电路中,如图1中的刷新控制电路116和/或图2中所示出的刷新控制电路216。在框604处,可以执行“将受害者数据设置成第一值”的步骤。在一些实施例中,受害者数据可以与寄存器中的行地址相关联。在一些实施例中,受害者数据可以与对应于行地址的字线的受害者字线相关联。

在框606处,可以执行“计算至少一个攻击者行地址”的步骤。在一些实施例中,攻击者行地址可以基于刷新地址或被存取行地址。在一些实施例中,刷新地址可以由刷新地址发生器(如图2的刷新地址发生器232)提供。在框608处,可以执行“将行地址与至少一个攻击者行地址进行比较”的步骤。在一些实施例中,比较可以由攻击者行检测器电路执行,如图2中所示出的攻击者行检测器电路230、图3中所示出的攻击者行检测器电路300和/或图5中所示出的攻击者行检测器电路504的一部分。在框610处,如果行地址与至少一个攻击者行地址匹配,则可以执行“将受害者数据设置成第二值”的步骤。在一些实施例中,设置可以由受害者数据逻辑电路执行,如图3中所示出的受害者数据逻辑电路318和/或图5中所示出的受害者数据逻辑电路508。在一些实施例中,受害者数据包括多个位。在这些实施例中,每个位可以对应于与行地址相关联的字线的受害者字线。在一些实施例中,如果行地址与攻击者地址不匹配,则可以不执行行动。

在一些实施例中,在流程图600中所示出的方法可以进一步包含存储与寄存器中的行地址相关联的计数值。在一些实施例中,寄存器可以包含在堆栈中,如图3中所示出的堆栈310。在一些实施例中,所述方法可以包含每次接收到被存取行地址时,调整计数值。在一些实施例中,当计数值达到阈值时,所述方法可以进一步包含计算在受害者数据被设置成第一值时的至少一个受害者行地址。在一些实施例中,所述方法可以进一步包含在目标刷新操作期间刷新至少一个受害者行地址。在一些实施例中,所述方法可以进一步包含将受害者数据设置成第二值和/或复位计数值。

在一些实施例中,一种方法可以包含将自动刷新地址或被存取行地址与存储在队列中的一或多个受害者行地址进行比较。如果所述自动刷新地址或被存取行地址与所述一或多个受害者行地址不匹配,则不采取行动。如果所述自动刷新地址或被存取行地址与所述一或多个受害者行地址匹配,则将匹配的一或多个受害者行地址从所述队列中移除。

本文中所描述的设备和方法可以允许调整与被存取行地址相关联的受害者字线数据。例如,可以调整受害者字线数据以指示受害者字线已经修复。本文中所描述的调整受害者字线数据可以减少一些应用中的不必要的刷新操作的数量。

当然,应当了解,本文中所描述的实例、实施例或过程中的任何一个可以与一或多个其它实例、实施例和/或过程组合,或者根据本发明系统、装置和方法在单独的装置或装置部分之间分离和/或执行。

最后,以上讨论旨在仅仅说明本发明系统并且不应当被解释为将所附权利要求限制于任何特定实施例或实施例组。因此,虽然已经参考示范性实施例特别详细地描述了本发明系统,但是还应当了解,本领域的技术人员可以在不脱离如以下权利要求中所阐述的本发明系统的更广泛的和预期的精神和范围的情况下设计出各种修改和替代性实施例。因此,说明书和附图应以说明性方式来看待并且不旨在限制所附权利要求的范围。