SRAM的存储单元结构及阵列结构

文献发布时间:2023-06-19 09:30:39

技术领域

本发明涉及半导体集成电路,特别是涉及一种SRAM的存储单元结构;本发明还涉及SRAM的阵列结构。

背景技术

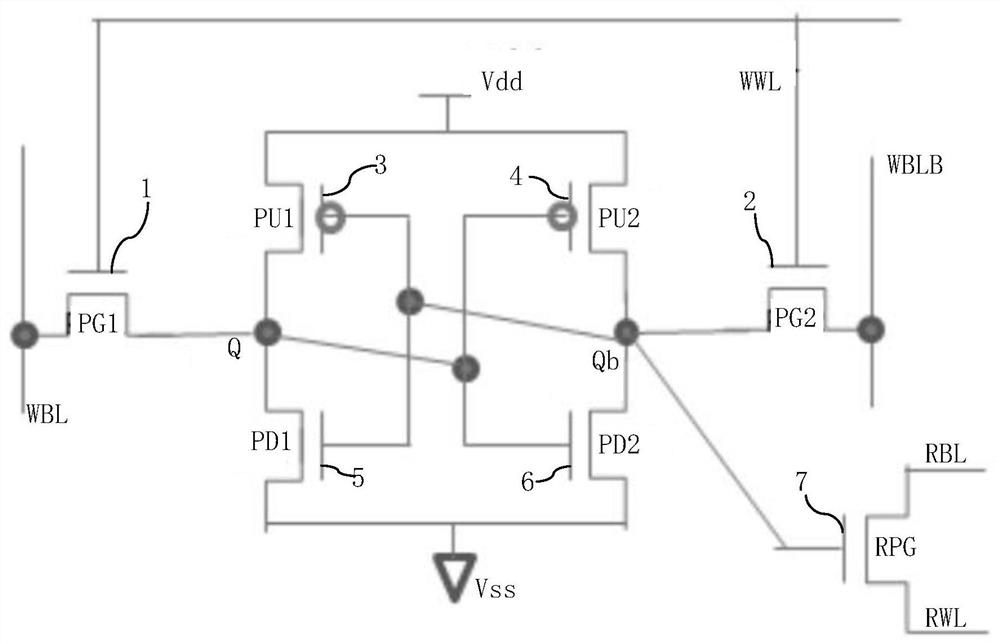

目前工业界普遍应用的读写分离SRAM电路,现有读写分离SRAM电路通常采用图1所示的8T2P型SRAM的存储单元,其中8T表示存储单元中有8个晶体管,2P表示有两个端口(port)即写端口(write port)和读端口(read port)。由图1所示可知,现有8T2P型SRAM的存储单元包括由选择晶体管101和102,P型上拉管103和104以及N型下拉管105和106组成写端口电路,图1中,选择晶体管101也用PG1表示,选择晶体管102也用PG2表示,P型上拉管103也用PU1表示,P型上拉管104也用PU2表示,N型下拉管105也用PD1表示,N型下拉管106也用PD2表示。可以看出,写端口电路为一传统的6T-SRAM存储单元。其中,P型上拉管103和N型下拉管105组成CMOS反相器,P型上拉管104和N型下拉管106也组成CMOS反相器,两个CMOS反相器首尾相连形成锁存器,锁存器包括两个互为反相且互锁的第一存储节点Q和所述第二存储节点Qb。P型上拉管103和104的源极都连接电源电压Vdd,N型下拉管105和106的源极都接地Vss,选择晶体管101和102的栅极都连接写字线WWL,在写字线WWL的控制下,选择晶体管101使第一存储节点Q和第一写位线WBL之间的连接和断开,选择晶体管102使第二存储节点Qb和第二写位线WBLB之间的连接和断开。

写端口电路能实现单独写操作。图1中还包括用于进行单独读操作的读端口电路,图1中的读端口电路包括两个NMOS管,分别为读选择管107和读下拉管108,图1中,读选择管107也用RPG表示,读下拉管108也用RPD表示。读下拉管108的栅极接第二存储节点Qb,源极接地Vss。读下拉管108的漏极连接读选择管107的源极,选择管107的漏极连接读位线RBL。

图1所示的电路中,在进行读操作时,读字线RWL接高电平如Vdd,读选择管107会打开;读位线RBL也接高电平,这样,第二存储节点Qb上存储的信息不同时,读下拉管108的导通状态不同,读下拉管108导通时,读位线RBL的电位会下降;读下拉管108断开时,读位线RBL的电位会保持为高电平。

而在写操作以及待机时,读字线RWL接低电平如接地Vss,这时,读选择管107断开,读位线RBL上的高电平并不会对第一存储节点Q和第二存储节点Qb产生不利影响。最后能提高电路的静态噪声容限(SNW)和写入余量(WM)。相反,如果在读位线RBL为高电平时,没有设置读选择管107,则读位线RBL的高电平容易对第一存储节点Q和第二存储节点Qb产生干扰,从而会降低SNW和WM。也即现有SRAM中,必须要采用图1所示的两个NMOS即读选择管107和读下拉管108,才能取得较好的SNW和WM。

图1所示的现有电路中,在各种操作下的端口设置如表一所示:

表一

表一中,Read表示读操作,Write表示写操作,Standby表示待机;

RBL表示读位线,RWL表示读字线,WWL表示写字线,WBL表示第一写位线、WBLB表示第二写位线。Vdd表示电源电压,表一中的高电平都取Vdd。Gnd表地即Vss。

随着技术的不断发展,希望芯片的尺寸越来越小,图1所示的SRAM的存储单元中包括了8个晶体管,这会增加电路的面积。如图2所示,是图1所示的存储单元的版图;图2中显示了同一行两个相邻列的存储单元,两个存储单元分别用虚线框201a和201b框出,存储单元201a和201b的呈左右对称结构。图1中各晶体管在图2中都用对应的虚线框标出。图2所示的版图显示了4个层次,分别为:有源区202,多晶硅栅203,接触孔204和第一层金属层图形205。图2中,同一个存储单元中包括了5个有源区,其中,读选择管107和读下拉管108形成在同一个有源区202,选择晶体管101和N型下拉管105位于同一个有源区202中,P型上拉管103和104分别位于单独的有源区中,选择晶体管102和N型下拉管106位于同一个有源区202中。

各晶体管包括了由多晶硅组成的多晶硅栅203和形成于多晶硅栅203两侧的有源区中的源区和漏区,多晶硅栅203、源区和漏区的顶部通过对应的接触孔204连接到对应的第一层金属层图形205。

由图2所示可知,读选择管107和读下拉管108需要单独占用一个有源区202,最后会增加电路面积。所以,图1所示的现有8T2P型SRAM和现有6T-SRAM相比,虽然能有效的提高SNM以及WM,但是对电路面积减少不利。

发明内容

本发明所要解决的技术问题是提供一种SRAM的存储单元结构,能实现读写分离,且能在保持电路具有较好的SNW和WM性能的条件下使读端口的晶体管数量最少,从而节约电路面积。为此,本发明还公开了一种SRAM的阵列结构。

为解决上述技术问题,本发明提供的SRAM的存储单元结构,其特征在于,存储单元包括:主体电路,写端口电路和读端口电路。

所述主体电路包括一对互为反相且互相锁存的第一存储节点和所述第二存储节点。

所述读端口电路包括第一MOS晶体管,所述第一MOS晶体管的栅极连接所述第一存储节点和所述第二存储节点中的一个,所述第一MOS晶体管的第一源漏区连接读位线,所述第一MOS晶体管的第二源漏区连接读字线。

所述存储单元的操作包括写操作、读操作和待机。

在读操作过程中,所述读位线为低电平,所述读字线为高电平。

在写操作和待机的过程中,所述读位线和所述读字线都保持为低电平,以消除所述读位线和所述读字线通过所述第一MOS晶体管对所述主体电路产生干扰,提高SRAM的静态噪声容限和写入余量。

进一步改进是,所述主体电路由第一CMOS反相器和第二CMOS反相器连接而成,所述第一CMOS反相器的输出端和所述第二CMOS反相器的输入端连接在一起并作为所述第二存储节点,所述第二CMOS反相器的输出端和所述第一CMOS反相器的输入端连接在一起并作为所述第一存储节点。

进一步改进是,所述写端口电路包括第一选择管和第二选择管。

所述第一选择管的栅极和所述第二选择管的栅极都连接到写字线。

所述第一选择管的第一源漏区连接第一写位线、所述第一选择管的第二源漏区连接所述第一存储节点。

所述第二选择管的第一源漏区连接第二写位线、所述第一选择管的第二源漏区连接所述第二存储节点。

进一步改进是,所述主体电路和所述写端口电路组成6T电路。

所述第一CMOS反相器由第一PMOS上拉管和第一NMOS下拉管组成。

所述第二CMOS反相器由第二PMOS上拉管和第二NMOS下拉管组成。

所述第一选择管和所述第二选择管都为NMOS管。

进一步改进是,所述主体电路、所述写端口电路和所述读端口电路组成7T电路。

进一步改进是,所述第一MOS晶体管为NMOS管;

或者,所述第一MOS晶体管为PMOS管。

为解决上述技术问题,本发明提供的SRAM的阵列结构由上述存储单元行列排列而成。

同一行中,相邻两列的所述存储单元的读端口电路形成在同一第一有源区中。

进一步改进是,位于同一所述第一有源区中的相邻两列的所述第一MOS晶体管的第二源漏区共用以及读字线共用。

进一步改进是,同一行的共用同一个所述第一有源区的两个相邻列的所述存储单元的版图呈以共用的所述第二源漏区的中心为对称中心的中心对称结构。

进一步改进是,所述主体电路由第一CMOS反相器和第二CMOS反相器连接而成,所述第一CMOS反相器的输出端和所述第二CMOS反相器的输入端连接在一起并作为所述第二存储节点,所述第二CMOS反相器的输出端和所述第一CMOS反相器的输入端连接在一起并作为所述第一存储节点。

进一步改进是,所述写端口电路包括第一选择管和第二选择管。

所述第一选择管的栅极和所述第二选择管的栅极都连接到写字线。

所述第一选择管的第一源漏区连接第一写位线、所述第一选择管的第二源漏区连接所述第一存储节点。

所述第二选择管的第一源漏区连接第二写位线、所述第一选择管的第二源漏区连接所述第二存储节点。

进一步改进是,所述主体电路和所述写端口电路组成6T电路。

所述第一CMOS反相器由第一PMOS上拉管和第一NMOS下拉管组成。

所述第二CMOS反相器由第二PMOS上拉管和第二NMOS下拉管组成。

所述第一选择管和所述第二选择管都为NMOS管。

进一步改进是,所述主体电路、所述写端口电路和所述读端口电路组成7T电路。

进一步改进是,所述第一MOS晶体管为NMOS管;

或者,所述第一MOS晶体管为PMOS管。

进一步改进是,同一行的所述写字线都连接在一起,同一列的所述第一写位线都连接在一起,同一列的所述第二写位线都连接在一起。

和现有8T2P型SRAM存储单元不同,本发明SRAM的存储单元的读端口进一步减少了一个MOS晶体管,而采用一个第一MOS晶体管即可实现,同时,为了避免图1所示的现有结构中,读位线BL直接读下拉管108的漏极时所产生的对存储单元的SNW和WM的不利影响,本发明还对第一MOS晶体管和读位线和读字线的连接关系做了特别的设置,将第一MOS晶体管的第一源漏区连接读位线以及将第一MOS晶体管的第二源漏区连接读字线,且对读位线和读字线在写操作、读操作和待机的过程中的电压进行了设置,本发明对读位线和读字线能保证实现读操作的同时,使读位线和读字线在写操作和待机的过程中都保持为低电平,从而能使存储单元依然具有较好的SNW和WM的性能;也即本发明能采用一个晶体管作为读端口即可实现现有8T2P型SRAM存储单元中采用2个晶体管相同的SNW和WM性能改善效果,但是本发明能节约一个晶体管,故最后会减少电路面积。

附图说明

下面结合附图和具体实施方式对本发明作进一步详细的说明:

图1是现有8T2P型SRAM的存储单元的电路图;

图2是图1所示的存储单元的版图;

图3是本发明实施例SRAM的存储单元的电路图;

图4是图3所示的存储单元的版图。

具体实施方式

如图3所示,是本发明实施例SRAM的存储单元的电路图;本发明SRAM的存储单元结构包括:主体电路,写端口电路和读端口电路。

所述主体电路包括一对互为反相且互相锁存的第一存储节点Q和第二存储节点Qb。

所述读端口电路包括第一MOS晶体管7,所述第一MOS晶体管7的栅极连接所述第一存储节点Q和所述第二存储节点Qb中的一个,所述第一MOS晶体管7的第一源漏区连接读位线RBL,所述第一MOS晶体管7的第二源漏区连接读字线RWL。

所述存储单元的操作包括写操作、读操作和待机。

在读操作过程中,所述读位线RBL为低电平,所述读字线RWL为高电平。

在写操作和待机的过程中,所述读位线RBL和所述读字线RWL都保持为低电平,以消除所述读位线RBL和所述读字线RWL通过所述第一MOS晶体管7对所述主体电路产生干扰,提高SRAM的静态噪声容限和写入余量。

本发明实施例中,所述主体电路由第一CMOS反相器和第二CMOS反相器连接而成,所述第一CMOS反相器的输出端和所述第二CMOS反相器的输入端连接在一起并作为所述第二存储节点Qb,所述第二CMOS反相器的输出端和所述第一CMOS反相器的输入端连接在一起并作为所述第一存储节点Q。

所述写端口电路包括第一选择管1和第二选择管2。

所述第一选择管1的栅极和所述第二选择管2的栅极都连接到写字线WWL。

所述第一选择管1的第一源漏区连接第一写位线WBL、所述第一选择管1的第二源漏区连接所述第一存储节点Q。

所述第二选择管2的第一源漏区连接第二写位线WBLB、所述第一选择管1的第二源漏区连接所述第二存储节点Qb。

所述主体电路和所述写端口电路组成6T电路。

所述第一CMOS反相器由第一PMOS上拉管3和第一NMOS下拉管5组成。

所述第二CMOS反相器由第二PMOS上拉管4和第二NMOS下拉管6组成。

所述第一选择管1和所述第二选择管2都为NMOS管。

所述主体电路、所述写端口电路和所述读端口电路组成7T电路。

本发明实施例中,所述第一MOS晶体管7为NMOS管。在其他实施例中也能为:所述第一MOS晶体管7为PMOS管。

本发明实施例SRAM的阵列结构由本发明实施例的存储单元行列排列而成。

同一行中,相邻两列的所述存储单元的读端口电路形成在同一第一有源区中。

位于同一所述第一有源区中的相邻两列的所述第一MOS晶体管7的第二源漏区共用以及读字线RWL共用。

同一行的共用同一个所述第一有源区的两个相邻列的所述存储单元的版图呈以共用的所述第二源漏区的中心为对称中心的中心对称结构。

同一行的所述写字线WWL都连接在一起,同一列的所述第一写位线WBL都连接在一起,同一列的所述第二写位线WBLB都连接在一起。

和图1所示的现有8T2P型SRAM存储单元不同,本发明实施例SRAM存储单元为7T2P型,能实现读端口和写端口分离的同时,还能减少一个晶体管,故能减少面积,同时,本发明实施例SRAM存储单元通过进行端口的电压设置,还能使SNW和WM的性能和现有8T2P型SRAM存储单元相同。

图3所示的本发明实施例SRAM存储单元中,在各种操作下的端口设置如表二所示:

表二

和表一比较可知,本发明实施例中的RBL始终都接低电平即接地,和表一中的RBL的设置正好相反,其他端口的设置相同。可见,本发明实施例仅需对RBL的电压设置为低电平,就能得到和图1所示现有电路相同的SNW和WM的性能。

本发明实施例SRAM的存储单元的读端口电路由于减少了一个晶体管,故能减少电路面积。如图4所示,是图3所示的存储单元的版图;图4中显示了同一行两个相邻列的存储单元,两个存储单元分别用虚线框301a和301b框出,存储单元301a和301b的呈中心对称结构。图3中各晶体管在图4中都用对应的虚线框标出。图4所示的版图显示了4个层次,分别为:有源区302,多晶硅栅303,接触孔304和第一层金属层图形305,图4中,在两个所述存储单元301a和301b的左侧了显示了4个层次对应的表述符号,有源区302还用AA表示,多晶硅栅303还用PO表示,接触孔304还用Contact表示,第一层金属层图形305还用M1表示。图4中,同一个存储单元中包括了4.5个有源区,其中,相邻两个所述存储单元301a和301b的第一MOS晶体管7共用同一个有源区,故平均下来一个所述存储单元中的第一MOS晶体管7仅占用0.5个有源区;第一选择管1和第一NMOS下拉管5位于同一个有源区302中,第一PMOS上拉管3和第二PMOS上拉管4分别位于单独的有源区中,第二选择管2和第二NMOS下拉管6位于同一个有源区302中。

各晶体管包括了由多晶硅组成的多晶硅栅303和形成于多晶硅栅303两侧的有源区中的源区和漏区,多晶硅栅303、源区和漏区的顶部通过对应的接触孔304连接到对应的第一层金属层图形305。

和图2比较可知,图4对应的本发明实施例版图中,平均下来一个所述存储单元的第一MOS晶体管7仅占用0.5个有源区302,所以会减少电路面积。同时,本发明实施例还能有效的提高SNM以及WM。

和现有8T2P型SRAM存储单元不同,本发明SRAM的存储单元的读端口进一步减少了一个MOS晶体管,而采用一个第一MOS晶体管7即可实现,同时,为了避免图1所示的现有结构中,读位线RBLBL直接读下拉管108的漏极时所产生的对存储单元的SNW和WM的不利影响,本发明还对第一MOS晶体管7和读位线RBL和读字线RWL的连接关系做了特别的设置,将第一MOS晶体管7的第一源漏区连接读位线RBL以及将第一MOS晶体管7的第二源漏区连接读字线RWL,且对读位线RBL和读字线RWL在写操作、读操作和待机的过程中的电压进行了设置,本发明对读位线RBL和读字线RWL能保证实现读操作的同时,使读位线RBL和读字线RWL在写操作和待机的过程中都保持为低电平,从而能使存储单元依然具有较好的SNW和WM的性能;也即本发明能采用一个晶体管作为读端口即可实现现有8T2P型SRAM存储单元中采用2个晶体管相同的SNW和WM性能改善效果,但是本发明能节约一个晶体管,故最后会减少电路面积。

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。