多层单元非易失性存储器的一种编程方法

文献发布时间:2023-06-19 09:30:39

技术领域

本发明涉及集成电路领域,尤其涉及一种多层单元非易失性存储器。

背景技术

非易失性存储器,如浮栅型闪存(Floating Gate Flash)、电荷捕获型闪存(Charge Trap Flash)、相变存储器(Phase Change Memory)和电阻型随机存取器(Resistive RAM)等,都使用模拟信号的存储单元来保存数据。每个模拟信号存储单元可以保存一个模拟信号,如电荷、电压或者电阻。对多层存储单元,模拟信号的允许取值范围可以分成多个区域,每个区域定义了一个单元状态,每个状态表示多个数据比特的取值。后文中,我们将该模拟信号称为状态模拟信号。每个存储单元状态都对应多个比特的一个取值,我们称之为“状态编码”。文献中,多层存储单元也常称为多状态存储单元或者多比特存储单元。

比如,SLC NAND闪存中每个单元可存储1个比特,而多层单元NAND闪存的一个单元可以存储多个比特。其中,MLC NAND闪存中每个单元可存储2个比特,TLC NAND闪存中每个单元可存储3个比特,QLC NAND闪存中每个单元可存储4个比特。

从模拟存储单元读取数据是通过感测(sensing)存储单元的状态来完成,感测是基于把存储单元的状态模拟信号与一个或多个参考阈值进行比较,从而确定单元状态。

一个模拟存储单元的数据写入是通过编程(program)操作,把该单元的状态模拟信号的值调整到一个与指定的写入数值对应的信号标称值来完成的。对存储单元的编程过程如图1,包括:通过编程脉冲步骤(program pulse step)改变待编程单元的状态;对每个待编程单元通过感测操作进行校验,检查每个待编程单元的状态是否达到与待写入数据对应的目标状态;对于已经达到目标状态的待编程单元进行编程抑制(program inhibit);循环执行以上步骤直到所有单元达到其目标状态或循环次数达到预设上限。在每次编程脉冲步骤中,在未被编程抑制的所有待编程单元上施加编程脉冲的时间相同。

NAND闪存是一种广泛使用的非易失性存储器。关于NAND闪存的基本原理、感测电路和编程电路,在书籍Rino Micheloni,Luca Crippa,Alessia Marelli(2010)“InsideNAND Flash Mem-ories”New York:Springer Science+Business Media中有详细的论述。该书籍中相关章节通过引入的方式并入本文本中。

NAND闪存单元的数据读写操作的原理如下。对于一个存储了n个比特的NAND闪存单元,其可能的阈值电压的范围,(V

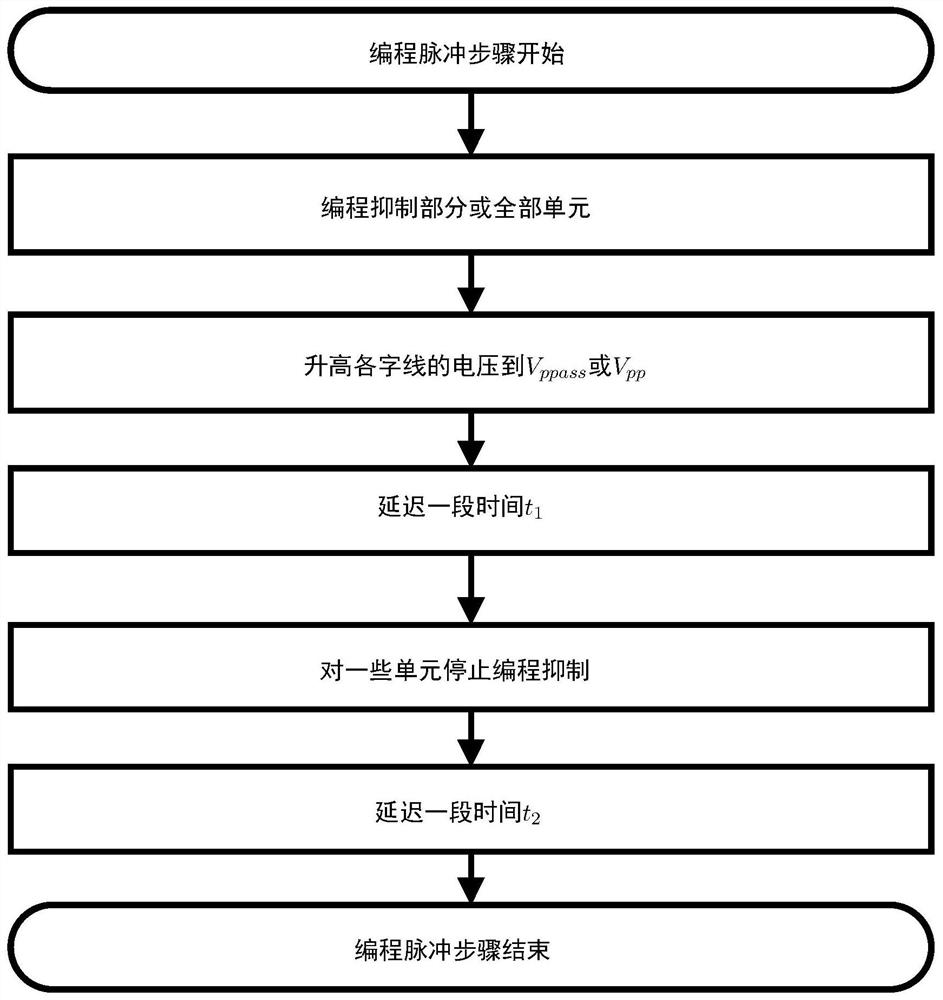

NAND的块的结构如图2。编程脉冲步骤的流程如图7所示。图8示例了块200中各点电压在一次编程脉冲步骤中的变化情况。其中,字线2是被编程字线;位线1所对应的待编程单元已达到目标状态并被编程抑制;位线2、3所对应的待编程单元尚未达到目标状态,未被编程抑制。为方便叙述,我们称与被编程抑制的待编程单元所在的NAND串处于抑制状态,与未被编程抑制的待编程单元所在的NAND串处于编程状态。

上述编程脉冲步骤的原理具体如下。根据MOS管的特性,各NAND串中的M

由于待写入的数据的值不同,各个被编程单元的目标阈值电压不同。在一次编程脉冲步骤中,各个被编程单元的阈值电压将升高,而阈值电压的增加幅度的期望值近似相同。为了防止过编程(over-program),一次编程脉冲步骤应该使各个被编程的单元的阈值电压的增加幅度不超过一个阈值电压区间的大小,即每个编程单元在一个编程脉冲步骤前、后的阈值电压必须位于相同或相邻的阈值电压区间。否则,可能使得单元的阈值电压高于期望阈值电压区间的上限,并导致编程错误。因此,一个编程操作所需编程脉冲步骤的循环次数近似与阈值电压区间的个数成正比。

在不考虑工艺变化及参数优化等其它条件的情况下,随着每单元比特数的增加,闪存的编程操作中的编程脉冲步骤的循环次数近似与阈值电压区间的个数成正比,即随着每单元比特数的增加而指数级增长。另外,随着每单元比特数的增加,阈值电压区间变窄。为了优化编程精度,编程脉冲步骤的循环次数将可能进一步增加。编程脉冲步骤的总循环次数的大幅增加,将导致编程性能的严重下降。

发明内容

针对现有技术中存在的问题,本发明的一些实施例提供了多层单元非易失性存储器的一种编程方法,具体如下:

通过编程脉冲步骤改变待编程单元的状态模拟信号;

对每个待编程单元进行校验,检查其状态是否达到目标状态;

对于已经达到目标状态的待编程单元进行完全地编程抑制;

对于未达到目标状态的待编程单元,根据其目标状态或者当前状态及目标状态,进行部分地编程抑制或完全地编程抑制,以调整其有效编程脉冲时间;

循环执行以上步骤直到所有单元达到其目标状态或循环次数达到预设上限。

本发明的进一步的一些实施例提供了多层单元闪存的一种编程方法,其中编程脉冲步骤具体如下:

将所有待编程单元的位线电压升高至第一电压,使得所有待编程单元进入编程抑制状态;

升高待编程单元所在块的所有栅极电压至第二电压;

然后升高待编程单元所在字线的栅极电压至第三电压;

对每个待编程单元,在各自延迟第一时间后,将其位线电压降低至第四电压;

在所述第三电压升高之后延迟第二时间,编程脉冲步骤结束,降低各栅极电压和位线电压至编程脉冲步骤开始前的状态。

在一些实施例中,上述方案中每个待编程单元的所述第一时间由该待编程单元的目标状态或目标状态和当前状态来确定。不同待编程单元的第一时间可以不同。在同一编程脉冲步骤中,目标状态与初始状态或当前状态差别越大的单元的第一时间越短。

在一些实施例中,上述方案中所述待编程单元的有效编程脉冲时间或第二时间与编程脉冲过程中编程电压的持续时间的比值与单元的目标阈值电压与初始阈值电压或擦除状态阈值电压的差成正比。

在一些实施例中,上述方案中所述待编程单元的有效编程脉冲时间或第二时间与编程脉冲过程中编程电压的持续时间的比值与单元的目标阈值电压与当前阈值电压的差成正比。

在一些实施例中,上述方案中所述编程脉冲步骤的第三电压随着循环次数的增加可以变化或不变。

在一些实施例中,上述方案中所述编程脉冲步骤的第一时间随着循环次数的增加可以变化或不变。

在一些实施例中,上述方案中所述编程脉冲步骤的编程电压持续时间随着循环次数的增加可以变化或不变。

在一些实施例中,上述方案中所述编程脉冲步骤的编程电压持续时间和第三电压随着循环次数的增加递减。

附图说明

图1示例了非易失性存储器的编程过程的流程图。

图2示例了NAND闪存的一个块中与编程相关的电路。

图3为SLC NAND闪存中阈值电压分布和参考阈值电压的示例图。

图4为MLC NAND闪存中阈值电压分布和参考阈值电压的示例图。

图5为TLC NAND闪存中阈值电压分布和参考阈值电压的示例图。

图6为QLC NAND闪存中阈值电压分布和参考阈值电压的示例图。

图7示例了现有技术方案中编程脉冲步骤的流程图。

图8示例了现有多层单元闪存的一个编程脉冲步骤中各个电压的变化过程。

图9示例了一个编程脉冲步骤中处于抑制状态的NAND串相关的电压分布。

图10示例了本发明一些实施例的编程脉冲步骤的流程图。

图11示例了本发明一些实施例的一个编程脉冲步骤中各点电压随时间的变化关系。

图12示例了本发明一些实施例中一种可能的编程电压随时间的变化关系。

图13示例了本发明一些实施例中又一种可能的编程电压随时间的变化关系。

图14示例了本发明一些实施例中又一种可能的编程电压随时间的变化关系。

具体实施方式

在下文中,将参照附图详细描述本发明的实施例。但是实现本发明的形式不应被这里阐述的具体实施方式所限制。相反,提供这些实施方式是为了更透彻地理解本发明,并且能够将本发明公开的范围完整地传达给本领域的技术人员。

针对现有技术存在的问题,本发明一实施例提供了多层单元存储器的一种与目标状态或目标状态和当前状态相关的编程方法,具体如下。

对存储单元的编程过程如图1,包括:

通过编程脉冲步骤改变待编程单元的状态模拟信号;

对每个待编程单元进行校验,检查每个待编程单元的状态是否达到目标状态;

对于已经达到目标状态的待编程单元单元进行完全地编程抑制;

对于未达到目标状态的待编程单元,根据其目标状态或者当前状态及目标状态,进行部分地编程抑制或完全地编程抑制,以调整其编程脉冲的有效时间;

循环执行以上步骤直到所有单元达到其目标状态或循环次数达到预设上限。

待编程单元的状态模拟信号的改变主要发生在编程脉冲步骤中,状态模拟信号改变的幅度与编程脉冲步骤中有效编程时间的长短有关。在一次编程脉冲步骤中,令不同的单元具有不一定相同的有效编程时间,待编程单元的状态模拟信号改变幅度的期望也因此不同。令目标状态与当前状态或目标状态与初始状态的差别较大的单元具有较长的有效编程时间,此类单元在一次编程脉冲中状态模拟信号改变幅度的期望较大。此时,由于目标状态与当前状态或目标状态与初始状态的单元差别较小的单元具有较短的有效编程时间,此类单元在一次编程脉冲中状态改变幅度的期望较小,过编程的可能性较低。显然,这样可以减少循环次数,提高编程的效率,同时能够保持或者提高编程后状态模拟信号的精度。

本发明又一实施例给出了一种多层单元NAND闪存的的一种与目标状态或目标状态和当前状态相关的编程方法,与现有技术中多层单元闪存的编程方法相比,其特征如下。

在多层单元NAND闪存的的一种与目标状态或目标状态和当前状态相关的编程方法中的编程脉冲步骤中,各点的电压变化如图11,其中字线2是被编程字线,位线1所对应单元已达到目标状态,位线2所对应单元目标状态与当前状态或目标状态与初始状态差别较小,位线3所对应单元目标状态与当前状态或目标状态与初始状态差别较大。

上述编程脉冲步骤的原理具体如下。位线1与位线3的电压变化与现有技术中相同,参照前文所述,位线1所对应的NAND串始终处于抑制状态,位线3所对应的NAND串始终处于编程状态。位线2所对应的NAND串在T时间之前,各点电压与位线1中各点电压相同,显然位线2在T时间之前处于抑制状态,T时间时,位线2的电压降低至GND,位线2对应的NAND串中的M

在一个编程脉冲步骤中,若一个NAND串始终处于编程状态,则称该NAND串未被抑制;若一个NAND串始终处于抑制状态,则称该NAND串被完全抑制;若一个NAND串在不同的时间内分别处于编程状态和抑制状态,则称该NAND串被部分抑制。显然,被完全抑制的NAND串中位于被编程字线上的存储单元的有效编程时间为0,未被抑制的NAND串中位于被编程字线上的存储单元的有效编程时间等于编程电压V

显然,通过位线电压改变时间T的位置,我们可以改变一次编程脉冲步骤中单元的有效编程时间。参照前文所述,对目标状态与当前状态或目标状态与初始状态差别较小的单元,其位线电压改变时间T较晚,对目标状态与当前状态或目标状态与初始状态差别较大的单元,其位线电压改变时间T较早。

记存储单元的初始阈值电压为V

在不超过编程脉冲电压的持续时间的范围内,每个待编程单元的有效编程时间可根据其目标状态与其当前状态或其目标状态与初始状态来确定。本发明又一实施例给出了一种多层单元NAND闪存的编程方法,相较于现有技术中的编程方法,可延长单个编程脉冲电压的持续时间并使得:目标状态与当前状态或目标状态与初始状态差别较大的单元的有效编程时间较长,阈值电压移动可超过一个阈值电压区间,提高编程效率;同时目标状态与当前状态或目标状态与初始状态差别较小的单元的有效编程时间依然较短,阈值电压移动不超过一个阈值电压区间,防止过编程情况的出现。当单个编程脉冲步骤的编程电压的持续时间不再有,必须使得各个被编程单元的阈值电压升高不超过一个阈值电压区间的大小的限制时,单个编程脉冲步骤编程电压的持续时间随着循环次数的增加可以变化或不变。可能的编程电压随时间的变化如图12所示。

本发明又一实施例给出了一种多层单元NAND闪存的编程方法,相较于现有技术中的编程方法,增大编程电压并使得目标状态与当前状态或目标状态与初始状态差别较大的单元的有效编程时间较长,阈值电压移动超过一个阈值电压区间,提高编程效率;同时目标状态与当前状态或目标状态与初始状态差别较小的单元的有效编程时间依然较短,阈值电压移动不超过一个阈值电压区间,防止过编程情况的出现。当单个编程脉冲步骤编程电压大小不再有,必须使得各个被编程的单元的阈值电压升高不超过一个阈值电压区间的大小的限制时,单个编程脉冲步骤编程电压的大小随着循环次数的增加可以变化或不变。可能的编程电压随时间的变化如图13所示。

本发明又一实施例给出了一种多层单元NAND闪存的编程方法,相较于现有技术中的编程方法,在最初的若干次编程脉冲步骤中给予较高的编程电压和较长的编程电压持续时间,随着循环次数的增加逐渐降低编程电压大小和持续时间;使得在最初的若干次编程脉冲步骤中各个单元阈值电压的变化较大,随着循环次数的增加,单次编程脉冲步骤中,各个单元阈值电压的变化幅度逐渐减小;使得各个单元在最初的几次编程脉冲步骤中快速接近目标状态,在后面的编程脉冲步骤中更准确地接近目标状态。能够增加编程的效率,提高编程的精度。可能的编程电压随时间的变化如图14所示。

对于本领域的技术人员而言,阅读上述说明后,各种变化和修正无疑将显而易见。因此,所附的权利要求书应看作是涵盖本发明真实意图和范围的全部变化和修正。在权利要求书范围内任何和所有等价的范围与内容,都应认为仍属本发明的意图和范围内。