内部电压发生电路及包括其的半导体器件

文献发布时间:2023-06-19 09:41:38

本专利申请是2015年8月26日申请的申请号为201510531691.2的名称为“内部电压发生电路及包括其的半导体器件”的分案申请。

相关申请的交叉引用

本申请要求于2015年2月2日提交的第10-2015-0015910号韩国专利申请的优先权,该韩国专利申请通过引用整体合并于此。

技术领域

本发明的示例性实施例涉及一种内部电压发生电路。

背景技术

随着半导体器件变得更加高度集成,使用的外部电压降低。低外部电压的使用对于提高可靠性以及降低功耗是重要的。然而,不是半导体器件之内的所有电路都由外部电压驱动,某些电路需要用于它们的操作的增高电压。该增高电压通常通过电荷泵电路产生。

外部电压通过电压焊盘而输入到半导体器件,并通过连接到电压焊盘的线路而传送到半导体器件之内的电路。电荷泵电路可以使用主电源电压VDD(例如,具有1.2V的目标电平)或高电源电压VPPEXT(例如,具有2.5V的目标电平)来产生内部电压。

通过电压焊盘而从半导体器件的外部供应的电源电压VDD和VPPEXT中的每个从特定电平(例如,地电压)开始,并以恒定斜率上升到相应的目标电平。在电源电压VDD和VPPEXT上升时,从电荷泵电路可以产生泄漏电流。如果电流泄露太大,则可能出现诸如自举失败的错误。

发明内容

各种实施例针对可以防止出现电流泄漏的内部电压发生电路及包括该内部电压发生电路的半导体器件。

而且,各种实施例针对可以通过阻止电流泄漏而防止出现诸如自举失败的错误的内部电压发生电路及包括该内部电压发生电路的半导体器件。

在实施例中,内部电压发生电路可以包括:第一控制信号发生单元,适用于在第一外部电压被激活时产生被激活为第二外部电压的第一控制信号;第二控制信号发生单元,适用于产生等于第二外部电压和内部电压中的较高者(即,具有等于第二外部电压和内部电压之间的较高者的无论哪个的电压)的第二控制信号;以及电压发生单元,适用于在基于第一控制信号和第二控制信号而阻挡电流流经发生节点(内部电压从发生节点产生)的同时,通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压。

在实施例中,半导体器件可以包括:第一电压传送线,适用于传送通过第一电压焊盘而输入的第一外部电压;第二电压传送线,适用于传送通过第二电压焊盘而输入的第二外部电压;第三电压传送线,适用于传送内部电压;内部电路,适用于使用被传送到第一电压传送线到第三电压传送线的电压来执行预定操作;内部电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压;以及NMOS晶体管,耦接在第二电压传送线与第三电压传送线之间,其中,NMOS晶体管在内部电路被测试时导通。

在实施例中,半导体器件可以包括:第一半导体芯片,包括第一电压焊盘和第二电压焊盘、第一NMOS晶体管以及第一内部电压发生单元和第一内部电路,第一内部电压发生单元适用于基于通过第二电压焊盘输入的电压以及第一振荡信号来产生第一内部电压,第一内部电路使用通过第一电压焊盘和第二电压焊盘输入的电压以及第一内部电压而驱动,其中,第一NMOS晶体管耦接在第二电压焊盘与第一发生节点(第一内部电压从第一发生节点产生)之间并在第一内部电路被测试时导通;第二半导体芯片,包括第三电压焊盘和第四电压焊盘、第二NMOS晶体管以及第二内部电压发生单元和第二内部电路,第二内部电压发生单元适用于基于通过第四电压焊盘而输入的电压以及第二振荡信号来产生第二内部电压,第二内部电路使用通过第三电压焊盘和第四电压焊盘而输入的电压以及第二内部电压来驱动,其中,第二NMOS晶体管耦接在第四电压焊盘与第二发生节点(第二内部电压从第二发生节点产生)之间并在第二内部电路被测试时导通;第一芯片通孔,适用于耦接第一电压焊盘与第三电压焊盘以传送第一外部电压;以及第二芯片通孔,适用于耦接第二电压焊盘与第四电压焊盘以传送第二外部电压。

在实施例中,内部电压发生单元可以包括:控制信号发生单元,适用于基于第一外部电压和第二外部电压以及内部电压来产生一个或更多个控制信号;电压发生单元,适用于在基于一个或更多个控制信号而阻挡电流流经发生节点(内部电压从该发生节点产生)的同时,通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压。

附图说明

图1是图示用于描述泄漏电流问题的内部电压发生电路的示图。

图2是图示根据本发明实施例的内部电压发生电路的示图。

图3是图2中示出的第一控制信号发生单元的详细图。

图4是图2中示出的第二控制信号发生单元的详细图。

图5是用于描述图2中示出的内部电压发生电路的操作的波形图。

图6是图示根据本发明实施例的内部电压发生电路的示图。

图7是图示根据本发明实施例的半导体器件的示图。

图8是图示根据本发明实施例的半导体器件的示图。

具体实施方式

下面将参照附图来更加详细地描述各种实施例。然而,本发明可以以不同的形式实施,而不应解释为局限于此处陈述的实施例。相反地,提供这些实施例使得本公开将是彻底的且完整的,这些实施例将把本发明的范围充分地传达给本领域技术人员。贯穿本公开,相同的附图标记在本发明的各种附图和实施例中指代相同的部分。

附图未必按比例绘制,在某些情况下,可能夸大了比例以清楚地图示实施例的特征。还需要注意的是,在本说明书中,“连接/耦接”不仅指一个部件直接地耦接到另一个部件,还指一个部件通过中间部件而间接地耦接到另一个部件。此外,只要在句中未特别提到,则单数形式可以包括复数形式。

图1是图示用于描述泄漏电流问题的内部电压发生电路的示图。

参见图1,内部电压发生电路可以包括电容器C1和C2、PMOS晶体管P1和P2、以及NMOS晶体管N1到N4和反相器I1到I5。内部电压发生电路可以包括通过电荷泵操作而产生增高电压的电荷泵电路。内部电压发生电路可以使用外部电压VDD和VPPEXT以及周期性触发的振荡信号OSC来产生内部增高电压VPP。外部电压VDD可以是主电源电压,外部电压VPPEXT可以是比主电源电压高的高电源电压。

对半导体器件上电时,外部电压VDD和VPPEXT被施加到半导体器件。外部电压VDD和VPPEXT从地电平上升到相应的目标电平。施加到半导体器件的外部电压上升的时段称作斜升时段。在斜升时段期间,外部电压VPPEXT可以首先从地电平上升到目标电平,然后外部电压VDD可以从地电平上升到目标电平。振荡信号OSC可以处于去激活状态,内部电压发生电路之内的节点NO1和NO2可以具有不同的电压。

将假定节点NO1具有低电压。在这种情况下,PMOS晶体管P1和NMOS晶体管N1响应于节点NO1的电压而导通,从而泄漏电流I

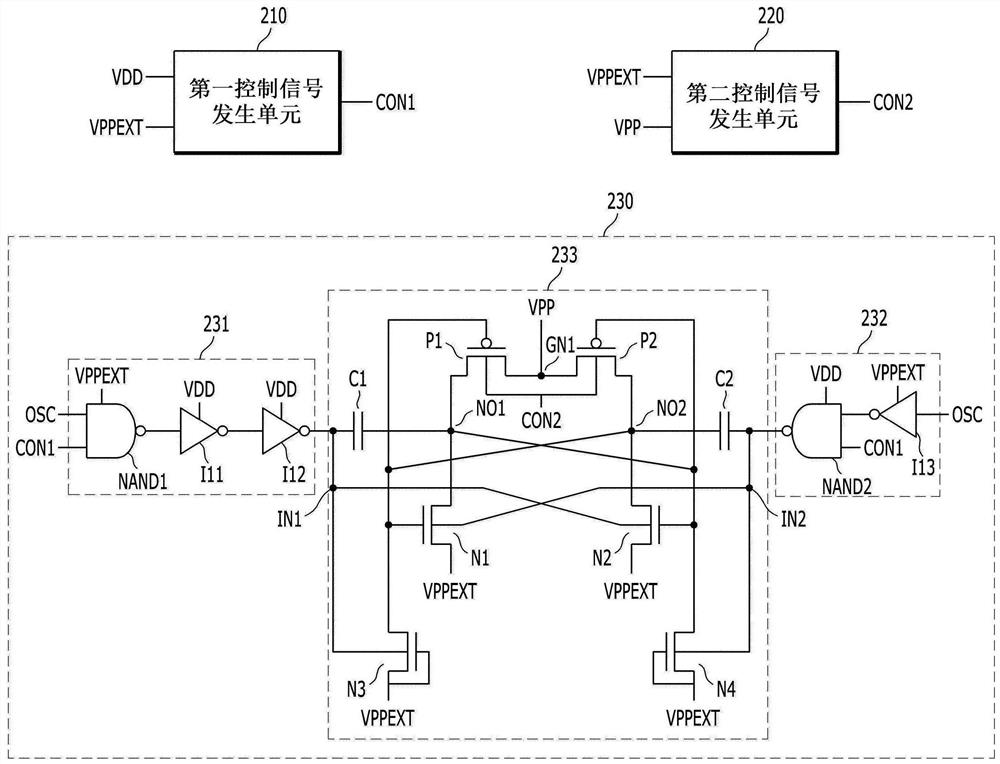

图2是图示根据本发明实施例的内部电压发生电路的示图。

参见图2,内部电压发生电路可以包括第一控制信号发生单元210、第二控制信号发生单元220和电压发生单元230。电压发生单元230可以包括第一输入单元231、第二输入单元232和电荷泵单元233。第二外部电压VPPEXT的目标电平可以比第一内部电压VDD的目标电平高。

当第一外部电压VDD被激活时,第一控制信号发生单元210可以产生被激活为第二外部电压VPPEXT的第一控制信号CON1。当第一外部电压VDD被去激活时,第一控制信号发生单元210可以去激活第一控制信号CON1。第二控制信号发生单元220可以产生等于第二外部电压VPPEXT和内部增高电压VPP中的较高者的第二控制信号CON2。

电压发生单元230可以响应于控制信号CON1和CON2而在阻挡电流流经发生节点GN1(内部增高电压VPP从发生节点GN1产生)的同时,通过响应于外部电压VDD和VPPEXT以及振荡信号OSC而执行电荷泵操作来产生内部增高电压VPP。电压发生单元230可以包括第一输入单元231、第二输入单元232和电荷泵单元233。

当第一控制信号CON1被激活时,第一输入单元231可以将第一输入节点IN1的电压固定为特定电压(例如,逻辑“高”电平)。当第一控制信号CON1被去激活时,第一输入单元231可以响应于振荡信号OSC而触发第一输入节点IN1的电压。第一输入单元231可以包括与非门NAND1以及反相器I11和I12。与非门NAND1可以使用第二外部电压VPPEXT来操作。当第一控制信号CON1被激活为低时,无论振荡信号OSC的电平是什么,第一输入节点IN1的电压都可以被固定为逻辑高电平。当第一控制信号CON1被去激活为逻辑高电平时,第一输入节点IN1的电压可以被触发为与振荡信号OSC相反的电平。

当第一控制信号CON1被激活时,第二输入单元232可以将第二输入节点IN2的电压固定为特定电平(例如,逻辑“高”电平)。当第一控制信号CON1被去激活时,第二输入单元232可以响应于振荡信号OSC来触发第二输入节点IN2的电压。第二输入单元232可以包括与非门NAND2和反相器I13。当第一控制信号CON1被激活为低时,无论振荡信号OSC的电平是什么,第二输入节点IN2的电压都可以被固定为逻辑高电平。当第一控制信号CON1被去激活为逻辑高电平时,第二输入节点IN2的电压可以被触发为与振荡信号OSC相同的电平。

电荷泵单元233可以包括第一电容性元件C1、第二电容性元件C2、第一PMOS晶体管P1、第二PMOS晶体管P2、第一NMOS晶体管N1、第二NMOS晶体管N2、第三NMOS晶体管N3和第四NMOS晶体管N4。第一电容性元件C1耦接在第一输入节点IN1与第一内部节点NO1之间。第二电容性元件C2耦接在第二输入节点IN2与第二内部节点NO2之间。第一PMOS晶体管P1耦接在发生节点GN1与第一内部节点NO1之间,并具有连接到第二内部节点NO2的栅极以及被施加第二控制信号CON2的基体(或主体)。第二PMOS晶体管P2耦接在发生节点GN1与第二内部节点NO2之间,并具有连接到第一内部节点NO1的栅极以及被施加第二控制信号CON2的基体。第一NMOS晶体管N1具有连接到第一内部节点NO1的一端、供应有第二外部电压VPPEXT的另一端、连接到第二内部节点NO2的栅极以及连接到第二输入节点NO2的基体。第二NMOS晶体管N2具有连接到第二内部节点NO2的一端、供应有第二外部电压VPPEXT的另一端、连接到第一内部节点NO1的栅极以及连接到第一输入节点IN1的基体。第三NMOS晶体管N3具有连接到第二内部节点NO2的一端、供应有第二外部电压VPPEXT的另一端和栅极以及连接到第一输入节点IN1的基体。第四NMOS晶体管N4具有连接到第一内部节点NO1的一端、供应有第二外部电压VPPEXT的另一端和栅极以及连接到第二输入节点IN2的基体。作为参考,电容性元件C1和C2中的每个可以是电容器。

在斜升时段中,如果第二外部电压VPPEXT首先上升而接下来第一外部电压VDD上升,则第一输入节点IN1和第二输入节点IN2的电压可以在第一外部电压VDD上升之前被固定为逻辑高电平,且由于电容器C1和C2的耦合效应,第一内部节点NO1和第二内部节点NO2的电压也可以被固定为逻辑高电平。相应地,PMOS晶体管P1和P2可以截止,使得电流不在发生节点GN1中流动。此外,PMOS晶体管P1和P2的阈值电压可以上升,并且发生节点GN1被阻挡的效果可以提高,因为施加到PMOS晶体管P1和P2的基体的第二控制信号CON2与第二外部电压VPPEXT具有相同的电平。

在第二外部电压VPPEXT被激活但第一外部电压VDD未被激活的时段中,内部电压发生电路的输入节点IN1和IN2的电压被固定为特定电平,且连接到发生节点GN1的晶体管P1和P2的阈值电压增加。相应地,可以防止泄漏电流流经发生节点GN1。

图3是图2中示出的第一控制信号发生单元210的详细图。

参见图3,第一控制信号发生单元210可以包括电阻元件R1、NMOS晶体管N5、PMOS晶体管P3、NMOS晶体管N6和反相器I14。电阻元件R1具有被供应有第一外部电压VDD的一端。NMOS晶体管N5具有连接到电阻元件R1的另一端的一端、供应有基电压VSS的另一端以及连接到电阻元件R1的另一端的栅极。PMOS晶体管P3具有供应有第二外部电压VPPEXT的一端、连接到节点NO3的另一端以及连接到节点NO3的栅极。NMOS晶体管N6具有连接到节点NO3的一端、供应有基电压VSS的另一端以及连接到NMOS晶体管N5的栅极的栅极。反相器I14接收节点NO3的电压以输出第一控制信号CON1。

图4是图2中示出的第二控制信号发生单元220的详细图。

参见图4,第二控制信号发生单元220可以包括:PMOS晶体管P4,具有供应有第二外部电压VPPEXT的一端和连接到节点NO4(第二控制信号CON2从节点NO4产生)的另一端;PMOS晶体管P5,具有供应有内部增高电压VPP的一端和连接到节点NO5的另一端;电阻元件R2,耦接在PMOS晶体管P4的一端与PMOS晶体管P5的栅极之间;以及电阻元件R3,耦接在PMOS晶体管P5的一端与PMOS晶体管P4的栅极之间。

图5是用于描述图2中示出的内部电压发生电路的操作的波形图。

参照图5来描述在斜升时段中内部电压发生电路的操作。VDD是第一外部电压的波形图,VPPEXT是第二外部电压的波形图,CON1是第一控制信号的波形图,CON2是第二控制信号的波形图,VPP是内部电压的波形图。

当斜升时段开始时,首先,第二外部电压VPPEXT上升并在步骤S1达到目标电平LV2。在这种情况下,第一控制信号CON1维持处于低电平的去激活态,第二控制信号CON2随着第二外部电压VPPEXT而上升并达到目标电平LV2。内部增高电压VPP维持低电平,因为第一控制信号CON1和第二控制信号CON2阻挡了流经发生节点GN1的电流。

第一外部电压VDD上升并在步骤S2达到目标电平LV1。当第一外部电压VDD被激活时,第一控制信号CON1被去激活并上升到逻辑高电平。相应地,第一输入节点IN1和第二输入节点IN2的电压可以响应于振荡信号OSC而被触发。第二控制信号CON2维持目标电平LV2。其后,当振荡信号OSC被激活并在步骤S3开始触发时,内部增高电压VPP上升,第二控制信号CON2随着内部增高电压VPP而上升。

图6是图示根据本发明实施例的内部电压发生电路的示图。

参见图6,内部电压发生电路可以包括第一控制信号发生单元610、第二控制信号发生单元620以及电压发生单元630。电压发生单元630可以包括信号发生单元631、信号传送单元632和电荷泵单元633。图6中的第一控制信号发生单元610和第二控制信号发生单元620具有相同的配置,并与参照图2到图4而描述的第一控制信号发生单元210和第二控制信号发生单元220类似地操作。图6中的内部电压发生电路可以包括与图2中的内部电压发生电路不同的电压发生单元630。电压发生单元630可以是用于通过执行电荷泵操作来产生内部增高电压VPP的电荷泵电路。

信号发生单元631可以通过将振荡信号OSC反相而产生第一信号G1,可以将第一信号G1反相而产生第二信号G2,可以将第二信号G2反相而产生第三信号K2,并且可以将第三信号K2反相而产生第四信号K1。信号发生单元631可以包括反相器I15到反相器I18。

信号传送单元632可以在第一控制信号CON1被激活时将第一输入信号K1’和第二输入信号K2’固定为特定电平,并且可以在第一控制信号CON1被去激活时将第四信号K1和第三信号K2作为第一输入信号K1’和第二输入信号K2’而传送。信号传送单元632可以包括与非门NAND11和与非门NAND12以及反相器I19和反相器I20。

电荷泵单元633可以包括电容性元件C3、电容性元件C4、电容性元件C5、电容性元件C6、PMOS晶体管P6和PMOS晶体管P7。电容性元件C3具有供应有第一输入信号K1’的一端以及连接到内部节点NO5的另一端。电容性元件C4具有供应有第二输入信号K2’的一端以及连接到内部节点NO6的另一端。电容性元件C5具有连接到第一信号G1的一端以及连接到内部节点NO7的另一端。电容性元件C6具有供应有第二信号G2的一端以及连接到内部节点NO8的另一端。PMOS晶体管P6耦接在发生节点GN2与内部节点NO5之间,并具有连接到内部节点NO6的栅极以及供应有控制信号CON2的基体。PMOS晶体管P7耦接在发生节点GN2与第二内部节点NO6之间,并具有连接到第一内部节点NO5的栅极和供应有第二控制信号CON2的基体。

电荷泵单元633还可以包括NMOS晶体管N7、NMOS晶体管N8、NMOS晶体管N9、NMOS晶体管N10、NMOS晶体管N11、NMOS晶体管N12、NMOS晶体管N13和NMOS晶体管N14。NMOS晶体管N7具有连接到内部节点NO5的一端、供应有第二外部电压VPPEXT的另一端以及连接到第三内部节点NO7的栅极。NMOS晶体管N8具有连接到内部节点NO6的一端、供应有第二外部电压VPPEXT的另一端以及连接到内部节点NO8的栅极。NMOS晶体管N9具有连接到内部节点NO7的一端、供应有第二外部电压VPPEXT的另一端以及连接到内部节点NO8的栅极。NMOS晶体管N10具有连接到第四内部节点NO8的一端、供应有第二外部电压VPPEXT的另一端以及连接到内部节点NO7的栅极。NMOS晶体管N11具有连接到内部节点NO7的一端以及供应有第二外部电压VPPEXT的另一端和栅极。NMOS晶体管N12具有连接到内部节点NO8的一端以及供应有第二外部电压VPPEXT的另一端和栅极。NMOS晶体管N13具有连接到内部节点NO7的一端和栅极以及供应有第二外部电压VPPEXT的另一端。NMOS晶体管N14具有连接到内部节点NO8的一端和栅极以及供应有第二外部电压VPPEXT的另一端。

在斜升时段中,如果第二外部电压VPPEXT首先上升而接下来第一外部电压VDD上升,则第一输入信号K1’和第二输入信号K2’可以在第一外部电压VDD上升之前被固定为逻辑高电平,且内部节点NO5和NO6的电压也可以由于电容器C1和C2的耦合效应而被固定为逻辑高电平。相应地,PMOS晶体管P6和P7截止,从而可以阻止电流在发生节点GN2中流动。此外,由于施加到PMOS晶体管P6和P7的基体的第二控制电压CON2与第二外部电压VPPEXT具有相同的电平,所以PMOS晶体管P6和P7的阈值电压上升,由此能够提高阻挡发生节点GN2的效果。

在第二外部电压VPPEXT被激活但第一外部电压VDD未被激活的时段中,内部电压发生电路的输入信号K1’和K2’的电压被固定到特定电平,且晶体管P6和P7的阈值电压上升。相应地,可以防止发生节点GN2中的电流泄漏。

图7是图示根据本发明实施例的半导体器件的示图。

参见图7,半导体器件可以包括第一焊盘701、第二焊盘702、第一电压传送线703、第二电压传送线704、第三电压传送线705、内部电路710、内部电压发生单元720以及NMOS晶体管NT。内部电压发生单元720可以包括图2或图6中的内部电压发生电路。在内部电压发生单元720和内部电路710中使用的电压VDD、VPPEXT和VPP可以通过各个电压传送线703到705传送。

第一电压传送线703可以传送通过第一电压焊盘701而输入的第一外部电压VDD。第二电压传送线704可以传送通过第二电压焊盘702而输入的第二外部电压VPPEXT。第三电压传送线705可以传送由内部电压发生单元720产生的内部增高电压VPP。

内部电路710可以使用被传送到电压传送线703-705的电压VDD、VPPEXT和VPP来执行特定操作。例如,如果半导体器件是存储器件,则内部电路710可以包括用于储存数据的存储单元,并对数据执行读取操作或写入操作或者执行用于测试存储器件的测试操作。

NMOS晶体管NT耦接在第二电压传送线704与第三电压传送线705之间,并可以在内部电路710被测试时导通。如果半导体器件执行正常操作,则内部电路710可以使用由内部电压发生单元720产生的内部增高电压VPP。在使用内部增高电压VPP的操作(其中对于测试操作需要精确电压)中,内部电路710可以使用通过第二焊盘702输入的第二外部电压VPPEXT来驱动。在这样的测试操作中,通过第二焊盘702输入的第二外部电压VPPEXT可以被传送到第三电压传送线705,使得在基于内部增高电压VPP而操作的电路中使用被传送的电压。

NMOS晶体管NT阻挡在第二电压传送线704与第三电压传送线705之间可能出现的泄漏电流,直到第二外部电压VPPEXT达到目标电平,使得稳定的测试操作被执行。施加到NMOS晶体管NT的栅极的测试信号TEST可以在测试操作被执行时被激活。对于第二电压传送线704的要被传送到第三电压传送线705的第二外部电压VPPEXT,测试信号TEST的激活电平可以比第二外部电压VPPEXT的目标电平高NMOS晶体管NT的阈值电压。例如,如果第二外部电压VPPEXT的目标电平是4.0V而NMOS晶体管NT的阈值电压是0.7V,则测试信号TEST的激活电平可以是4.7V或更高。

作为参考,如果PMOS晶体管而不是NMOS晶体管NT被使用,则下面的问题可能出现。在第二外部电压VPPEXT被传送到第三电压传送线705之后使用内部增高电压VPP的操作中,测试信号TEST的激活电平可以具有接近基电压(例如,0V)的值,因为PMOS晶体管需要使用测试信号TEST来导通。在这种情况下,在第二外部电压VPPEXT达到目标电平(例如,4.0V)之前,PMOS晶体管导通,第二电压传送线704和第三电压传送线705被耦接。即,泄漏电流产生。如果泄漏电流出于任何原因而变得过大,则施加第二外部电压VPPEXT的控制器(在图7中未图示)可以检测过大的泄漏电流并停止系统。相应地,可以通过使用NMOS晶体管在第二外部电压VPPEXT达到合适的电平之前阻挡第二电压传送线704与第三电压传送线705来防止前面提到的问题。

图8是图示根据本发明实施例的半导体器件。

参见图8,半导体器件可以包括第一半导体芯片810、第二半导体芯片820、第一芯片通孔TSV1以及第二芯片通孔TSV2。第一半导体芯片810可以包括电压焊盘PAD1和PAD2、内部电压发生单元811、内部电路812和NMOS晶体管NTA,第二半导体芯片820可以包括电压焊盘PAD3和PAD4、内部电压发生单元821、内部电路822和NMOS晶体管NTB。第一半导体芯片810和第二半导体芯片820中的每个可以包括图7中的半导体器件。

第一半导体芯片810的内部电路811使用通过电压焊盘PAD1和PAD2输入的电压VDD和VPPEXT以及由内部电压发生单元812产生的内部电压VPP1来执行操作,第二半导体芯片820的内部电路821使用通过电压焊盘PAD3和PAD4输入的电压VDD和VPPEXT以及由内部电压发生单元822产生的内部电压VPP2来执行操作。在测试操作期间,重要的可以是以相似的方式驱动半导体芯片810和820。由于第一半导体芯片810和第二半导体芯片820之间的制造不完美,第一半导体芯片810的内部电压VPP1和第二半导体芯片820的内部电压VPP2可以稍微不同。相应地,在测试操作期间,外部电压VPPEXT可以在第一半导体芯片810的内部电路812和第二半导体芯片820的内部电路822中被用作增高电压。

相应地,在测试操作期间,NMOS晶体管NTA可以通过激活与第一半导体芯片810相对应的测试信号TEST1而导通,NMOS晶体管NTB可以通过激活与第二半导体芯片820相对应的测试信号TEST2而导通,内部电路811和821可以使用通过相应的电压焊盘PAD2和PAD4作为增高电压而被施加的外部电压VPPEXT来驱动。在这种情况下,NMOS晶体管NTA和NTB中的每个阻挡相应的节点NOA和NOB与相应的节点GNA和GNB之间可能出现的泄漏电流,直到外部电压VPPEXT达到目标电平,使得稳定的测试操作被执行,其中,外部电压VPPEXT被施加到相应的节点NOA和NOB,相应的内部增高电压VPP1和VPP2从相应的节点GNA和GNB产生。如果使用PMOS晶体管,则由于参照图7而描述的问题,可能不能正常地执行测试。

在附图中图示的栅极中,标有VPPEXT的栅极可以使用VPPEXT来驱动,其他栅极可以使用VDD来驱动。

根据本发明的实施例,在斜升(或上电)被执行时,通过将内部电压发生电路的内部节点的电压固定或者通过控制包括在内部电压发生电路中的开关元件的基体电压,可以防止泄漏电流的产生。

此外,根据本发明的实施例,可以通过防止内部电压发生电路中的泄漏电流的产生来防止在半导体器件中出现诸如自举失败的错误。

尽管已经出于说明性的目的而描述了各种实施例,但对于本领域技术人员明显的是,在不脱离如所附权利要求书中所限定的本发明的精神和范围的情况下,可以做出各种改变和变型。

通过以上实施例可见,本申请可以提供以下技术方案。

技术方案1.一种内部电压发生电路,包括:

第一控制信号发生单元,适用于在第一外部电压被激活时产生被激活为第二外部电压的电平的第一控制信号;

第二控制信号发生单元,适用于产生等于第二外部电压和内部电压中的较高者的第二控制信号;以及

电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压,同时基于第一控制信号和第二控制信号而阻挡电流流经发生节点,内部电压从所述发生节点产生。

技术方案2.根据技术方案1所述的内部电压发生电路,其中,第二外部电压的目标电平比第一外部电压的目标电平高。

技术方案3.根据技术方案1所述的内部电压发生电路,其中,第一控制信号发生单元在第一外部电压被去激活时去激活第一控制信号。

技术方案4.根据技术方案1所述的内部电压发生电路,其中,第一控制信号发生单元包括:

电阻元件,具有供应有第一外部电压的第一端;

第一NMOS晶体管,具有连接到电阻元件的第二端的第一端、供应有地电压的第二端以及连接到电阻元件的第二端的栅极;

第一PMOS晶体管,具有供应有第二外部电压的第一端、连接到第一节点的第二端以及连接到第一节点的栅极;

第二NMOS晶体管,具有连接到第一节点的第一端、供应有基电压的第二端以及连接到第一NMOS晶体管的栅极的栅极;以及

反相器,适用于接收第一节点的电压以产生第一控制信号。

技术方案5.根据技术方案1所述的内部电压发生电路,其中,第二控制信号发生单元包括:

第一PMOS晶体管,具有供应有第二外部电压的第一端以及连接到第一节点的第二端,第二控制信号从所述第一节点产生;

第二PMOS晶体管,具有连接到发生节点的第一端以及连接到第一节点的第二端;

第一电阻元件,耦接在第一PMOS晶体管的第一端与第二PMOS晶体管的栅极之间;以及

第二电阻元件,耦接在第二PMOS晶体管的第一端与第一PMOS晶体管的栅极之间。

技术方案6.根据技术方案1所述的内部电压发生电路,其中,电压发生单元包括:

第一输入单元,适用于在第一控制信号被激活时将第一输入节点的电压固定为特定电平,以及在第一控制信号被去激活时基于振荡信号而触发第一输入节点的电压;

第二输入单元,适用于在第一控制信号被激活时将第二输入节点的电压固定为特定电平,以及在第一控制信号被去激活时基于振荡信号而将第二输入节点的电压触发为具有与第一输入节点相反的相位;以及

电荷泵单元,适用于基于第一输入节点和第二输入节点的电压以及第二外部电压来产生内部电压,同时基于第二控制信号而阻挡电流流经发生节点。

技术方案7.根据技术方案6所述的内部电压发生电路,其中,电荷泵单元包括:

第一电容性元件,耦接在第一输入节点与第一内部节点之间;

第二电容性元件,耦接在第二输入节点与第二内部节点之间;

第一PMOS晶体管,耦接在发生节点与第一内部节点之间,并具有连接到第二内部节点的栅极以及供应有第二控制信号的基体;

第二PMOS晶体管,耦接在发生节点与第二内部节点之间,并具有连接到第一内部节点的栅极以及供应有第二控制信号的基体;

第一NMOS晶体管,具有连接到第一内部节点的第一端、供应有第二外部电压的第二端、连接到第二内部节点的栅极以及连接到第二输入节点的基体;

第二NMOS晶体管,具有连接到第二内部节点的第一端、供应有第二外部电压的第二端、连接到第一内部节点的栅极以及连接到第一输入节点的基体;

第三NMOS晶体管,具有连接到第二内部节点的第一端、供应有第二外部电压的第二端和栅极以及连接到第一输入节点的基体;以及

第四NMOS晶体管,具有连接到第一内部节点的第一端、供应有第二外部电压的第二端和栅极以及连接到第二输入节点的基体。

技术方案8.根据技术方案1所述的内部电压发生电路,其中,电压发生单元包括:

信号发生单元,适用于通过将振荡信号反相而产生第一信号、将第一信号反相而产生第二信号、将第二信号反相而产生第三信号以及将第三信号反相而产生第四信号;

信号传送单元,适用于在第一控制信号被激活时将第一输入信号和第二输入信号固定为特定电平,以及在第一控制信号被去激活时分别将第四信号和第三信号作为第一输入信号和第二输入信号而传送;

电荷泵单元,适用于基于第一输入信号和第二输入信号、第一信号和第二信号以及第二外部电压来产生内部电压,同时基于第二控制信号而阻挡电流流经发生节点。

技术方案9.根据技术方案8所述的内部电压发生电路,其中,电荷泵单元包括:

第一电容性元件,具有供应有第一输入信号的第一端以及连接到第一内部节点的第二端;

第二电容性元件,具有供应有第二输入信号的第一端以及连接到第二内部节点的第二端;

第三电容性元件,具有供应有第一信号的第一端以及连接到第三内部节点的第二端;

第四电容性元件,具有供应有第二信号的第一端以及连接到第四内部节点的第二端;

第一PMOS晶体管,耦接在发生节点与第一内部节点之间,并具有连接到第二内部节点的栅极以及供应有第二控制信号的基体;以及

第二PMOS晶体管,耦接在发生节点与第二内部节点之间,并具有连接到第一内部节点的栅极以及供应有第二控制信号的基体。

技术方案10.根据技术方案9所述的内部电压发生电路,其中,电荷泵单元包括:

第一NMOS晶体管,具有连接到第一内部节点的第一端、供应有第二外部电压的第二端以及连接到第三内部节点的栅极;

第二NMOS晶体管,具有连接到第二内部节点的第一端、供应有第二外部电压的第二端以及连接到第四内部节点的栅极;

第三NMOS晶体管,具有连接到第三内部节点的第一端、供应有第二外部电压的第二端以及连接到第四内部节点的栅极;

第四NMOS晶体管,具有连接到第四内部节点的第一端、供应有第二外部电压的第二端以及连接到第三内部节点的栅极;

第五NMOS晶体管,具有连接到第三内部节点的第一端以及供应有第二外部电压的第二端和栅极;

第六NMOS晶体管,具有连接到第四内部节点的第一端以及供应有第二外部电压的第二端和栅极;

第七NMOS晶体管,具有连接到第三内部节点的第一端和栅极以及供应有第二外部电压的第二端;以及

第八NMOS晶体管,具有连接到第四内部节点的第一端和栅极以及供应有第二外部电压的第二端。

技术方案11.一种半导体器件,包括:

第一电压传送线,适用于传送通过第一电压焊盘而输入的第一外部电压;

第二电压传送线,适用于传送通过第二电压焊盘而输入的第二外部电压;

第三电压传送线,适用于传送内部电压;

内部电路,适用于使用被传送到第一电压传送线到第三电压传送线的电压来执行预定操作;

内部电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压;以及

NMOS晶体管,耦接在第二电压传送线与第三电压传送线之间,其中,NMOS晶体管在内部电路被测试时导通。

技术方案12.根据技术方案11所述的半导体器件,其中,第二外部电压的目标电平比第一外部电压的目标电平高。

技术方案13.根据技术方案11所述的半导体器件,其中,内部电压发生单元在第一外部电压具有去激活态时阻挡电流流经发生节点,内部电压从所述发生节点产生。

技术方案14.根据技术方案13所述的半导体器件,其中,内部电压发生单元包括:

第一控制信号发生单元,适用于在第一内部电压被激活时产生被激活为第二外部电压的电平的第一控制信号;

第二控制信号发生单元,适用于产生等于第二外部电压和内部电压中的较高者的第二控制信号;以及

电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压,同时基于第一控制信号和第二控制信号而阻挡电流流经发生节点。

技术方案15.根据技术方案14所述的半导体器件,其中,电压发生单元包括:

第一输入单元,适用于在第一控制信号被激活时将第一输入节点的电压固定为特定电平,以及在第一控制信号被去激活时基于振荡信号来触发第一输入节点的电压;

第二输入单元,适用于在第一控制信号被激活时将第二输入节点的电压固定为特定电平,以及在第一控制信号被去激活时基于振荡信号来将第二输入节点的电压触发为与第一输入节点的电压相反的相位;以及

电荷泵单元,适用于基于第一输入节点和第二输入节点的电压以及第二外部电压来产生内部电压,同时基于第二控制信号而阻挡电流流经发生节点。

技术方案16.根据技术方案14所述的半导体器件,其中,电压发生单元包括:

信号发生单元,适用于通过将振荡信号反相而产生第一信号、通过将第一信号反相而产生第二信号、通过将第二信号反相而产生第三信号以及通过将第三信号反相而产生第四信号;

信号传送单元,适用于在第一控制信号被激活时阻挡振荡信号,以及在第一控制信号被去激活时分别将第四信号和第三信号作为第一输入信号和第二输入信号来传送;

电荷泵单元,适用于基于第一输入信号和第二输入信号、第一信号和第二信号以及第二外部电压来产生内部电压,同时基于第二控制信号而阻挡电流流经发生节点。

技术方案17.一种半导体器件,包括:

第一半导体芯片,包括第一电压焊盘和第二电压焊盘、第一NMOS晶体管以及第一内部电压发生单元和第一内部电路,第一内部电压发生单元适用于基于通过第二电压焊盘而输入的电压以及第一振荡信号来产生第一内部电压,第一内部电路使用通过第一电压焊盘和第二电压焊盘而输入的电压以及第一内部电压来驱动,其中,第一NMOS晶体管耦接在第二电压焊盘与从其产生第一内部电压的第一发生节点之间,并在第一内部电路被测试时导通;

第二半导体芯片,包括第三电压焊盘和第四电压焊盘、第二NMOS晶体管以及第二内部电压发生单元和第二内部电路,第二内部电压发生单元适用于基于通过第四电压焊盘输入的电压以及第二振荡信号来产生第二内部电压,第二内部电路使用通过第三电压焊盘和第四电压焊盘而输入的电压以及第二内部电压来驱动,其中,第二NMOS晶体管耦接在第四电压焊盘与从其产生第二内部电压的第二发生节点之间,并在第二内部电路被测试时导通;

第一芯片通孔,适用于耦接第一电压焊盘与第三电压焊盘以传送第一外部电压;以及

第二芯片通孔,适用于耦接第二电压焊盘与第四电压焊盘以传送第二外部电压。

技术方案18.根据技术方案17所述的半导体器件,其中,第二外部电压的目标电平比第一外部电压的目标电平高。

技术方案19.根据技术方案17所述的半导体器件,其中,第一内部电压发生单元和第二内部电压发生单元中的每个在第一外部电压处于去激活态时阻挡电流流经相应的发生节点。

技术方案20.根据技术方案19所述的半导体器件,其中,第一内部电压发生单元和第二内部电压发生单元中的每个包括:

第一控制信号发生单元,适用于在第一外部电压被激活时产生被激活为第二外部电压的电平的第一控制信号;

第二控制信号发生单元,适用于产生等于第二外部电压和对应的内部电压中的较高者的第二控制信号;以及

电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压,同时基于第一控制信号和第二控制信号而阻挡电流流经对应的发生节点。

技术方案21.一种内部电压发生电路,包括:

控制信号发生单元,适用于基于第一外部电压和第二外部电压以及内部电压来产生一个或更多个控制信号;以及

电压发生单元,适用于通过基于第二外部电压和振荡信号而执行电荷泵操作来产生内部电压,同时基于所述一个或更多个控制信号而阻挡电流流经发生节点,内部电压从发生节点产生。

技术方案22.根据技术方案21所述的内部电压发生电路,其中,第二外部电压的目标电平比第一外部电压的目标电平高。

技术方案23.根据技术方案21所述的内部电压发生电路,其中,当第一外部电压被激活时,控制信号发生单元产生第一控制信号和第二控制信号,第一控制信号被激活为第二外部电压的电平,第二控制信号等于第二外部电压与内部电压中的较高者。

技术方案24.根据技术方案23所述的内部电压发生电路,其中,当第一外部电压被去激活时,控制信号发生单元去激活第一控制信号。

- 内部电压发生电路及包括其的半导体器件

- 内部电压发生电路和包括其的半导体器件