循续渐近式模拟至数字转换器及其参考涟波抑制电路

文献发布时间:2023-06-19 11:03:41

技术领域

本发明是有关一种模拟至数字转换器(ADC),特别是关于一种具低复杂度码相依(low-complexity code-dependent)参考涟波抑制(reference ripple suppression)的循续渐近式模拟至数字转换器(SAR ADC)。

背景技术

循续渐近式模拟至数字转换器(successive approximation register analog-to-digital converter,SAR ADC,或称为循续渐近式类比至数位转换器)为模拟至数字转换器(ADC,或称为类比至数位转换器)的一种,用以等效转换模拟信号为数字信号。循续渐近式模拟至数字转换器借由比较与搜寻所有可能的量化阶层以执行转换,用以得到数字输出。相较于一般的模拟至数字转换器,循续渐近式模拟至数字转换器使用较少的电路面积与相应成本。

考量参考电压产生电路,其功率消耗通常大于循续渐近式模拟至数字转换器的主要电路。循续渐近式模拟至数字转换器需重复切换电容数字至模拟转换器(capacitivedigital-to-analog converter,或称为电容数位至类比转换器),因而从参考电压产生电路重复汲取电流,造成参考电压产生电路的驱动更为困难。此外,传统循续渐近式模拟至数字转换器具非线性,特别是差动非线性度(differential nonlinearity,DNL)。

因此亟需提出一种新颖的循续渐近式模拟至数字转换器,以改善线性度、功率消耗及电路面积。

发明内容

鉴于上述,本发明实施例的目的之一在于提出一种具低复杂度码相依(code-dependent)参考涟波抑制的循续渐近式模拟至数字转换器(SAR ADC),用以抑制差动非线性度(DNL),更节省参考电压产生电路的功率与电路面积。

本发明的目的是采用以下的技术方案来实现的。依据本发明提出的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路包含多个码相依补偿单元,每一个码相依补偿单元包含逻辑电路与补偿电容器。补偿电容器的第一板接收待补偿的参考电压,且补偿电容器的第二板接收逻辑电路的输出,其中逻辑电路执行逻辑运算于循续渐近式模拟至数字转换器的输出码及代表切换数字至模拟转换器的底板电压的至少一个逻辑值。n位循续渐近式模拟至数字转换器的第k次切换最多使用(k-1)个码相依补偿单元,k为1至(n-1)的正整数,n为大于1的正整数。

本发明的目的还可以采用以下技术措施进一步实现。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该输出码包含输出码对,其包含B

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该逻辑电路根据以下真值表,于取样期间与转换期间执行逻辑运算:

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中仅使用第m次及其之后的该码相依补偿单元,但是借由加入冗余以容忍未受补偿所造成错误,其中m为大于2的正整数。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中仅使用该补偿电容器的电容值大于预设临界值的该码相依补偿单元。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该码相依补偿单元的最大数目与该循续渐近式模拟至数字转换器的切换数呈线性增加。

本发明的目的还采用以下技术方案来实现。依据本发明提出的一种适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,包含:多个码独立补偿单元,每一个该码独立补偿单元包含第一逻辑电路与第一补偿电容器,该第一补偿电容器的第一板接收待补偿的参考电压,且该第一补偿电容器的第二板接收该第一逻辑电路的输出,其中该第一逻辑电路执行逻辑运算于该循续渐近式模拟至数字转换器的输出码;及多个码相依补偿单元,每一个该码相依补偿单元包含第二逻辑电路与第二补偿电容器,该第二补偿电容器的第一板接收待补偿的该参考电压,且该第二补偿电容器的第二板接收该第二逻辑电路的输出,其中该第二逻辑电路执行逻辑运算于该循续渐近式模拟至数字转换器的输出码及代表切换数字至模拟转换器的底板电压的至少一个逻辑值;其中n位循续渐近式模拟至数字转换器最多使用(n-1)个该码独立补偿单元,该循续渐近式模拟至数字转换器的第k次切换最多使用(k-1)个该码相依补偿单元,其中n为大于1的正整数且k为1至(n-1)的正整数。

本发明的目的还可以采用以下的技术措施来进一步实现。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该输出码包含差动信号对,用以让该第一逻辑电路执行逻辑运算。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该第一逻辑电路所执行的逻辑运算包含或(OR)逻辑运算。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该输出码包含输出码对,其包含B

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该第二逻辑电路根据以下真值表,于取样期间与转换期间执行逻辑运算:

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中仅使用第m次及其之后的该码独立补偿单元与该码相依补偿单元,但是借由加入冗余以容忍未受补偿所造成错误,其中m为大于2的正整数。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中仅使用该第一及第二补偿电容器的电容值大于预设临界值的该码独立补偿单元与该码相依补偿单元。

前述的适用于循续渐近式模拟至数字转换器的参考涟波抑制电路,其中该码独立补偿单元与该码相依补偿单元的最大数目与该循续渐近式模拟至数字转换器的切换数呈线性增加。

本发明的目的还采用以下技术方案来实现。依据本发明提出的一种循续渐近式模拟至数字转换器,包含:至少一个切换数字至模拟转换器,接收输入信号以产生输出信号;比较器,接收该输出信号;循续渐近式控制器,根据该比较器的比较输出以产生输出码;参考缓冲器,产生参考电压给该切换数字至模拟转换器;及参考涟波抑制电路,用以抑制该参考电压的参考涟波,该参考涟波抑制电路包含:

多个码独立补偿单元,每一个该码独立补偿单元包含第一逻辑电路与第一补偿电容器,该第一补偿电容器的第一板接收该参考电压,且该第一补偿电容器的第二板接收该第一逻辑电路的输出,其中该第一逻辑电路执行逻辑运算于该循续渐近式模拟至数字转换器的输出码;及多个码相依补偿单元,每一个该码相依补偿单元包含第二逻辑电路与第二补偿电容器,该第二补偿电容器的第一板接收该参考电压,且该第二补偿电容器的第二板接收该第二逻辑电路的输出,其中该第二逻辑电路执行逻辑运算于该循续渐近式模拟至数字转换器的输出码及代表该切换数字至模拟转换器的底板电压的至少一逻辑值;其中n位循续渐近式模拟至数字转换器最多使用(n-1)个该码独立补偿单元,该循续渐近式模拟至数字转换器的第k次切换最多使用(k-1)个该码相依补偿单元,其中n为大于1的正整数且k为1至(n-1)的正整数。

前述的循续渐近式模拟至数字转换器,其中该输出码包含差动信号对,用以让该第一逻辑电路执行逻辑运算。

前述的循续渐近式模拟至数字转换器,其中该第一逻辑电路所执行的逻辑运算包含或(OR)逻辑运算。

前述的循续渐近式模拟至数字转换器,其中该输出码包含输出码对,其包含B

前述的循续渐近式模拟至数字转换器,其中该第二逻辑电路根据以下真值表,于取样期间与转换期间执行逻辑运算:

前述的循续渐近式模拟至数字转换器,其中仅使用第m次及其之后的该码独立补偿单元与该码相依补偿单元,但是借由加入冗余以容忍未受补偿所造成错误,其中m为大于2的正整数。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

图1是本发明实施例的具低复杂度码相依参考涟波抑制的循续渐近式模拟至数字转换器(SAR ADC)的方块图。

图2是本发明实施例的参考涟波抑制电路(图1)的码独立补偿单元的电路图。

图3显示本发明实施例的码相依补偿单元的电路图。

图4A至图4D例示4位模拟至数字转换器的补偿机制。

【符号说明】

100:循续渐近式模拟至数字转换器

11A:第一数字至模拟转换器

11B:第二数字至模拟转换器

12:启动开关

13:比较器

14:循续渐近式控制器

15:参考缓冲器

16:参考涟波抑制电路

16A:码独立补偿单元

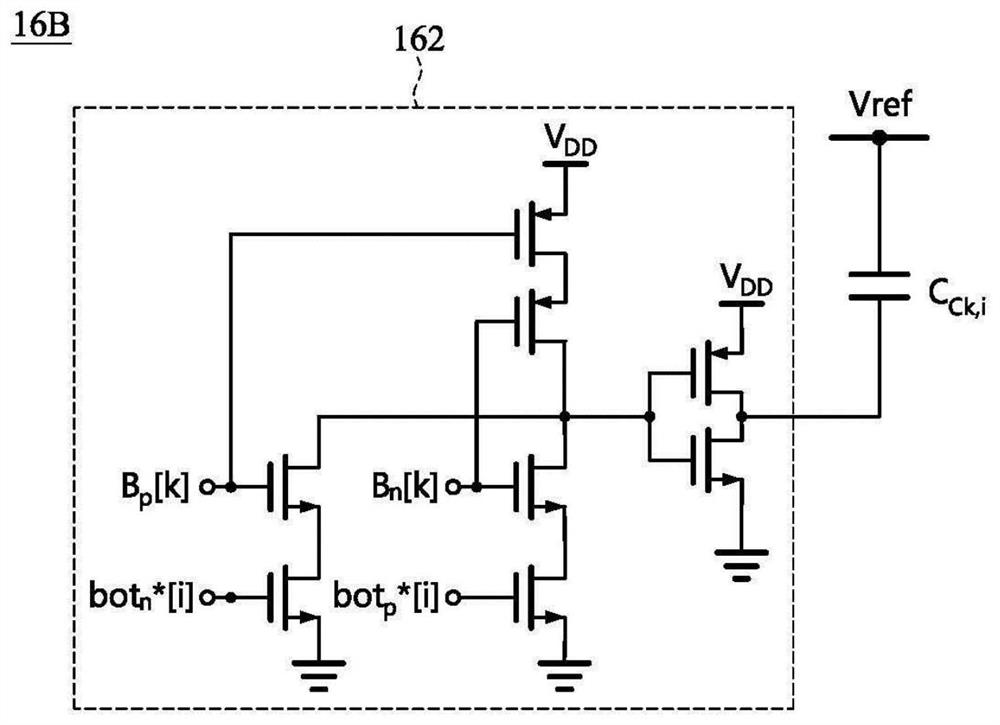

16B:码相依补偿单元

161:第一逻辑电路

162:第二逻辑电路

V

Vref:参考电压

Vip:第一输入信号

Vin:第二输入信号

Vop:第一输出信号

Von:第二输出信号

B

B

B

B

bot

bot

C

C

C

C

具体实施方式

为更进一步阐述本发明为达成预定发明目的所采取的技术手段及功效,以下结合附图及较佳实施例,对依据本发明提出的循续渐近式模拟至数字转换器及其参考涟波抑制电路的具体实施方式、结构、特征及其功效,详细说明如后。

图1显示本发明实施例的具低复杂度码相依(low-complexity code-dependent)参考涟波抑制(reference ripple suppression)的循续渐近式模拟至数字转换器(SARADC)100的方块图。

在本实施例中,循续渐近式模拟至数字转换器100(以下简称模拟至数字转换器)可包含至少一个切换数字至模拟转换器(switched digital-to-analog converter,switched DAC),例如第一数字至模拟转换器(DAC)11A(例如电容数组)与第二数字至模拟转换器(DAC)11B(例如电容数组),经由启动开关(bootstrapped switch)12以分别接收第一输入信号Vip与第二输入信号Vin,藉以分别产生第一输出信号Vop与第二输出信号Von。

本实施例的模拟至数字转换器100可包含比较器13,分别于第一输入节点(例如正(+)输入节点)与第二输入节点(例如负(-)输入节点)接收第一输出信号Vop与第二输出信号Von。模拟至数字转换器100可包含循续渐近式(SAR)控制器14,根据比较器13的比较输出,从最高有效位(MSB)至最低有效位(LSB)依序以产生输出码。模拟至数字转换器100可根据比较器13的比较输出以控制切换第一数字至模拟转换器11A与第二数字至模拟转换器11B。本实施例使用差动信号(differential signaling)机制,因此输出码可包含差动信号对,例如输出码对(code pair),其包含B

在本实施例中,模拟至数字转换器100可包含参考缓冲器(referencebuffer)15,用以产生参考电压Vref,提供给第一数字至模拟转换器11A与第二数字至模拟转换器11B。根据本实施例的特征之一,模拟至数字转换器100可包含参考涟波抑制(reference ripplesuppression)电路16,用以抑制参考电压Vref的参考涟波,其可包含多个码独立(code-independent)补偿单元16A与码相依(code-dependent)补偿单元16B。

图2显示本发明实施例的参考涟波抑制电路16(图1)的码独立(code-independent)补偿单元16A的电路图。在本实施例中,对于(第一数字至模拟转换器11A与第二数字至模拟转换器11B的)每一次切换,使用一个码独立补偿单元16A。码独立补偿单元16A可包含第一逻辑电路161与第一补偿电容器C

其中C

码独立补偿单元16A接收输出码对,其包含B

图3显示本发明实施例的码相依(code-dependent)补偿单元16B的电路图。在本实施例中,对于(第一数字至模拟转换器11A与第二数字至模拟转换器11B的)第k次切换,最多使用(k-1)个码相依补偿单元16B。第k次切换的第i个码相依补偿单元16B可包含第二逻辑电路162与第二补偿电容器C

码相依补偿单元16B接收输出码对,其包含B

表1

图4A至图4D例示4位模拟至数字转换器100于取样期间与转换期间的补偿机制,其显示(码独立补偿单元16A的)第k次切换的第一补偿电容器C

于取样期间(图4A),码独立补偿单元16A与码相依补偿单元16B的输出为“0”,因此所有第一、第二补偿电容器接地。接着,如图4B所示,于转换期间的第1次切换,所产生输出码的第一位B

值得注意的是,并非需要使用所有的码独立补偿单元16A与码相依补偿单元16B。在一个实施例中,仅使用第m次及其之后的码独立补偿单元16A与码相依补偿单元16B,但是借由加入冗余(redundancy)以容忍未受补偿所造成错误(其中m为大于2的正整数,例如m=3)。

在另一实施例中,仅使用具大电容值的第一及第二补偿电容器的码独立补偿单元16A与码相依补偿单元16B。在本说明书中,大电容一词是指大于预设临界值的电容。

根据上述实施例,码独立补偿单元16A与码相依补偿单元16B的最大数目与模拟至数字转换器100的切换数(或位元数)仅呈线性增加。反观传统循续渐近式模拟至数字转换器,例如美国专利第10,236,903号,题为“电荷补偿电路及其模拟至数字转换器(CHARGECOMPENSATION CIRCUIT AND ANALOG-TO-DIGITAL CONVERTER WITH THE SAME)”,其补偿单元的数目与循续渐近式模拟至数字转换器的切换数(或位元数)则呈指数(exponentially)增加。

以上所述,仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

- 循续渐近式模拟至数字转换器及其参考涟波抑制电路

- 高线性度的循续渐近式模拟至数字转换器