半导体存储装置

文献发布时间:2023-06-19 11:21:00

[相关申请案]

本申请案享有以日本专利申请案2019-222788号(申请日:2019年12月10日)为基础申请案的优先权。本申请案通过参考该基础申请案而包含基础申请案的全部内容。

技术领域

实施方式涉及一种半导体存储装置。

背景技术

作为半导体存储装置,已知有NAND(Not AND,与非)型快闪存储器。

发明内容

实施方式提供一种能够减少电路元件数量的半导体存储装置。

实施方式的半导体存储装置包括:源极线;位线;第1存储单元;第1选择晶体管,配置在所述第1存储单元与所述源极线之间;第2选择晶体管,配置在所述第1存储单元与所述位线之间;第3选择晶体管,配置在所述源极线与所述位线之间,且与所述第1选择晶体管不同;及控制电路;所述第1选择晶体管及所述第3选择晶体管连接到所述源极线,所述控制电路在对所述第1存储单元进行擦除动作时,对所述源极线施加第1电压的期间,对所述第3选择晶体管的栅极施加低于所述第1电压的第2电压,通过对所述源极线施加所述第1电压、及对所述第3选择晶体管的栅极施加所述第2电压,而在对所述位线施加第3电压期间,对所述第2选择晶体管的栅极施加低于所述第3电压的第4电压。

附图说明

图1是表示包括第1实施方式的半导体存储装置的存储系统的构成的一例的框图。

图2是表示第1实施方式的半导体存储装置的构成的一例的框图。

图3是表示第1实施方式的半导体存储装置中的存储单元阵列的电路构成的一例的图。

图4是表示第1实施方式的半导体存储装置的截面构造的一例的剖视图。

图5是表示第1实施方式的半导体存储装置的由存储单元晶体管形成的阈值电压分布的一例的图。

图6是表示第1实施方式的半导体存储装置的感测放大器模块的电路构成的一例的图。

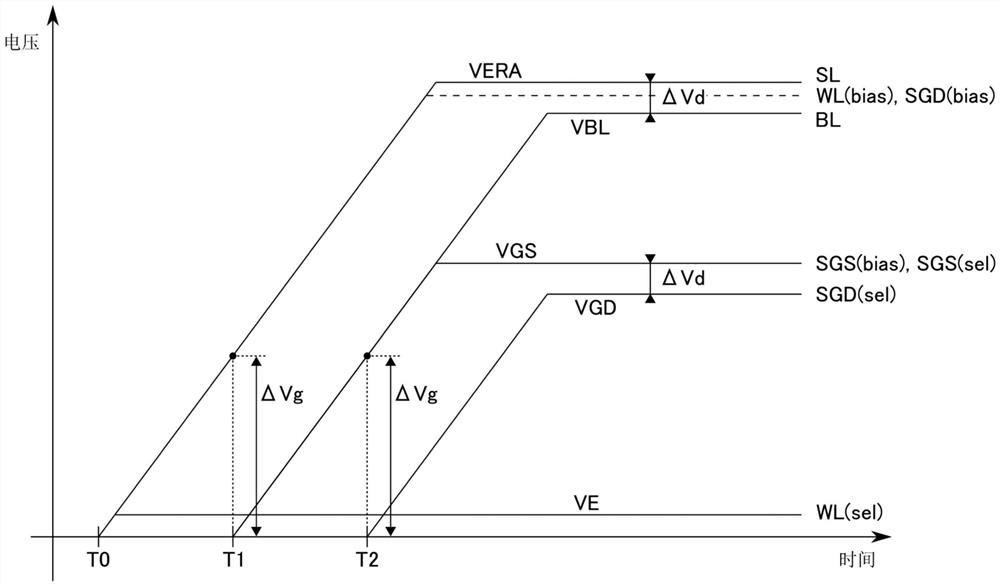

图7是表示第1实施方式的半导体存储装置中的擦除动作中利用的对各种布线施加的电压的时间变化的一例的时序图。

图8是用来说明第1实施方式的半导体存储装置中的擦除动作的示意图。

具体实施方式

以下,参考附图对实施方式进行说明。在以下的说明中,对具有相同功能及构成的构成要素标注共通的参考符号。此外,当要区分具有共通的参考符号的多个构成要素时,对该共通的参考符号标注下标来进行区分。当对于多个构成要素无需特别进行区分时,对该多个构成要素仅标注共通的参考符号而不标注下标。

<第1实施方式>

以下,对第1实施方式的半导体存储装置1进行说明。

[构成例]

(1)存储系统

图1是表示包括第1实施方式的半导体存储装置1的存储系统3的构成一例的框图。

如图1所示,存储系统3包括半导体存储装置1及存储器控制器2,且由主机装置4进行控制。存储系统3例如为SSD(Solid State Drive,固态硬盘)或SD

半导体存储装置1由存储器控制器2控制。存储器控制器2从主机装置4接收命令,且基于该接收的命令控制半导体存储装置1。

存储器控制器2包括:主机接口电路21、CPU(Central Processing Unit,中央处理器)22、RAM(Random Access Memory,随机存取存储器)23、ROM(Read Only Memory,只读存储器)24、及存储器接口电路25。存储器控制器2例如构成为SoC(System-on-a-Chip,片上系统)。

ROM24存储固件(程序)。RAM23能够保存该固件,且用作CPU22的工作区。RAM23进而暂时保存数据,作为缓冲器及高速缓冲存储器发挥功能。ROM24中存储着并加载到RAM23上的固件由CPU22执行。由此,存储器控制器2执行包括写入动作、读出动作、及擦除动作等的各种动作、以及主机接口电路21及存储器接口电路25的一部分功能。

主机接口电路21经由主机接口连接到主机装置4,掌管存储器控制器2与主机装置4之间的通信。例如,主机接口电路21接收来自主机装置4的命令。存储器接口电路25经由存储器接口连接到半导体存储装置1,掌管存储器控制器2与半导体存储装置1之间的通信。例如,存储器接口电路25基于来自主机装置4的命令,发出包含指令及地址信息的指令序列并发送到半导体存储装置1。存储器接口例如传输芯片使能信号CEn、指令锁存使能信号CLE、地址锁存使能信号ALE、写入使能信号WEn、读出使能信号REn、写入保护信号WPn、就绪/忙碌信号R/Bn、及信号DQ。

(2)半导体存储装置

图2是表示第1实施方式的半导体存储装置1的构成的一例的框图。第1实施方式的半导体存储装置1是例如能够非易失性存储数据的NAND型快闪存储器。

半导体存储装置1包括存储单元阵列11及外围电路。外围电路包括:感测放大器模块12、行译码器模块13、输入输出电路14、寄存器15、逻辑控制电路16、定序器17、就绪/忙碌控制电路18、及电压产生电路19。在半导体存储装置1中,执行使存储单元阵列11存储写入数据DAT的写入动作、将读出数据DAT从存储单元阵列11读出的读出动作、及将存储单元阵列11中存储的数据擦除的擦除动作等各种动作。

存储单元阵列11包括块BLK0~BLKn(n为1以上的整数)。块BLK包括与位线及字线建立关联的多个非易失性存储单元,且例如成为数据的擦除单位。半导体存储装置1中,例如能够适应SLC(Single-Level Cell,单层单元)方式或MLC(Multi-Level Cell,多层单元)方式。SLC方式是在各存储单元中保存1位数据,MLC方式是在各存储单元保存2位数据。此外,也可在各存储单元中保存3位以上的数据。

输入输出电路14控制与存储器控制器2的信号DQ的输入输出。信号DQ可包括指令CMD、数据DAT、地址信息ADD、及状态信息STS等。指令CMD例如包括用来执行来自主机装置4的命令的命令。数据DAT包括写入数据DAT或读出数据DAT。地址信息ADD例如包括列地址及行地址。状态信息STS例如包括与关于写入动作、读出动作、及擦除动作的结果的半导体存储装置1的状态相关的信息。

更具体来说,输入输出电路14包括输入电路及输出电路,输入电路及输出电路进行以下所述的处理。输入电路从存储器控制器2接收写入数据DAT、地址信息ADD、及指令CMD。输入电路将收到的写入数据DAT传送到感测放大器模块12,且将收到的地址信息ADD及指令CMD传送到寄存器15。输出电路从寄存器15接收状态信息STS,且从感测放大器模块12接收读出数据DAT。输出电路将收到的状态信息STS或读出数据DAT发送到存储器控制器2。输出电路也可将收到的状态信息STS及读出数据DAT一同地发送到存储器控制器2。此处,输入输出电路14与感测放大器模块12经由数据总线而连接。数据总线例如包括与信号DQ0~DQ7对应的8条数据线IO0~IO7。此外,数据线IO的条数不限于8条,例如也可为16条或32条,能够任意设定。

寄存器15包括状态寄存器151、地址寄存器152、及指令寄存器153。

状态寄存器151保存状态信息STS,且基于定序器17的指示将该状态信息STS传送到输入输出电路14。

地址寄存器152保存从输入输出电路14传送的地址信息ADD,且将地址信息ADD传送到定序器17。另外,地址寄存器152将地址信息ADD中的列地址传送到感测放大器模块12,且将地址信息ADD中的行地址传送到行译码器模块13。

指令寄存器153保存从输入输出电路14传送的指令CMD,且将指令CMD传送到定序器17。

逻辑控制电路16从存储器控制器2接收例如芯片使能信号CEn、指令锁存使能信号CLE、地址锁存使能信号ALE、写入使能信号WEn、读出使能信号REn、及写入保护信号WPn。逻辑控制电路16基于收到的信号,控制输入输出电路14及定序器17。

芯片使能信号CEn是用于启用半导体存储装置1的信号。指令锁存使能信号CLE是用于对输入输出电路14通知输入到半导体存储装置1的信号DQ为指令CMD的信号。地址锁存使能信号ALE是用于对输入输出电路14通知输入到半导体存储装置1的信号DQ为地址信息ADD的信号。写入使能信号WEn及读出使能信号REn分别是用于例如命令输入输出电路14输入及输出信号DQ的信号。写入保护信号WPn是用于指示半导体存储装置1禁止数据写入及擦除的信号。

定序器17接收指令CMD及地址信息ADD,按照该接收的指令CMD及地址信息ADD控制半导体存储装置1整体的动作。例如,定序器17控制感测放大器模块12、行译码器模块13、及电压产生电路19等,执行写入动作、读出动作、及擦除动作等各种动作。

就绪/忙碌控制电路18按照定序器17的控制,产生就绪/忙碌信号R/Bn,并将产生的就绪/忙碌信号R/Bn发送到存储器控制器2。就绪/忙碌信号R/Bn是用于通知半导体存储装置1处于受理来自存储器控制器2的命令的就绪状态还是处于不受理命令的忙碌状态的信号。

电压产生电路19基于定序器17的控制,产生各种电压,并向存储单元阵列11、感测放大器模块12、及行译码器模块13等供给该产生的电压。

感测放大器模块12从地址寄存器152接收列地址,并将收到的列地址译码。感测放大器模块12基于该译码的结果,执行存储器控制器2与存储单元阵列11之间的数据DAT的传送动作。也就是说,感测放大器模块12感测存储单元阵列11内的存储单元晶体管的阈值电压,产生读出数据DAT,且经由输入输出电路14将产生的读出数据DAT输出到存储器控制器2。另外,感测放大器模块12从存储器控制器2经由输入输出电路14接收写入数据DAT,并将收到的写入数据DAT传送到存储单元阵列11。

行译码器模块13从地址寄存器152接收行地址,并将收到的行地址译码。行译码器模块13基于该译码的结果,选择执行各种动作的对象的块BLK。行译码器模块13能够将从电压产生电路19供给的电压传送到该选择的块BLK。

(3)存储单元阵列

图3表示第1实施方式的半导体存储装置1中的存储单元阵列11的电路构成的一例。作为存储单元阵列11的电路构成的一例,示出了存储单元阵列11中包含的多个块BLK中的块BLK0及BLK1的电路构成的一例。块BLK0与块BLK1具有同等的电路构成。例如,存储单元阵列11中包含的其它块BLK也具有与块BLK0及BLK1同等的电路构成。

如图3所示,各块BLK例如包括4个字符串单元SU0~SU3。各字符串单元SU包括多个NAND字符串NS。各NAND字符串NS连接到位线BL0~BLm(m为1以上的整数)中对应的位线BL,且例如包括存储单元晶体管MT0~MT7以及选择晶体管ST1及ST2。各存储单元晶体管MT包括控制栅极(以下也称为栅极)及电荷储存层,且非易失性存储数据。选择晶体管ST1及ST2各自用于各种动作时选择包括该选择晶体管ST1及ST2的NAND字符串NS。

各NAND字符串NS的选择晶体管ST1的漏极连接到所述对应的位线BL。在选择晶体管ST1的源极与选择晶体管ST2的漏极之间,串联有存储单元晶体管MT0~MT7。选择晶体管ST2的源极连接到源极线SL。

同一块BLK的同一字符串单元SUj中包含的NAND字符串NS各自的选择晶体管ST1的栅极共通连接到选择栅极线SGDj。此处,在图3的例子中,j是0到3的任一整数。同一块BLK中包含的NAND字符串NS各自的选择晶体管ST2的栅极共通连接到选择栅极线SGS。同一块BLK中包含的NAND字符串NS各自的存储单元晶体管MTk的栅极共通连接到字线WLk。此处,在图3的例子中,k是0到7的任一整数。例如,不同块BLK之间,使用未电连接的不同的布线作为这些选择栅极线SGD及SGS以及字线WL的各布线。

各位线BL共通连接到同一块BLK的字符串单元SU各自之中包含的对应的NAND字符串NS的选择晶体管ST1的漏极。另外,各位线BL例如在不同块BLK中也同样地连接,由此,在块BLK之间共用。

源极线SL共通连接到同一块BLK中包含的NAND字符串NS各自的选择晶体管ST2的源极,由此,在该块BLK的字符串单元SU之间共用。另外,源极线SL例如在不同块BLK中也同样地连接,由此,在块BLK之间共用。

1个字符串单元SU中的共通连接到某字线WL的存储单元晶体管MT的集合例如称为单元组件CU。例如,将单元组件CU内的存储单元晶体管MT各自中保存的同位的1位数据的集合例如称为“1页数据”。

以上对存储单元阵列11的电路构成进行了说明,但存储单元阵列11的电路构成不限于以上所述。例如,能够将各块BLK包含的字符串单元SU的个数设计成任意个数。另外,能够将各NAND字符串NS包含的存储单元晶体管MT以及选择晶体管ST1及ST2分别设计成任意个数。字线WL以及选择栅极线SGD及SGS的条数是分别基于NAND字符串NS中的存储单元晶体管MT以及选择晶体管ST1及ST2的个数进行变更。

(4)半导体存储装置的截面构造

图4是表示第1实施方式的半导体存储装置1的截面构造的一例的剖视图。在图4的例子中,省略了层间绝缘体。图4所图示的截面构造仅为一例,半导体存储装置1的截面构造不限于图示。

半导体存储装置1包括半导体衬底31。此处,将与半导体衬底31的面平行的例如相互正交的2个方向定义为x方向及y方向,将例如与半导体衬底31的面正交且形成存储单元阵列11的方向定义为z方向。以下,将z方向设为“上”,将与z方向相反的方向设为“下”进行说明,但这个记法仅为方便起见,与例如重力方向没有关系。

半导体存储装置1包括设置在半导体衬底31上方的存储单元部100。在存储单元部100设置有存储单元阵列11。具体来说,存储单元部100中,三维状排列着图3所示的存储单元晶体管MT。包括导电体43及导电体45的积层体、以及该积层体内的存储柱MP构成存储单元阵列11的一部分构造。在半导体衬底31与存储单元部100之间设置有例如构成图2所示的外围电路的电路元件。

以下,详细地对存储单元部100的构造进行说明。

在半导体衬底31的上方设置有导电体41。导电体41例如包含掺杂有磷等N型杂质的多晶硅(Si)、或金属。导电体41作为源极线SL发挥功能。在导电体41的上方,隔着绝缘体设置有导电体43。导电体43作为选择栅极线SGS发挥功能。

在图4的例子中,在导电体43的上方,9层导电体45隔着绝缘体依次积层在各导电体间。导电体45分别例如从接近半导体衬底31的一侧,依次作为字线WL0、字线WL1、字线WL2、……、字线WL7、选择栅极线SGD发挥功能。

导电体45、导电体43、及导电体41中设置有存储柱MP。1个存储柱MP相当于1个NAND字符串NS中包含的存储单元晶体管MT0~MT7以及选择晶体管ST1及ST2所在的区域。存储柱MP例如在z方向上延伸。例如,存储柱MP的上端位于比最上方导电体45的上表面更靠上方,存储柱MP的下端位于比导电体41的上表面更靠下方。

存储柱MP例如包括核心部471、半导体472、隧道氧化膜473、绝缘膜474、阻挡绝缘膜475、及半导体476。柱状核心部471的上端位于比最上方导电体45的上表面更靠上方,核心部471的下端位于比导电体41的上表面更靠下方。核心部471的侧面及下表面由半导体472所覆盖。半导体472的上表面位于比核心部471的上表面更靠上方。半导体472的侧面中的导电体41的上表面与下表面之间的某区域与导电体41接触。在除该区域以外的半导体472的侧面及下表面上,以隧道氧化膜473、绝缘膜474、及阻挡绝缘膜475的顺序设置有隧道氧化膜473、绝缘膜474、及阻挡绝缘膜475。在核心部471的上表面上设置有半导体476。半导体476的侧面由半导体472所覆盖。半导体472作为存储单元晶体管MT及选择晶体管ST的通道发挥功能。绝缘膜474作为电荷储存层发挥功能。存储柱MP中与导电体43相交的部分例如作为选择晶体管ST2发挥功能。存储柱MP中与导电体45相交的部分分别例如从接近半导体衬底31的一侧,依次作为存储单元晶体管MT0、存储单元晶体管MT1、……、存储单元晶体管MT7、选择晶体管ST1发挥功能。

在半导体472及476的上表面上设置有柱状接触插塞CP。各接触插塞CP的上表面与被设置位线的层中的1个导电体51接触。导电体51作为位线BL发挥功能。导电体51例如在y方向上延伸。多个导电体51例如沿x方向相互具有间隔地设置。

在导电体45、导电体43、及导电体41中设置有分隔区域SR。分隔区域SR例如以在与x方向及z方向对应的xz平面上板状展开的方式设置。分隔区域SR的上端位于比最上方导电体45的上表面更靠上方,分隔区域SR的下端位于比导电体41的上表面更靠下方且比导电体41的下表面更靠上方。通过分隔区域SR将导电体45及导电体43分隔。多个分隔区域SR例如沿y方向相互具有间隔地设置。在相邻的分隔区域SR间设置有例如1个块BLK。如图4所图示,不同的块BLK的存储柱MP共通连接到同一导电体51。由此,位线BL在块BLK之间共用。另一方面,导电体41未被分隔区域SR分隔。由此,源极线SL在块BLK之间共用。

另外,在导电体41上设置有导电体LI。导电体LI例如以在与x方向及z方向对应的xz平面上板状展开的方式设置。导电体LI作为源极线接点发挥功能。

(5)存储单元晶体管的阈值电压分布

图5表示图3所示的存储单元阵列11中的各存储单元晶体管MT保存2位数据时的阈值电压分布、数据分配、及读出电压的一例。

存储单元晶体管MT基于能够将该存储单元晶体管MT从断开状态切换成接通状态的栅极、源极间的最小电位差(以下称为阈值电压),保存所述2位数据。在写入动作中,通过将电子注入到存储单元晶体管MT的电荷储存层而进行使该存储单元晶体管MT的阈值电压上升的程序动作。

图5表示作为这种阈值电压的控制结果而形成的4个阈值电压分布。在图5所示的阈值电压分布中,纵轴对应于存储单元晶体管MT的个数,横轴对应于存储单元晶体管MT的阈值电压Vth。在横轴中,作为一例,示出了对存储单元晶体管MT的源极施加例如基准电压VSS时能够将该存储单元晶体管MT从断开状态切换成接通状态的施加至该存储单元晶体管MT的栅极的最低的电压。

例如,根据存储单元晶体管MT的阈值电压包含在这4个阈值电压分布的哪一个中,将该存储单元晶体管MT区分为处于“Er”状态、“A”状态、“B”状态、及“C”状态中的任一状态。按照存储单元晶体管MT处于“Er”状态、“A”状态、“B”状态、“C”状态的顺序,该存储单元晶体管MT的阈值电压变高。例如,对“Er”状态分配“11”(“高位/低位”)数据,对“A”状态分配“01”数据,对“B”状态分配“00”数据,对“C”状态分配“10”数据。对各状态分配的数据是存储在处于该状态的存储单元晶体管MT中的数据。

在读出动作中,判定存储单元晶体管MT处于哪一个状态。设定读出动作中使用的读出电压。具体来说,对应“A”状态设定读出电压AR,对应“B”状态设定读出电压BR,对应“C”状态设定读出电压CR。

在擦除动作中,通过从存储单元晶体管MT的电荷储存层去除电子,而进行使该存储单元晶体管MT的阈值电压下降而包含在“Er”状态的阈值电压分布中的动作。

另外,在擦除动作中,也进行确认存储单元晶体管MT的阈值电压是否低于特定电压的擦除验证动作。设定擦除验证动作中使用的擦除验证电压(未图示)。擦除验证电压例如设定为始终高于处于“Er”状态的存储单元晶体管MT的阈值电压,而且低于读出电压AR。

此外,以上说明的1个存储单元晶体管MT中存储的数据的位数与对所述阈值电压分布的数据分配仅为一例,但不限于此。

(6)感测放大器模块

图6表示第1实施方式的半导体存储装置1的感测放大器模块12的一部分电路构成的一例。此外,以下详细说明的感测放大器模块12的构成仅为一例,作为感测放大器模块12,能够适应各种构成。在以下说明中,将写入对象或读出对象的存储单元晶体管MT称为选择存储单元晶体管MT。

感测放大器模块12包括例如设置在每个位线BL的感测放大器单元SAU。以下,以例说明连接到某位线BL的感测放大器单元SAU的构成。例如,连接到其它位线BL的感测放大器单元SAU也具有相同的构成。

感测放大器单元SAU例如包括n通道MOS晶体管Tr1及Tr2以及感测放大器电路SA。

晶体管Tr1的第1端子连接到位线BL,晶体管Tr1的第2端子连接到晶体管Tr2的第1端子。对晶体管Tr1的栅极施加控制信号BLS。晶体管Tr2的第2端子连接到感测放大器电路SA,对晶体管Tr2的栅极施加控制信号BLC。通过晶体管Tr1,能够控制位线BL与感测放大器电路SA之间的电连接。通过晶体管Tr2,能够将位线BL钳位为与控制信号BLC对应的电位。控制信号BLS及BLC例如利用定序器17供给。

对感测放大器电路SA的某端子施加电压VDD,对感测放大器电路SA的其他端子施加电压VSS。感测放大器电路SA能够将这些电压传送到位线BL。由此,在读出动作及写入动作中,感测放大器电路SA能够以如下所述的方式进行动作。

在读出动作中,感测放大器电路SA基于流入位线BL的电流或该位线BL的电位,感测电连接到该位线BL的选择存储单元晶体管MT的阈值电压。由此,感测放大器电路SA读出该选择存储单元晶体管MT中存储的数据。感测放大器电路SA能够将该读出的数据发送到输入输出电路14。

另外,在写入动作中,感测放大器电路SA从输入输出电路14接收数据。感测放大器电路SA将基于该收到的数据的电压施加到位线BL。由此,可使电连接到该位线BL的选择存储单元晶体管MT的阈值电压例如上升,将数据存储到该选择存储单元晶体管MT。

[动作例]

对第1实施方式的半导体存储装置1中执行的擦除动作进行说明。以下,为使说明简洁而省略对擦除动作中的擦除验证动作的说明。

(1)GIDL擦除动作的概要

半导体存储装置1在擦除动作中分别在擦除动作的对象的块BLK的选择晶体管ST1及ST2中产生GIDL(Gate-Induced Drain Leakage,栅致漏极泄漏)电流。以下,列举擦除动作的对象的块BLK的某个存储柱MP为例,对该存储柱MP的选择晶体管ST1及ST2的控制进行说明,该块BLK的其它存储柱MP也情况相同。

例如,当源极线SL的电位比选择晶体管ST2的栅极的电位高电位差ΔVα以上时,产生GIDL电流(以下也称为SL侧GIDL电流)。与SL侧GIDL电流对应的电子向源极线SL侧移动,伴随SL侧GIDL电流产生的电洞供给到存储柱MP内。同样地,当对应的位线BL的电位比选择晶体管ST1的栅极的电位高电位差ΔVβ以上时,产生GIDL电流(以下也称为BL侧GIDL电流)。与BL侧GIDL电流对应的电子向位线BL侧移动,伴随BL侧GIDL电流产生的电洞供给到存储柱MP内。在这些GIDL电流的产生中,例如优选在成为选择晶体管ST1及/或ST2的漏极的区域掺杂N型杂质。另外,产生这些GIDL电流时的源极线SL与选择晶体管ST2的栅极的电位差及位线BL与选择晶体管ST1的栅极的电位差例如出于防止选择晶体管ST1及ST2破坏的目的,优选为电位差ΔVg th以内。电位差ΔVg th大于电位差ΔVα及ΔVβ。

半导体存储装置1利用该原理产生GIDL电流。供给到存储柱MP内的电洞与该存储柱MP的存储单元晶体管MT的电荷储存层中的电子结合。由此,使该存储单元晶体管MT的阈值电压下降,包含在“Er”状态的阈值电压分布中。

(2)GIDL擦除动作中使用的各种电压的例子

图7是表示在第1实施方式的半导体存储装置1中的擦除动作中利用的对各种布线施加的电压的时间变化的一例的时序图。以下详细说明的擦除动作仅为一例,本实施方式的擦除动作不限于此。此外,以下,当对施加到某布线的电压等进行说明时,除非之后明确说明对该布线施加其它电压、或将该布线设为浮置状态,否则继续对该布线施加该电压。

图7表示对擦除动作的对象的块BLK的布线施加的电压的时间变化的一例。以下,将擦除动作的对象的块BLK称为选择块BLK(sel)。另外,将选择块BLK(sel)的字线WL以及选择栅极线SGS及SGD分别称为字线WL(sel)以及选择栅极线SGS(sel)及SGD(sel)。图7表示分别对与选择块BLK(sel)中举例说明的存储柱MP对应的某个字线WL(sel)及某1个选择栅极线SGD(sel)施加的电压的时间变化。以下,对分别施加到该字线WL(sel)及该选择栅极线SGD(sel)的电压的控制进行说明,但分别施加到其它字线WL(sel)及选择栅极线SGD(sel)的电压也以同样方式控制。

另外,图7也表示对与选择块BLK(sel)不同的某块BLK的布线施加的电压的时间变化的一例。以下,为了使说明简洁,而将该块BLK称为偏压块BLK(bias)。另外,将偏压块BLK(bias)的字线WL以及选择栅极线SGS及SGD分别称为字线WL(bias)以及选择栅极线SGS(bias)及SGD(bias)。图7表示分别对与偏压块BLK(bias)中举例说明的存储柱MP对应的某个字线WL(bias)及某个选择栅极线SGD(bias)施加的电压的时间变化。以下,对分别施加到该字线WL(bias)及该选择栅极线SGD(bias)的电压的控制进行说明,但分别施加到其它字线WL(bias)及选择栅极线SGD(bias)的电压也以同样方式控制。以下,列举偏压块BLK(bias)的1个存储柱MP为例,进行与该存储柱MP中的GIDL电流的产生的控制相关的说明,但该块BLK(bias)的其它存储柱MP也情况相同。

行译码器模块13按照定序器17的控制,选择用作偏压块BLK(bias)的块BLK。该偏压块BLK(bias)的选择也可基于经选择的擦除动作对象的块BLK。或者,用作偏压块BLK(bias)的块BLK也可在半导体存储装置1中预先设定。在此情况下,例如也可在包含以沿某方向依次相邻的方式设置的多个块BLK的平面,将位于端的块BLK设定为偏压块BLK(sel)。

行译码器模块13能够将从电压产生电路19供给的电压传送到偏压块BLK(bias)。可用作偏压块BLK(bias)的块BLK例如不用作被存储数据的区域。也就是说,偏压块BLK(bias)中的存储单元晶体管MT分别具有包含在“Er”状态的阈值电压分布中的阈值电压。或者,可用作偏压块BLK(bias)的块BLK也可用作被存储数据的区域。

如上所述,在选择块BLK(sel)与偏压块BLK(bias)之间,共用各位线BL及源极线SL。举例说明的2个存储柱MP设为连接到同一位线BL。图7中表示分别对与该2个存储柱对应的1个位线BL及源极线SL施加的电压的时间变化。以下,对施加到该位线BL的电压的控制进行说明,但施加到这些位线BL中的其它位线BL的电压也以同样方式控制。

电压对字线WL以及选择栅极线SGS及SGD的施加例如通过定序器17对电压产生电路19及行译码器模块13的控制而执行。电压对源极线SL的施加例如通过定序器17对电压产生电路19的控制而执行。电压对位线BL的施加例如通过定序器17对电压产生电路19及感测放大器模块12的控制而执行。

在图7的例中,开始擦除动作前,分别对字线WL(sel)及WL(bias)、选择栅极线SGS(sel)、SGD(sel)、SGS(bias)、及SGD(bias)、位线BL、以及源极线SL施加电压VSS。

在时刻T0,施加到源极线SL的电压升压至电压VERA,对字线WL(sel)施加电压VE。电压VE是对选择块BLK(sel)的存储单元晶体管MT的栅极施加的选择电压。图7表示电压VE高于电压VSS,但不限于此,例如可为电压VSS,也可低于电压VSS。电压VERA高于电压VE。

另外,在时刻T0,字线WL(bias)及选择栅极线SGD(bias)设为浮置状态。相应于施加到源极线SL的电压升压,使分别施加到浮置状态的字线WL(bias)及选择栅极线SGD(bias)的电压升压。这是由于在字线WL(bias)及选择栅极线SGD(bias)各自与连接到源极线SL的导电体LI之间存在电容耦合。例如,字线WL(bias)及选择栅极线SGD(bias)各自的电位上升至接近源极线SL的电位。此外,字线WL(bias)及选择栅极线SGD(bias)设为浮置状态的时点不限定于时刻T0,可为时刻T0前,也可为时刻T0后。

在如上所述地对各布线施加电压的状况下,在偏压块BLK(bias)及选择块BLK(sel)中的任一个中,选择晶体管ST2都为断开状态,电子不从源极线SL流向存储柱MP内。

之后,在时刻T1,施加到选择栅极线SGS(bias)的电压升压至电压VGS。电压VGS高于电压VE。时刻T1例如为如下时刻,即,在如上所述地施加电压而使源极线SL的电位上升的过程中,源极线SL的电位比被施加电压VSS的选择栅极线SGS(bias)的电位仅高出电位差ΔVg。电位差ΔVg例如为电位差ΔVα及ΔVβ以上且为电位差ΔVg th以下。电压VGS例如为如下电压:在以此方式施加了电压的源极线SL及选择栅极线SGS(bias)的电位稳定时,源极线SL的电位比选择栅极线SGS(bias)的电位仅高出例如电位差ΔVg。在这种情况下,例如,在时刻T1以后,能够视作源极线SL的电位比选择栅极线SGS(bias)的电位仅高出电位差ΔVg。

因此,在时刻T1以后,在偏压块BLK(bias)的存储柱MP产生SL侧GIDL电流。在偏压块BLK(bias)中,字线WL(bias)为浮置状态。因此,伴随该SL侧GIDL电流而产生的电洞在偏压块BLK(bias)中未被擷取到电荷储存层,而能够在该存储柱MP内移动。

另外,在时刻T1,施加到连接到位线BL的晶体管Tr1的栅极的控制信号BLS为低电平。晶体管Tr1在低电平的控制信号BLS被施加到栅极期间为断开状态。施加到以此方式控制的位线BL的电压相应于SL侧GIDL电流的产生而升压,并升压至电压VBL。这是由于如上所述电洞能够在存储柱内移动,由此,例如传送施加到源极线SL的电压VERA。施加了电压VBL的位线BL的电位比施加了电压VERA的源极线SL的电位仅低了电位差ΔVd。电位差ΔVd相当于例如偏压块BLK(bias)的选择晶体管ST1的二极管阈值及选择晶体管ST2的二极管阈值之和。此外,晶体管Tr1成为断开状态的时点不限定于时刻T1。

进而,在时刻T1,施加到选择栅极线SGS(sel)的电压与选择栅极线SGS(bias)同样地升压至电压VGS。在这种情况下,例如,在时刻T1以后,能够视作源极线SL的电位比选择栅极线SGS(sel)的电位仅高出电位差ΔVg。此外,施加到选择栅极线SGS(sel)的电压的该升压不限定于时刻T1。

因此,在时刻T1以后,在选择块BLK(sel)的存储柱MP产生SL侧GIDL电流。在选择块BLK(sel)中,对字线WL(sel)施加像电压VE这样的低电压。因此,伴随该SL侧GIDL电流而产生的电洞进入该存储柱MP的存储单元晶体管MT的电荷储存层,与该电荷储存层中的电子耦合。

之后,在时刻T2,施加到选择栅极线SGD(sel)的电压升压至电压VGD。电压VGD高于电压VE。时刻T2例如为如下时刻:在如上所述地施加电压而使位线BL的电位上升的过程中,位线BL的电位比被施加电压VSS的选择栅极线SGD(sel)的电位仅高出电位差ΔVg。电压VGD例如为如下电压,即,在以此方式施加了电压的位线BL及选择栅极线SGD(sel)的电位稳定时,位线BL的电位比选择栅极线SGD(sel)的电位仅高出例如电位差ΔVg。在这种情况下,例如,在时刻T2以后,能够视作位线BL的电位比选择栅极线SGD(sel)的电位仅高出电位差ΔVg。另外,在这种情况下,施加了电压VGD的选择栅极线SGD(sel)的电位比施加了电压VGS的选择栅极线SGS(sel)的电位仅低了电位差ΔVd。

因此,在时刻T2以后,在选择块BLK(sel)的存储柱MP产生BL侧GIDL电流。与对选择块BLK(sel)中的SL侧GIDL电流进行说明一样,伴随BL侧GIDL电流而产生的电洞进入该存储柱MP的存储单元晶体管MT的电荷储存层,与该电荷储存层中的电子耦合。

在上述内容中,对如下情况的例子进行了说明:对选择栅极线SGS(bias)及SGS(sel)施加电压VGS,对选择栅极线SGD(sel)施加低于电压VGS的电压VGD。但本实施方式不限于此。例如,也可对选择栅极线SGS(bias)、SGS(sel)、及SGD(sel)施加同一电压VGD。

另外,在上述内容中,对在偏压块BLK(bias)中字线WL(bias)及选择栅极线SGD(bias)成为浮置状态的情况的例子进行了说明。但本实施方式不限于此。只要分别对字线WL(bias)及选择栅极线SGD(bias)施加例如使在时刻T1以后伴随SL侧GIDL电流而产生的电洞能够在存储柱MP内移动的电压即可。

另外,在上述内容中,对在选择块BLK(sel)中产生SL侧GIDL电流与BL侧GIDL电流两者的情况的例子进行了说明。但本实施方式不限于此。例如,也可将半导体存储装置1构成为在选择块BLK(sel)中仅产生BL侧GIDL电流。

进而,在上述内容中,对分别在选择晶体管ST1及ST2中以同一电位差ΔVg产生GIDL电流的情况的进行了说明,但本实施方式不限于此。

(3)GIDL擦除动作的机制

图8是用来说明第1实施方式的半导体存储装置1中的擦除动作的示意图。图8对应于图4所图示的半导体存储装置1的截面构造。

在图8中,图示了偏压块BLK(bias)的某存储柱MP与选择块BLK(sel)的某存储柱MP。一面参考图8,一面对与图7所示的时序图对应的擦除动作进行说明。

首先,在时刻T0,对源极线SL施加电压VERA。之后,在时刻T1,一面对源极线SL施加电压VERA,一面分别对选择栅极线SGS(bias)及SGS(sel)施加电压VGS。

以此方式对各布线施加电压,源极线SL的电位变得比选择栅极线SGS(bias)及SGS(sel)的电位仅高出例如电位差ΔVg。

与之相应地,在时刻T1以后,在偏压块BLK(bias)的存储柱MP的选择晶体管ST2,继续产生SL侧GIDL电流(图中的“GIDL1”),另外,在选择块BLK(sel)的存储柱MP的选择晶体管ST2也继续产生SL侧GIDL电流(图中的“GIDL2”)。伴随这些GIDL电流而产生的电洞分别供给到偏压块BLK(bias)及选择块BLK(sel)的存储柱MP内。

另外,相应于偏压块BLK(bias)中的SL侧GIDL电流的产生,而对位线BL施加电压VBL。电压VBL例如高于感测放大器模块12能够施加的最高的电压。之后,在时刻T2,一面对位线BL施加电压VBL,一面对选择栅极线SGD(sel)施加电压VGD。

以此方式对各布线施加电压,位线BL的电位比选择栅极线SGD(sel)的电位仅高出例如电位差ΔVg。

与之相应地,在选择块BLK(sel)的存储柱MP的选择晶体管ST1产生BL侧GIDL电流(图中的“GIDL3”)。伴随BL侧GIDL电流而产生的电洞供给到选择块BLK(sel)的存储柱MP内。另一方面,与BL侧GIDL电流对应的电子流经位线BL,该电子与在偏压块BLK(bias)中伴随SL侧GIDL电流的产生而产生的电洞耦合(图中的“再耦合”)。这样,即便电子流经位线BL,位线BL的电位也不会下降而得以维持,在时刻T2以后,在选择块BLK(sel)中也继续产生BL侧GIDL电流。

如上所述,对选择块BLK(sel)的存储柱MP内继续供给电洞。该供给的电洞与该存储柱MP的存储单元晶体管MT的电荷储存层中的电子耦合。由此,该存储单元晶体管MT的阈值电压下降而包含在“Er”状态的阈值电压分布中。

[效果]

第1实施方式的半导体存储装置1在擦除动作中,在擦除动作的对象的块BLK产生SL侧GIDL电流及BL侧GIDL电流。伴随这些GIDL电流而产生的电洞供给到该块BLK的存储柱MP内。该供给的电洞与该存储柱MP的存储单元晶体管MT的电荷储存层中的电子耦合。由此,该存储单元晶体管MT的阈值电压下降。

半导体存储装置1为了产生BL侧GIDL电流,而对位线BL施加某电压(以下,也称为擦除电压),在执行擦除动作期间,例如继续施加该电压。

此处,在不对位线BL继续施加擦除电压的情况下,与BL侧GIDL电流对应的电子流经位线BL,该位线BL的电位可降低。其结果,可能会发生如下情况:连所述电洞都可从存储柱MP内流向位线BL、及/或在擦除动作中无法继续产生BL侧GIDL电流。这可能与目标数据擦除不完整有关。

擦除电压例如高于感测放大器模块12所能够施加的电压。因此,为了对位线BL施加擦除电压,例如考虑在各位线BL设置能够传送擦除电压的高耐压MOS晶体管。但如果在各位线BL设置高耐压MOS晶体管,则对半导体存储装置1的芯片尺寸的不良影响较大。

对此,半导体存储装置1在擦除动作中利用偏压块BLK(bias)对位线BL施加擦除电压,并继续施加该电压。更具体来说,半导体存储装置1在偏压块BLK(bias)产生SL侧GIDL电流。相应于SL侧GIDL电流的产生,将擦除电压VBL施加到位线BL。

因此,在半导体存储装置1中,无需如上所述地在各位线BL设置高耐压MOS晶体管。也就是说,在半导体存储装置1中,能够减少电路元件的数量。特别是能够减少占有面积相对较大的高耐压MOS晶体管的数量。因此,根据半导体存储装置1,例如能够提供芯片尺寸小型化、及/或位成本降低的半导体存储装置。进而,通过减少电路元件的数量,电路元件与布线之间的接点的数量也减少。因此,根据半导体存储装置1,例如能够提供接点间产生的寄生电容小且性能提高的半导体存储装置。

<其它实施方式>

在本说明书中,当使用同一、一致、固定、及维持等表述时,也可包括包含了设计范围内的误差的情况。

另外,当表述为施加或供给某电压时,还包括进行像施加或供给该电压这样的控制、以及实际上施加或供给该电压中的任一种情况。进而,施加或供给某电压也可包括施加或供给例如0V的电压。

在本说明书中,“连接”表示电连接,不排除例如在其间经由另一元件。

另外,当表述为第1电路元件配置在第2电路元件与第3电路元件之间时,包括如下情况:第1电路元件具有像第1电路元件的第1端子连接到第2电路元件且第1电路元件的第2端子连接到第3电路元件这样的连接关系。在此情况下,不排除在第1电路元件与第2电路元件之间、及/或第1电路元件与第3电路元件之间经由另一元件。

上述内容中说明了若干实施方式,但这些实施方式是作为例子提出的,并不意图限定发明的范围。这些新颖的实施方式能够以其它各种方式实施,能够在不脱离发明主旨的范围内进行各种省略、替换、变更。这些实施方式及其变化包含在发明的范围或主旨内,并且包含在权利要求书所记载的发明及其均等的范围内。

[符号的说明]

1 半导体存储装置

11 存储单元阵列

12 感测放大器模块

13 行译码器模块

14 输入输出电路

15 寄存器

151 状态寄存器

152 地址寄存器

153 指令寄存器

16 逻辑控制电路

17 定序器

18 就绪/忙碌控制电路

19 电压产生电路

BLK 块

SU 字符串单元

NS NAND字符串

CU 单元组件

BL 位线

WL 字线

SGD、SGS 选择栅极线

SL 源极线

MT 存储单元晶体管

ST 选择晶体管

SAU 感测放大器单元

SA 感测放大器电路

Tr 晶体管

2 存储器控制器

21 主机接口电路

22 CPU

23 RAM

24 ROM

25 存储器接口电路

3 存储系统

4 主机装置

31 半导体衬底

100 存储单元部

41、43、45、51、LI 导电体

471 核心部

472、476 半导体

473 隧道氧化膜

474 绝缘膜

475 阻挡绝缘膜

MP 存储柱

CP 接触插塞

SR 分隔区域

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统