数据驱动电路

文献发布时间:2023-06-19 11:39:06

技术领域

各种实施方式总体上可能涉及一种半导体电路,并且更具体地,涉及一种数据驱动电路。

背景技术

半导体电路可以包括被配置为向外部装置输出数据的数据驱动电路。

数据驱动电路可以被设计为实现与半导体装置的驱动强度和端接的规格相对应的各种阻抗。

发明内容

根据本公开的一个实施方式,数据驱动电路可以包括触发电路和预驱动器。触发电路可以被配置为阻挡用于发送数据的多个信号路径中的除了与当前选择的驱动强度相对应的信号路径之外的其余信号路径。预驱动器可以被配置为使用根据多个阻抗控制代码确定的阻抗来驱动通过与当前选择的驱动强度相对应的信号路径而发送的数据。

附图说明

从以下结合附图的详细描述中,将更清楚地理解本公开的主题的上述和其他方面、特征和优点,在附图中:

图1示出了根据示例实施方式的数据驱动电路;

图2示出了图1的触发电路;

图3示出了图1的预驱动器;

图4示出了图3的预上拉驱动单元;

图5示出了图3的预下拉驱动单元;

图6示出了图1的主驱动器;

图7示出了图1的阻抗校准电路;

图8示出了根据一个实施方式的数据驱动电路;

图9示出了图8的触发电路;

图10示出了图8的预驱动器;

图11示出了图10的预上拉驱动单元;以及

图12示出了图10的预下拉驱动单元。

具体实施方式

参照附图详细描述本教导的各种实施方式。附图是各种实施方式(和中间结构)的示意表示。这样,可以预期由于例如制造技术和/或公差而导致图示的配置和形状的变化。因此,所描述的实施方式不应被解释为限于这里所示出的特定配置和形状,而是可以包括不脱离由所附权利要求书限定的本教导的精神和范围的配置和形状上的偏差。

本文中部分参考本教导的理想化实施方式的截面图和/或平面图来描述本教导。然而,本教导的实施方式不应被解释为限制性的。尽管示出并描述了本教导的一些实施方式,但是本领域普通技术人员将理解,可以在不脱离本教导的原理和精神的情况下对这些实施方式进行改变。

一些实施方式设计提供能够简化逻辑并降低功耗的数据驱动电路。

图1是示出根据示例实施方式的数据驱动电路100的图。

参照图1,数据驱动电路100可以包括触发电路101、预驱动器102和主驱动器103。

此外,该示例实施方式的数据驱动电路100还可以包括阻抗校准电路105。

触发电路101可以根据具有相位差的多个时钟信号RCLKDO和FCLKDO锁存多个第一数据RDATA和FDATA,以输出多个第二数据RDATAS

预驱动器102可以使用根据多个驱动强度控制信号CONPU

主驱动器103可以根据驱动控制信号PU

阻抗校准电路105可以控制阻抗控制代码PUCODE

图2是示出图1中的触发电路101的图。图2示出了当第二数据RDATAS

参照图2,触发电路101可以包括第一锁存电路110、第一信号分配电路111-0~111-2、第二锁存电路120和第二信号分配电路121-0~121-2。如本文中所使用的,波浪符号“~”指示组件的范围。例如,“111-0~111-2”指示图2中所示的第一信号分配电路111-0、111-1和111-2。

第一锁存电路110可以根据时钟信号RCLKDO和FCLKDO中的第一时钟信号RCLKDO锁存第一数据RDATA以生成第一锁存信号RDIN。

第一信号分配电路111-0至111-2可以分配第一锁存信号RDIN以输出第二数据RDATAS<2:0>和FDATAS<2:0>中的第二数据RDATAS<2:0>。

在示例实施方式中,第一信号分配电路111-0~111-2中的每一个可以包括反相器链(inverter chain)。

第二锁存电路120可以根据时钟信号RCLKDO和FCLKDO中的第二时钟信号FCLKDO锁存第一数据FDATA以生成第二锁存信号FDIN。

第二信号分配电路121-0~121-2可以分配第二锁存信号FDIN以输出第二数据RDATAS<2:0>和FDATAS<2:0>中的第二数据FDATAS<2:0>。

在示例实施方式中,第二信号分配电路121-0~121-2中的每一个可以包括传输门(transmission gate)和反相器。

传输门可以包括被配置为接收接地电压的负控制端子和被配置为接收电源电压的正控制端子。

传输门可以被配置为向第二信号分配电路121-0~121-2和第一信号分配电路111-0~111-2提供相同的信号延迟时间。

图3是示出图1中的预驱动器102的图。

图3示出了当驱动强度控制信号CONPU

参照图3,预驱动器102可以包括多个预驱动单元201-0~201-4和202-0~202-4。

预驱动单元201-0~201-4和202-0~202-4可以被分类为多个预上拉驱动单元201-0~202-4和多个预下拉驱动单元202-0~202-4。

第一预上拉驱动单元201-0可以根据第二数据RDATAS<0>、第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<0>_<4:0>。

第二预上拉驱动单元201-1可以根据第二数据RDATAS<1>、第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<1>_<4:0>。

第三预上拉驱动单元201-2可以根据第二数据RDATAS<2>、第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<2>_<4:0>。

第四预上拉驱动单元201-3可以根据第二数据RDATAS<2>、第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<3>_<4:0>。

第五预上拉驱动单元201-4可以根据第二数据RDATAS<2>、第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<4>_<4:0>。

第一预下拉驱动单元202-0可以根据第二数据FDATAS<0>、第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<0>_<4:0>。

第二预下拉驱动单元202-1可以根据第二数据FDATAS<1>、第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<1>_<4:0>。

第三预下拉驱动单元202-2可以根据第二数据FDATAS<2>、第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<2>_<4:0>。

第四预下拉驱动单元202-3可以根据第二数据FDATAS<2>、第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<3>_<4:0>。

第五预下拉驱动单元202-4可以根据第二数据FDATAS<2>、第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<4>_<4:0>。

图4是示出图3中的第五上拉驱动单元201-4的图。

预上拉驱动单元201-0~201-4可以全部具有基本相同的配置。因此,仅示出了第五预上拉驱动单元201-4的配置。

参照图4,第五预上拉驱动单元201-4可以包括代码控制电路210和驱动控制信号生成电路220。

代码控制电路210可以根据第一驱动强度控制信号CONPU<4:0>和第一阻抗控制代码PUCODE<4:0>来生成第一强度和阻抗控制信号TRIMPU<4:0>。

代码控制电路210可以根据第一驱动强度控制信号CONPU<4:0>通过第一强度和阻抗控制信号TRIMPU<4:0>旁路(bypass)第一阻抗控制代码PUCODE<4:0>或者将第一强度和阻抗控制信号TRIMPU<4:0>固定为特定逻辑电平。

代码控制电路210可以包括多个代码控制单元,即,第一代码控制单元至第五代码控制单元211~215。

第一代码控制单元211可以输出通过第一驱动强度控制信号CONPU<0>与第一阻抗控制代码PUCODE<0>的与运算(AND operation)而生成的信号作为第一强度和阻抗控制信号TRIMPU<0>。

第二代码控制单元212可以输出通过第一驱动强度控制信号CONPU<1>与第一阻抗控制代码PUCODE<1>的与运算而生成的信号作为第一强度和阻抗控制信号TRIMPU<4:0>中的第一强度和阻抗控制信号TRIMPU<1>。

第三代码控制单元213可以输出通过第一驱动强度控制信号CONPU<2>与第一阻抗控制代码PUCODE<2>的与运算而生成的信号作为第一强度和阻抗强度控制信号TRIMPU<4:0>中的第一强度和阻抗控制信号TRIMPU<2>。

第四代码控制单元214可以输出通过第一驱动强度控制信号CONPU<3>与第一阻抗控制代码PUCODE<3>的与运算而生成的信号作为第一强度和阻抗控制信号TRIMPU<4:0>中的第一强度和阻抗控制信号TRIMPU<3>。

第五代码控制单元215可以输出通过第一驱动强度控制信号CONPU<4>与第一阻抗控制代码PUCODE<4>的与运算而生成的信号作为第一强度和阻抗控制信号TRIMPU<4:0>中的第一强度和阻抗控制信号TRIMPU<4>。

在示例实施方式中,第一代码控制单元至第五代码控制单元211~215可以全部具有基本相同的配置。因此,仅示出了第一代码控制单元211的配置。

第一代码控制单元211可以包括第一逻辑门211-1和第二逻辑门211-2。

第一逻辑门211-1可以对第一驱动强度控制信号CONPU<4:0>中的第一驱动强度控制信号CONPU<0>与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<0>执行与非运算(negative AND operation)。

第二逻辑门211-2可以输出通过将第一逻辑门211-1的输出反相而生成的信号作为第一强度和阻抗控制信号TRIMPU<0>。

驱动控制信号生成电路220可以根据第一强度和阻抗控制信号TRIMPU<4:0>和第二数据RDATAS<2>来生成第一驱动控制信号PU<4>_<4:0>。

驱动控制信号生成电路220可以根据第一强度和阻抗控制信号TRIMPU<4:0>通过第一驱动控制信号PU<4>_<4:0>旁路第二数据RDATAS<2>或将第一驱动控制信号PU<4:0>_<4:0>固定为特定逻辑电平

驱动控制信号生成电路220可以包括多个驱动控制信号生成单元,即,第一驱动控制信号生成单元至第五驱动控制信号生成单元221~225。

第一驱动控制信号生成单元221可以输出通过第二数据RDATAS<2>的反相信号与第一强度和阻抗控制信号TRIMPU<0>的与运算而生成的信号作为第一驱动控制信号PU<4>_<0>。

第二驱动控制信号生成单元222可以输出通过第二数据RDATAS<2>的反相信号与第一强度和阻抗控制信号TRIMPU<1>的与运算而生成的信号作为第一驱动控制信号PU<4>_<1>。

第三驱动控制信号生成单元223可以输出通过第二数据RDATAS<2>的反相信号与第一强度和阻抗控制信号TRIMPU<2>的与运算而生成的信号作为第一驱动控制信号PU<4>_<2>。

第四驱动控制信号生成单元224可以输出通过第二数据RDATAS<2>的反相信号与第一强度和阻抗控制信号TRIMPU<3>的与运算而生成的信号作为第一驱动控制信号PU<4>_<3>。

第五驱动控制信号生成单元225可以输出通过第二数据RDATAS<2>的反相信号与第一强度和阻抗控制信号TRIMPU<4>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4>。

在示例实施方式中,第一驱动控制信号生成单元至第五驱动控制信号生成单元221~225可以全部具有基本相同的配置。因此,仅示出了第一驱动控制信号生成单元221的配置。

第一驱动控制信号生成单元221可以包括第一逻辑门221-1、第二逻辑门221-2和第三逻辑门221-3。

第一逻辑门221-1可以被配置为将第二数据RDATAS<2>反相并输出。

第二逻辑门221-2可以对第一逻辑门221-1的输出与第一强度和阻抗控制信号TRIMPU<0>执行与非运算,以输出所计算的信号。

第三逻辑门221-3可以被配置为将第二逻辑门221-2的输出反相以输出第一驱动控制信号PU<4>_<0>。

除了第三逻辑门221-3之外,第五驱动控制信号生成单元225可以具有与第一驱动控制信号生成单元221的配置基本相同的配置。

图5是示出图3中的预下拉驱动单元202-4的图。

预下拉驱动单元202-0~202-4可以全部具有基本相同的配置。因此,仅示出了第五预下拉驱动单元202-4的配置。

参照图5,第五预下拉驱动单元202-4可以包括代码控制电路310和驱动控制信号生成电路320。

代码控制电路310可以根据第二驱动强度控制信号CONPD<4:0>和第二阻抗控制代码PDCODE<4:0>来生成第二强度和阻抗控制信号TRIMPD<4:0>。

代码控制电路310可以根据第二驱动强度控制信号CONPD<4:0>通过第二强度和阻抗控制信号TRIMPD<4:0>旁路第二阻抗控制代码PDCODE<4:0>或将第二强度和阻抗控制信号TRIMPD<4:0>固定为特定逻辑电平。

代码控制电路310可以包括多个代码控制单元,即,第一代码控制单元至第五代码控制单元311~315。

第一代码控制单元311可以输出通过第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<0>和第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<0>的与运算而生成的信号作为第二强度和阻抗控制信号TRIMPD<4:0>中的第二强度和阻抗控制信号TRIMPD<0>。

第二代码控制单元312可以输出通过第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<1>与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<1>的与运算而生成的信号作为第二强度和阻抗控制信号TRIMPD<4:0>中的第二强度和阻抗控制信号TRIMPD<1>。

第三代码控制单元313可以输出通过第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<2>和第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<2>的与运算而生成的信号作为第二强度和阻抗控制信号TRIMPD<4:0>中的第二强度和阻抗控制信号TRIMPD<2>。

第四代码控制单元314可以输出通过第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<3>和第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<3>的与运算而生成的信号作为第二强度和阻抗控制信号TRIMPD<4:0>中的第二强度和阻抗控制信号TRIMPD<3>。

第五代码控制单元315可以输出通过第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<4>和第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<4>的与运算而生成的信号作为第二强度和阻抗控制信号TRIMPD<4:0>中的第二强度和阻抗控制信号TRIMPD<4>。

在示例实施方式中,第一代码控制单元至第五代码控制单元311~315可以全部具有基本相同的配置。因此,仅示出了第一代码控制单元311的配置。

第一代码控制单元311可以包括第一逻辑门311-1和第二逻辑门311-2。

第一逻辑门311-1可以执行第二驱动强度控制信号CONPD<4:0>中的第二驱动强度控制信号CONPD<0>与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<0>的与非运算。

第二逻辑门311-2可以输出通过将第一逻辑门311-1的输出反相而生成的信号作为第二强度和阻抗控制信号TRIMPD<0>。

驱动控制信号生成电路320可以根据第二强度和阻抗控制信号TRIMPD<4:0>和第二数据RDATAS<2>来生成第二驱动控制信号PD<4>_<4:0>。

驱动控制信号生成电路320可以根据第二强度和阻抗控制信号TRIMPD<4:0>通过第二驱动控制信号PD<4>_<4:0>旁路第二数据RDATAS<2>或将第二驱动控制信号PD<4:0>_<4:0>固定为特定逻辑电平。

驱动控制信号生成电路320可以包括多个驱动控制信号生成单元,即,第一驱动控制信号生成单元至第五驱动控制信号生成单元321~325。

第一驱动控制信号生成单元321可以输出通过第二数据RDATAS<2>的反相信号与第二强度和阻抗控制信号TRIMPD<0>的与运算而生成的信号作为第二驱动控制信号PD<4>_<0>。

第二驱动控制信号生成单元322可以输出通过第二数据RDATAS<2>的反相信号与第二强度和阻抗控制信号TRIMPD<1>的与运算而生成的信号作为第二驱动控制信号PD<4>_<1>。

第三驱动控制信号生成单元323可以输出通过第二数据RDATAS<2>的反相信号与第二强度和阻抗控制信号TRIMPD<2>的与运算而生成的信号作为第二驱动控制信号PD<4>_<2>。

第四驱动控制信号生成单元324可以输出通过第二数据RDATAS<2>的反相信号与第二强度和阻抗控制信号TRIMPD<3>的与运算而生成的信号作为第二驱动控制信号PD<4>_<3>。

第五驱动控制信号生成单元325可以输出通过第二数据RDATAS<2>的反相信号与第二强度和阻抗控制信号TRIMPD<4>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4>。

在示例实施方式中,第一动控制信号生成单元至第五驱动控制信号生成单元321~325可以全部具有基本相同的配置。因此,仅示出了第一驱动控制信号生成单元321的配置。

第一驱动控制信号生成单元321可以包括第一逻辑门321-1、第二逻辑门321-2和第三逻辑门321-3。

第一逻辑门321-1可以被配置为将第二数据RDATAS<2>反相并输出。

第二逻辑门321-2可以对第一逻辑门321-1的输出与第二强度和阻抗控制信号TRIMPD<0>进行与非运算,以输出所计算的信号。

第三逻辑门321-3可以被配置为将第二逻辑门321-2的输出反相以输出第二驱动控制信号PD<4>_<0>。

图6是示出图1中的主驱动器103的图。

参照图6,主驱动器103可以包括共同连接到输出端子DQ的第一驱动器410和第二驱动器420。

第一驱动器410可以上拉输出端子DQ以满足根据第一驱动控制信号PU<4>_<4:0>确定的端接阻抗(termination impedance)和驱动强度。

第二驱动器420可以下拉输出端子DQ以满足根据第二驱动控制信号PD<4>_<4:0>确定的端接阻抗和驱动强度。

第一驱动器410可以包括多个上拉支路(leg)410-0~410-P。

上拉支路410-0~410-P可以被设计用于阻抗值的组合,以实现在半导体装置的规格中确定的驱动强度和端接阻抗。

上拉支路410-0~410-P的数量和上拉支路410-0~410-P中的每一个的目标阻抗可以根据半导体装置的规格来确定。

用于将第一驱动控制信号PU<4>_<4:0>分配到上拉支路410-0~410-P的分配方式可以根据半导体装置的规格来确定。

第一驱动控制信号PU<4:0>_<4:0>的信号分量中的每一个可以一对一的关系输入到上拉支路410-0~410-P的一部分中。第一驱动控制信号PU<4:0>_<4:0>的信号分量中的至少一个可以被共同输入到上拉支路410-0~410-P的另一部分中。

第二驱动器420可以包括多个下拉支路420-0~420-Q。

下拉支路420-0~420-Q可以被设计用于阻抗值的组合,以实现在半导体装置的规格中确定的驱动强度和端接阻抗。

下拉支路420-0~420-Q的数量和下拉支路420-0~420-Q中的每一个的目标阻抗可以根据半导体装置的规格来确定。

用于将第二驱动控制信号PD<4>_<4:0>分配到下拉支路420-0~420-Q的分配方式可以根据半导体装置的规格来确定。

第二驱动控制信号PD<4:0>_<4:0>的信号分量中的每一个可以以一对一的关系输入到下拉支路420-0至420-Q的一部分中。第二驱动控制信号PD<4:0>_<4:0>的信号分量中的至少一个可以共同输入到下拉支路420-0~420-Q的另一部分中。

图7是示出图1中的阻抗校准电路105的图。

在图7中,当外部电阻器109的电阻可以是大约300ohm时,阻抗校准电路105可以被设计为实现根据半导体装置的规格确定的驱动强度和端接阻抗。

参照图7,阻抗校准电路105可以包括:参考电压生成电路(VREF Gen)431、第一再现支路432、第一代码生成电路433、第二再现支路435、第三再现支路436和第二代码生成电路437。

参考电压生成电路431可以被配置为生成参考电压VREF。例如,参考电压VREF可以是电源电压的一半。

第一再现支路432可以具有根据第一阻抗控制代码PUCODE<4:0>而受到控制的阻抗。

第一再现支路432可以被设计为具有第一目标值,即,与外部电阻器109的电阻基本相同的大约300ohm的阻抗。

例如,第一再现支路432可以通过再现上拉支路410-0~410-P中的任何一个来形成。

第一再现支路432可以通过外部电阻器焊盘107与外部电阻器109连接。

第一代码生成电路433可以被配置为根据可以连接到第一再现支路432和外部电阻器109的节点的电压与参考电压VREF之间的比较结果来控制第一阻抗控制代码PUCODE<4:0>的值。

第一代码生成电路433可以包括第一比较器433-1和第一计数器433-2。

第一比较器433-1可以将连接到第一再现支路432和外部电阻器109的节点的电压与参考电压VREF进行比较。然后,第一比较器433-1可以输出比较结果。

第一计数器433-2可以根据来自第一比较器433-1的输出来控制第一阻抗控制代码PUCODE<4:0>的值。

第二再现支路435可以具有根据第一阻抗控制代码PUCODE<4:0>而受到控制的阻抗。

第二再现支路435可以被设计为具有第一目标值,即,与外部电阻器109的电阻基本相同的大约300ohm的阻抗。

第二再现支路435可以具有与第一再现支路432的配置基本相同的配置。

第三再现支路436可以具有根据第二阻抗控制代码PDCODE<4:0>而受到控制的阻抗。例如,第三再现支路436可以通过再现下拉支路420-0~420-Q中的任何一个来形成。

第二代码生成电路437可以被配置为根据可以连接到第二再现支路435和第三再现支路436的节点的电压与参考电压VREF之间的比较结果来控制第二阻抗控制代码PDCODE<4:0>的值。

第二代码生成电路437可以包括第二比较器437-1和第二计数器437-2。

第二比较器437-1可以将连接到第二再现支路435和第三再现支路436的节点的电压与参考电压VREF进行比较。然后,第二比较器437-1可以输出比较结果。

第二计数器437-2可以根据来自第二比较器437-1的输出来控制第二阻抗控制代码PDCODE<4:0>的值。

在下文中,可以详细示出阻抗校准电路105的操作。

因为外部电阻器109可以布置在半导体芯片的外部,所以外部电阻器109可以具有恒定的电阻(即,大约300ohm),而不管内部操作环境如何。

因此,可以执行用于将第一再现支路432的阻抗控制到作为目标值的外部电阻器109的电阻的操作。

可以将连接到第一再现支路432和外部电阻器109的节点的电压与参考电压VREF进行比较。当节点的电压可以在误差范围内与参考电压VREF一致时,可以完成对第一阻抗控制代码PUCODE<4:0>的控制。

因为可以将第一阻抗控制代码PUCODE<4:0>提供给第二再现支路435,所以对第二再现支路435的阻抗的控制可以与第一再现支路432的控制的完成同时完成。

然后可以执行用于将第三再现支路436的阻抗控制为作为目标值的第二再现支路435的阻抗的操作。

可以将连接到第二再现支路435和第三再现支路436的节点的电压与参考电压VREF进行比较。当节点的电压可以在误差范围内与参考电压VREF一致时,可以完成第二阻抗控制代码PDCODE<4:0>的控制。

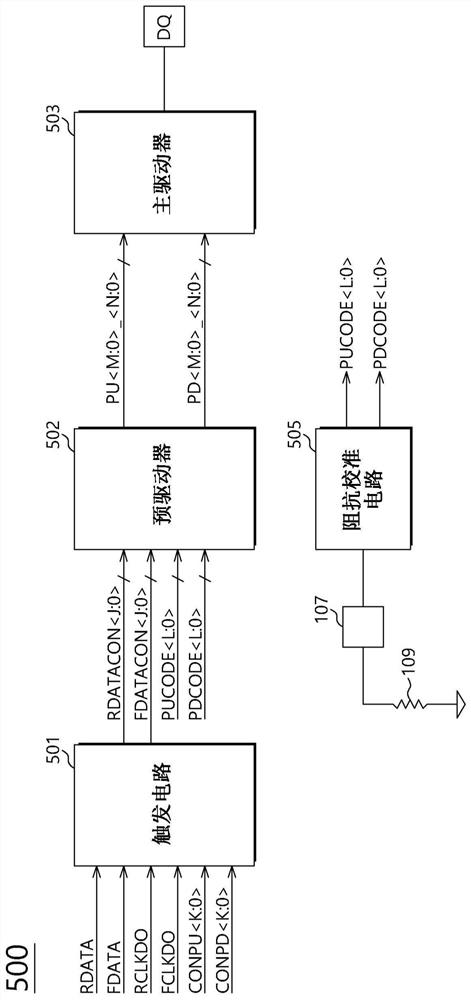

图8是示出根据示例实施方式的数据驱动电路500的图。

参照图8,数据驱动电路500可以包括触发电路501、预驱动器502和主驱动器503。

此外,该示例实施方式的数据驱动电路500可以进一步包括阻抗校准电路505。

触发电路501可以被配置为阻挡用于发送数据的多个信号路径中的除了用于与当前选择的驱动强度相对应的信号路径之外的其余信号路径。

触发电路501可以阻挡用于发送第二数据RDATACON

触发电路501可以根据多个驱动强度控制信号CONPU

预驱动器502可以使用根据多个阻抗控制代码PUCODE

主驱动器503可以根据驱动控制信号PU

阻抗校准电路505可以控制阻抗控制代码PUCODE

图9是示出图8中的触发电路501的图。

图9示出了当第二数据RDATACON

参照图9,触发电路501可以包括第一锁存电路510、第一信号分配电路511、第二锁存电路520和第二信号分配电路521。

第一锁存电路510可以根据时钟信号RCLKDO和FCLKDO中的第一时钟信号RCLKDO锁存第一数据RDATA,以生成第一锁存信号RDIN。

在示例实施方式中,第一信号分配电路511可以包括多个第一信号路径511-0~511-4。

第一信号分配电路511可以仅通过第一信号路径511-0~511-4中的根据第一驱动强度控制信号CONPU<4:0>选择的信号路径分配第一锁存信号RDIN以输出第二数据RDATACON<2:0>和FDATACON<2:0>中的第二数据RDATACON<2:0>。

第一信号路径511-0~511-4可以全部具有基本相同的配置。因此,这里可以示出第一信号路径511-0~511-4中的任何一个511-0。

当第一驱动强度控制信号CONPU<0>仅为高电平时,信号路径511-0可以将第一锁存信号RDIN反相并输出。

当第一驱动强度控制信号CONPU<0>可以为低电平时,信号路径511-0可以将第二数据RDATACON<0>固定为高电平,而不管第一锁存信号RDIN的逻辑电平如何。

信号路径511-0可以包括与非门和反相器链。

与非门可以对第一驱动强度控制信号CONPU<0>和第一锁存信号RDIN执行与非运算。

第二锁存电路520可以根据时钟信号RCLKDO和FCLKDO中的第二时钟信号FCLKDO锁存第一数据FDATA以生成第二锁存信号FDIN。

第二信号分配电路521可以包括多个第二信号路径521-0~521-4。

第二信号分配电路521可以仅通过第二信号路径521-0~521-4中的根据第二驱动强度控制信号CONPD<4:0>选择的信号路径分配第二锁存信号FDIN以输出第二数据RDATACON<2:0>和FDATACON<2:0>中的第二数据FDATACON<2:0>。

第二信号路径521-0~521-4可以全部具有基本相同的配置。因此,这里可以示出第二信号路径521-0~521-4中的任何一个521-0。

当第二驱动强度控制信号CONPD<0>可以为低电平时,信号路径521-0可以将第二锁存信号FDIN反相并输出。

当第二驱动强度控制信号CONPD<0>可以为高电平时,信号路径521-0可以将第二数据FDATACON<0>固定为高电平,而不管第二锁存信号FDIN的逻辑电平如何。

信号路径521-0可以包括或非门(NOR gate)、传输门和反相器。

与非门可以对第一驱动强度控制信号CONPU<0>和第一锁存信号RDIN执行与非运算。

或非门可以对第二驱动强度控制信号CONPD<0>和第二锁存信号FDIN执行或非运算。

传输门可以包括被配置为接收接地电压的负控制端子和被配置为接收电源电压的正控制端子。

传输门可以配置为向信号路径521-0提供与第一信号分配电路511的信号路径511-0的信号延迟时间基本相同的信号延迟时间。

反相器可以将或非门的输出反相以输出第二数据FDATACON<0>。

图10是示出图8中的预驱动器502的图。

参照图10,预驱动器502可以包括多个预驱动单元601-0~601-4和602-0~602-4。

预驱动单元601-0~601-4和602-0~602-4可以被分类为多个预上拉驱动单元601-0~601-4和多个预下拉驱动单元602–0至602-4。

第一预上拉驱动单元601-0可以根据第二数据RDATACON<0>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<0>_<4:0>。

第二预上拉驱动单元601-1可以根据第二数据RDATACON<1>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<1>_<4:0>。

第三预上拉驱动单元601-2可以根据第二数据RDATACON<2>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<2>_<4:0>。

第四预上拉驱动单元601-3可以根据第二数据RDATACON<2>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<3>_<4:0>。

第五预上拉驱动单元601-4可以根据第二数据RDATACON<2>和第一阻抗控制代码PUCODE<4:0>来生成第一驱动控制信号PU<4>_<4:0>。

第一预下拉驱动单元602-0可以根据第二数据FDATACON<0>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<0>_<4:0>。

第二预下拉驱动单元602-1可以根据第二数据FDATACON<1>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<1>_<4:0>。

第三预下拉驱动单元602-2可以根据第二数据FDATACON<2>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<2>_<4:0>。

第四预下拉驱动单元602-3可以根据第二数据FDATACON<2>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<3>_<4:0>。

第五预下拉驱动单元602-4可以根据第二数据FDATACON<2>和第二阻抗控制代码PDCODE<4:0>来生成第二驱动控制信号PD<4>_<4:0>。

图11是示出图10中的第五预上拉驱动单元601-4的图。

预上拉驱动单元601-0~601-4可以全部具有基本相同的配置。因此,仅示出了第五上拉驱动单元601-4的配置。

参照图11,第五预上拉驱动单元601-4可以包括多个代码控制单元,即,第一代码控制单元至第五代码控制单元611至615。

第一代码控制单元611可以输出通过第二数据RDATACON<4>的反相信号与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<0>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4:0>中的第一驱动控制信号PU<4>_<0>。

第二代码控制单元612可以输出通过第二数据RDATACON<4>的反相信号与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<1>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4:0>中的第一驱动控制信号PU<4>_<1>。

第三代码控制单元613可以输出通过第二数据RDATACON<4>的反相信号与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<2>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4:0>中的第一驱动控制信号PU<4>_<2>。

第四代码控制单元614可以输出通过第二数据RDATACON<4>的反相信号与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<3>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4:0>中的第一驱动控制信号PU<4>_<3>。

第五代码控制单元615可以输出通过第二数据RDATACON<4>的反相信号与第一阻抗控制代码PUCODE<4:0>中的第一阻抗控制代码PUCODE<4>的与运算而生成的信号作为第一驱动控制信号PU<4>_<4:0>中的第一驱动控制信号PU<4>_<4>。

在示例实施方式中,第一代码控制单元至第五代码控制单元611~615可以全部具有基本相同的配置。因此,仅示出了第一代码控制单元611的配置。

第一代码控制单元611可以包括第一逻辑门611-1、第二逻辑门611-2和第三逻辑门611-3。

第一逻辑门611-1可以被配置为将第二数据RDATACON<4>反相并输出。

第二逻辑门611-2可以对第一逻辑门611-1的输出和第一阻抗控制代码PUCODE<0>执行与非运算,以输出所计算的信号。

第三逻辑门611-3可以被配置为将第二逻辑门611-2的输出反相以输出第一驱动控制信号PU<4>_<0>。

除了第三逻辑门611-3之外,第五代码控制单元615可以具有与第一代码控制单元611的配置基本相同的配置。

图12是示出图10中的第五预下拉驱动单元602-4的图。

预下拉驱动单元602-0~602-4可以全部具有基本相同的配置。因此,仅示出了第五预下拉驱动单元602-4的配置。

参照图12,第五预下拉驱动单元602-4可以包括多个代码控制单元,即,第一代码控制单元至第五代码控制单元621~625。

第一代码控制单元621可以输出通过第二数据FDATACON<4>的反相信号与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<0>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4:0>中的第二驱动控制信号PD<4>_<0>。

第二代码控制单元622可以输出通过第二数据FDATACON<4>的反相信号与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<1>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4:0>中的第二驱动控制信号PD<4>_<1>。

第三代码控制单元623可以输出通过第二数据FDATACON<4>的反相信号与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<2>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4:0>中的第二驱动控制信号PD<4>_<2>。

第四代码控制单元624可以输出通过第二数据FDATACON<4>的反相信号与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<3>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4:0>中的第二驱动控制信号PD<4>_<3>。

第五代码控制单元625可以输出通过第二数据FDATACON<4>的反相信号与第二阻抗控制代码PDCODE<4:0>中的第二阻抗控制代码PDCODE<4>的与运算而生成的信号作为第二驱动控制信号PD<4>_<4:0>中的第二驱动控制信号PD<4>_<4>。

在示例实施方式中,第一代码控制单元至第五代码控制单元621~625可以全部具有基本相同的配置。因此,仅示出了第一代码控制单元621的配置。

第一代码控制单元621可以包括第一逻辑门621-1、第二逻辑门621-2和第三逻辑门621-3。

第一逻辑门621-1可以被配置为将第二数据RDATACON<4>反相并输出。

第二逻辑门621-2可以对第一逻辑门621-1的输出和第二阻抗控制代码PDCODE<0>执行与非运算,以输出与非(NAND)运算信号。

第三逻辑门621-3可以被配置为将第二逻辑门621-2的输出反相以输出第二驱动控制信号PD<4>_<0>。

在示例实施方式中,主驱动器503可以具有与图6基本相同的结构。因此,为简洁起见,在此可以省略关于主驱动器503的任何进一步的图示。

此外,阻抗校准电路505可以具有与图7中的阻抗校准电路基本相同的结构。因此,为了简洁起见,在此可以省略关于阻抗校准电路505的任何进一步的图示。

在下文中,可以详细示出数据驱动电路500的操作。

触发电路501可以通过选择的信号路径而非参照图9所示的所有第一信号路径511-0~511-4和第二信号路径521-0~521-4来发送可以通过根据时钟信号RCLK和FCLK锁存数据RDATA和FDATA而生成的第二数据RDATAS

触发电路501可以根据驱动强度控制信号CONPU<4:0>和CONPD<4:0>来选择信号路径511-0~511-4和521-0~521-4中的至少一个。

第一信号路径511-0~511-4和第二信号路径521-0~521-4中的未选择的信号路径可以被固定为特定逻辑电平以减少电流消耗。

预驱动器502可以将阻抗控制代码PUCODE<4:0>和PDCODE<4:0>施加到通过所选信号路径发送的第二数据RDATAS

主驱动器503可以驱动输出端子DQ以满足根据驱动控制信号PU<4:0>_<4:0>和PD<4:0>_<4:0>确定的端接阻抗和驱动强度。

本教导的上述实施方式旨在说明而非限制本教导。各种替代方案和等效方案是可能的。本教导不限于本文描述的实施方式。本教导也不限于任何特定类型的半导体装置。基于本公开的增加、减少或修改是可能的,并且旨在落入所附权利要求的范围内。

相关申请的交叉引用

本申请要求于2019年12月26日在韩国知识产权局提交的韩国申请第10-2019-0175034号的优先权,其全部内容通过引用合并于此。

- 数据驱动电路和使用该数据驱动电路的显示装置

- 数据驱动器、显示驱动电路和显示驱动电路的操作方法