半导体存储装置

文献发布时间:2023-06-19 11:39:06

本申请是以2019年12月27日提出申请的现有日本专利申请第2019-239101号的优先权的利益为基础,且追求其利益,其全部内容以引用的方式包含于本文中。

技术领域

本发明的实施方式涉及一种半导体存储装置。

背景技术

近年来,开发了一种将垂直型晶体管用作开关晶体管的1T(Transistor(晶体管))-1C(Capacitor(电容器))型半导体存储装置。垂直型晶体管是这样一种晶体管,它将在相对于半导体衬底的主面大致垂直的方向上延伸的半导体柱用作通道,且在半导体柱的周围具有在与主面大致平行的方向上延伸的栅极电极(字线)。

为使这种垂直型晶体管的接通电流(电流驱动能力)增大,而考虑使半导体柱变粗,增加垂直型晶体管的栅极宽度。然而,如果使半导体柱变粗,其周边的字线会变窄,导致字线电阻上升。或者,为将字线电阻维持得较低,而必须使字线宽度变宽。而且,使半导体柱变宽或加大字线宽度不利于存储单元阵列小型化。

如此一来,在垂直型晶体管的电流驱动能力与存储单元阵列小型化之间,存在权衡关系。

发明内容

本实施方式的半导体存储装置具有:多条第1布线,设置在半导体衬底的表面上方,且在第1方向延伸;及多条第2布线,设置在多条第1布线的上方,且向相对于所述第1方向交叉的第2方向延伸。多个电容器元件在从半导体衬底的表面上方观察时,每隔1个地配置在多条第1布线与多条第2布线的交叉区域。多个晶体管分别对应地设置在多个电容器元件上。第1方向上相邻的2个电容器元件间的第1间隔窄于第2方向上相邻的2个电容器元件间的第2间隔。

附图说明

图1A是表示本实施方式的半导体存储装置的一例构成的立体图。

图1B是表示1个存储单元的一例构成的剖视图。

图2是表示本实施方式的半导体存储装置的一例构成的俯视图。

图3A是表示折叠位线构成的配置的概略俯视图。

图3B是表示折叠位线构成的配置的概略俯视图。

图3C是表示折叠位线构成的配置的概略俯视图。

图4是表示柱的形状的概略俯视图。

图5是表示本实施方式的存储单元MC的一例制造方法的剖视图。

图6是继图5后表示一例制造方法的剖视图。

图7是继图6后表示一例制造方法的剖视图。

图8是继图7后表示一例制造方法的剖视图。

图9是继图8后表示一例制造方法的剖视图。

图10是继图9后表示一例制造方法的剖视图。

图11是表示本实施方式的DRAM的变化例1的剖视图。

图12是表示本实施方式的DRAM的变化例2的剖视图。

图13是表示本实施方式的DRAM的变化例3的剖视图。

图14A是表示其它折叠位线构成的配置的概略俯视图。

图14B是表示其它折叠位线构成的配置的概略俯视图。

图14C是表示其它折叠位线构成的配置的概略俯视图。

图15A是表示图14C的交叉部的更详细构成的图。

图15B是表示图14C的交叉部的更详细构成的图。

具体实施方式

以下将参考附图解释实施例。本发明不限于这些实施例。在实施例中,“上方向”或“下方向”是指当将与设置有半导体元件的半导体衬底的表面垂直的方向假定为“上方向”时的相对方向。因此,术语“上方向”或“下方向”有时不同于基于重力加速度方向的上方向或下方向。在本说明书和附图中,与所述附图中描述的元件相同的元件由相似的参考符号表示,并且视情况省略其详细说明。

本实施方式的半导体存储装置具有:多条第1布线,设置在半导体衬底的表面上方,且在第1方向延伸;及多条第2布线,设置在多条第1布线的上方,且向相对于所述第1方向交叉的第2方向延伸。多个电容器元件在从半导体衬底的表面上方观察时,每隔1个地配置在多条第1布线与多条第2布线的交叉区域。多个晶体管分别对应地设置在多个电容器元件上。第1方向上相邻的2个电容器元件间的第1间隔窄于第2方向上相邻的2个电容器元件间的第2间隔。

图1A是表示本实施方式的半导体存储装置1的一例构成的立体图。半导体存储装置1具有半导体衬底10、多条字线WL、多条位线BL、多个电容器元件20、及多个单元晶体管30。半导体存储装置1也可为例如DRAM(Dynamic Random Access Memory,动态随机存取存储器)。然而,本实施方式不限于DRAM,而可适用于任意的1T1C型存储器。1个电容器元件20和与之对应的1个单元晶体管30之对作为1个存储单元MC发挥作用。另外,存储单元MC也可为mT1C型(m为2以上整数)。即,存储单元MC的单元晶体管可分别共通连接着源极端子及漏极端子,且包含并联连接的多个单元晶体管30。在此情况下,并联连接的多个单元晶体管连接于电容器元件。

半导体衬底10包含例如硅单晶等。在半导体衬底10的表面上方,设置有在X方向上延伸的多条字线WL。多条字线WL相互大致平行地延伸,且在Y方向上以大致等间隔排列。

在字线WL的上方,设置有在与X方向交叉的Y方向上延伸的多条位线BL。多条位线BL相互大致平行地延伸,且在X方向上以大致等间隔排列。

在半导体衬底10的表面上,二维配置有多个电容器元件20。各电容器元件20的一电极Et(参照图1B)与单元晶体管30连接,且另一电极Eb(参照图1B)与半导体衬底10连接。电容器元件20的构成无特别限定。电容器元件20经由单元晶体管30接收并储存电荷(例如电子),或者将电荷排出。由此,电容器元件20作为电荷储存部发挥作用。此外,对于电容器元件20及单元晶体管30的构成,后面参照图1B进行说明。

本实施方式中,存储单元MC设置在半导体衬底10上。然而,如图11及图12所示,存储单元MC也可设置在半导体衬底10或外围电路上设置的板状电极(包括掺杂多晶硅、金属、金属硅化物等导电性材料的电极)12上。

多个单元晶体管30分别对应地设置在多个电容器元件20上。单元晶体管30各自具有半导体柱31。各半导体柱31从对应的电容器元件20贯通某1条字线WL而设置到1个位线BL。半导体柱31的下端与半导体柱31的电极Et(参照图1B)连接,且它的上端与位线BL连接。由此,构成具有字线WL作为栅极电极且具有半导体柱31作为通道区域的单元晶体管30。

半导体柱31是例如氧化物半导体,更具体而言,半导体柱31是例如包含氧化铟、氧化镓及氧化锌的IGZO(InGaZnO,铟镓锌氧化物)。单元晶体管30是例如3端子元件。3端子元件是以源极、漏极、栅极进行动作,且未设本体触点。因此,未对半导体柱31施加本体电压,单元晶体管30成为以3端子(源极、漏极、栅极)动作的开关元件。单元晶体管30的源极端子连接到电容器元件20的电极Et(参照图1B),漏极端子连接到1条位线BL,栅极端子连接到1条字线WL。这种将氧化物半导体用作通道区域(本体部分)的3端子元件的晶体管(以下也称为氧化物半导体晶体管)具有以宽带隙的氧化物半导体形成的通道部,且不具有PN结部。因此,当将氧化物半导体晶体管用作单元晶体管30时,单元晶体管30的断态泄漏电流变得极小,且也不存在结漏。由此,从电容器元件20经由单元晶体管30泄漏的电荷变少。因此,可通过将氧化物半导体晶体管用作单元晶体管30,而减少电容器元件20的电容。其结果,可使存储单元MC小型化。存储单元MC的小型化可使半导体存储装置1的存储单元阵列整体的布局面积减小,从而可降低制造成本。进而,因单元晶体管30的泄漏电流较小而可减少更新动作的频率,降低耗电。此外,也可在半导体柱31的中心部,设置有例如柱状的氧化硅膜等绝缘材料,且在该绝缘材料的周围设置IGZO等氧化物半导体。即,半导体柱31的氧化物半导体也可构成为筒状、例如通心粉状。

另一方面,各存储单元MC中储存的电荷量较少导致写入数据或读出数据对噪声敏感,噪声抗扰性下降。因此,本实施方式中,为保证噪声抗扰性而采用所谓的折叠位线构成。下文对折叠位线构成进行说明。

半导体衬底10上的电容器元件20、单元晶体管30、字线WL及位线BL由例如包含氧化硅膜等绝缘膜的层间绝缘膜40被覆。

在对某存储单元MC选择性存取的情况下,对从多条字线WL中选择的1条字线WL施加接通电压,对从多条位线BL中选择的1条位线BL施加写入电压或读出电压。由此,例如在写入动作中,和选择字线WL与选择位线BL的交点对应的选择存储单元MC的单元晶体管30成为导通状态(接通状态),而使电容器元件20中储存有电荷。DRAM之类的易失性存储器中,储存在电容器元件20的电荷随着时间经过,经由单元晶体管30等逸出。因此,为维持储存在电容器元件20中的电荷,而必须定期地执行保持(更新)动作。与之相对,根据本实施方式,如上所述,可通过将氧化物半导体晶体管用作单元晶体管30,而减少单元晶体管30中的泄漏电流,降低保持动作的频率。

而且,根据本实施方式,电容器元件20设置在半导体衬底10上,单元晶体管30设置在电容器元件20的上方。

当电容器元件20设置在单元晶体管30的上方时,为了连接电容器元件20的电极与半导体衬底10,在存储单元MC的侧方需要接触插塞。这种接触插塞导致存储单元阵列MCA的布局面积增大。

与之相对,本实施方式中,无需设置这种连接电容器元件20的电极与半导体衬底10的接触插塞。由此,可使存储单元阵列MCA小型化。

图1B是表示1个存储单元MC的一例构成的剖视图。如图1B所示,存储单元MC在半导体衬底10上具有电容器元件20,且在电容器元件20上具有单元晶体管30。

电容器元件20具有:与半导体衬底10连接的电极柱P、覆盖电极柱P的绝缘部13、及覆盖绝缘部13的单元电极14。电极柱P与单元电极14因绝缘部13而电绝缘,构成2个电极。

单元晶体管30具有:作为通道区域(电流路径)的氧化物半导体层(半导体柱)31、辅助层(supplemental layer)31CP、31BL、栅极绝缘层32、及字线WL。

图1B的电容器元件20是所谓的鳍型电容器。电容器元件20具有圆柱形状,但不限于此。电极柱P及单元电极14中,例如使用铜、钨等金属材料。绝缘部13中,例如使用铜氧化物、钨氧化物、硅氧化物、铝氧化物、铪氧化物、锆氧化物、钽氧化物、或它们的积层构造等。电极柱P与半导体衬底10电连接。另一方面,单元电极14经由辅助层31CP而与单元晶体管30的半导体柱31电连接。

单元晶体管30是例如垂直型晶体管,具备包含配置在比电容器元件20更靠上的作为通道的氧化物半导体(例如IGZO)的半导体柱31,且通道长度方向与半导体衬底10的表面交叉(例如正交)。而且,半导体柱31贯通字线WL。即,字线WL将半导体柱31的侧面(周围)包围。在此情况下,单元晶体管30的通道宽度成为半导体柱31的圆周方向,所以,半导体柱31的圆周方向的长度对单元晶体管30的电流驱动能力造成影响。

半导体柱31的下端的电极经由辅助层31CP而与单元电极14电连接,上端的电极经由辅助层31BL而与位线BL连接。

辅助层31CP设置在半导体柱31与单元电极14之间。而且,辅助层31BL设置在半导体柱31与位线BL之间。这是为了抑制半导体柱31内的氧在半导体柱31与单元电极14的界面及半导体柱31与位线BL的界面形成高电阻的金属氧化物层。即,辅助层31BL、31CP作为抑制半导体柱31与位线BL或单元电极14的反应的阻挡层发挥作用。

此外,辅助层31BL、31CP的材料中,不优选与半导体柱31的氧进行反应成为高电阻的金属氧化物层之类的金属材料。而且,作为辅助层31BL、31CP,也不优选使位线BL或单元电极14氧化的材料。因此,辅助层31BL、31CP中,优选使用氧的离解能(dissociationenergy)较大的氧化物。其中,期望辅助层31BL、31CP极薄地形成,以免阻碍单元晶体管30与电容器元件20或位线BL的电连接。

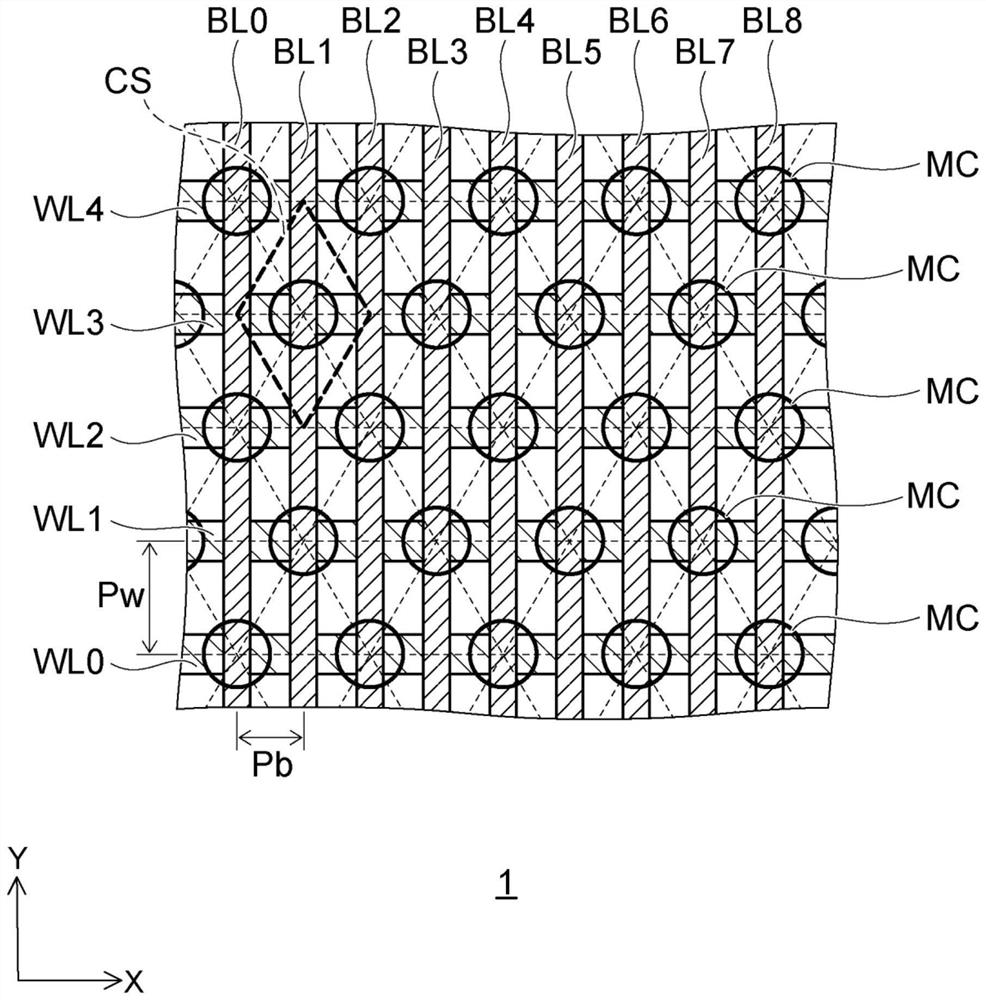

图2是表示本实施方式的半导体存储装置1的一例构成的俯视图。图2中,表示字线WL、位线BL及存储单元MC的配置关系。此外,字线WL及位线BL的条数无特别限制。

字线WL0~WL4分别向X方向延伸,且相互大致平行。相邻字线WL间的间距Pw约为1.7F。F(Feature size,特征尺寸)是半导体控制工艺中的最小加工尺寸。

位线BL0~BL8分别向Y方向延伸,且相互大致平行。相邻位线BL间的间距Pb约为1F。即,位线BL0~BL8间的间距Pb窄于字线WL0~WL4间的间距Pw。而且,在此情况下,平面布局中的1个存储单元MC的单位(单位单元的布局面积)成为3.4F

如图2所示,在从半导体衬底10的上方观察时,字线WL0~WL4与位线BL0~BL8交叉(例如正交)。存储单元MC在X方向及Y方向上每隔1个地配置在字线WL0~WL4与位线BL0~BL8的交点。即,X方向上排列的存储单元MC每隔1条位线BL配置1个。而且,Y方向上排列的存储单元MC每隔1条字线WL配置1个。进而换句话说,存储单元MC在X方向及Y方向上分别每隔半间距错开排列。

由此,在从半导体衬底10的表面上方观察时,存储单元MC的中心(电容器元件的中心)以成为平面最密堆积(即,六方最密配置)的方式配置。即,着眼于1个存储单元MC的话,在该存储单元MC的周围,6个存储单元MC几乎等距离地相邻。此6个存储单元MC配置在大致正六边形的顶点。在此情况下,彼此相邻的3个存储单元MC呈具有在X方向上延伸的边的大致三角形,且3个存储单元MC位于该三角形的顶点。当所述6个存储单元MC配置在大致正六边形的顶点时,彼此相邻的3个存储单元MC所成的三角形成为大致正三角形。

进而,着眼于X方向及Y方向上相邻的4个电容器元件20的话,此4个电容器元件20位于X方向及Y方向上具有对角线的四边形的顶点,且具有大致菱形的形状。此处,因间距Pb窄于间距Pw,所以,包括4个电容器元件20的四边形的X方向的对角线变得短于Y方向的对角线。因此,在平面布局中,包括4个电容器元件20的四边形成为位线BL方向(Y方向)上细长的菱形形状。因设为这种存储单元MC的配置,位线BL的间距Pb变得相对较窄,字线WL的间距Pw变得相对较宽。

因字线WL的间距Pw变宽,而可使字线WL的宽度变宽。由此,可使字线WL的电阻下降,使单元晶体管30的动作速度高速化。另一方面,因位线BL的间距Pb变窄,位线BL间的耦合噪声成为问题。本实施方式中,该噪声问题由下述折叠位线构成来应对。而且,在X方向及Y方向上,存储单元MC每隔1条位线BL配置1个。由此,可进行折叠位线构成。

图3A~图3C是表示折叠位线构成的配置的概略俯视图。折叠位线构成是将相邻的2条位线BL之对BLP连接到1个感测放大器SA。感测放大器SA是将从位线对BLP的一位线BL中所得的数据作为参照数据,将从另一位线BL中所得的数据作为信号数据,将信号数据与参照数据进行比较,检测信号数据的逻辑。以此方式,感测放大器SA构成为与相邻的2条位线对BLP的一端连接,且位线BL在感测放大器SA中折返。因此,这种构成称为折叠位线构成。

折叠位线构成中,相邻的2条位线对BLP被用于数据的写入或检测。即,位线对BLP的2条位线BL相互靠近。例如,当考量噪声从被激活的字线耦合到位线BL的实例时,噪声与构成位线对BLP的2条位线BL均耦合。当噪声与参照数据和信号数据均耦合时、即共模噪声的情况下,在采用差动传感方式的感测放大器中,读出信号量减少相当于与参照数据和信号数据分别耦合的噪声的差值。另一方面,在开放位线构成的情况下,因同样的实例中噪声仅与信号数据耦合,读出信号量相应于已耦合的噪声减少。如此一来,折叠位线构成具有噪声抗扰性优于开放位线构成的优点。

因此,本实施方式的半导体存储装置1即便将氧化物半导体晶体管用作单元晶体管30使存储单元MC小型化,使位线BL间的间距Pb变窄,也可通过采用折叠位线构成来提升噪声抗扰性。

此外,虽未图示,但开放位线构成从延伸到感测放大器中的其中一个感测放大器的位线及延伸到另一个感测放大器的位线,获得参照数据及信号数据。在此情况下,位线对不相邻,噪声容易仅加载到其中一条位线。因此,开放位线构成在噪声抗扰性上不如折叠位线构成。因此,采用开放位线构成的情况下,例如在读出动作时,实效性的读出信号量(参照数据与信号数据之差)会相应于噪声减少。为弥补此信号量的减少,而需要增大电容器元件20的电容等措施。在此情况下,必须将电容器元件20的绝缘体变更为高介电材料,或者进而提高电容器元件20的高度。例如,在提高电容器元件20的高度的情况下,会导致图11中所示的位线BL的位置变高,接触插塞18的高度(深度)变高。由此,位线BL与晶体管T的接触电阻会上升。或者,会产生接触插塞18的深宽比变高,从而生产率下降等问题。因此,开放位线构成如本实施方式所示,不适合将氧化物半导体晶体管用作单元晶体管或缩窄位线间的间距的半导体存储装置1。

图3A的构成中,感测放大器SA设置在存储单元阵列MCA的Y方向的一端(一边)侧,且仅配置在位线BL的单侧。

图3B的构成中,感测放大器SA设置在存储单元阵列MCA的Y方向的两端(两边)侧,且交替地配置在每一位线对BLP。例如,某位线对BLP中,感测放大器SA配置在一端侧,与之相邻的位线对BLP中,感测放大器SA配置在另一端侧。

图3C的构成中,感测放大器SA设置在2个存储单元阵列MCAa与MCAb之间,且与任一存储单元阵列MCAa或MCAb的位线对BLP选择性连接。开关元件SWa设置在感测放大器SA与一存储单元阵列MCAa的位线对BLP之间,开关元件SWb设置在感测放大器SA与另一存储单元阵列MCAb的位线对BLP之间。开关元件SWa、SWb分别设置在每一位线对BLP。开关元件SWa、SWb包含例如晶体管之类的半导体元件(未图示),将1个位线对BLP选择性连接到感测放大器SA。一开关元件SWa将存储单元阵列MCAa的位线对BLP连接到感测放大器SA时,另一开关元件SWb将存储单元阵列MCAb的位线对BLP与感测放大器SA电切断。相反地,开关元件SWb将存储单元阵列MCAb的位线对BLP连接到感测放大器SA时,开关元件SWa将存储单元阵列MCAa的位线对BLP与感测放大器SA电切断。即,开关元件SWa、SWb相辅地动作。

在读出/写入动作时,以将存储单元阵列MCAa、MCAb中包含选择字线WL的存储单元阵列的位线对BLP连接到感测放大器SA的方式,开关元件SWa、SWb的任一个成为接通状态,另一个成为断开状态。

感测放大器SA从经由开关元件SWa或SWb连接的位线对BLP,接收参照数据及信号数据,且检测信号数据。

本实施方式的半导体存储装置1可为图3A~图3C中所示的折叠位线构成的任一个。

进而,本实施方式也可适用于Twisted-BL方式。在此情况下,可利用加载到位线BL的噪声的共模噪声化带来的噪声降低效应,进而改善读出裕度。

图4是表示半导体柱31的形状的概略俯视图。半导体柱31从电容器元件20贯通字线WL连接到位线BL。在半导体衬底10的与表面大致平行的截面(X-Y截面)中,贯通字线WL的半导体柱31的形状如图4所示,成为字线WL的延伸方向(X方向)上具有长轴的细长形状。例如,半导体柱31的截面形状是X方向上具有长轴的大致椭圆形。即,半导体柱31的截面形状是X方向的宽度大于Y方向的宽度。在半导体柱31的外周设置有字线WL,半导体柱31的外周的长度成为单元晶体管30的通道宽度。因此,如果X-Y截面中的半导体柱31的外周长度较长,单元晶体管30的电流驱动能力就会提升。因此,优选半导体柱31的外周长度较长。

另一方面,在X-Y截面中,如果字线WL中半导体柱31所贯通的部分的宽度(即,字线WL的侧面与半导体柱31的距离)Ww较窄,就会导致字线WL的电阻上升。如果字线WL的电阻较高,就会导致驱动字线WL的速度变慢,而使装置整体的动作速度变慢。因此,考虑到字线WL的电阻,优选减小X-Y截面中的单元晶体管30的截面形状,增大宽度Ww。

因此,可通过将X-Y截面中的半导体柱31的形状设为X方向上具有长轴的细长形状,而一面增长半导体柱31的外周长度,一面扩大字线WL的宽度Ww。由此,解决了单元晶体管30的电流驱动能力提升与字线WL的电阻降低的权衡。

如上所述,根据本实施方式,可通过将氧化物半导体晶体管用作单元晶体管30,而将存储单元MC小型化,减小耗电,并且使写入动作及读出动作高速化。

进而,可通过采用折叠位线构成,抑制因氧化物半导体晶体管产生的噪声抗扰性低下。

接着,说明本实施方式的存储单元MC的制造方法。

图5~图10是表示本实施方式的存储单元MC的一例制造方法的剖视图。

首先,利用光刻技术及刻蚀技术,在半导体衬底10形成电极柱P。电极柱P的平面配置如同参照图2所说明。例如,电极柱P的中心在从半导体衬底10的上方观察时具有大致圆形,且如上所述,以成为平面最密堆积(即,六方最密配置)的方式配置。

接着,在半导体衬底10上形成绝缘部13。绝缘部13以热氧化法、CVD(ChemicalVapor Deposition,化学气相沉积)、ALD(Atomic Layer Deposition,原子层沉积)等形成即可。

接着,将单元电极14的材料沉积在半导体衬底10及绝缘部13上,利用光刻技术及刻蚀技术将半导体衬底10上的单元电极14的材料去除。由此,单元电极14形成在绝缘部13的上表面及侧面的一部分。由此,如图5所示,形成具有电极柱P、绝缘部13及单元电极14的电容器元件20。

接着,形成被覆电容器元件20的层间绝缘膜17-1。在层间绝缘膜17-1上形成字线WL,进而以将字线WL被覆的方式形成层间绝缘膜17-2。层间绝缘膜17-1、17-2也可为例如TEOS(TetraEthoOxySilane,四乙氧基硅烷)等氧化硅膜。

接着,利用光刻技术及刻蚀技术,以在电容器元件20上对应于电极柱P的方式,在层间绝缘膜17-1、17-2及字线WL形成开口OP。开口OP以贯通字线WL的方式对准。开口OP的底部到达单元电极14。由此,获得图5中所示的构造。

接着,如图6所示,利用CVD法或ALD法等,在层间绝缘膜17-2上、及开口OP的内表面上沉积栅极绝缘层32的材料。接着,利用RIE(Reactive Ion Etching,反应离子刻蚀)法,各向异性回蚀栅极绝缘层32。由此,如图6所示,使开口OP侧面的栅极绝缘层32留存,将开口OP的底部及层间绝缘膜17-2上的栅极绝缘层32的材料去除。

接着,如图7所示,利用CVD法或ALD法等,在层间绝缘膜17-2上、及开口OP的内表面沉积辅助层31CP的材料。接着,利用CVD法等,以填充开口OP的方式,沉积半导体柱31的材料(氧化物半导体)。

此处,辅助层31CP抑制在半导体柱31的材料与单元电极14之间形成高电阻的金属氧化物。因此,使半导体柱31与单元电极14之间的接触电阻降低。而且,辅助层31CP也具有在单元晶体管30的作为通道区域的半导体柱31与栅极绝缘层32之间,减少通道中移动的载流子的界面散射的功能。由此,可使单元晶体管30的载流子迁移率提升。

接着,如图8所示,利用CMP(Chemical Mechanical Polishing,化学机械研磨)法,研磨半导体柱31及辅助层31CP直到露出层间绝缘膜17-2。由此,将层间绝缘膜17-2上的半导体柱31及辅助层31CP去除,使半导体柱31及辅助层31CP残留在开口OP内。

而且,在露出层间绝缘膜17-2的上表面之后,还进行某种程度的过刻蚀。由此,在CMP处理后,半导体柱31及辅助层31CP的上表面位于比层间绝缘膜17-2的上表面更靠略微下方。

接着,如图9所示,利用CVD法等,在层间绝缘膜17-2上及半导体柱31上,沉积辅助层31BL的材料。接着,利用CMP法,研磨辅助层31BL的材料直到露出层间绝缘膜17-2的表面。由此,使辅助层31BL残留在开口OP内的半导体柱31上。由此,半导体柱31被辅助层31CP、31BL包围。

接着,如图10所示,在辅助层31BL上形成位线BL。由此,形成存储单元MC。此处,辅助层31BL如上所述地抑制在位线BL与半导体柱31之间形成金属氧化物。由此,可降低位线BL与半导体柱31之间的接触电阻。

此后,形成其它层间绝缘膜40及多层布线层(未图示)等,由此,完成本实施方式的半导体存储装置1。所述制造方法始终仅为一例,也可为其它制造方法。

(变化例1)

图11是表示所述实施方式的半导体存储装置的变化例1的剖视图。根据变化例1,存储单元MC设置在板状电极12上。

例如,在半导体衬底11的上方设置有板状电极12。在半导体衬底11与板状电极12之间,设置有层间绝缘膜,而未设置外围电路。多个存储单元MC在板状电极12上并联。多个存储单元MC的电容器元件20与板状电极12共通地电连接。Y方向上排列的多个存储单元MC共享位线BL。而且,这些多个存储单元MC与各不相同的字线WL连接。

板状电极12与多个存储单元MC共通地连接,且包含例如掺杂多晶硅、金属、金属硅化物等导电性材料。板状电极12经由接触插塞19,被设定为固定电位,且对电容器元件20的电极Eb施加固定电位。

位线BL经由接触插塞18及晶体管T连接到未图示的外围电路。外围电路配置在例如存储单元MC的周边。

例如,在读出/写入时,选择1条字线WL。将1条选择字线WL设定为有效状态(例如,高电平电压),将此外的非选择字线设定为无效状态(例如,低电平电压)。由此,包含感测放大器的外围电路可经由位线BL检测与选择字线WL连接的存储单元MC中储存的电荷。

(变化例2)

图12是表示所述实施方式的半导体存储装置的变化例2的剖视图。变化例2中,存储单元MC设置在外围电路21上设置的板状电极12上。

例如图12中,在半导体衬底11上,设置有包含感测放大器等的外围电路(CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)电路)21,且在外围电路21上设置有板状电极12。多个存储单元MC在板状电极12上并联。多个存储单元MC的电容器元件20与板状电极12共通地电连接。Y方向上排列的多个存储单元MC共享位线BL。而且,这些多个存储单元MC与各不相同的字线WL连接。

板状电极12与多个存储单元MC共通地连接,且包含例如掺杂多晶硅、金属、金属硅化物等导电性材料。板状电极12经由接触插塞19,被设定为固定电位,且对电容器元件20的电极Eb施加固定电位。

位线BL经由接触插塞18及晶体管T连接到外围电路(包含感测放大器)21。外围电路21配置在例如存储单元MC的正下方。

例如,在读出/写入时选择1条字线WL。将1条选择字线WL设定为有效状态(例如,高电平电压),将此外的非选择字线设定为无效状态(例如,低电平电压)。由此,包含感测放大器的外围电路21可经由位线BL检测与选择字线WL连接的存储单元MC中储存的信息,或者经由位线BL将信息写入到与选择字线WL连接的存储单元MC中。

(变化例3)

存储单元MC可设置在外围电路21上,但也可与外围电路21的侧方相邻配置。在此情况下,板状电极12也可与外围电路21的布线在同一层包含同一材料。虽将与板状电极12连接的接触插塞的图示省略,但板状电极12经由接触插塞,被设定为固定电位,且对电容器元件20的电极Eb施加固定电位。

例如,图13是表示所述实施方式的DRAM的变化例3的剖视图。变化例3中,存储单元MC与外围电路21在Y方向上相邻配置。板状电极12形成为与设置在接触插塞18的中途的布线12a及设置在外围电路21的布线(本地布线)12b同一层且同一材料。图13中,省略了外围电路21的布线12a、12b以外的构成的图示。如此一来,板状电极12也可利用外围电路21的布线的形成步骤同时形成。此外,接触插塞18是从位线BL经由布线12a连接到晶体管T的扩散层,但也可不经由布线12a而直接从位线BL连接到扩散层。

图14A~图14C是表示其它折叠位线构成的配置的概略俯视图。这些折叠位线构成在2条位线BL之对BLP与1个感测放大器SA连接的方面与图3A~图3C中所示的构成相同。然而,图14A~图14C中所示的折叠位线构成在与感测放大器SA连接的位线对的位线间,配置有与其它感测放大器SA连接的至少1条其它位线。

这种折叠位线构成的半导体存储装置1即便将氧化物半导体晶体管用作单元晶体管30使存储单元MC小型化,使位线BL间的间距Pb变窄,也可通过采用折叠位线构成,而提升噪声抗扰性。

图14A的构成中,感测放大器SA排列在存储单元阵列MCA的两端。在与设置在存储单元阵列MCA的一端侧的感测放大器SAa连接的位线对BLP的位线BL间,配置有与设置在存储单元阵列MCA的另一端侧的感测放大器SAb连接的位线对BLP。即,在与感测放大器SAa连接的位线对BLP的位线BL间,插入有与其它感测放大器SAb连接的2条其它位线对BLP。

图14A中,感测放大器SAa仅配置在存储单元阵列MCA的一端侧,且感测放大器SAb仅配置在存储单元阵列MCA的另一端侧。另一方面,图14B的构成中,交错地交替呈现感测放大器SAa与感测放大器SAb的关系。例如,在存储单元阵列MCA的一端侧,像感测放大器SAa、SAb、SAa…这样,交替地配置感测放大器SAa、SAb。在存储单元阵列MCA的另一端侧,像感测放大器SAb、SAa、SAb…这样,交替地配置感测放大器SAb、SAa。也可以是这种构成。

图14C的构成中,感测放大器SAc、SAd均排列在存储单元阵列MCA的一端。在与感测放大器SAc连接的位线对BLP的位线BL间,配置有与相邻的感测放大器SAd连接的位线对BLP。与感测放大器SAd连接的位线对BLP以不在感测放大器SAc的位线对BLP的一位线BL短路的方式,至少在它们的交叉部,布线在交叉部的上方或下方。例如,图15A及图15B是表示图14C的交叉部的更详细构成的图。如图15A所示,感测放大器SAc的位线对BLP的其中一个在交叉部分,因上层布线UW而比感测放大器SAd的位线对BLP更迂回。或者,如图15B所示,感测放大器SAd的位线对BLP在交叉部分,利用上层布线UW而比感测放大器SAc的位线对BLP的其中一个更迂回。在上层布线UW与它下方的位线或位线对之间,设置有层间绝缘膜。此外,CNT是位线BL与上层布线UW的触点。由此,在与感测放大器SAc连接的位线对BLP的位线BL间,插入有与相邻感测放大器SAd连接的2条其它位线对BLP。

本实施方式的半导体存储装置1也可为图14A~图14C中所示的折叠位线构成的任一个。

尽管已经描述了某些实施例,但是这些实施例仅是通过示例的方式给出的,并且不意图限制本发明的范围。实际上,本文描述的新颖的方法和系统能够以多种其它形式来体现;此外,在不背离本发明的精神的情况下,可以对本文所述的方法和系统的形式进行各种省略、替代和改变。所附权利要求及其等效形式旨在包含本发明的范围和精神内之形式与变化。

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统