延迟锁定回路、存储器元件以及该延迟回路的操作方法

文献发布时间:2023-06-19 11:45:49

技术领域

本公开主张2019年12月23日申请的美国正式申请案第16/725,239号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

背景技术

一般而言,一动态随机存取存储器(DRAM)的一延迟锁定回路(delay-lockedloop,DLL)电路用于调整在动态随机存取存储器中的一数据输出与输入时钟信号之间的时间差,直到其校准为止。该存储器可在一正常模式(normal mode)、一自刷新模式(self-refresh mode)或一省电模式(power-down mode)下进行操作。在该正常模式下,存取该存储器用以读取/写入操作,且在所述多个读取操作期间,延迟锁定回路电路延迟一输入时钟信号,以产生一延迟时钟信号。在该自刷新模式下,该存储器执行一自刷新操作,且没有来自一外部电路的帮助。在该省电模式下,该存储器在一待命模式(stand-by mode),且并未执行任何数据存取。

当一读取需求进入该随机动态存取存储器时,则开启该延迟锁定回路电路以及一输出缓冲,且一相位检测器比较由一输入时钟信号所获得的一参考时钟信号以及由延迟锁定回路电路所提供的一反馈信号,以决定在延迟锁定回路电路中的延迟线的一调整值。请参考图1,为了限制功耗,在一第一读取操作READ_01完成的后以及在请求一第二读取操作READ_02之前,延迟锁定回路电路与该输出缓冲是一贯地关闭。因此,提高了提供给延迟锁定回路电路的一电压VDLL;在已经过去一预定时间区间之后,电压VDLL达到一预定饱和电压Vsat。理想地,当请求该第二读取操作READ_02时,由于开启延迟锁定回路电路,所以降低电压VDLL;然而,延迟锁定回路电路的一(请求)响应时间(response time)Td造成该输入时钟信号CLKIN以及该输出数据DQ的一未校准(misalignment)。

上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明公开本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

发明内容

在本公开的一实施例中,提供一种延迟锁定回路电路。该延迟锁定回路电路包括一延迟线以及一控制单元。该延迟线具有多个延迟单元,并经配置以延迟一输入信号以产生一第一延迟信号。该控制单元接收该输入信号、一存取开始信号以及一存取结束信号;该控制单元经配置以依据该输入信号、该存取开始信号以及该存取结束信号而产生一控制信号,其中该控制信号用于控制该延迟线在二读取操作之间的一时间区间期间产生该第一延迟信号。

在本公开的一些实施例中,在已经发生多个时钟周期之后,该控制单元传输该控制信号到该延迟线。

在本公开的一些实施例中,该控制单元还包括一计数器(counter),用于计数该时钟周期的数量。

在本公开的一些实施例中,在一时间区间(time period)过去之后,该控制单元传输该控制信号到该延迟线。

在本公开的一些实施例中,该控制单元还包括一计时器(timer),用于决定该时间区间。

在本公开的一些实施例中,该延迟锁定回路电路还包括一相位检测器(phasedetector),接收该输入信号以及一反馈信号,该相位检测器经配置以选择地检测该输入信号以及该反馈信号的相位,以产生一相位检测结果,其中在所述多个读取操作期间,该相位检测结果用于控制该延迟线,并依据该第一延迟信号产生该反馈信号。

本公开的一些实施例中,该延迟锁定回路电路还包括一时钟树、一晶片外元件(off-chip device,OCD)以及一延迟仿效(delay mimic)。该时钟树经配置以延迟该第一延迟信号,以产生一第二延迟信号。该晶片外元件接收该第二延迟信号以及一输出数据。该延迟仿效接收该第一延迟信号并产生该反馈信号,其中在该反馈信号中的一虚拟延迟(dummydelay)用于匹配该时钟树与该晶片外元件的延迟。

在本公开的另一实施例中,提供一种存储器元件。该存储器元件包括多个存储器胞;以及多个周边元件(peripheral devices),用于从所述多个存储器胞读取数据或将数据写入到该存储器胞。所述多个周边元件包括一延迟锁定回路电路,该延迟锁定回路电路包括一延迟线以及一控制单元。该延迟线具有多个延迟单元,该延迟线经配置以延迟一输入信号以产生一第一延迟信号。该控制单元接收该输入信号、一存取开始信号以及一存取结束信号,该控制单元经配置以依据该输入信号、该存取开始信号以及该存取结束信号而产生一控制信号,进而控制该延迟线在二读取操作之间的一时间区间期间产生该第一延迟信号。

本公开的一些实施例中,在已经发生多个时钟周期(clock cycles)之后,该控制单元传输该控制信号到该延迟线。

本公开的一些实施例中,该控制单元还包括一计数器,用于计数该时钟周期的数量。

本公开的一些实施例中,在一时间区间过去之后,该控制单元传输该控制信号到该延迟线。

本公开的一些实施例中,该控制单元还包括一计时器,用于决定该时间区间。

本公开的一些实施例中,该存储器元件还包括一相位检测器,接收该输入信号以及一反馈信号,该相位检测器经配置以选择地检测该输入信号以及该反馈信号的相位,以产生一相位检测结果,其中在所述多个读取操作期间,该相位检测结果用于控制该延迟线,并依据该第一延迟信号产生该反馈信号。

本公开的一些实施例中,该存储器元件还包括一时钟树、一晶片外元件以及一延迟仿效;该时钟树经配置以延迟该第一延迟信号,以产生一第二延迟信号。该晶片外元件接收该第二延迟信号以及一输出数据。该延迟仿效接收该第一延迟信号并产生该反馈信号,其中在该反馈信号中的一虚拟延迟用于匹配该时钟树与该晶片外元件的延迟。

在本公开的另一实施例中,提供一种延迟锁定回路电路的操作方法。该延迟锁定回路电路的操作方法的步骤包括施加一输入信号到一延迟线,并以该延迟线延迟该输入信号以产生一第一延迟信号,而该延迟线具有多个延迟单元;以及输入该输入信号、一存取开始信号以及一存取结束信号到一控制单元,并通过该控制单元依据该输入信号、该存取开始信号以及该存取结束信号以产生一控制信号,其中在多个读取操作之间的一时间区间期间,该控制信号用于控制该延迟线以产生该第一延迟信号。

在本公开的一些实施例中,该延迟锁定回路电路的操作方法还包括:通过一计数器计数该存取开始信号与该存取结束信号之间的时钟周期数量,并已经在通过该计数器计数一预定数量的时钟周期之后,产生该控制信号。

在本公开的一些实施例中,该延迟锁定回路电路的操作方法还包括:通过一计时器决定在该存取开始信号与该存取结束信号之间的一时间区间,并在一时间区段(timesegment)过去之后,产生该控制信号。

在本公开的一些实施例中,延迟锁定回路电路的操作方法还包括:输入该输入信号以及一反馈信号到一相位检测器,并通过该相位检测器选择地检测该输入信号与该反馈信号的相位,以产生一相位检测结果,其中在所述多个读取操作期间,该相位检测结果用于控制该延迟线,并依据该第一延迟信号产生该反馈信号。

由于在本公开中延迟锁定回路电路的控制机制,可调整在输出数据与输入信号之间的未校准。通过实施在延迟锁定回路电路的控制单元中的一计数器、一计时器或其他适用的技术,可在高速伴随最低功耗下矫正所述的未对准(misalignments)。

上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得优选了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或工艺而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离权利要求所界定的本公开的构思和范围。

附图说明

参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

图1为示意图,其是描述输入到一存储器的一命令、提供到该存储器的延迟锁定回路电路的一电压、由该延迟锁定回路电路的一延迟线所提供的一第一延迟信号以及从该存储器输出的数据之间的关系。

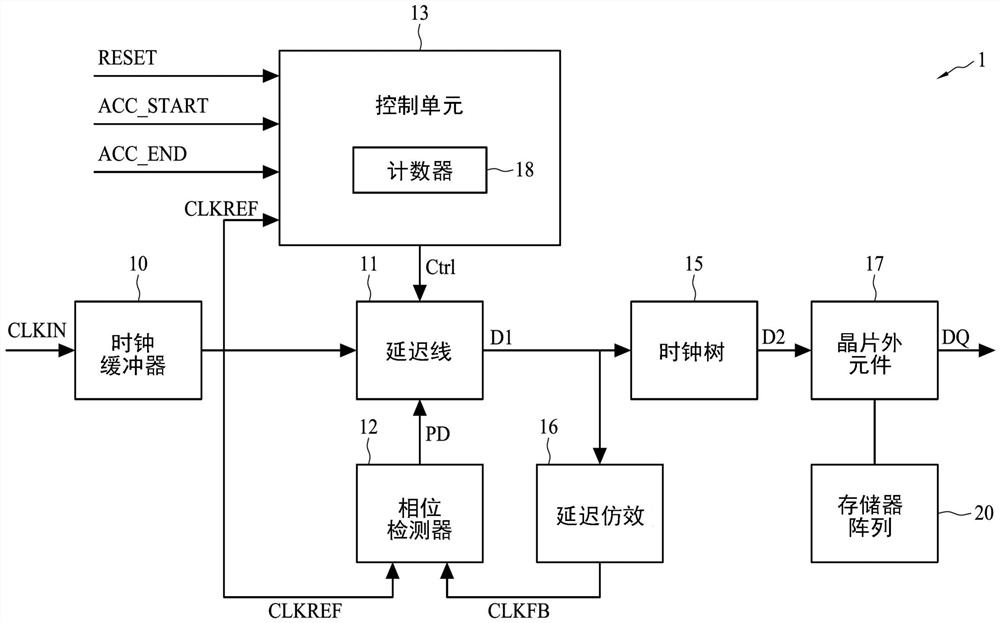

图2为依据本公开一些实施例的一种延迟锁定回路电路的方框示意图。

图3为依据本实施例的示意图,其是描述输入到一存储器元件的一命令、提供到该存储器元件的一延迟锁定回路电路的一控制电压、由延迟锁定回路电路的一延迟线所提供的一第一延迟信号以及从该存储器元件输出的数据之间的关系。

图4为依据本公开一些实施例的一种延迟锁定回路电路的方框示意图。

图5为依据本公开一些实施例的应用延迟锁定回路电路的一种存储器元件的方框示意图。

图6为依据本公开一些实施例的示意图,其是描述一或多个如图5的存储器元件使用在一系统。

图7为依据本公开一些实施例的一种延迟锁定回路电路的操作方法的流程图。

附图标记说明:

1:延迟锁定回路电路

2:延迟锁定回路电路

10:时钟缓冲器

11:延迟线

12:相位检测器

13:控制单元

15:时钟树

16:延迟仿效

17:晶片外元件

18:计数器

20:存储器阵列

33:控制单元

38:计时器

400:存储器元件

420:存储器芯片

422:引脚

423:存储器位址引脚或位址总线

424:数据引脚或数据总线

425:控制引脚或控制总线

426:存储器胞

428:列解码电路

430:行解码电路

432:输入/输出单元

500:系统

535:计算单元

536:处理器

538:总线

540:存储器控制器

542:总线

544:输入元件

546:输出元件

548:数据存储元件

ACC_START:存取开始信号

ACC_END:存取结束信号

CLKFB:反馈信号

CLKIN:输入时钟信号

CLKREF:参考时钟信号

COMM:命令

Ctrl:控制信号

D1:第一延迟信号

D2:第二延迟信号

DQ:输出数据

PD:相位检测结果

READ_01:第一读取操作

READ_02:第二读取操作

RESET:重设信号

Td:响应时间

VDLL:电压

Vsat:预定饱和电压

S610:步骤

S630:步骤

S640:步骤

具体实施方式

本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等是指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

为了使得本公开可被完全理解,以下说明提供详细的步骤与结构。显然,本公开的实施不会限制该技艺中的技术人士已知的特定细节。此外,已知的结构与步骤不再详述,以免不必要地限制本公开。本公开的优选实施例详述如下。然而,除了详细说明之外,本公开亦可广泛实施于其他实施例中。本公开的范围不限于详细说明的内容,而是由权利要求定义。

本公开针对延迟锁定回路电路、存储器元件以及延迟锁定回路电路的操作方法。为了使本公开完全地可理解,详细的步骤以及结构提供在下列的描述中。显而易见地,本公开的实施并不会限制所属技术领域中技术人员所熟知的特殊细节。此外,已知的结构与步骤不会详细描述,慈不会没必要地限制本公开。本公开的优选实施例会在下列详细描述。然而,除了所述多个详细描述之外,本公开亦可广泛地实施在其他实施例中。本公开的范围不会被所述多个详细描述所限制,而是由权利要求所界定。

依据本公开的一些实施例,图2为描述一种延迟锁定回路电路1的方框示意图。如图2所示,一输入时钟信号CLKIN提供到一延迟锁定回路电路1的一时钟缓冲器10,而延迟锁定回路电路1经配置以调整在一输出数据DQ与输入时钟信号CLKIN之间的一时间差。时钟缓冲器10耦接到一延迟线11、一相位检测器12以及一控制单元13。时钟缓冲器10从一外部系统时钟(external system clock)接收输入时钟信号CLKIN,并提供一参考时钟信号CLKREF,而该外部系统时钟当作是微处理器。应当理解,时钟缓冲器10可包括一或多个缓冲器,其是接收输入时钟信号CLKIN。

在一些实施例中,延迟线11耦接到控制单元13、相位检测器12以及时钟缓冲器10。延迟线11可包括多个延迟单元(图未示),举例来说,其是可包括一网络(network)或一连串的反相器(inverters),虽然亦可包括所述多个延迟单元的其他适用的实施。参考时钟信号CLKREF供应到延迟线11,而延迟线11可在一延迟阶段以所述多个延迟单元延迟参考时钟信号CLKREF,以产生一第一延迟信号D1,其是提供给一时钟树15以及一延迟仿效16。

时钟树15可为一复制输出信号缓冲器,其是接收第一延迟信号D1并产生一第二延迟信号D2,而第二延迟信号D2提供给一晶片外元件(OCD)17。延迟仿效16接收第一延迟信号D1并产生一反馈信号CLKFB。延迟仿效16可为一复制时钟缓冲器,其是通过缓冲第一延迟信号D1而产生反馈信号CLKFB。延迟缓冲16经配置以从延迟线11通过一特定时间区间而延迟第一延迟信号D1。在一些实施例中,当延迟仿效16经配置以提供与时钟树15及晶片外元件17相同的延迟区间。换言之,在反馈信号CLKFB中的一虚拟延迟用来匹配时钟树15及晶片外元件17的延迟。

在一些实施例中,晶片外元件17经配置以从一存储器阵列20锁存(latch)数据,而存储器阵列20具有多个存储器胞(图未示),且所述多个存储器胞用于存储数据以及将由从一存储器元件而来的数据转移至一数据请求元件(data-requesting device),而存储器元件包括存储器阵列20,数据请求元件例如一微处理器。存储器元件以及使用该存储器元件的一系统将在本公开的后文详述。

在一些实施例中,相位检测器12接收参考时钟信号CLKREF以及反馈信号CLKFB当作用于选择的检测参考时钟信号CLKREF以及反馈信号CLKFB的输入,并产生一相位检测结果PD。举例来说,可通过一相位比较器(phase comparator)(图未示)执行相位检测,其是比较参考时钟信号CLKREF与反馈信号CLKFB的(上升或下降)边缘的相对时间。依据相位检测结果PD,延迟线11可调整所述多个延迟单元的延迟阶段,以便建立锁定状态(lockcondition)。该调整可从多个位移暂存器(shift registers)或其他适合的电路(图未示)传送,举例来说,相位检测结果PD可包括一左移指令(shift left instruction)(例如减少被致动延迟阶段),或一右移指令(shift right instruction)(例如致动更多延迟阶段),以提供给延迟线11。

如图2所示,延迟锁定回路电路1还包括一控制单元13,经配置以产生一控制信号Ctrl并提供控制信号Ctrl给延迟线11,以便在二读取操作之间的一时间间隔(timeinterval)等于或大于一预定时间区间(period of time)时,延迟线11可导入至少一特定延迟期间(delay period)到参考时钟信号CLKREF。在一些实施例中,控制单元13可依据由存储器元件传出的一存取开始信号ACC_START与一存取结束信号ACC_END以及从时钟缓冲器10传出的参考时钟信号CLKREF以产生控制信号Ctrl。在一些实施例中,在二读取操作之间的时间间隔可至少由参考时钟信号CLKREF以及存取结束信号ACC_END所决定。在另外的实施例中,在二读取操作之间的时间间隔可为开始于存取结束信号ACC_END的检测以及结束于当提供给延迟锁定回路电路1达到一饱和电压Vsat时。如此的时间间隔可为一效能参数(performance parameter),其是表明存储器元件的性能(behavior)。在一些实施例中,当接收到一重设信号RESET时,则重设计数器18。重设信号RESET可由微处理器或存储器元件提供。

请参考图3,其包括一输入时钟信号CLKIN、输入到存储器元件的命令COMM、提供给延迟锁定回路电路1的控制电压VDLL、由延迟线11所提供的第一延迟信号D1以及由存储器元件传出的数据DQ的时序图。数据DQ可为数据请求元件所提出请求的数据。在第一读取操作READ_01期间,可使能(enabled)延迟锁定回路电路1以及时钟树15,且相位检测器12检测参考时钟信号CLKREF以及反馈信号CLKFB的相位,以产生相位检测结果PD给位于延迟锁定回路电路1中的延迟线11。因此,延迟线11可依据由相位检测器121所提供的相位检测结果PD产生第一延迟信号D1。在第一读取操作READ_01完成之后,时钟树15被禁能(disabled),直到请求一第二读取操作READ_02为止,而延迟线11则通过控制单元33周期地使能,以位移(shift)参考时钟信号CLKREF的相位,以便降低输入时钟信号CLKIN与当地二读取请求输入时的数据DQ之间的时间差Td。

请参考图2,在一些实施例中,控制单元13还包括一计数器18,用于计数第一读取操作READ_01的存取结束信号ACC_END与第二读取操作READ_02的存取开始信号ACC_START之间的时钟周期数量。在另外的实施例中,计数器18可测量开始于存取结束信号ACC_END的检测且结束于提供给延迟锁定回路电路1的电压达到饱和电压Vsat时的时间区间。举例来说,可依据时钟周期(clock cycles)的数量产生控制信号Ctrl。在一些实施例中,在已经计数时钟周期的一预定数量之后,控制单元13传送控制信号Ctrl到延迟线11。

在一些实施例中,延迟线11可依据控制信号Ctrl致动(activated)一些延迟单元。举例来说,可依据控制信号Ctrl在延迟阶段致动所述多个延迟单元。在一些实施例中,所述多个延迟单元的调整可从位移暂存器或其他适合的电路(图未示)传送。举例来说,控制信号Ctrl可具有一左移指令(例如减少被致动延迟阶段),或一右移指令(例如致动更多延迟阶段),以提供给延迟线11。

在延迟锁定回路电路1中的控制单元13的控制机制会在谢列的例子中描述。请参考图3,在第一读取操作READ_01完成以及存取结束信号ACC_END被控制单元13接收之后,控制单元13的计数器18可计数参考时钟信号CLKREF的时钟周期,直到接收到存取开始信号ACC_START为止或是直到已经计数到特定数量的时钟周期。当计数的时钟周期等于特定数量的时钟周期时,控制单元13可提供至少一控制信号Ctrl到延迟线11并位移参考时钟信号CLKREF的相位。由于在第二读取操作READ_02之前,延迟线11的所述多个延迟阶段已经通过控制单元13依据控制信号Ctrl进行调整,其中所述多个延迟阶段由在控制单元13中的计数器18所计数的时钟周期数量所决定,所以延迟锁定回路电路1能够降低第二读取操作READ_02的(请求)响应时间Td。

应当理解,延迟锁定回路电路1中的控制单元13可通过其他适合的技术所实现。图4为依据本公开一些实施例的其他延迟锁定回路电路的方框示意图。请参考图4,一延迟锁定回路电路2可包括类似于延迟锁定回路电路1的零件,而这些类似零件的描述将不会在文中重复。延迟锁定回路电路2与延迟锁定回路电路1的差异,在于延迟锁定回路电路2的控制单元33。在一些实施例中,控制单元33还包括一计时器38,用于决定一存储器元件的第一读取操作READ_01的存取结束信号ACC_END与其第二读取操作READ_02的存取开始信号ACC_START之间的一时间区间,而存储器元件使用在延迟锁定回路电路2中。可依据由计时器38所决定的时间区间而产生控制信号Ctrl。举例来说,计时器38可决定存储器元件的二读取操作之间的一预定时间区间,且可依据由计时器38所决定的该预定时间区间而产生控制信号Ctrl。在一些实施例中,当已经过去一特定时间区间之后,控制单元33传送控制信号Ctrl到延迟线11。在一些实施例中,在二读取操作之间的时间区间可包括多个时间区段(timesegments),而控制单元33可传送控制信号Ctrl到延迟线11,也借此在过去了每一个时间区段之后,延迟参考时钟信号CLKREF。在一些实施例中,当接收到一重设信号RESET时,可重设(reset)计时器38。

在其他的实施例中,其他延迟锁定回路电路的一控制单元可包括一电路零件(circuit element),其是决定如图2所示的控制电压VDLL的电压电平(voltage level)。在此延迟锁定回路电路中,控制信号Ctrl可依据如由控制单元中的电路零件所决定的电压电平所产生。

图5为依据本公开一些实施例的应用延迟锁定回路电路的一种存储器元件400的方框示意图。举例来说,一存储器元件400可为一存储器芯片,其是使用如图2的延迟锁定回路电路1,虽然亦可使用本实施例的其他延迟锁定回路电路,例如图4的延迟锁定回路电路2。存储器元件400可为双列直插式存储器模块(Dual In-line Memory Module,DIMM)的一部分,或者是含有许多如此存储器芯片(图未示)的印刷电路板(printed circuit board,PCB)。存储器元件400可包括多个引脚(pins)422,位于存储器元件400外侧,用于将存储器元件400电性连接到其他系统元件。一些引脚422可包括存储器位址引脚或位址总线423、数据引脚或数据总线424以及控制引脚或控制总线425。应当理解,每一参考元件编号423到425可当作在对应总线中一个以上的引脚。也应当理解,在图5中的图示仅为图例说明。意即,在典型的存储器元件或存储器芯片中的引脚配置或架构,可不是如图5的形式。

一处理器(processor)或存储器控制器(memory controller)(如图6所示)可与存储器元件400进行通信,并执行存储器读取/写入操作。处理器及存储器元件400可使用在位址线或位址总线423上的位址信号、在数据线或数据总线424上的数据信号、以及在控制线或控制总线425上的控制信号(例如一列位址选通(row address strobe,RAS)信号、一栏位址选通(column address strobe,CAS)信号等等(图未示))进行通信。位址、数据以及控制总线的引脚的宽度或数量可因不同存储器架构而异。所属技术领域中技术人员将轻易地认出图5的存储器元件400已被简化,进而图例说明一存储器元件的一实施例,并非意图成为一典型存储器芯片的所有特征的详细叙述。典型地,可沿着存储器元件400提供众多周边元件或电路,用于将数据写入存储器元件400或从存储器元件400读取数据。然而,为了清楚起见,图5并未显示这些周边元件或电路。

存储器元件400可包括多个存储器胞426,一般为行、列排列,用于将数据存储其中。每一存储器胞426可存储一位元的数据。一列解码电路(row decode circuit)428以及一行解码电路(column decode circuit)430可选择在存储器元件400中的行或列,以响应到解码一位址,该位址是如位址总线423上所提供的位址。然后,数据经由感应放大器(sense amplifiers)以及一数据输出路径(图未示)而在所述多个存储器胞426与数据总线424之间传送。一存储器控制器(图未示)可提供在控制总线425上的相关的控制信号(图未示),以控制数据经由一输入/输出单元432通信到存储器芯片420或是从存储器芯片420进行通信(communication)。输入/输出单元432可包括多个数据输出缓冲器(图未示),以从所述多个存储器胞426接收所述多个数据位元,并提供所述多个数据位元或数据信号给在数据总线424中的对应数据线。存储器元件400还可包括一延迟锁定回路电路(例如图2的延迟锁定回路电路1),以调整在一输出数据DQ与一输入时钟CLKIN之间的时间差。

存储器控制器可决定存储器元件400的操作模式。在控制总线425上的输入信号或控制信号的一些例子,可包括一外部时钟信号、一芯片选择信号、一列存取选通(rowaccess strobe)信号、一行存取选通(column access strobe)信号、一写入使能(writeenable)信号等等。存储器元件400经由在存储器元件400上的所述多个引脚422而与和其连接的其他元件进行通信。如上所述的这些引脚可连接到适当的位址、数据以及控制线,以实施数据传送操作(data transfer operations)。

图6为依据本公开一些实施例的示意图,其是描述一或多个如图5的存储器元件400使用在一系统。该系统500可包括一计算单元(computing unit)535,其包括一处理器536,用于执行不同计算功能,例如执行特定软件以执行特定计算或数据处理任务。计算单元535亦可包括多个存储器元件400,其是经由一总线538与处理器536进行通信。总线538可包括一位址总线、一数据总线以及一控制总线(图未示)。每一存储器元件400可为一动态随机存取存储器芯片或其他形式的存储器电路,例如一静态随机存取存储器(SRAM)芯片或快闪存储器(Flash memory)。再者,DRAM可为一同步DRAM,通常为一同步图形随机存取存储器(synchronous graphics random access memory,SGRAM)﹐一SDRAM(synchronous dynamicrandom access memory)、一SDRAM II或一DDR SDRAM(double data rate SDRAM),如同Synchlink或Rambus DRAMs。所属技术领域中技术人员将轻易地认出图5及图6的存储器元件400已被简化,以图例说明一存储器元件的一实施例,而并未意图为一典型存储器芯片的所有特征的详细描述。处理器536可依据存储在所述多个存储器元件400中的信息或数据以执行覆述个功能。处理器536可为一微处理器、数字信号处理器、嵌入式处理器、微控制器、专用(dedicated)存储器测试芯片等等。

每一存储器元件400可具有类似于如图5所示的一架构(例如每一存储器元件400可包括依据本公开所述多个实施例所架构的延迟锁定回路电路)。相同的参考元件编号400使用在图5及图6,以表示这些存储器元件。一存储器控制器540控制数据通信到所述多个存储器元件400或从所述多个存储器元件400进行通信,以响应在从总线542上的处理器536所接收的多个控制信号(图未示)。存储器控制器540可包括一命令解码电路(command decodecircuit)(图未示)。命令解码电路可接收所述多个输入控制信号(在总线542上),以决定一或多个存储器元件400的操作模式。在总线542(以及可在总线538上)上的所述多个输入信号或控制信号的一些例子,包括一外部时钟信号、一芯片选择信号、一列存取选通信号、一行存取选通信号以及一写入使能信号。

系统500可包括一或多个输入元件544(例如一键盘、一鼠标等等),是连接到计算单元535以允许一使用者手动输入数据、指令(instructions)等等,进而操作计算单元535。亦可提供连接到计算单元535的一或多个输出元件546,当作系统500的一部分,以显示或是输出通过处理器536产生的数据。所述多个输出元件546的例子包括印表机、影像终端机(video terminals)或影像显示单元(video display units,VDUs)。在一些实施例中,系统500亦包括一或多个数据存储元件548,其是连接到计算单元535,以允许处理器536存储数据在内部或外部存储媒体(storage media)(图未示),或是从内部或外部存储媒体取回数据。典型的数据存储元件548的例子包括驱动机(drives),其是接收硬盘、软碟、光盘只读存储器(compact disk read-only memories,CD-ROM)以及卡式磁带(tape cassettes)。

依据本公开的一些实施例,图7为依据本公开一些实施例的一种延迟锁定回路电路的操作方法的流程图。请参考图7,该操作方法包括施加一输入信号到一延迟线,并以该延迟线延迟该输入信号,以产生一第一延迟信号(步骤S610)。该输入信号以及一反馈信号输入到一相位检测器,且通过该相位检测器执行该输入信号与该反馈信号的选择相位检测(selective phase detection),以产生一相位检测结果,进而在所述多个读取操作期间控制该延迟线,所述多个读取操作期间是在依据该第一延迟信号产生该反馈信号中(步骤S630)。该输入信号、一存取开始信号以及一存取结束信号输入到一控制单元,且通过该控制单元依据该输入信号、该存取开始信号以及该存取结束信号而产生一控制信号,进而控制位于二读取操作之间的该延迟线(步骤S640)。

在一些实施例中,该操作方法还包括通过一计数器计数位于该存取开始信号与该存取结束信号之间的时钟周期数量,并通过该计数器依据时钟周期的数量以产生该控制信号。

在一些实施例中,该操作方法还包括通过一计时器决定在该存取开始信号与该存取结束信号之间的一时间区间,并依据通过该计时器所决定的该时间区间以产生该控制信号。

在本公开的一实施例中,提供一种延迟锁定回路电路。该延迟锁定回路电路包括一延迟线以及一控制单元。该延迟线具有多个延迟单元,并经配置以延迟一输入信号以产生一第一延迟信号。该控制单元接收该输入信号、一存取开始信号以及一存取结束信号;该控制单元经配置以依据该输入信号、该存取开始信号以及该存取结束信号而产生一控制信号,其中该控制信号用于控制该延迟线在二读取操作之间的一时间区间期间产生该第一延迟信号。

在本公开的另一实施例中,提供一种存储器元件。该存储器元件包括多个存储器胞;以及多个周边元件,用于从所述多个存储器胞读取数据或将数据写入到该存储器胞。所述多个周边元件包括一延迟锁定回路电路,该延迟锁定回路电路包括一延迟线以及一控制单元。该延迟线具有多个延迟单元,该延迟线经配置以延迟一输入信号以产生一第一延迟信号。该控制单元接收该输入信号、一存取开始信号以及一存取结束信号,该控制单元经配置以依据该输入信号、该存取开始信号以及该存取结束信号而产生一控制信号,进而控制该延迟线在二读取操作之间的一时间区间期间产生该第一延迟信号。

在本公开的另一实施例中,提供一种延迟锁定回路电路的操作方法。该延迟锁定回路电路的操作方法的步骤包括施加一输入信号到一延迟线,并以该延迟线延迟该输入信号以产生一第一延迟信号,而该延迟线具有多个延迟单元;以及输入该输入信号、一存取开始信号以及一存取结束信号到一控制单元,并通过该控制单元依据该输入信号、该存取开始信号以及该存取结束信号以产生一控制信号,其中在多个读取操作之间的一时间区间期间,该控制信号用于控制该延迟线以产生该第一延迟信号。

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的构思与范围。例如,可用不同的方法实施上述的许多工艺,并且以其他工艺或其组合替代上述的许多工艺。

再者,本公开的范围并不受限于说明书中所述的工艺、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的工艺、机械、制造、物质组成物、手段、方法、或步骤。据此,这些工艺、机械、制造、物质组成物、手段、方法、或步骤是包含于本公开的权利要求内。

- 延迟锁定回路、存储器元件以及该延迟回路的操作方法

- 用于半导体存储器装置中的延迟锁定回路及其方法