信号接收电路、存储器存储装置及信号接收方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及一种信号接收技术,尤其涉及一种信号接收电路、存储器存储装置及信号接收方法。

背景技术

数字相机、移动电话与MP3播放器在这几年来的成长十分迅速,使得消费者对存储媒体的需求也急速增加。由于可复写式非易失性存储器模块(rewritable non-volatilememory module)(例如,快闪存储器)具有数据非易失性、省电、体积小,以及无机械结构等特性,所以非常适合内建于上述所举例的各种可携式多媒体装置中。

一般来说,为了克服信号传输时的通道损耗,信号的接收端电路会使用等化器对接收到的信号进行补偿并使用时脉数据回复电路来对信号进行相位锁定。此外,在某些接收端电路中,为了改善特定样式的信号对相位锁定造成的不良影响,时脉数据回复电路可能会对特定样式的信号进行过滤。但是,在某些情况下,根据通道状态不同,对特定样式的信号进行过滤反而会降低时脉数据回复电路的相位锁定效率,进而可能降低接收端电路的整体信号接收能力。

发明内容

本发明提供一种信号接收电路、存储器存储装置及信号接收方法,可有效针对不同通道状态提高或维持对于信号的接收能力。

本发明的范例实施例提供一种信号接收电路,其包括等化器模块、时脉数据回复电路及控制器。所述等化器模块用以接收第一信号并对所述第一信号进行补偿以产生第二信号。所述时脉数据回复电路连接至所述等化器模块并用以对所述第二信号执行相位锁定。所述控制器连接至所述等化器模块与所述时脉数据回复电路。所述控制器用以根据所述第二信号开启或关闭所述时脉数据回复电路的信号样式过滤器,且所述信号样式过滤器用以过滤所述第二信号中具有特定样式的信号。

在本发明的一范例实施例中,所述控制器还用以根据对所述信号样式过滤器的控制调整所述等化器模块的设定参数。

本发明的范例实施例另提供一种存储器存储装置,其包括连接接口单元、可复写式非易失性存储器模块、信号接收电路及存储器控制电路单元。所述连接接口单元用以连接至主机系统。所述信号接收电路设置于所述连接接口单元。所述存储器控制电路单元连接至所述连接接口单元、所述可复写式非易失性存储器模块及所述信号接收电路。所述信号接收电路用以接收第一信号并对所述第一信号进行补偿以产生第二信号。所述信号接收电路还用以对所述第二信号执行相位锁定。所述信号接收电路还用以根据所述第二信号开启或关闭信号样式过滤器,且所述信号样式过滤器用以过滤所述第二信号中具有特定样式的信号。

在本发明的一范例实施例中,在所述信号样式过滤器被开启后,所述信号接收电路中的时脉数据回复电路仅处理所述第二信号中具有所述特定样式的所述信号。

在本发明的一范例实施例中,根据所述第二信号开启或关闭所述信号样式过滤器的操作包括:分析所述第二信号以获得评估参数,其中所述评估参数反映所述信号接收电路中的等化器模块的收敛状态与所述第一信号传输时的通道损耗状况的至少其中之一。

在本发明的一范例实施例中,根据所述第二信号开启或关闭所述信号样式过滤器的操作还包括:根据所述评估参数与临界值的比较结果决定开启或关闭所述信号样式过滤器。

在本发明的一范例实施例中,根据所述评估参数与所述临界值的所述比较结果决定开启或关闭所述信号样式过滤器的操作包括:若所述比较结果符合预设条件,开启所述信号样式过滤器;以及若所述比较结果不符合所述预设条件,关闭所述信号样式过滤器。

在本发明的一范例实施例中,若所述比较结果符合所述预设条件,开启所述信号样式过滤器的操作包括:若所述比较结果符合第一预设条件,开启第一信号样式过滤器,其中所述第一信号样式过滤器用以过滤所述第二信号中具有第一样式的信号;以及若所述比较结果符合第二预设条件,开启第二信号样式过滤器,其中所述第二信号样式过滤器用以过滤所述第二信号中具有第二样式的信号,且所述第一样式不同于所述第二样式。

在本发明的一范例实施例中,所述信号接收电路还用以根据对所述信号样式过滤器的控制调整等化器模块的设定参数。

本发明的范例实施例另提供一种信号接收方法,其用于存储器存储装置。所述信号接收方法包括:接收第一信号并对所述第一信号进行补偿以产生第二信号;对所述第二信号执行相位锁定;以及根据所述第二信号开启或关闭信号样式过滤器,其中所述信号样式过滤器用以过滤所述第二信号中具有特定样式的信号。

在本发明的一范例实施例中,在所述信号样式过滤器被开启后,所述存储器存储装置中的时脉数据回复电路仅处理所述第二信号中具有所述特定样式的所述信号。

在本发明的一范例实施例中,根据所述第二信号开启或关闭所述信号样式过滤器的步骤包括:分析所述第二信号以获得评估参数,其中所述评估参数反映所述存储器存储装置中的等化器模块的收敛状态与所述第一信号传输时的通道损耗状况的至少其中之一。

在本发明的一范例实施例中,根据所述第二信号开启或关闭所述信号样式过滤器的步骤还包括:根据所述评估参数与临界值的比较结果决定开启或关闭所述信号样式过滤器。

在本发明的一范例实施例中,根据所述评估参数与所述临界值的所述比较结果决定开启或关闭所述信号样式过滤器的操作包括:若所述比较结果符合预设条件,开启所述信号样式过滤器;以及若所述比较结果不符合所述预设条件,关闭所述信号样式过滤器。

在本发明的一范例实施例中,若所述比较结果符合所述预设条件,开启所述信号样式过滤器的操作包括:若所述比较结果符合第一预设条件,开启第一信号样式过滤器,其中所述第一信号样式过滤器用以过滤所述第二信号中具有第一样式的信号;以及若所述比较结果符合第二预设条件,开启第二信号样式过滤器,其中所述第二信号样式过滤器用以过滤所述第二信号中具有第二样式的信号,且所述第一样式不同于所述第二样式。

在本发明的一范例实施例中,所述的信号接收方法还包括:根据对所述信号样式过滤器的控制调整所述存储器存储装置中的等化器模块的设定参数。

基于上述,在对第一信号进行补偿以产生第二信号后,根据所述第二信号,时脉数据回复电路中用于过滤具有特定样式的信号的信号样式过滤器可被动态地开启或关闭。藉此,可有效针对不同通道状态提高或维持信号接收端对于信号的接收能力。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

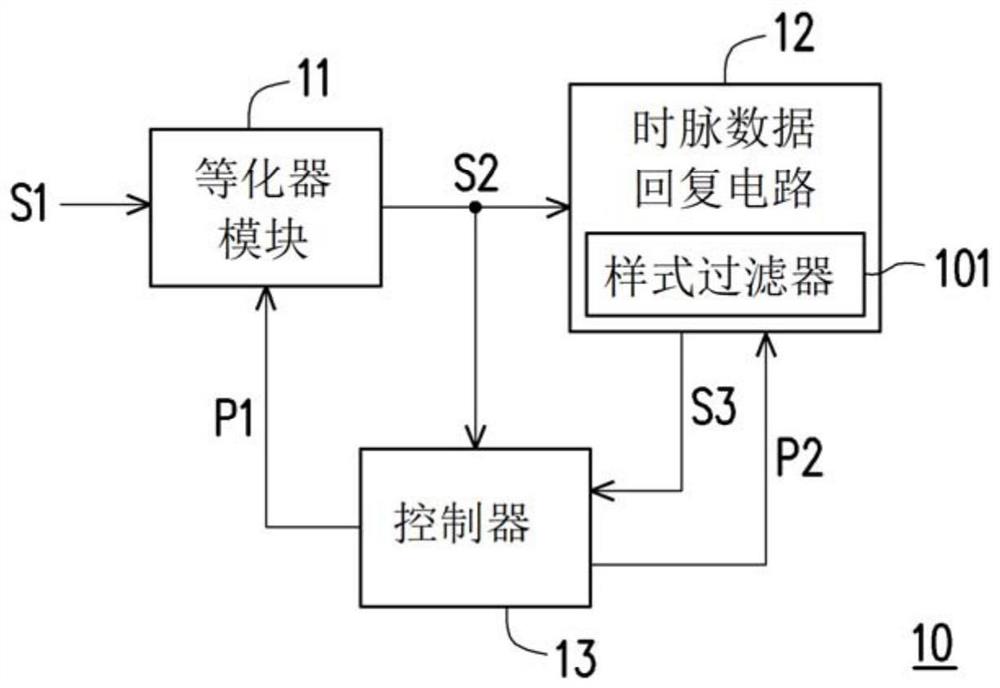

图1是根据本发明的一范例实施例所示出的信号接收电路的示意图;

图2是根据本发明的一范例实施例所示出的根据评估参数来调整等化器模块的设定参数与控制信号样式过滤器的示意图;

图3是根据本发明的一范例实施例所示出的信号接收电路的示意图;

图4是根据本发明的一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图;

图5是根据本发明的另一范例实施例所示出的主机系统、存储器存储装置及I/O装置的示意图;

图6是根据本发明的另一范例实施例所示出的主机系统与存储器存储装置的示意图;

图7是根据本发明的一范例实施例所示出的存储器存储装置的概要方块图;

图8是根据本发明的一范例实施例所示出的信号接收方法的流程图。

符号标记说明

10、30:信号接收电路

11、31:等化器模块

12、32:时脉数据回复电路

13、33:控制器

101、301:信号样式过滤器

S1、S2、S3、P1、P2、C1、C2、C3:信号

VTH1、VTH2、VTH3:临界值

VC1、VC2、VC3、VC1’、VC2’、VC3’:收敛值

311:线性等化器

312:决策反馈等化器

331:等化器控制器

332:信号样式过滤器控制器

40、60:存储器存储装置

41、61:主机系统

410:系统总线

411:处理器

412:随机存取存储器

413:只读存储器

414:数据传输接口

42:输入/输出(I/O)装置

520:主机板

501:U盘

502:存储卡

503:固态硬盘

504:无线存储器存储装置

505:全球定位系统模块

506:网络接口卡

507:无线传输装置

508:键盘

509:屏幕

510:喇叭

62:SD卡

63:CF卡

64:嵌入式存储装置

641:嵌入式多媒体卡

642:嵌入式多芯片封装存储装置

702:连接接口单元

704:存储器控制电路单元

706:可复写式非易失性存储器模块

S801:步骤(接收第一信号并对所述第一信号进行补偿以产生第二信号)

S802:步骤(对所述第二信号执行相位锁定)

S803:步骤(根据所述第二信号开启或关闭信号样式过滤器,其中所述信号样式过滤器用以过滤所述第二信号中具有特定样式的信号)

具体实施方式

以下提出多个范例实施例来说明本发明,然而本发明不仅限于所例示的多个范例实施例。又范例实施例之间也允许有适当的结合。在本案说明书全文(包括权利要求)中所使用的“连接”一词可指任何直接或间接的连接手段。举例而言,若文中描述第一装置连接于第二装置,则应该被解释成该第一装置可以直接连接于该第二装置,或者该第一装置可以通过其他装置或某种连接手段而间接地连接至该第二装置。此外,“信号”一词可指至少一电流、电压、电荷、温度、数据、或任何其他一或多个信号。

图1是根据本发明的一范例实施例所示出的信号接收电路的示意图。请参照图1,信号接收电路10包括等化器模块11、时脉数据回复电路12及控制器13。等化器模块11用以接收信号(亦称为第一信号)S1并对信号S1进行补偿以产生信号(亦称为第二信号)S2。例如,等化器模块11可包括线性等化器、连续时间线性等化器(Continuous-Time LinearEqualizer,CTLE)、无限脉冲响应电路(Infinite Impulse Response,IIR)及决策反馈等化器(Decision Feedback Equalizer,DFE)的至少其中之一。等化器模块11可根据当前的通道状态对信号S1进行补偿(例如放大)以产生信号S2。

时脉数据回复电路12连接至等化器模块11。时脉数据回复电路12用以接收信号S2并对信号S2执行相位锁定以产生信号S3(亦称为第三信号)。例如,时脉数据回复电路12可包括相位检测电路(未示出)、充电电路(未示出)及压控振荡器(未示出)。通过相位检测电路、充电电路及压控振荡器的共同运作,时脉数据回复电路12可逐渐将信号S2的相位与信号S3的相位保持同步。当信号S2的相位发生变化时,时脉数据回复电路12可再次将信号S2的相位与信号S3的相位保持同步。在一范例实施例中,使信号S2的相位与信号S3的相位保持同步的操作亦称为相位锁定。

须注意的是,时脉数据回复电路12还包括信号样式过滤器(亦称为样式过滤器)101。信号样式过滤器101可被动态地启动或关闭。在启动信号样式过滤器101后,信号样式过滤器101可用以过滤信号S2中具有特定样式(pattern)的信号,且时脉数据回复电路12可仅对信号S2中具有此特定样式的信号进行处理(例如执行相位锁定)。例如,假设此特定样式对应于比特“001”,则在启动信号样式过滤器101后,信号样式过滤器101可用以过滤信号S2中带有比特“001”的信号,且时脉数据回复电路12只针对信号S2中带有比特“001”的信号进行处理。此外,若信号样式过滤器101未被启动(即被关闭),则信号样式过滤器101可不过滤信号S2中具有特定样式的信号,且时脉数据回复电路12可对信号S2中不具有特定样式的信号或所有信号进行处理。

控制器13连接至等化器模块11与时脉数据回复电路12。控制器13用以根据信号S2来开启或关闭信号样式过滤器101。例如,控制器13可包括可程序化的一般用途或特殊用途的微处理器、嵌入式控制器、数字信号处理器(Digital Signal Processor,DSP)、可程序化控制器、特殊应用集成电路(Application Specific Integrated Circuits,ASIC)、可程序化逻辑装置(Programmable Logic Device,PLD)或其他类似装置或这些装置的组合。此外,控制器13还用以根据信号S2来决定或调整等化器模块11的设定参数。

在一范例实施例中,控制器13可根据信号S2与信号S3来发送信号(亦称为第一控制信号)P1至等化器模块11以通过信号P1来调整等化器模块11的设定参数。例如,等化器模块11对于信号S1的补偿能力可通过调整等化器模块11的设定参数来进行调整。等化器模块11可根据此设定参数来持续对信号S1进行补偿并产生信号S2。

在一范例实施例中,控制器13可根据信号S2来发送信号(亦称为第二控制信号)P2至时脉数据回复电路12。时脉数据回复电路12可根据信号P2来开启或关闭信号样式过滤器101。例如,信号P2可指示开启或关闭信号样式过滤器101中的特定信号样式过滤器。

在一范例实施例中,控制器13可分析信号S2以获得至少一评估参数。在一范例实施例中,此评估参数可反映等化器模块11的收敛状态。在一范例实施例中,,此评估参数可反映与信号S1有关的通道状态。在一范例实施例中,此评估参数可反映等化器模块11的收敛状态与接收信号S1时的通道损耗状况的至少其中之一。

在一范例实施例中,控制器13可根据此评估参数来调整等化器模块11的设定参数和/或开启(或关闭)信号样式过滤器101。例如,在一范例实施例中,若此评估参数反映等化器模块11的收敛状态不好和/或通道状态较差(例如信号S1的通道损耗较大)时,控制器13可调整等化器模块11的设定参数和/或可开启信号样式过滤器101。或者,在一范例实施例中,若此评估参数反映等化器模块11的收敛状态很好和/或通道状态较佳(例如信号S1的通道损耗较小)时,控制器13可不调整等化器模块11的设定参数和/或可关闭信号样式过滤器101。

在一范例实施例中,控制器13可根据此评估参数与至少一个临界值的比较结果决定开启或关闭信号样式过滤器101。在一范例实施例中,假设信号样式过滤器101的数目为一个。若比较结果符合一预设条件,控制器13可开启信号样式过滤器101。然而,若比较结果不符合此预设条件,则控制器13可关闭信号样式过滤器101。

在一范例实施例中,假设信号样式过滤器101的数量为多个,且此些信号样式过滤器101可用以过滤信号S2中具有不同样式的信号。例如,假设信号样式过滤器101包括第一信号样式过滤器与第二信号样式过滤器。第一信号样式过滤器用以过滤信号S2中具有第一样式的信号。第二信号样式过滤器用以过滤信号S2中具有第二样式的信号。第一样式不同于第二样式。例如,第一样式可对应比特“001”和/或第二样式可对应比特“010”。第一信号样式过滤器与第二信号样式过滤器可择一或同时被开启(或关闭)。

在一范例实施例中,临界值至少包括第一临界值与第二临界值。控制器13可将所获得的评估参数与第一临界值和/或第二临界值进行比较。若比较结果符合一预设条件(亦称为第一预设条件),控制器13可开启第一信号样式过滤器且不开启第二信号样式过滤器。或者,若比较结果符合另一预设条件(亦称为第二预设条件),控制器13可开启第二信号样式过滤器且不开启第一信号样式过滤器。或者,若比较结果符合另一预设条件(亦称为第三预设条件),控制器13可同时开启第一信号样式过滤器与第二信号样式过滤器。或者,若比较结果符合另一预设条件(亦称为第四预设条件),控制器13可同时关闭第一信号样式过滤器与第二信号样式过滤器。

在一范例实施例中,控制器13可根据当前对于信号样式过滤器101的控制(例如开启或关闭)来调整等化器模块11的设定参数。例如,若控制器13决定开启信号样式过滤器101中的某一个信号样式过滤器,则控制器13可同步调整等化器模块11的设定参数。例如,控制器13可指示等化器模块11采用与信号样式过滤器101中被开启的信号样式过滤器相互匹配的设定参数。例如,当控制器13指示开启第一信号样式过滤器时,控制器13可同步指示等化器模块11采用与第一信号样式过滤器相互匹配的设定参数。或者,当控制器13指示开启第二信号样式过滤器时,控制器13可同步指示等化器模块11采用与第二信号样式过滤器相互匹配的设定参数。或者,当控制器13指示同步开启第一信号样式过滤器与第二信号样式过滤器时,控制器13可同步指示等化器模块11采用与第一信号样式过滤器与第二信号样式过滤器的同步开启相互匹配的设定参数。

图2是根据本发明的一范例实施例所示出的根据评估参数来调整等化器模块的设定参数与控制信号样式过滤器的示意图。须注意的是,图2的曲线图中的横轴为时间,而纵轴为评估参数。

请参照图2,信号C1的逻辑低表示某一个信号样式过滤器处于关闭状态,且信号C1的逻辑高表示此信号样式过滤器处于开启状态。信号C2用以指示在此信号样式过滤器处于开启状态的期间,此信号样式过滤器可过滤的特定样式(例如比特“001”与“110”)。此外,信号C3用以指示在此信号样式过滤器处于开启状态的期间,图1的等化器模块11所采用的设定参数。

在图2的范例实施例中,假设一开始信号C1是处于逻辑低,故对应于信号C1的信号样式过滤器处于关闭状态。在此信号样式过滤器处于关闭状态的期间,3个评估参数被持续获得直到分别收敛至收敛值VC1~VC3。在评估参数分别收敛至收敛值VC1~VC3后,收敛值VC1~VC3可分别与临界值VTH1~VTH3进行比较。

在本范例实施例中,是假设比较结果为收敛值VC1大于临界值VTH1、收敛值VC2大于临界值VTH2、且收敛值VC3小于临界值VTH3。根据此比较结果,图1的控制器13可指示开启信号样式过滤器101中可用于过滤带有比特“001”或“110”的信号的信号样式过滤器并指示等化器模块11采用对应于“Setting 2”的设定参数。例如,在开启对应于信号C1的信号样式过滤器(即信号C1处于逻辑高)的期间,仅带有比特“001”或“110”的信号可被图1的时脉数据回复电路12处理(例如执行相位锁定)。

在开启对应于信号C1的信号样式过滤器(即信号C1处于逻辑高)并重新运行图1的等化器模块11与时脉数据回复电路12后,3个评估参数可被重新获得并分别收敛至新的收敛值VC1’~VC3’。新的收敛值VC1’~VC3’分别高于临界值VTH1~VTH3。

须注意的是,在图2的范例实施例中,是假设当前的通道状态较差(例如图1中信号S1的通道损耗较大)。因此,在开启对应于信号C1的信号样式过滤器之前(即信号C1处于逻辑低),收敛值VC1~VC3反映图1的等化器模块11的收敛状态不好。然而,在开启对应于信号C1的信号样式过滤器之后(即信号C1处于逻辑高),通过过滤特定样式的信号,新的收敛值VC1’~VC3’反映等化器模块11的收敛状态(例如收敛速度)被显著提升。此外,等化器模块11所采用的新的设定参数“Setting 2”也可能对于等化器模块11的收敛状态提升有所帮助。

须注意的是,图2的范例实施例是以收敛值VC1~VC3中的至少一者越大代表图1的等化器模块11的收敛状态越好(和/或通道状态较好),但本发明不限于此。在另一范例实施例中,亦可以是以收敛值VC1~VC3中的至少一者越小代表图1的等化器模块11的收敛状态越好(和/或通道状态较好),视实务需求而定。

此外,在图2的另一范例实施例,若所述比较结果反映收敛值VC1~VC3中的至少一者与相应的临界值VTH1~VTH3之间的数值关系发生变化,则图1的信号样式过滤器101中的一或多个信号样式过滤器可被对应地开启或关闭,和/或不同的设定参数可以被套用至图1的等化器模块11。

图3是根据本发明的一范例实施例所示出的信号接收电路的示意图。请参照图3,在本范例实施例中,信号接收电路30包括等化器模块31、时脉数据回复电路32及控制器33。

等化器模块31包括线性等化器311与决策反馈等化器(DFE)312。在信号S1可依序经过线性等化器311与决策反馈等化器312的处理(例如补偿)以产生信号S2。须注意的是,在另一范例实施例中,决策反馈等化器312亦可替换为连续时间线性等化器(CTLE)或其他类型的等化器。

时脉数据回复电路32可对信号S2执行相位锁定以产生信号S3。此外,时脉数据回复电路32包括信号样式过滤器301。信号样式过滤器301可被动态地开启或关闭以决定是否过滤信号S2中具有特定样式的信号。在信号样式过滤器301开启后,时脉数据回复电路32可对通过信号样式过滤器301的信号进行处理(例如执行相位锁定)。

控制器33包括等化器控制器331与信号样式过滤器控制器332。等化器控制器331用以接收并分析信号S2与S3。等化器控制器331可根据分析结果产生信号P1,以通过信号P1控制或调整等化器控制器331和/或信号样式过滤器控制器332的设定参数。信号样式过滤器控制器332可根据等化器控制器331的分析结果产生信号P2,以通过信号P2控制信号样式过滤器301的开启或关闭。此外,信号样式过滤器控制器332也可根据信号样式过滤器301的开启或关闭指示等化器控制器331同步调整等化器控制器331和/或信号样式过滤器控制器332的设定参数。

在一范例实施例中,等化器控制器331可分析信号S2以获得所述评估参数。信号样式过滤器控制器332可根据此评估参数来控制信号样式过滤器301的开启或关闭。此外,信号样式过滤器控制器332也可根据此评估参数来指示等化器控制器331同步调整等化器控制器331和/或信号样式过滤器控制器332的设定参数。例如,可将与信号样式过滤器301相匹配的特定设定参数套用至等化器控制器331和/或信号样式过滤器控制器332。

须注意的是,关于根据此评估参数来控制信号样式过滤器301的开启或关闭以及根据评估参数来同步调整等化器控制器331和/或信号样式过滤器控制器332的设定参数的操作细节皆已详述于上,在此便不赘述。

须注意的是,在前述范例实施例中,是假设被信号样式过滤器过滤的信号会被输入至时脉信息回复电路(即被信号样式过滤器过滤的信号会通道信号样式过滤器)进行处理。然而,在另一范例实施例中,亦可以是假设被信号样式过滤器过滤的信号不会被输入至时脉信息回复电路(即被信号样式过滤器过滤的信号无法通道信号样式过滤器),只要可以达到优化等化器模块和/或时脉信息回复电路的运作效能即可。

在一范例实施例中,图1的信号接收电路10和/或图3的信号接收电路30可设置于存储器存储装置中。在另一范例实施例中,图1的信号接收电路10和/或图3的信号接收电路30亦可设置于其他类型的电子装置中,而不限于存储器存储装置。

一般而言,存储器存储装置(亦称,存储器存储系统)包括可复写式非易失性存储器模块(rewritable non-volatile memory module)与控制器(亦称,控制电路)。通常存储器存储装置是与主机系统一起使用,以使主机系统可将数据写入至存储器存储装置或从存储器存储装置中读取数据。

图4是根据本发明的一范例实施例所示出的主机系统、存储器存储装置及输入/输出(I/O)装置的示意图。图5是根据本发明的另一范例实施例所示出的主机系统、存储器存储装置及I/O装置的示意图。

请参照图4与图5,主机系统41一般包括处理器411、随机存取存储器(randomaccess memory,RAM)412、只读存储器(read only memory,ROM)413及数据传输接口414。处理器411、随机存取存储器412、只读存储器413及数据传输接口414皆连接至系统总线(system bus)410。

在本范例实施例中,主机系统41是通过数据传输接口414与存储器存储装置40连接。例如,主机系统41可经由数据传输接口414将数据存储至存储器存储装置40或从存储器存储装置40中读取数据。此外,主机系统41是通过系统总线410与I/O装置42连接。例如,主机系统41可经由系统总线410将输出信号传送至I/O装置42或从I/O装置42接收输入信号。

在本范例实施例中,处理器411、随机存取存储器412、只读存储器413及数据传输接口414可设置在主机系统41的主机板520上。数据传输接口414的数目可以是一或多个。通过数据传输接口414,主机板520可以经由有线或无线方式连接至存储器存储装置40。存储器存储装置40可例如是U盘501、存储卡502、固态硬盘(Solid State Drive,SSD)503或无线存储器存储装置504。无线存储器存储装置504可例如是近距离无线通讯(Near FieldCommunication,NFC)存储器存储装置、无线传真(WiFi)存储器存储装置、蓝牙(Bluetooth)存储器存储装置或低功耗蓝牙存储器存储装置(例如,iBeacon)等以各式无线通讯技术为基础的存储器存储装置。此外,主机板520也可以通过系统总线410连接至全球定位系统(Global Positioning System,GPS)模块505、网络接口卡506、无线传输装置507、键盘508、屏幕509、喇叭510等各式I/O装置。例如,在一范例实施例中,主机板520可通过无线传输装置507存取无线存储器存储装置504。

在一范例实施例中,所提及的主机系统为可实质地与存储器存储装置配合以存储数据的任意系统。虽然在上述范例实施例中,主机系统是以电脑系统来作说明,然而,图6是根据本发明的另一范例实施例所示出的主机系统与存储器存储装置的示意图。请参照图6,在另一范例实施例中,主机系统61也可以是数字相机、摄影机、通讯装置、音频播放器、视频播放器或平板电脑等系统,而存储器存储装置60可为其所使用的安全数字(SecureDigital,SD)卡62、小型快闪(Compact Flash,CF)卡63或嵌入式存储装置64等各式非易失性存储器存储装置。嵌入式存储装置64包括嵌入式多媒体卡(embedded Multi MediaCard,eMMC)641和/或嵌入式多芯片封装(embedded Multi Chip Package,eMCP)存储装置642等各类型将存储器模块直接连接于主机系统的基板上的嵌入式存储装置。

图7是根据本发明的一范例实施例所示出的存储器存储装置的概要方块图。请参照图7,存储器存储装置40包括连接接口单元702、存储器控制电路单元704与可复写式非易失性存储器模块706。

连接接口单元702用以将存储器存储装置40连接至主机系统41。存储器存储装置40可通过连接接口单元702与主机系统41通讯。在本范例实施例中,连接接口单元702是相容于串行高级技术附件(Serial Advanced Technology Attachment,SATA)标准。然而,必须了解的是,本发明不限于此,连接接口单元702亦可以是符合并行高级技术附件(Parallel Advanced Technology Attachment,PATA)标准、电气和电子工程师协会(Institute of Electrical and Electronic Engineers,IEEE)1394标准、高速周边零件连接接口(Peripheral Component Interconnect Express,PCI Express)标准、通用串行总线(Universal Serial Bus,USB)标准、SD接口标准、超高速一代(Ultra High Speed-I,UHS-I)接口标准、超高速二代(Ultra High Speed-II,UHS-II)接口标准、存储棒(MemoryStick,MS)接口标准、MCP接口标准、MMC接口标准、eMMC接口标准、通用快闪存储器(Universal Flash Storage,UFS)接口标准、eMCP接口标准、CF接口标准、整合式驱动电子接口(Integrated Device Electronics,IDE)标准或其他适合的标准。连接接口单元702可与存储器控制电路单元704封装在一个芯片中,或者连接接口单元702是布设于一包含存储器控制电路单元704的芯片外。

存储器控制电路单元704用以执行以硬件型式或固件型式实作的多个逻辑门或控制指令并且根据主机系统41的指令在可复写式非易失性存储器模块706中进行数据的写入、读取与抹除等运作。

可复写式非易失性存储器模块706是连接至存储器控制电路单元704并且用以存储主机系统41所写入的数据。可复写式非易失性存储器模块706可以是单阶存储单元(Single Level Cell,SLC)NAND型快闪存储器模块(即,一个存储单元中可存储1个比特的快闪存储器模块)、多阶存储单元(Multi Level Cell,MLC)NAND型快闪存储器模块(即,一个存储单元中可存储2个比特的快闪存储器模块)、三阶存储单元(Triple Level Cell,TLC)NAND型快闪存储器模块(即,一个存储单元中可存储3个比特的快闪存储器模块)、四阶存储单元(Quad Level Cell,TLC)NAND型快闪存储器模块(即,一个存储单元中可存储4个比特的快闪存储器模块)、其他快闪存储器模块或其他具有相同特性的存储器模块。

可复写式非易失性存储器模块706中的每一个存储单元是以电压(以下亦称为临界电压)的改变来存储一或多个比特。具体来说,每一个存储单元的控制栅极(controlgate)与通道之间有一个电荷捕捉层。通过施予一写入电压至控制栅极,可以改变电荷补捉层的电子量,进而改变存储单元的临界电压。此改变存储单元的临界电压的操作亦称为“把数据写入至存储单元”或“程序化(programming)存储单元”。随着临界电压的改变,可复写式非易失性存储器模块1006中的每一个存储单元具有多个存储状态。通过施予读取电压可以判断一个存储单元是属于哪一个存储状态,藉此取得此存储单元所存储的一或多个比特。

在本范例实施例中,可复写式非易失性存储器模块706的存储单元可构成多个实体程序化单元,并且此些实体程序化单元可构成多个实体抹除单元。具体来说,同一条字线上的存储单元可组成一或多个实体程序化单元。若每一个存储单元可存储2个以上的比特,则同一条字线上的实体程序化单元可至少可被分类为下实体程序化单元与上实体程序化单元。例如,一存储单元的最低有效位(Least Significant Bit,LSB)是属于下实体程序化单元,并且一存储单元的最高有效位(Most Significant Bit,MSB)是属于上实体程序化单元。一般来说,在MLC NAND型快闪存储器中,下实体程序化单元的写入速度会大于上实体程序化单元的写入速度,和/或下实体程序化单元的可靠度是高于上实体程序化单元的可靠度。

在本范例实施例中,实体程序化单元为程序化的最小单元。即,实体程序化单元为写入数据的最小单元。例如,实体程序化单元可为实体页面(page)或是实体扇(sector)。若实体程序化单元为实体页面,则此些实体程序化单元可包括数据比特区与冗余(redundancy)比特区。数据比特区包含多个实体扇,用以存储使用者数据,而冗余比特区用以存储系统数据(例如,错误更正码等管理数据)。在本范例实施例中,数据比特区包含32个实体扇,且一个实体扇的大小为512字节(byte,B)。然而,在其他范例实施例中,数据比特区中也可包含8个、16个或数目更多或更少的实体扇,并且每一个实体扇的大小也可以是更大或更小。另一方面,实体抹除单元为抹除的最小单位。亦即,每一实体抹除单元含有最小数目的一并被抹除的存储单元。例如,实体抹除单元为实体区块(block)。

在一范例实施例中,图7的可复写式非易失性存储器模块706亦称为快闪存储器模块。在一范例实施例中,图7的存储器控制电路单元704亦称为用于控制快闪存储器模块的快闪存储器控制器。

在一范例实施例中,图1的信号接收电路10和/或图3的信号接收电路30可设置于图7的连接接口单元702,以接收并处理来自主机系统41的信号S1。例如,信号S1可包括来自主机系统41的数据信号。在另一范例实施例中,图1的信号接收电路10和/或图3的信号接收电路30可设置于图7的存储器控制电路单元704和/或可复写式非易失性存储器模块706。

图8是根据本发明的一范例实施例所示出的信号接收方法的流程图。请参照图8,在步骤S801中,接收第一信号并对所述第一信号进行补偿以产生第二信号。在步骤S802中,对所述第二信号执行相位锁定。在步骤S803中,根据所述第二信号开启或关闭信号样式过滤器,其中所述信号样式过滤器用以过滤所述第二信号中具有特定样式的信号。

然而,图8中各步骤已详细说明如上,在此便不再赘述。值得注意的是,图8中各步骤可以实作为多个程序码或是电路,本发明不加以限制。此外,图8的方法可以搭配以上范例实施例使用,也可以单独使用,本发明不加以限制。

综上所述,在对第一信号进行补偿以产生第二信号后,根据所述第二信号,时脉数据回复电路中用于过滤具有特定样式的信号的信号样式过滤器可被动态地开启或关闭。例如,当通道状态较差时,一或多个信号样式过滤器可被开启,以使时脉数据回复电路仅针对特定样式的信号进行处理,以尝试提高等化器模块和/或时脉信息回复电路的运作效能。待通道状态变好后,先前开启的信号样式过滤器可被关闭。藉此,可有效针对不同通道状态提高或维持信号接收端对于信号的接收能力。

虽然本发明已以实施例揭示如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作些许的更改与润饰,故本发明的保护范围当视权利要求所界定的为准。

- 信号接收电路、存储器存储装置及信号接收方法

- 等化器调校方法、信号接收电路及存储器存储装置