记忆体元件及其制造方法

文献发布时间:2023-06-19 11:54:11

技术领域

本领域是关于一种记忆体元件及其制造方法。

背景技术

快闪记忆体(Flash memories)相较于其他形式的固态非挥发记忆体结构具有特定的优点及功效。这些优点及功效大多与下列相关,例如,促进读、写及/或擦除的速度、功率消耗、紧凑度、成本,等等。快闪记忆体经常使用于高密度数据储存装置,配置于相机、移动电话、录音机、外接式USB数据储存元件(亦可称作thumb drive或flash drive),等等。一般而言,在应用上,快闪记忆体制造于精密的微晶片上,接着被耦接至具有适合的处理电路的另一个晶片或多个晶片上,且可配置于同一套件中,或是配置于不同的套件中并电性耦接。

处理器与内嵌式快闪记忆体为更近代的发展。在这些元件中,快闪记忆体阵列与逻辑电路或是控制电路一起制造在单一晶片上。这些配置大多用于微处理器单元(microcontroller units;MCU)中,例如安装在单一晶片上的小型计算机元件,其设计于重复执行具有特定数量的特殊工作。微处理器单元经常用于智能卡、无线通讯元件、汽车的控制单元,等等。记忆体与相关处理电路的组合可促进处理速度且同时降低尺寸、功率消耗,以及成本。

发明内容

本揭露的部分实施例为一种记忆体元件,包含擦除栅极、擦除栅极介电质、第一和第二浮栅极、第一和第二控制栅极、第一选择栅极、第二选择栅极、共用源极条,以及硅化物垫。擦除栅极位于基板的第一部分上方。擦除栅极介电质位于擦除栅极和基板的第一部分之间。第一和第二浮栅极位于擦除栅极的相对两侧。第一和第二控制栅极分别位于第一和第二浮栅极上方。第一选择栅极沿着第一方向至少部分通过第一控制栅极与擦除栅极隔开。第二选择栅极沿着第一方向至少部分通过第二控制栅极与擦除栅极隔开。共用源极条位于基板的第二部分上,其中共用源极条与擦除栅极沿着垂直第一方向的第二方向上排列。硅化物垫位于共用源极条下方且位于基板的第二部分内,其中硅化物垫的上表面平坦于擦除栅极介电质的下表面。

本揭露的部分实施例为一种记忆体元件,包含擦除栅极、擦除栅极介电质、第一和第二浮栅极、第一和第二控制栅极、第一选择栅极、第二选择栅极、第一硅化物垫、第一浮栅极间隔物,以及第二浮栅极间隔物。擦除栅极位于基板的第一部分上方。擦除栅极介电质位于擦除栅极和基板的第一部分之间。第一和第二浮栅极位于擦除栅极的相对两侧。第一和第二控制栅极分别位于第一和第二浮栅极上方。第一选择栅极沿着第一方向至少部分通过第一控制栅极与擦除栅极隔开。第二选择栅极沿着第一方向至少部分通过第二控制栅极与擦除栅极隔开。第一硅化物垫位于基板的第二部分中,其中第一硅化物垫和擦除栅极沿着垂直第一方向的第二方向排列。第一浮栅极间隔物位于第一浮栅极的侧壁上,其中第一硅化物垫通过第一浮栅极间隔物与第一浮栅极隔开。第二浮栅极间隔物位于第二浮栅极的侧壁上,其中第一硅化物垫通过第二浮栅极间隔物与第二浮栅极隔开。

本揭露的部分实施例为一种制造记忆体元件的方法,包含在基板上形成第一浮栅极和第二浮栅极;分别在第一浮栅极和第二浮栅极上方形成第一控制栅极和第二控制栅极;形成图案化遮罩以覆盖第一控制栅极和第二控制栅极,其中图案化遮罩曝露位于第一控制栅极和第二控制栅极之间的基板的第一部分,且图案化遮罩曝露第一控制栅极和第二控制栅极之间的基板的第二部分;在基板的第一部分中形成共用源极区,其中在形成共用源极区期间,图案化遮罩保护基板的第二部分;移除图案化遮罩;在基板的第一部分上方形成擦除栅极;以及在基板的第二部分上方形成共用源极条。

附图说明

阅读以下详细叙述并搭配对应的附图,可了解本揭露的多个态样。应注意,根据业界中的标准做法,多个特征并非按比例绘制。事实上,多个特征的尺寸可任意增加或减少以利于讨论的清晰性。

图1A为本揭露的部分实施例的记忆体元件的上视图;

图1B为本揭露的部分实施例的沿着图1A的线B-B的剖面图;

图1C为本揭露的部分实施例的沿着图1A的线C-C的剖面图;

图1D为本揭露的部分实施例的沿着图1A的线D-D的剖面图;

图2A至图33D为本揭露的部分实施例的制造记忆体元件的方法在不同阶段的示意图;

图34A至图34C为本揭露的部分实施例的制造记忆体元件的方法。

【符号说明】

100:记忆体元件

104:基板

104A:部分

104B:部分

104P:主动区

106:隔离结构

108:分离栅极快闪记忆体单元

108a、108b:记忆体单元

126、126a、126b:漏极区

128:共用源极区

130a、130b:通道区

134、134a、134b:浮栅极

138、138a、138b:控制栅极

140:栅极间隔物

142:浮栅极间隔物

144:擦除栅极

146:擦除栅极介电质

148:选择栅极间隔物

149:浮栅极间隔物

150、150a、150b:选择栅极

156:选择栅极介电质

158:浮栅极介电质

160:控制栅极介电质

160CS:共用源极条

160D:漏极条

160EG:擦除栅极条

170、172:硅化物垫

200、202:层间介电层

210:控制栅极硬遮罩

300:硬遮罩

302、304:图案化遮罩

403:栅极氧化物

602:浮栅极层

702:控制栅极堆叠

704:控制栅极介电层

706:控制栅极层

708:控制栅极硬遮罩

902:控制栅极间隔物层

1502:介电层

1504:栅极层

1702:硬遮罩层

M1、M2、M3、M4:图案化遮罩

O1、O2、O3、O4、O5:开口

W1、W2、W3、W4、W5:宽度

A-A、B-B、C-C:线

具体实施方式

以下揭露提供众多不同的实施例或范例,用于实施本案提供的主要内容的不同特征。下文描述一特定范例的组件及配置以简化本揭露。当然,此范例仅为示意性,且并不拟定限制。举例而言,以下描述“第一特征形成在第二特征的上方或之上”,于实施例中可包括第一特征与第二特征直接接触,且亦可包括在第一特征与第二特征之间形成额外特征使得第一特征及第二特征无直接接触。此外,本揭露可在各范例中重复使用元件符号及/或字母。此重复的目的在于简化及厘清,且其自身并不规定所讨论的各实施例及/或配置之间的关系。

此外,空间相对术语,诸如“下方(beneath)”、“以下(below)”、“下部(lower)”、“上方(above)”、“上部(upper)”等等在本文中用于简化描述,以描述如附图中所图示的一个元件或特征结构与另一元件或特征结构的关系。除了描绘图示的方位外,空间相对术语也包含元件在使用中或操作下的不同方位。此设备可以其他方式定向(旋转90度或处于其他方位上),而本案中使用的空间相对描述词可相应地进行解释。

快闪记忆体可形成在块状硅基板中,且运用不同篇压情况以进行读写数据数值。例如,第三世代超级快闪单元(third generation SUPERFLASH;ESF3)包括一组对称的分离栅极(split gate)记忆体单元,每一个单元包括一组源/漏极区域及位于其间的通道区域。在ESF3结构中,用于每一个分离栅极记忆体单元的其中一个源/漏极区域作为共用源/漏极区域(common source/drain region),且与邻近的分离栅极记忆体单元共同使用此源/漏极区域,而另一个源/漏极区域则为此单元内的独立源/漏极区域。在每一个分离栅极记忆体单元中,浮栅极(floating gate)配置于单元的通道区域上,而控制栅极(control gate)配置于浮栅极上。选择栅极(select gate)配置在浮栅极和控制栅极的一侧(例如位在ESF3单元的独立源/漏极区域和浮栅极及/或控制栅极的侧壁之间)。至少一单元配置于储存一可变的电荷值于浮栅极中,其中此电荷值对应于储存在此单元的数据态(data state),且是以非挥发的形式储存,因此在没有电源的时候此储存的电荷/数据可维持。

通过改变储存在浮栅极中的电荷量,记忆体单元元件的阈值电压V

本揭露的部分实施例是关于形成在基板的凹陷区域上的快闪记忆体元件。虽然下方绘制的部分实施例是关于分离栅极快闪记忆体,但应了解此概念并不限制于分离栅极快闪记忆体单元,且可应用于其他型态的快闪记忆体单元以及其他型态的半导体元件,例如金属氧化物场效晶体管(MOSFETs)、鳍式场效晶体管(FinFETs),或类似者。

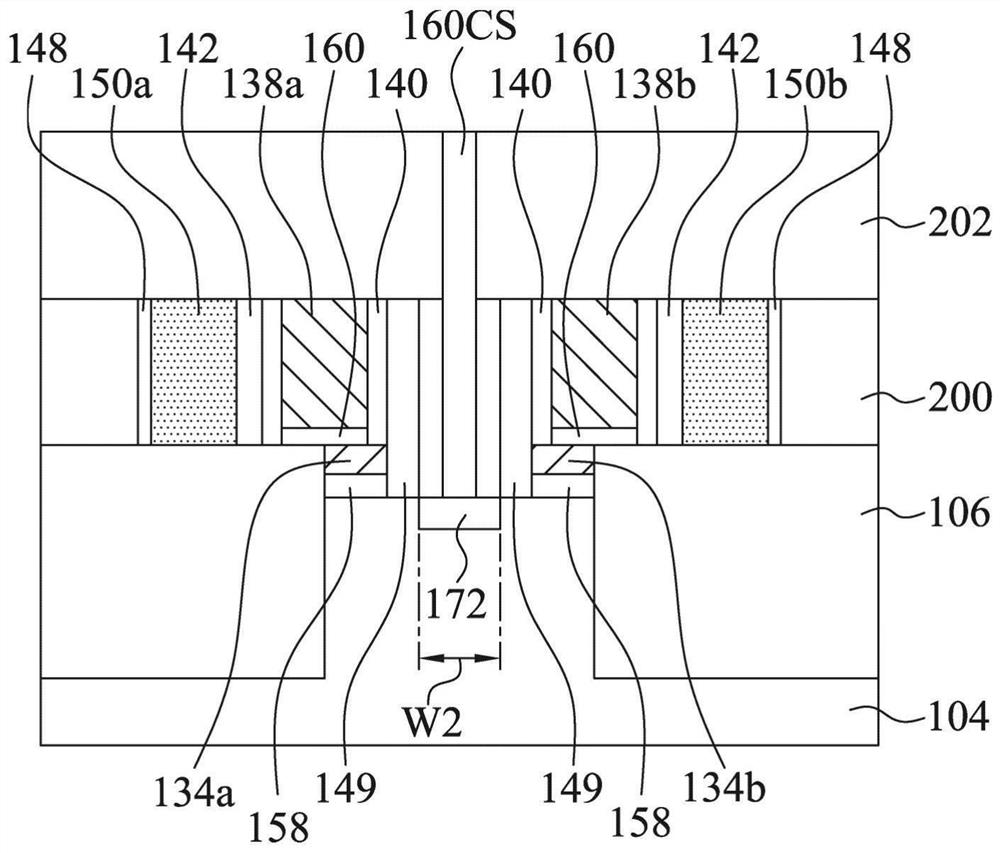

图1A为本揭露的部分实施例的记忆体元件100的上视图。图1B为本揭露的部分实施例的沿着图1A的线B-B的剖面图。图1C为本揭露的部分实施例的沿着图1A的线C-C的剖面图。图1D为本揭露的部分实施例的沿着图1A的线D-D的剖面图。

记忆体元件100包括基板104。在部分实施例中,基板104包括主动区104P,且在水平方向上被由介电材料组成的隔离结构106包围。半导体基板104可为或者包括,例如,块状硅基板、III-V族基板、绝缘体上硅(SOI)基板、其他适合的半导体基板,或相似者。隔离结构106可为浅沟槽隔离(STI)结构,深沟槽隔离(DTI)结构、其他适合的隔离结构、上述的组合,或相似者。在部分实施例中若隔离结构106是由氧化物(例如氧化硅)组成,则主动区104P亦可称为氧化物定义(oxide defined;OD)区域。

在图1A中,记忆体元件100包括记忆体单元阵列。在图示的范例中,记忆体单元阵列包括数个分离栅极快闪记忆体单元108,其中每一对分离栅极快闪记忆体单元108包括第一记忆体单元108a和第二记忆体单元108b。

如图1A和图1B所示,图1B为沿着垂直擦除栅极144的长度方向且通过擦除栅极144的剖面图。第一和第二漏极区126a、126b(分别对应至第一和第二记忆体单元108a、108b)配置于基板104中,而共用源极区128(共用于第一和第二记忆体单元108a、108b之间)配置于基板104中且在水平方向上和第一和第二漏极区126a、126b分离。第一漏极区126a和共用源极区128通过第一通道区130a分离,而共用源极区128和第二漏极区126b通过第二通道区130b分离。

擦除栅极144配置于共用源极区128上方,且通过擦除栅极介电质146和共用源极区128分离。第一和第二浮栅极134a、134b分别位于基板104的第一和第二通道区130a、130b上方。第一和第二控制栅极138a、138b分别覆盖第一和第二浮栅极134a、134b。第一和第二选择栅极150a、150b分别覆盖第一和第二通道区130a、130b,且在水平方向上通过第一和第二浮栅极134a、134b和擦除栅极144分离。

在部分实施例中,擦除栅极介电质146包住擦除栅极144的底部,且垂直地将擦除栅极144的底部和共用源极区128分离,且水平地将擦除栅极144和第一和第二浮栅极134a、134b分离。擦除栅极介电质146可具有凸出的上表面以及凸出的下表面,且可为掺杂多晶硅、金属、其他适合的导电材料、上述的组合,或相似者。在部分实施例中,擦除栅极介电质146和共用源极区128具有弯曲交界面,且擦除栅极介电质146和擦除栅极144具有弯曲交界面。

擦除栅极144、第一和第二控制栅极138a、138b、第一和第二浮栅极134a、134b,以及第一和第二选择栅极150a、150b可为掺杂多晶硅、金属、其他适合的导电材料、上述的组合,或相似者。擦除栅极介电质146可为或包括,例如,氧化物、氮化物、其他适合的介电质、上述的组合,或相似者。

一对栅极间隔物140位于第一和第二浮栅极134a、134b上方,且位于第一和第二控制栅极138a、138b的相对侧壁上。选择栅极介电质156将第一和第二选择栅极150a、150b和基板104分离,浮栅极介电质158将第一和第二浮栅极134a、134b和基板104分离。控制栅极介电质160将第一和第二浮栅极134a、134b分别和第一和第二控制栅极138a、138b分离。在部分实施例中,选择栅极介电质156、浮栅极介电质158及/或控制栅极介电质160至少两者具有相同成分且具有相同厚度。然而在其他实施例中,选择栅极介电质156、浮栅极介电质158及/或控制栅极介电质160各者具有不同成分及/或不同的厚度。

控制栅极间隔物140可具有适合的成分。在部分实施例中,控制栅极间隔物140可为或包括,例如,氮化物、氧化物、其他适合的介电质、上述的组合,或相似者。在部分实施例中,控制栅极间隔物140为同质材料。在其他实施例中,控制栅极间隔物140各者为ONO结构。例如,控制栅极间隔物140可包括氧化物-氮化物-氧化物(Oxide-Nitride-Oxide)结构,并具有外氧化物层、中间氮化物层,以及内氧化物层。

选择栅极介电质156可为或包括,例如,氧化物、氮化物、其他适合的介电质、上述的组合,或相似者。控制栅极介电质160可为或包括,例如,氧化物、氮化物、其他适合的介电质、上述的组合,或相似者。

浮栅极间隔物142将第一和第二选择栅极150a、150b分别和第一和第二浮栅极134a、134b分离,且分别和第一和第二控制栅极138a、138b分离。浮栅极间隔物142位于第一和第二通道区130a、130b上方。在图1B中,每一个浮栅极间隔物142分别位于第一和第二浮栅极134a、134b的侧壁上。选择栅极间隔物148分别位于第一和第二选择栅极150a、150b的侧壁上。

浮栅极间隔物142可具有适合的成分。在部分实施例中,浮栅极间隔物142可为或包括,例如,氮化物、氧化物、其他适合的介电质、上述的组合,或相似者。在部分实施例中,浮栅极间隔物142为同质材料。在其他实施例中,浮栅极间隔物142各者为ONO结构。例如,浮栅极间隔物142可包括氧化物-氮化物-氧化物(Oxide-Nitride-Oxide)结构,并具有外氧化物层、中间氮化物层,以及内氧化物层。在部分实施例中,浮栅极间隔物142可具有和控制栅极间隔物140具有相同成分。选择栅极间隔物148可为或包括,例如,氮化物、氧化物、其他适合的介电质、上述的组合,或相似者。

硅化物垫170分别位于第一和第二漏极区126a、126b上方。在部分实施例中,硅化物垫170包括和第一和第二漏极区126a、126b相同的掺杂。在部分实施例中,硅化物垫170可为硅化镍(nickel silicide;NiSi)或其他适合的硅化物,且可透过适合的硅化制程形成。

第一层间介电层200位于第一和第二漏极区126a、126b和硅化物垫170上方。在部分实施例中,硅化物垫170将第一层间介电层200和第一和第二漏极区126a、126b分离。第二层间介电层202位于擦除栅极144、第一和第二控制栅极138a、138b,以及第一和第二选择栅极150a、150b上方。漏极条160D延伸穿越第一和第二层间介电层200、202至硅化物垫170。在部分实施例中,漏极条160D亦可称为漏极接触160D。

在部分实施例中,第一和第二层间介电层200、202可为氧化物、低介电常数(low-k)介电质、其他适合的介电质、上述的组合,或相似者。此处所提及的低介电常数(low-k)介电质为介电质具有低于约3.9的介电常数(k)。在部分实施例中,若第一和第二层间介电层200、202由相同材料组成,则第一和第二层间介电层200、202可能融合在一起且其间可能不具有可辨识的交界面。漏极条160D为导电材料,且可为钨、铜、铝、铜铝、其他适合金属或导电材料、上述的组合,或相似者。

如图1A和图1C所示,图1C为沿着垂直擦除栅极144的长度方向且通过共用源极条160CS的剖面图。图1C中的部分元件已经于图1B中讨论,因此这些元件使用相同的编号且相关结构细节将不再赘述。应了解图1B和图1C具有相同尺寸,因此图1B和图1C中的元件比例是相同的。

图1C中,第一和第二浮栅极134a、134b的上表面与隔离结构106的上表面共线。在部分实施例中,位于第一控制栅极138a下方的控制栅极介电质160自第一浮栅极134a的上表面延伸至隔离结构106的上表面。而位于第二控制栅极138b下方的控制栅极介电质160自第二浮栅极134b的上表面延伸至隔离结构106的上表面。在图1C的剖面图中,第一和第二浮栅极134a、134b和浮栅极介电质窄于第一和第二控制栅极138a、138b和控制栅极介电质160。然而,在图1B的剖面图中,第一和第二浮栅极134a、134b和浮栅极介电质宽于第一和第二控制栅极138a、138b和控制栅极介电质160。

硅化物垫172配置于基板104上。第一层间介电层200位于硅化物垫172上方且与其接触。共用源极条160CS延伸穿越第一和第二层间介电层200、202至硅化物垫172。在部分实施例中,共用源极条160CS亦可称为共用源极接触160CS。在部分实施例中,硅化物垫172可为硅化镍(nickel silicide;NiSi)或其他适合的硅化物,且可透过适合的硅化制程形成。在部分实施例中,硅化物垫172的掺杂浓度(例如,植入杂质浓度)可低于图1B中的硅化物垫170的掺杂浓度。在部分实施例中,硅化物垫172不具有硅化物垫170的掺杂。

在沿着垂直擦除栅极144的长度方向上,硅化物垫172的上表面(图1C)相较于擦除栅极介电质146的下表面(图1B)较为平坦。例如,擦除栅极介电质146的下表面为弯曲的,而硅化物垫172的上表面为实质上平坦。

在图1C的部分实施例中,浮栅极间隔物149位于第一和第二浮栅极134a、134b的侧壁、浮栅极介电质158的侧壁、控制栅极间隔物140的侧壁上,以将第一和第二浮栅极134a、134b、浮栅极介电质158、控制栅极间隔物140和第一层间介电层200分离。在部分实施例中,基板104位于浮栅极间隔物149正下方的部分至少一部分不具有硅化物垫172。在部分实施例中,硅化物垫172在水平方向上通过浮栅极间隔物149和第一和第二浮栅极134a、134b和浮栅极介电质158分离。意即,硅化物垫172分别和第一和第二浮栅极134a、134b通过一非0的距离隔开。在部分实施例中,浮栅极间隔物149由氮化物组成,而第一层间介电层200由氧化物组成。在部分实施例中,浮栅极间隔物149的厚度小于约10nm且大于约5nm。

应了解到浮栅极间隔物149在图1B的剖面图中不存在,因此图1B的擦除栅极介电质146沿着并接触第一和第二浮栅极134a、134b的侧壁、浮栅极介电质158的侧壁、控制栅极间隔物140的侧壁。在部分实施例中,硅化物垫172的宽度小于擦除栅极介电质146的宽度,以及共用源极区128的宽度。例如,擦除栅极介电质146具有最大宽度W1(图1B),而硅化物垫172具有宽度W2(图1C),其中宽度W1大于宽度W2。另一方面,硅化物垫172的宽度W2小于第一和第二浮栅极134a、134b之间的距离。

如图1A和图1D所示,图1D为沿着擦除栅极144的长度方向且通过擦除栅极144和共用源极条160CS的剖面图。图1D中的部分元件已经于图1B和图1C中讨论,因此这些元件使用相同的编号且相关结构细节将不再赘述。应了解图1B、图1C和图1D具有相同尺寸,因此图1B、图1C和图1D中的元件比例是相同的。

在图1D的剖面图中,擦除栅极144通过共用栅极条160CS和第一层间介电层200被分割为第一部分144A和第二部分144B。多个擦除栅极条160EG延伸穿越第二层间介电层202并分别接触擦除栅极144的第一部分144A和第二部分144B。在部分实施例中,硅化物垫172的上表面低于擦除栅极介电质146的上表面,且高于擦除栅极介电质146的下表面。在部分实施例中,在图1D的剖面图中,硅化物垫172具有宽度W3,其中宽度W3的范围约自80nm至约120nm。硅化物垫172与共用源极区128和共用源极条160CS接触,借此将共用源极条160CS电性连接至共用源极区128。在部分实施例中,硅化物垫172中(或者硅化物垫172下方的区域)的掺杂浓度(例如:植入杂质)低于共用源极区128的掺杂浓度。在部分实施例中,硅化物垫172实质上不具有共用源极区128的掺杂物。

图2A至图33D为本揭露的部分实施例的制造记忆体元件的方法在不同阶段的示意图。详细而言,图2A至图33D为制造图1A至图1D的记忆体元件100的方法。

参照图2A至图2C,其中图2A为图1A的记忆体元件100的初始结构,且和图1A具有相同的上视图,图2B为沿着图2A的线B-B的剖面图,图2C为沿着图2A的线C-C的剖面图。图示为半导体基板104。在部分实施例中,半导体基板104可为或者包括,例如,块状硅基板、III-V族基板、绝缘体上硅(SOI)基板、其他适合的半导体基板,或相似者。半导体基板104可为二元半导体基板(例如,GaAs),三元半导体基板(例如,AlGaAs),或更多元半导体基板。在部分实施例中,半导体基板104包括主动区104P,其中主动区104P可通过根据预定的图案凹陷基板104而形成。

隔离结构106接着形成在基板104内且围绕主动区104P,借此在主动区104P之间提供电性隔离。结果图图示于图2A至图2C。在部分实施例中,隔离结构106可为浅沟槽隔离(STI)结构,深沟槽隔离(DTI)结构、其他适合的隔离结构、上述的组合,或相似者。在部分实施例中,形成隔离结构106包括,例如,形成氧化物层于基板上方及氮化物层于氧化物层上方。形成图案化遮罩于氮化物层上方。将图案化遮罩作为蚀刻遮罩,蚀刻氮化物层和氧化物层直到基板104内。通过沉积氧化物或是氧化物前驱物,形成由氧化物组成的隔离结构106。执行化学机械研磨制程(CMP)以平坦化隔离结构106与氮化物。接着自基板104上方移除氮化物层和氧化物层。因此,隔离结构106的上表面将会高于基板104的主动区104P的上表面,如图2C所示。举例来说,隔离结构106的上表面和基板104的主动区104P的上表面的断差相当于移除的氮化物层和氧化物层的总厚度,但本揭露并不限定于此。

参照图3A至图3C,其中图3A为在图1A至图1C的操作后的记忆体元件100的上视图,且和图2A具有相同的上视图,图3B为沿着图3A的线B-B的剖面图,图3C为沿着图3A的线C-C的剖面图。为简洁起见,图3B和图3C的部分元件在图3A中省略。栅极氧化物403成长于半导体基板104的曝露部分。在部分实施例中,栅极氧化物403可通过选择性氧化制程(例如,湿氧化及/或热氧化),借此使栅极氧化物403选择性地成长在半导体基板104的曝露部分,而使得隔离结构106的上表面实质上未被栅极氧化物403覆盖。

浮栅极层602接着形成于半导体基板104上方。浮栅极层602可共形地形成,且可为掺杂的多晶硅或其他适合的导电材料。在部分实施例中,浮栅极层602可通过CVD、PVD、溅镀,或其他适合的沉积制程形成。接着,可执行平坦化制程以移除隔离结构106上方的浮栅极层602直到隔离结构106曝露时停止。平坦化制程凹陷浮栅极层602的顶表面使其和隔离结构106的顶表面实质上等高。在部分实施例中,平坦化制程可为CMP或其他适合的平坦化制程。

控制栅极堆叠702可接着形成在浮栅极层602和隔离结构106的平坦化表面上。在部分实施例中,控制栅极堆叠702包括控制栅极介电层704、控制栅极层706,以及控制栅极硬遮罩708。控制栅极介电层704可通过CVD、PVD、其他适合的沉积制程形成、上述的组合,或相似者。在部分实施例中,控制栅极介电层704的总厚度约为

控制栅极层706可共形地形成,且可为掺杂的多晶硅或其他适合的导电材料。在部分实施例中,形成控制栅极层706包括沉积一材料、植入掺杂物于材料中,并退火以活化掺杂物。控制栅极层706的材料可通过CVD、PVD,或其他适合的沉积制程形成。在部分实施例中,控制栅极层706的厚度约为

控制栅极硬遮罩708可包括多层不同的材料。控制栅极硬遮罩708可包括氧化物、氮化物,或适合的材料。在部分实施例中,控制栅极硬遮罩708包括位于一第一氮化物层上方的氧化物层。在部分实施例中,这些层的厚度约为

参照图4A至图4C,其中图4A为在图4A至图4C的操作后的记忆体元件100的上视图,且和图3A具有相同的上视图,图4B为沿着图4A的线B-B的剖面图,图4C为沿着图4A的线C-C的剖面图。为简洁起见,图4B和图4C的部分元件在图4A中省略。执行一选择性蚀刻以移除部分控制栅极堆叠702,借此在浮栅极层602上形成控制栅极硬遮罩210、控制栅极138,以及控制栅极介电质160。在部分实施例中,执行选择性蚀刻的制程包括形成光阻层。光阻层可经图案化以定义控制栅极138的图案。接着使用光阻层执行蚀刻制程直到浮栅极层602曝露。在部分实施例中,可接着移除光阻层。

参照图5A及图5B,其中图5A和图4B有相同剖面,而图5B和图4C有相同剖面。在浮栅极层602、控制栅极介电质160、控制栅极138,以及控制栅极硬遮罩210上共形地形成控制栅极间隔物层902。在部分实施例中,控制栅极间隔物层902可通过CVD、PVD,或其他适合的沉积制程形成。

参照图6A及图6B,其中图6A和图5A有相同剖面,而图6B和图5B有相同剖面。蚀刻控制栅极间隔物层902(参照图5A及图5B)以形成控制栅极间隔物140。蚀刻的后的结果,控制栅极间隔物140覆盖控制栅极138的相对侧壁。在部分实施例中,控制栅极间隔物140位于隔离结构106上,如图6B所示。蚀刻制程包括电浆蚀刻或其他蚀刻制程,其选择性地移除控制栅极间隔物层902的水平部分。更详细来说,这些间隔物可在上部具有圆角且平顺地倾斜的侧壁表面。另一方面,可对浮栅极层602和栅极氧化物403(参照图5A及图5B)执行另一蚀刻制程以形成浮栅极134和浮栅极介电质158。在部分实施例中,控制栅极间隔物140和控制栅极硬遮罩210可在此蚀刻步骤中作为蚀刻遮罩。

参照图7A及图7B,其中图7A和图6A有相同剖面,而图7B和图6B有相同剖面。形成多个浮栅极间隔物142在浮栅极134的相对侧壁上以及每一个控制栅极间隔物140的侧壁上。在部分实施例中,形成浮栅极间隔物142的制程包括沉积浮栅极间隔物层在图6A和图6B所示的结构上,接着进行电浆蚀刻或其他适合的蚀刻制程以移除浮栅极间隔物层的水平部分。浮栅极间隔物142可通过CVD、PVD,或其他适合的沉积制程形成。为方便描述,浮栅极间隔物142绘制为具有垂直侧壁。在其他实施例中,浮栅极间隔物142可在上部具有圆角且平顺地倾斜的侧壁表面。

参照图8A至图8D,其中图8A为在图7A和图7B的操作后的记忆体元件100的上视图,且和图4A具有相同的上视图,图8B为沿着图8A的线B-B的剖面图,图8C为沿着图8A的线C-C的剖面图,而图8D为沿着图8A的线D-D的剖面图。为简洁起见,图8B至图8D的部分元件在图8A中省略。形成图案化遮罩M1在基板104上方。在部分实施例中,图案化遮罩M1可为光阻层。图案化遮罩M1可通过光微影制程进行图案化。

在部分实施例中,图案化遮罩M1具有多个开口曝露基板104的部分104A。另一方面,沿着平行控制栅极138的长度方向的方向上,图案化遮罩M1覆盖基板104的部分104B(参照图8A)。详细来说,部分104B定义了后续形成的共用源极条的位置(例如,图32A至图32D的共用源极条160CS)。因此,部分104B亦可称为共用源极条形成区域。另一方面,图案化遮罩M1曝露基板104的部分104A,其中部分104A定义了后续形成的擦除栅极的位置(例如,图22A至图22C的擦除栅极144)。

图8D中,沿着平行控制栅极138的长度方向的方向上,基板104的被覆盖的部分104B位于基板104的曝露的部分104A之间。换言之,基板104的曝露的部分104A分别位于基板104的被覆盖的部分104B的两侧。

参照图9A至图9C,其中图9A至图9C分别和图8B至图8D具有相同的剖面。在基板104内且在浮栅极134之间形成多个共用源极区128。在部分实施例中,形成共用源极区128的制程包括离子植入或其他适合的掺杂制程。在部分实施例中,掺杂物经由图案化遮罩M1的开口O1被引入至基板104的曝露的部分104A以在基板104内形成共用源极区128。另一方面,基板104的被覆盖的部分104B在离子植入期间被图案化遮罩M1保护,使得基板104的被覆盖的部分104B不具有共用源极区128的掺杂物。意及,基板104的被覆盖的部分104B的掺杂物浓度会低于共用源极区128(基板104的曝露的部分104A)的掺杂物浓度。

参照图10A至图10C,其中图10A至图10C分别和图9A至图9C具有相同的剖面。移除经由图案化遮罩M1的开口O1曝露的浮栅极间隔物142。移除浮栅极间隔物142的制程可包括蚀刻制程,并以图案化遮罩M1作为蚀刻遮罩。

参照图11A至图11C,其中图11A至图11C分别和图10A至图10C具有相同的剖面。通过适当制程移除图案化遮罩M1,例如剥离。形成擦除栅极介电质146以覆盖共用源极区128并附着于浮栅极134的侧壁和控制栅极间隔物140的侧壁。形成擦除栅极介电质146的制程可包括高温氧化(high temperature oxidation;HTO)、原位蒸气产生(in-situ steamgeneration;ISSG)氧化、其他适合的沉积或成长制程、上述的组合,或相似者。在部分实施例中。擦除栅极介电质146的形成可通过氧化物沉积制程并接着执行氧化物成长制程。在部分实施例中,如图11A的剖面图所示,由于共用源极区128的离子植入,使得擦除栅极介电质146产生弯曲或球根状的表面轮廓。共用源极区128的中心区域接收了较高剂量的掺杂物,因此共用源极区128的中心区域相较于周边区域会受到比较多的损坏。因此,氧化物将在中心区域相较于周边区域具有较快的生长速度。

在图11B和图11C中,如前述所提及,由于基板104的曝露的部分104B为不具有掺杂物的区域,擦除栅极介电质146在基板104的未掺杂的部分104B的生长速率会低于在基板104的经掺杂的部分104A的生长速率。因此,擦除栅极介电质146在基板104的经掺杂的部分104A上方具有厚度T1,而擦除栅极介电质146在基板104的未掺杂的部分104B上方具有厚度T2,其中厚度T1大于厚度T2。意及,擦除栅极介电质146在经掺杂的部分104A上的部分的厚度会大于在未掺杂的部分104B上方的部分的厚度。在图11B的剖面图中,擦除栅极介电质146在未掺杂的部分104B上方具有实质上平坦的底表面。意及,在沿着垂直控制栅极138的长度方向的方向上,擦除栅极介电质146在未掺杂的部分104B上方的部分的底表面平坦于擦除栅极介电质146在经掺杂的部分104A上的部分的底表面。

参照图12A至图12D,其中图12A为在图11A至图11C的操作后的记忆体元件100的上视图,且和图8A具有相同的上视图,图12B为沿着图12A的线B-B的剖面图,图12C为沿着图12A的线C-C的剖面图,而图12D为沿着图12A的线D-D的剖面图。在基板104上形成图案化遮罩M2。接着,执行蚀刻制程以移除擦除栅极介电质146不需要的部分。详细来说,图案化遮罩M2形成在并保护共用源极区128的上方的擦除栅极介电质146。例如,擦除栅极介电质146覆盖基板104的部分104A并曝露基板104的部分104B。因此,基板104的部分104B上方的擦除栅极介电质146经由图案化遮罩M2被移除,因此基板104的部分104B曝露于图案化遮罩M2。在部分实施例中,图案化遮罩M2的图案实质上与图8A所示的图案化遮罩M1的图案相反。

参照图13A至图13D,其中图13A为在图12A至图12D的操作后的记忆体元件100的上视图,且和图12A具有相同的上视图,图13B为沿着图13A的线B-B的剖面图,图13C为沿着图13A的线C-C的剖面图,而图13D为沿着图13A的线D-D的剖面图。移除图案化遮罩M2。选择性地形成介电层1502在基板104的曝露表面上。例如,介电层1502覆盖了基板104的部分104B。形成介电层1502的制程可包括高温氧化、原位蒸气产生氧化、其他适合的沉积或成长制程、上述的组合,或相似者。

参照图14A至图14D,其中图14A为在图13A至图13D的操作后的记忆体元件100的上视图,且和图13A具有相同的上视图,图14B为沿着图14A的线B-B的剖面图,图14C为沿着图14A的线C-C的剖面图,而图14D为沿着图14A的线D-D的剖面图。形成栅极层1504于基板104上方并覆盖介电层1502。栅极层1504可由掺杂多晶硅、金属,或其他适合的导电材料组成,且可由CVD、PVD,或其他适合的方法形成。

参照图15A至图15D,其中图15A为在图14A至图14D的操作后的记忆体元件100的上视图,且和图14A具有相同的上视图,图15B为沿着图15A的线B-B的剖面图,图15C为沿着图15A的线C-C的剖面图,而图15D为沿着图15A的线D-D的剖面图。回蚀刻栅极层1504直到栅极层1504的上表面低于控制栅极硬遮罩210的上表面。在部分实施例中,栅极层1504的上表面实质上与控制栅极138的上表面齐平。在部分实施例中,蚀刻制程使得凹陷的栅极层1504具有实质上平坦的表面。在蚀刻制程后,可将掺杂物植入栅极层1504内,并接着执行退火制程以活化掺杂物。在部分实施例中,栅极层1504残留在擦除栅极介电质146上方的部分称为擦除栅极144。

参照图16A至图16C,其中图16A至图16C分别和图15B至图15D具有相同剖面。共形地形成硬遮罩层1702于基板104上方。硬遮罩层1702可通过CVD、PVD,或其他适合的沉积方法形成。

参照图17A至图17D,其中图17A为在图16A至图16C的操作后的记忆体元件100的上视图,且和图15A具有相同的上视图,图17B为沿着图17A的线B-B的剖面图,图17C为沿着图17A的线C-C的剖面图,而图17D为沿着图17A的线D-D的剖面图。形成图案化遮罩M3于基板104上方。接着经由图案化遮罩M3执行蚀刻制程以图案化硬遮罩层1702及栅极层1504(参照图16A至图16C)以形成选择栅极150。在部分实施例中,图案化遮罩M3可为光阻。

参照图18A至图18D,其中图18A为在图17A至图17D的操作后的记忆体元件100的上视图,且和图17A具有相同的上视图,图18B为沿着图18A的线B-B的剖面图,图18C为沿着图18A的线C-C的剖面图,而图18D为沿着图18A的线D-D的剖面图。移除图案化遮罩M3(参照图17A至图17D)。在部分实施例中,图案化遮罩M3可通过适当方法移除,例如剥离。沿着选择栅极150的外侧壁形成选择栅极间隔物148。选择栅极间隔物148可通过下列方法形成,沉积间隔物层并移除间隔物层最薄的部分。选择栅极间隔物148可通过CVD、PVD、其他适合的沉积制程形成、上述的组合,或相似者。

参照图19A至图19C,其中图19A至图19C分别和图18B至图18D具有相同剖面。形成硬遮罩300于基板104上方并邻近选择栅极间隔物148。在部分实施例中,硬遮罩300可形成具有经平坦化的上表面。形成硬遮罩300的制程包括旋涂有机抗反射涂布层(organic ARC(anti-reflective coating)coating)。

参照图20A至图20D,其中图20A为在图19A至图19C的操作后的记忆体元件100的上视图,且和图18A具有相同的上视图,图20B为沿着图20A的线B-B的剖面图,图20C为沿着图20A的线C-C的剖面图,而图20D为沿着图20A的线D-D的剖面图。形成图案化遮罩M4于基板104上方。在部分实施例中,图案化遮罩M4具有开口O2位于基板104的部分104B上方。例如,基板104的部分104B上方的栅极层1504经由图案化遮罩M4曝露。另一方面,在图20A中,选择栅极150的部分经由图案化遮罩M4曝露。在部分实施例中,图案化遮罩M4为光阻。

参照图21A至图21D,其中图21A为在图20A至图20D的操作后的记忆体元件100的上视图,且和图20A具有相同的上视图,图21B为沿着图21A的线B-B的剖面图,图21C为沿着图21A的线C-C的剖面图,而图21D为沿着图21A的线D-D的剖面图。执行蚀刻制程以经由开口O2移除基板104的部分104B上方的栅极层1504的部分。因此,基板104的部分104B在蚀刻制程后经由图案化遮罩M4曝露。另一方面,选择栅极150经由图案化遮罩M4曝露的部分被移除,如图21A所示。

参照图22A至图22D,其中图22A为在图21A至图21D的操作后的记忆体元件100的上视图,且和图21A具有相同的上视图,图22B为沿着图22A的线B-B的剖面图,图22C为沿着图22A的线C-C的剖面图,而图22D为沿着图22A的线D-D的剖面图。通过适当的方法移除图案化遮罩M4,例如剥离。接着,移除硬遮罩300。在部分实施例中,硬遮罩300可通过适当的蚀刻制程移除。

参照图23A至图23D,其中图23A为在图22A至图22D的操作后的记忆体元件100的上视图,且和图22A具有相同的上视图,图23B为沿着图23A的线B-B的剖面图,图23C为沿着图23A的线C-C的剖面图,而图23D为沿着图23A的线D-D的剖面图。形成图案化遮罩302以覆盖基板104的部分104B。图案化遮罩302可为光阻,且可通过光微影制程形成。接着,执行蚀刻制程以移除曝露的介电层1502,借此在选择栅极150下方形成选择栅极介电质156。

参照图24A至图24C,其中图24A至图24C分别和图23B至图23D具有相同剖面。执行离子植入制程以在基板104中形成漏极区126。在部分实施例中,漏极区126分别邻近于选择栅极介电质156。在部分实施例中,离子植入可通过多层遮罩的系列步骤以在漏极区126中形成不同程度的掺杂。

参照图25A至图25C,其中图25A至图25C分别和图24A至图24C具有相同剖面。在基板104内和漏极区126上方形成硅化物垫170。在部分实施例中,硅化物垫170可为硅化镍或其他适合的硅化物,且可通过适当的硅化制程形成。

参照图26A至图26C,其中图26A至图26C分别和图25A至图25C具有相同剖面。移除位于基板104的部分104B上方的图案化遮罩302。在部分实施例中,图案化遮罩302可通过剥离移除。在图案化遮罩302移除后,浮栅极间隔物142和基板104的部分104B曝露。

参照图27A至图27C,其中图27A至图27C分别和图26A至图26C具有相同剖面。形成图案化遮罩304于基板104上方并覆盖漏极区126。图案化遮罩304可为光阻,且可通过光微影制程形成。

在图27B中,沿着垂直擦除栅极144的长度方向的方向,基板104的部分104B的曝露表面具有宽度W4。在部分实施例中,宽度W4的范围约80nm至约120nm。在部分实施例中,宽度W4为单元间距,为选择栅极临界尺寸的关键因素。若宽度W4过小,则在后续步骤中将会难以填补材料至此窄小区域(例如,浮栅极间隔物142之间的间距),且会导致在此区域中形成不希望形成的孔隙。另一方面,若宽度W4过大,则元件则会过大,且无法达到所欲的元件密度。

在图27C中,沿着擦除栅极144的长度方向的方向,基板104的部分104B的曝露表面具有宽度W5。在部分实施例中,宽度W5的范围约80nm至约120nm。在部分实施例中,宽度W5为擦除栅极144之间的间距。若宽度W5过小,则此曝露的区域将会过小以至于无法容纳后续步骤中所形成的共用源极条(例如,共用源极条160CS)。另一方面,基板104的部分104B的上表面和擦除栅极介电质146的上表面的距离D1的范围约30nm至约50nm。若距离D1过小(例如,擦除栅极介电质146太薄),则擦除栅极介电质146将无法分隔擦除栅极144和基板104。另一方面,若距离D1过大(例如,擦除栅极介电质146太厚),则擦除栅极介电质146将可能导致不满意的元件表现。在部分实施例中,宽度W4与宽度W5的比例约为0.66至约1.5。在部分实施例中,宽度W5和距离D1的比例约为1.6至约4。

参照图28A至图28C,其中图28A至图28C分别和图27A至图27C具有相同剖面。在基板104的部分104B上方形成硅化物垫172。在部分实施例中,硅化物垫172可为硅化镍或其他适合的硅化物,且可通过适当的硅化制程形成。在图28C中,硅化物垫172至少部分地接触共用源极区128,借此在硅化物垫172和共用源极区128之间形成电性连接。

如图9A至图9C所讨论的,基板104的部分104B在形成共用源极区128期间被遮罩,而基板104的部分104B实质上不具有共用源极区128的掺杂物。此外,在本处所讨论的制程中,亦没有对基板104的部分104B执行其他有意的掺杂制程。因此,基板104的部分104B不具有掺杂,或是具有可忽略的掺杂。另一方面,由于硅化物垫172形成在基板104的部分104B上,硅化物垫172不具有掺杂,或是具有可忽略的掺杂。换言之,硅化物垫172的掺杂物浓度小于共用源极区128的掺杂物浓度。

参照回图24A,如前述所提及,硅化物垫170是通过离子植入直接形成在基板104的漏极区126上。因此,漏极区126上方的硅化物垫170可能具有漏极区126的掺杂物。相反地,与共用源极区128连接的硅化物垫172不具有掺杂,或是具有可忽略的掺杂。换言之,硅化物垫172的掺杂物浓度小于硅化物垫170的掺杂物浓度。

在本揭露部分实施例中,由于基板104的部分104B在形成共用源极区128的期间被遮罩,通过离子植入而形成在共用源极区128中具有弯曲或球根表面轮廓的擦除栅极介电质146将不会形成在基板104的部分104B上方(由于此处不具有共用源极区128)。也因此基板104的部分104B至此步骤仍具有实质上平坦的上表面,也因此导致具有平坦上表面的硅化物垫172。因此,在部分实施例中,硅化物垫172的上表面和硅化物垫170的上表面实质上齐平。这样的配置有利于后续形成的条(例如,图33A至图33C中的共用源极条160CS和漏极条160D)。

另一方面,如图21A至图21D所提及,基板104的部分104B上方的栅极层1504是与选择栅极150使用同一遮罩移除的。然而,若基板104的部分104B上方具有弯曲或球根表面轮廓的擦除栅极介电质146,则需要额外的光罩曝露此区域,并移除基板104的部分104B上方的擦除栅极介电质146,因此将对制程产生额外的开销。

参照图29A至图29C,其中图29A至图29C分别和图28A至图28C具有相同剖面。移除图案化遮罩304,且在基板104上方形成第一层间介电层200。在部分实施例中,第一层间介电层200填补硅化物垫170和172上方的区域。第一层间介电层200可为氧化物、低介电常数(low-k)介电质、其他适合的介电质、上述的组合,或相似者。第一层间介电层200可通过CVD、PVD、溅镀,或其他适合的沉积制程形成。

参照图30A至图30C,其中图30A至图30C分别和图29A至图29C具有相同剖面。执行化学机械研磨制程以移除多余的第一层间介电层200直到擦除栅极144、控制栅极138,和选择栅极150曝露。

参照图31A至图31C,其中图31A至图31C分别和图30A至图30C具有相同剖面。在基板104上方形成第二层间介电层202。第二层间介电层202可为氧化物、低介电常数(low-k)介电质、其他适合的介电质、上述的组合,或相似者。第二层间介电层202可通过CVD、PVD、溅镀,或其他适合的沉积制程形成。

参照图32A至图32D,其中图32A为在图31A至图31C的操作后的记忆体元件100的上视图,且和图23A具有相同的上视图,图32B为沿着图32A的线B-B的剖面图,图32C为沿着图32A的线C-C的剖面图,而图32D为沿着图32A的线D-D的剖面图。蚀刻(或图案化)第一和第二层间介电层200、202以形成开口O3、O4、O5。在部分实施例中,开口O3曝露漏极区126上方的硅化物垫172,开口O4曝露硅化物垫172,而开口O5曝露擦除栅极144。如前述所提及,由于硅化物垫172具有实质上平坦的上表面,且和硅化物垫170的上表面齐平,故蚀刻剂会实质上在相同的时间抵达硅化物垫170和172。在部分实施例中,假如硅化物垫170和172的上表面位于不同水平高度,则具有比较高的上表面的将会产生过度蚀刻,进而影响元件表现。

参照图33A至图33D,其中图33A为在图32A至图32D的操作后的记忆体元件100的上视图,且和图32A具有相同的上视图,图33B为沿着图33A的线B-B的剖面图,图33C为沿着图33A的线C-C的剖面图,而图33D为沿着图33A的线D-D的剖面图。分别形成漏极条160D、共用源极条160CS和擦除栅极条160EG在开口O3、O4、O5内。在部分实施例中,开口O3内的漏极条160D亦可称为漏极接触160D。开口O4内的共用源极条160CS亦可称为共用源极接触160CS。开口O5内的擦除栅极条160EG亦可称为擦除栅极接触160EG。漏极条160D、共用源极条160CS和擦除栅极条160EG具有导电性,且可为钨、铜、铝、铜铝、其他适合金属或导电材料、上述的组合,或相似者。漏极条160D、共用源极条160CS和擦除栅极条160EG可通过下列方法形成,例如,沉积导电材料于基板104上方并填补开口O3、O4、O5内,接着执行CMP制程以移除多余的导电材料直到第二层间介电层202曝露。

图34A至图34C为本揭露的部分实施例的形成记忆体元件的方法1000。虽然方法100是由一系列操作或步骤来描述,然应了解此方法并没有限制操作或其顺序。因此,在部分实施例中,这些操作或步骤可以不同的顺序被执行,及/或同时地执行。此外,在部分实施例中,描述的操作或步骤可被切割为多个操作或步骤,其可在不同时间点或是相同时间点与其他操作或是子操作一起进行。在部分实施例中,描述的操作或步骤可被省略,或包括其他没有被描述的操作或步骤。

在方块S101中,在基板上形成隔离结构。图2A至图2C为对应至方块S101的部分实施例的示意图。

在方块S102中,在基板上形成栅极氧化物、浮栅极层、控制栅极介电层、控制栅极层,以及控制栅极硬遮罩。图3A至图3C为对应至方块S102的部分实施例的示意图。

在方块S103中,蚀刻控制栅极硬遮罩、控制栅极层,以及控制栅极介电层以形成控制栅极和控制栅极介电质。图4A至图4C为对应至方块S103的部分实施例的示意图。

在方块S104中,在基板上形成控制栅极间隔物层。图5A和图5B为对应至方块S104的部分实施例的示意图。

在方块S105中,蚀刻控制栅极间隔物层以在控制栅极的相对侧壁上形成控制栅极间隔物,并蚀刻浮栅极层和栅极氧化物以形成浮栅极和浮栅极介电质。图6A和图6B为对应至方块S105的部分实施例的示意图。

在方块S106中,在浮栅极的相对侧壁上形成浮栅极间隔物。图7A和图7B为对应至方块S106的部分实施例的示意图。

在方块S107中,在基板上形成第一图案化遮罩,第一图案化遮罩曝露基板的第一部分并覆盖基板的第二部分。图8A至图8D为对应至方块S107的部分实施例的示意图。

在方块S108中,在基板的第一部分中形成共用源极区。图9A至图9C为对应至方块S108的部分实施例的示意图。

在方块S109中,移除经第一图案化遮罩曝露的浮栅极间隔物。图10A至图10C为对应至方块S109的部分实施例的示意图。

在方块S110中,移除第一图案化遮罩,并在共用源极区上方形成擦除栅极介电层。图11A至图11C为对应至方块S110的部分实施例的示意图。

在方块S111中,在基板上形成第二图案化遮罩,其中第二图案化遮罩覆盖基板的第一部分,并移除经由第二图案化遮罩曝露的擦除栅极介电层。图12A至图12D为对应至方块S111的部分实施例的示意图。

在方块S112中,在基板上形成第一介电层。图13A至图13D为对应至方块S112的部分实施例的示意图。

在方块S113中,在基板上形成栅极层。图14A至图14D为对应至方块S113的部分实施例的示意图。

在方块S114中,回蚀刻栅极层以形成擦除栅极。图15A至图15D为对应至方块S114的部分实施例的示意图。

在方块S115中,在基板上形成硬遮罩层。图16A至图16C为对应至方块S115的部分实施例的示意图。

在方块S116中,在基板上形成第三图案化遮罩,并蚀刻栅极层以形成选择栅极。图17A至图17D为对应至方块S116的部分实施例的示意图。

在方块S117中,移除第三图案化遮罩,并在选择栅极的侧壁上形成选择栅极间隔物。图18A至图18D为对应至方块S117的部分实施例的示意图。

在方块S118中,在基板上和选择栅极间隔物旁形成硬遮罩。图19A至图19C为对应至方块S118的部分实施例的示意图。

在方块S119中,在基板上形成第四图案化遮罩,其中第四图案化遮罩曝露基板的第二部分。图20A至图20D为对应至方块S119的部分实施例的示意图。

在方块S120中,移除基板的第二部分上方的栅极层。图21A至图21D为对应至方块S120的部分实施例的示意图。

在方块S121中,移除第四图案化遮罩和硬遮罩。图22A至图22D为对应至方块S121的部分实施例的示意图。

在方块S122中,在基板的第二部分上方形成第五图案化遮罩。图23A至图23D为对应至方块S122的部分实施例的示意图。

在方块S123中,执行离子植入以在基板内形成漏极区。图24A至图24C为对应至方块S123的部分实施例的示意图。

在方块S124中,在漏极区上方形成第一硅化物垫。图25A至图25C为对应至方块S124的部分实施例的示意图。

在方块S125中,移除第五图案化遮罩以曝露基板的第二部分。图26A至图26C为对应至方块S125的部分实施例的示意图。

在方块S126中,在基板上方形成第六图案化遮罩并覆盖漏极区。图27A至图27C为对应至方块S126的部分实施例的示意图。

在方块S127中,在基板的第二部分中形成第二硅化物垫。图28A至图28C为对应至方块S127的部分实施例的示意图。

在方块S128中,移除第六图案化遮罩,并在基板上形成第一层间介电层。图29A至图29C为对应至方块S128的部分实施例的示意图。

在方块S129中,执行CMP制程直到擦除栅极曝露。图30A至图30C为对应至方块S129的部分实施例的示意图。

在方块S130中,在基板上方形成第二层间介电层。图31A至图31C为对应至方块S130的部分实施例的示意图。

在方块S131中,蚀刻第一和第二层间介电层以形成开口。图32A至图32D为对应至方块S131的部分实施例的示意图。

在方块S132中,在开口内填补导电材料。图33A至图33D为对应至方块S132的部分实施例的示意图。

根据上述讨论,可看出本揭露的部分实施例提供了优点。然应了解,这些实施例可提供其他优点,且不是所有优点皆需要在此讨论,且不是所有实施例都具有特定的优点。其中一优点为,基板上定义共用源极条的区域在形成共用源极区的期间被遮罩。因此,具有弯曲或球根状表面轮廓的擦除栅极介电质将不会形成在基板的这些区域上。因此,用于移除具有弯曲或球根状表面轮廓的擦除栅极介电质的的外遮罩将可以省略,并可节省制程的开销。另一方面,基板的这些区域的上表面为实质上平坦,使得此区域形成的硅化物垫也具有平坦上表面。此有助于后续在硅化物垫上方形成接触的制程。

本揭露的部分实施例为一种记忆体元件,包含擦除栅极、擦除栅极介电质、第一和第二浮栅极、第一和第二控制栅极、第一选择栅极、第二选择栅极、共用源极条,以及硅化物垫。擦除栅极位于基板的第一部分上方。擦除栅极介电质位于擦除栅极和基板的第一部分之间。第一和第二浮栅极位于擦除栅极的相对两侧。第一和第二控制栅极分别位于第一和第二浮栅极上方。第一选择栅极沿着第一方向至少部分通过第一控制栅极与擦除栅极隔开。第二选择栅极沿着第一方向至少部分通过第二控制栅极与擦除栅极隔开。共用源极条位于基板的第二部分上,其中共用源极条与擦除栅极沿着垂直第一方向的第二方向上排列。硅化物垫位于共用源极条下方且位于基板的第二部分内,其中硅化物垫的上表面平坦于擦除栅极介电质的下表面。

根据部分实施例,其中擦除栅极介电质的下表面为弯曲。

根据部分实施例,还包含共用源极区,位于擦除栅极介电质下方并位于基板的第一部分内,其中硅化物垫不具有共用源极区内的掺杂物。

根据部分实施例,其中在沿着第一方向的剖面中,硅化物垫的水平宽度小于擦除栅极介电质的水平宽度。

根据部分实施例,其中在沿着第二方向的剖面中,硅化物垫与擦除栅极介电质的侧壁接触。

根据部分实施例,其中在沿着第二方向的剖面中,硅化物垫与第一和第二浮栅极以非零距离隔开。

根据部分实施例,其中在沿着第二方向的剖面中,硅化物垫的上表面低于擦除栅极介电质的上表面,且高于擦除栅极介电质的下表面。

本揭露的部分实施例为一种记忆体元件,包含擦除栅极、擦除栅极介电质、第一和第二浮栅极、第一和第二控制栅极、第一选择栅极、第二选择栅极、第一硅化物垫、第一浮栅极间隔物,以及第二浮栅极间隔物。擦除栅极位于基板的第一部分上方。擦除栅极介电质位于擦除栅极和基板的第一部分之间。第一和第二浮栅极位于擦除栅极的相对两侧。第一和第二控制栅极分别位于第一和第二浮栅极上方。第一选择栅极沿着第一方向至少部分通过第一控制栅极与擦除栅极隔开。第二选择栅极沿着第一方向至少部分通过第二控制栅极与擦除栅极隔开。第一硅化物垫位于基板的第二部分中,其中第一硅化物垫和擦除栅极沿着垂直第一方向的第二方向排列。第一浮栅极间隔物位于第一浮栅极的侧壁上,其中第一硅化物垫通过第一浮栅极间隔物与第一浮栅极隔开。第二浮栅极间隔物位于第二浮栅极的侧壁上,其中第一硅化物垫通过第二浮栅极间隔物与第二浮栅极隔开。

根据部分实施例,还包含层间介电层位于第一浮栅极间隔物和第二第一浮栅极间隔物之间。以及共用源极条延伸穿越层间介电层并接触第一硅化物垫。

根据部分实施例,还包含共用源极区,位于基板的第一部分内以及位于擦除栅极下方,其中在沿着第二方向的剖面中,共用源极条通过第一硅化物垫与共用源极区电性连接。

根据部分实施例,其中第一浮栅极间隔物和第二浮栅极间隔物由氮化物组成。

根据部分实施例,还包含漏极区,位于基板内且邻近第一选择栅极。第二硅化物,位于漏极区内,其中第二硅化物的掺杂物浓度低于第一硅化物的掺杂物浓度。以及漏极条,位于第二硅化物上方并与第二硅化物接触。

根据部分实施例,还包含第一控制栅极间隔物和第二控制栅极间隔物,分别位于第一控制栅极的侧壁和第二控制栅极的侧壁上,其中在沿着第一方向并穿越第一硅化物的第一剖面中,第一浮栅极间隔物和第二浮栅极间隔物分别与第一控制栅极间隔物和第二控制栅极间隔物接触。

根据部分实施例,其中在沿着第一方向并穿越擦除栅极的第二剖面中,擦除栅极与第一控制栅极间隔物和第二控制栅极间隔物接触。

根据部分实施例,其中在沿着第一方向并穿越第一硅化物的第一剖面中,第一硅化物的宽度小于第一浮栅极间隔物和第二浮栅极间隔物之间的距离。

本揭露的部分实施例为一种制造记忆体元件的方法,包含在基板上形成第一浮栅极和第二浮栅极;分别在第一浮栅极和第二浮栅极上方形成第一控制栅极和第二控制栅极;形成图案化遮罩以覆盖第一控制栅极和第二控制栅极,其中图案化遮罩曝露位于第一控制栅极和第二控制栅极之间的基板的第一部分,且图案化遮罩曝露第一控制栅极和第二控制栅极之间的基板的第二部分;在基板的第一部分中形成共用源极区,其中在形成共用源极区期间,图案化遮罩保护基板的第二部分;移除图案化遮罩;在基板的第一部分上方形成擦除栅极;以及在基板的第二部分上方形成共用源极条。

根据部分实施例,还包含在形成共用源极条之前在基板的第二部分中形成硅化物垫。

根据部分实施例,还包含在基板的第一部分和第二部分上方形成擦除栅极介电质,其中擦除栅极介电质在基板的第一部分上具有在比基板的第二部分上还快的成长速率。

根据部分实施例,其中形成擦除栅极包含形成擦除栅极层于基板的第一部分和第二部分上方;以及自基板的第二部分上方移除擦除栅极层。

根据部分实施例,还包含在形成该图案化遮罩之前在第一浮栅极的侧壁和第二浮栅极的侧壁上分别形成第一浮栅极间隔物和第二浮栅极间隔物;以及在形成该图案化遮罩之后,移除基板的第一部分上方的第一浮栅极间隔物和第二浮栅极间隔物,其中第一浮栅极间隔物和第二浮栅极间隔物残留在基板的第二部分上方。

上文概述了若干实施例的特征,以便本领域熟悉此项技艺者可更好地理解本揭示案的态样。本领域熟悉此项技艺者应当了解到他们可容易地使用本揭示案作为基础来设计或者修改其他制程及结构,以实行相同目的及/或实现相同优势的。本领域熟悉此项技艺者亦应当了解到,此类等效构造不脱离本揭示案的精神及范畴,以及在不脱离本揭示案的精神及范畴的情况下,其可对本文进行各种改变、取代及变更。

- 记忆体元件的制造方法、记忆体元件与相变化记忆体元件

- 记忆体元件以及制造与操作记忆体元件的方法