像素电路

文献发布时间:2023-06-19 13:45:04

技术领域

本公开文件涉及一种像素电路,特别是一种关于常黑型(Normally black,简称NB)的像素电路。

背景技术

在一般采用常白型(Normally white,简称NW)的显示面板中,为了产生低灰阶的显示画面,需要提高与发光单元耦接的驱动晶体管的控制端的电压使其关闭,进而降低发光单元发光的时间以减低灰阶。

然而,在大尺寸的显示面板中,像素电路与电源信号的入力点间可能会产生较大的电压降与信号延迟,导致显示面板产生漏光而无法画面全黑的问题。

发明内容

本公开文件提供一种像素电路,其包含发光单元、第一晶体管、驱动电路、脉冲宽度判定电路、驱动振幅判定电路以及重置电路。第一晶体管耦接发光单元,用以响应于第一节点的电压导通。驱动电路用以提供对应于第二节点的电压的驱动电流至第一晶体管。脉冲宽度判定电路用以选择性地将第一驱动信号传递至第一节点以导通第一晶体管而决定驱动电流的脉冲宽度。驱动振幅判定电路耦接第二节点,用以响应于第一栅极信号,以根据第一数据信号决定驱动电流的振幅大小。重置电路用以在重置信号的电压变化时重置第一节点的电压和第二节点的电压。

上述的像素电路的优点之一,在于通过常黑型的像素电路,解决显示面板在低灰阶情况时因为漏光导致无法画面全黑的问题。

附图说明

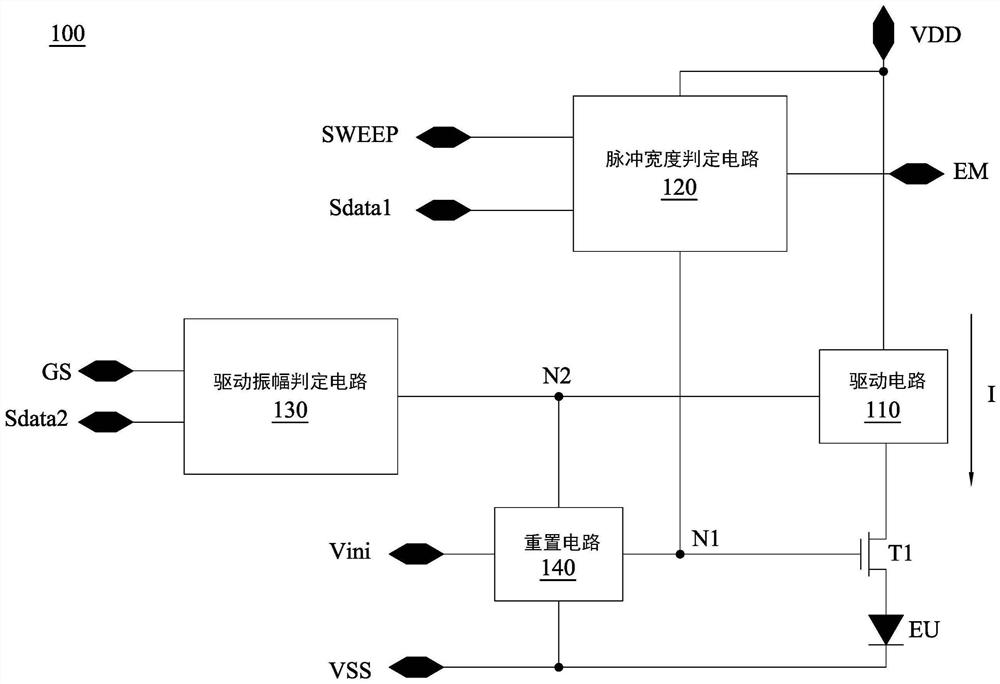

图1为根据本公开文件一些实施例所示出的像素电路的功能方框图。

图2为根据本公开文件一实施例所示出的像素电路的示意图。

图3为根据本公开文件一实施例所示出的像素电路的信号时序波形图。

图4A~4D为根据本公开文件一实施例所示出的像素电路的操作示意图。

图5为根据本公开文件另一实施例所示出的像素电路的示意图。

图6为根据图5的像素电路所示出的信号时序波形图。

附图标记说明:

100:像素电路

500:像素电路

EU:发光单元

T1~T11:晶体管

110,510:驱动电路

120,520:脉冲宽度判定电路

130,530:驱动振幅判定电路

140,540:重置电路

VDD:驱动信号

VSS:驱动信号

Vini:重置信号

Comp:补偿信号

Sdata,Sdata1,Sdata2:数据信号

SWEEP:脉冲信号

GS,GS1,GS2:栅极信号

EM:发光信号

V1:第一电压电平

V2:第二电压电平

Vs,Vs1,Vs2:数据电压

N1~N7:节点

I:驱动电流

具体实施方式

下文是举实施例配合说明书附图作详细说明,但所描述的具体实施例仅仅用以解释本发明,并不用来限定本发明,而结构操作的描述非用以限制其执行的顺序,任何由元件重新组合的结构,所产生具有均等技术效果的装置,皆为本发明公开内容所涵盖的范围。

在全篇说明书与权利要求所使用的用词(terms),除有特别注明外,通常具有每个用词使用在此领域中、在此公开的内容中与特殊内容中的平常意义。某些用以描述本公开的用词将于下或在此说明书的别处讨论,以提供本领域技术人员在有关本公开的描述上额外的引导。

图1为根据本公开文件一些实施例所示出的像素电路100的功能方框图。如图1所示,像素电路100包含发光单元EU、第一晶体管T1、驱动电路110、脉冲宽度判定电路120、驱动振幅判定电路130以及重置电路140。

结构上,第一晶体管T1耦接于发光单元EU以及驱动电路110之间。第一晶体管T1的控制端耦接第一节点N1。脉冲宽度判定电路120通过第一节点N1耦接第一晶体管T1的控制端。重置电路140分别耦接第一晶体管T1的控制端以及驱动电路110于第一节点N1以及第二节点N2。驱动振幅判定电路130通过第二节点N2耦接驱动电路110。

操作上,驱动电路110用以提供对应于第二节点N2的电压的驱动电流I至第一晶体管T1,而第一晶体管T1则用以响应于第一节点N1的电压导通。在本公开文件的实施例中,第一晶体管T1为N型金属氧化物半导体导体(NMOS)。

脉冲宽度判定电路120用以选择性地将驱动信号VDD传递至第一节点N1以导通第一晶体管T1,而决定驱动电流I的脉冲宽度。更详细地说,脉冲宽度判定电路120会根据数据信号Sdata1和脉冲信号SWEEP决定是否致能。当脉冲宽度判定电路120致能时,第一节点N1便会接收到驱动信号VDD,进而导通第一晶体管T1。也就是说,脉冲宽度判定电路120能够控制第一晶体管T1的导通时间,以决定驱动电流I的脉冲宽度。

驱动振幅判定电路130用以响应于栅极信号GS,以将数据信号Sdata2传递至第二节点N2。如此一来,驱动电路110便能产生对应数据信号Sdata2的驱动电流I。

重置电路140用以在重置信号Vini的电压变化时,重置第一节点N1的电压和第二节点N2的电压。

图2为根据本公开文件一实施例所示出的像素电路100的示意图。如图2所示,驱动电路110包含第二晶体管T2、第三晶体管T3,其各自包含第一端、第二端和控制端,且驱动电路110还包含第一电容C1。第二晶体管T2的第一端用以接收驱动信号VDD,第二晶体管T2的第二端耦接第一晶体管T1的第一端,第二晶体管T2的控制端耦接第二节点N2。第三晶体管T3的第一端耦接第二节点N2,第三晶体管T3的第二端耦接第一晶体管T1的第一端,第三晶体管T3的控制端用以接收补偿信号Comp。在一些实施例中,驱动电路110的第一电容C1可以省略。

脉冲宽度判定电路120包含第四晶体管T4、第五晶体管T5、第六晶体管T6、第七晶体管T7,其各自包含第一端、第二端和控制端,且脉冲宽度判定电路120还包含第二电容C2以及第三电容C3。第四晶体管T4的第一端耦接第三节点N3,第四晶体管T4的第二端耦接第一节点N1,第四晶体管T4的控制端用以接收发光信号EM。第五晶体管T5的第一端用以接收驱动信号VDD,第五晶体管T5的控制端耦接第四节点N4,第五晶体管T5的第二端耦接第三节点N3。第六晶体管T6的第一端耦接第四节点N4,第六晶体管T6的第二端耦接第三节点N3,第六晶体管T6的控制端用以接收补偿信号Comp。第七晶体管T7的第一端用以接收数据信号Sdata1,第七晶体管T7的第二端耦接第五节点N5,第七晶体管T7的控制端用以接收栅极信号GS。第二电容C2包含第一端以及第二端。第二电容C2的第一端用以接收脉冲信号SWEEP,第二电容C2的第二端耦接第五节点N5。第三电容C3耦接于第四节点N4以及第五节点N5之间。

驱动振幅判定电路130包含第八晶体管T8以及第四电容C4。第八晶体管T8包含第一端、第二端以及控制端。第八晶体管T8的第一端用以接收数据信号Sdata2,第八晶体管T8的控制端用以接收栅极信号GS。第四电容C4包含第一端及第二端。第四电容C4的第一端耦接第八晶体管T8的第二端,第四电容C4的第二端耦接第二节点N2。

重置电路140包含第九晶体管T9、第十晶体管T10含第十一晶体管T11,其各自包含第一端、第二端以及控制端,且重置电路140还包含第五电容C5。第九晶体管T9的第一端耦接第一节点N1,第九晶体管T9的第二端用以接收驱动信号VSS,第九晶体管T9的控制端用以接收重置信号Vini。第四电容C4包含第一端以及第二端。第四电容C4的第一端耦接第一节点N1,第四电容C4的第二端用以接收驱动信号VSS。第十晶体管T10的第一端用以接收重置信号Vini,第十晶体管T10的第二端耦接第二节点N2,第十晶体管T10的控制端与第一端耦接于第六节点N6。第十一晶体管T11的第一端耦接第四节点N4,第十一晶体管T11的第二端与第十一晶体管T11的控制端耦接于第六节点N6。

在图2的实施例中,驱动电路110以及脉冲宽度判定电路120是耦接到相同的信号源以共同接收相同驱动信号VDD。然而,在一些其他的实施例中,驱动电路110以及脉冲宽度判定电路120可以各自耦接于不同的信号源以分别接收不同的驱动信号。通过将驱动电路110以及脉冲宽度判定电路120的信号源独立,可以避免驱动信号VDD的电压降(IR-drop)耦合至脉冲宽度判定电路120的第五晶体管T5的第一端,以避免脉冲宽度判定电路120提供给第一节点N1的电压下降。

图3为根据本公开文件一实施例所示出的像素电路100的信号时序波形图。如图3所示,像素电路100的信号时序可分为四个阶段,分别为重置阶段、补偿阶段、写入阶段与发光阶段。驱动信号VDD具有第一电压电平V1,而驱动信号VSS具有低于第一电压电平V1的第二电压电平V2。数据信号Sdata1、Sdata2则分别具有数据电压Vs1以及数据电压Vs2。

在一些实施例中,数据电压Vs1以及数据电压Vs2介于第一电压电平V1与第二电压电平V2之间,且数据电压Vs1以及数据电压Vs2可以为相等的电压电平。

图4A~4D为根据本公开文件一实施例所示出的像素电路100的操作示意图。以下将以图4A~4D搭配图3更详细地说明像素电路100的操作流程。

如图4A所示,于重置阶段,重置信号Vini会提供逻辑高电平(Logic High level,例如可使P型晶体管导通的第二电压电平V2),使对应的第九晶体管T9、第十晶体管T10以及第十一晶体管T11导通。发光信号EM、补偿信号Comp以及栅极信号GS则会提供逻辑低电平(Logic Low level,例如可使P型晶体管关断的第一电压电平V1),使对应的第三晶体管T3、第四晶体管T4、第六晶体管T6、第七晶体管T7以及第八晶体管T8关断。

此时,第一节点N1会通过第九晶体管T9接收驱动信号VSS,使得第一节点N1的电压被重置为第二电压电平V2。第二节点N2、第四节点N4以及第六节点N6则会接收重置信号Vini,使得第二节点N2、第四节点N4以及第六节点N6的电压也被重置为第二电压电平V2。

如此一来,第一晶体管T1会因为第一节点N1的第二电压电平V2而关断。第二晶体管T2、第五晶体管T5则会分别因为第二节点N2以及第四节点N4的第二电压电平V2而导通,使得驱动信号VDD能够分别传递至第二晶体管T2的第二端以及第三节点N3。

如图4B所示,于补偿阶段,重置信号Vini会从第二电压电平V2变化至第一电压电平V1,使得对应的第九晶体管T9、第十晶体管T10以及第十一晶体管T11关断。补偿信号Comp以及栅极信号GS则会由第一电压电平V1变化至第二电压电平V2,以致能对应的第三晶体管T3、第六晶体管T6、第七晶体管T7以及第八晶体管T8。发光信号EM则会持续提供逻辑低电平,使得第四晶体管T4保持关断。

此时,第二节点N2与第二晶体管T2的第二端之间形成一条充电路径,使得第二晶体管T2的第二端的高电压(亦即,驱动信号VDD的第一电压电平V1)会经由第三晶体管T3对第二节点N2持续充电,直到第二节点N2的电压与第二晶体管T2的第一端的电压的差值,达到第二晶体管T2的临界电压为止,其中具有第二电压电平V2的数据信号Sdata2用于稳定第四电容C4的第一端。

另一方面,第四节点N4与第五晶体管T5的第二端之间也会形成一条充电路径,使得第五晶体管T5的第二端的高电压(亦即,驱动信号VDD的第一电压电平V1)会经由第六晶体管T6对第四节点N4持续充电,直到第四节点N4的电压与第五晶体管T5的第一端的电压的差值达到第五晶体管T5的临界电压为止,其中具有第二电压电平V2的数据信号Sdata1用于稳定第五节点N5。

如图4C所示,于写入阶段,补偿信号Comp会由第二电压电平V2变化至第一电压电平,使得对应的第三晶体管T3、第六晶体管T6关断。发光信号EM以及重置信号Vini则持续提供逻辑低电平,使得对应的第四晶体管T4、第九晶体管T9、第十晶体管T10以及第十一晶体管T11保持关断。栅极信号GS则会于写入阶段提供一逻辑高电平脉冲以致能对应的第七晶体管T7以及第八晶体管T8,使得数据信号Sdata1的数据电压Vs1与数据信号Sdata2的数据电压Vs2,可分别通过第三电容C3以及第四电容C4耦合至第四节点N4与第二节点N2。

如图4D所示,于发光阶段,栅极信号GS、补偿信号Comp以及重置信号Vini会提供逻辑低电平,使得对应的第三晶体管T3、第六晶体管T6、第七晶体管T7、第八晶体管T8、第九晶体管T9、第十晶体管T10以及第十一晶体管T11关断。发光信号EM则会由第一电压电平V1变化至第二电压电平V2,以致能第四晶体管T4。

此时,脉冲信号SWEEP会由第一电压电平V1下降至第二电压电平V2,并通过第三电容C3将上述的电压变化(亦即,第一电压电平V1与第二电压电平V2间的差值)耦合至第四节点N4。

如此一来,第四节点N4的电压会随着脉冲信号SWEEP的电压电平的变化而开始下降,直到第四节点N4的电压与第五晶体管T5的第一端的电压的差值小于第五晶体管T5的临界电压,使得第五晶体管T5导通。

因此,于发光阶段,驱动电路110会依据第二节点N2的电压,提供驱动电流I至第一晶体管T1。脉冲宽度判定电路120则会将驱动信号VDD经由第四晶体管T4以及第五晶体管T5传递至第一节点N1,以将第一节点N1的电压设为第一电压电平V1,进而导通第一晶体管T1。驱动电流I便能通过第一晶体管T1驱动发光单元EU使其发光。

图5为根据本公开文件另一实施例所示出的像素电路500的示意图。像素电路500包含发光单元EU、第一晶体管T1、驱动电路510、脉冲宽度判定电路520、驱动振幅判定电路530以及重置电路540。驱动电路510以及重置电路540可以分别用图2的驱动电路110以及重置电路140来实现。

结构上,前述图2的发光单元EU、第一晶体管T1、驱动电路110、脉冲宽度判定电路120、驱动振幅判定电路130以及重置电路140的连接关系亦适用于图5的发光单元EU、第一晶体管T1、驱动电路510、脉冲宽度判定电路520、驱动振幅判定电路530以及重置电路540,在此不再赘述。

脉冲宽度判定电路520包含第四晶体管T4、第五晶体管T5、第六晶体管T6、第七晶体管T7、第二电容C2以及第三电容C3。前述图2的脉冲宽度判定电路120的第四晶体管T4、第五晶体管T5、第六晶体管T6、第二电容C2以及第三电容C3的连接关系,亦适用于图5的脉冲宽度判定电路520。

值得注意的是,脉冲宽度判定电路520的第七晶体管T7的第一端以及控制端,分别用以接收数据信号Sdata以及栅极信号GS1。

驱动振幅判定电路530包含第八晶体管T8以及第四电容C4。驱动振幅判定电路530的第八晶体管T8的第一端以及控制端,分别用以接收数据信号Sdata以及栅极信号GS2。驱动振幅判定电路530的第四电容C4耦接于驱动振幅判定电路530的第八晶体管T8和第二节点N2之间。

图6为根据图5的像素电路500所示出的信号时序波形图。像素电路500是根据图6的信号时序波形图操作。像素电路500的操作与像素电路100的操作差异在于,像素电路100是通过栅极信号GS共同控制第七晶体管T7与第八晶体管T8的导通与关断,而像素电路500则是通过栅极信号GS1以及栅极信号GS2,分别控制第七晶体管T7与第八晶体管T8的导通与关断。

也就是说,在写入阶段,驱动振幅判定电路530会响应栅极信号GS2于第一子时段内的一脉冲而致能,以将数据信号Sdata的数据电压Vs传递至第二节点N2。接着,脉冲宽度判定电路520会响应栅极信号GS1于第二子时段内的一脉冲而致能,以将数据信号Sdata的数据Vs传递至第四节点N4。

虽然本公开内容已以实施方式公开如上,然其并非用以限定本公开内容,任何本领域具通常知识者,在不脱离本公开内容的构思和范围内,当可作各种的变动与润饰,因此本公开内容的保护范围当视权利要求所界定者为准。