一种基于单Die读重试的纠错调度方法

文献发布时间:2024-04-18 19:44:28

技术领域

本发明涉及半导体存储器技术,尤其涉及一种基于单Die读重试的纠错调度方法。

背景技术

目前SSD行业固件对于读出错的数据一般都首先采用读重试(ReadRetry)方法进行纠错由于固件对于闪存阵列的存储单元AU的状态是不能直接感知,需要通过闪存控制器进行上报,在实际应用过程中,闪存阵列上出错存储单元分布形态各异,在固件调度算法上非常复杂,行业内通常做法是根据闪存控制器上报的出错AU逐个进行ReadRetry纠错。如果当前AU没有纠错成功,固件会重新更新一组参考电压参数进行新一轮的ReadRetry纠错,直到该出错的AU被纠错成功或参考电压参数表内的所有电压参数全部被遍历完还没有纠错成功,才开始进行下一个出错AU的纠错过程。因此在纠错单元最小粒度上行业内普遍调度的为单个AU。

如果按照现有的SSD行业内按照单个4KB大小的AU数据进行逐一纠错会导致ReadRetry读重试纠错效率很低,对于每一个4KB大小的纠错AU单元纠错读命令都需要硬件读取等待时间,该操作调度耗时时间长,导致SSD的命令延时大,SSD纠错性能差。

发明内容

本发明要解决的技术问题在于针对现有技术中的缺陷,提供一种基于单Die读重试的纠错调度方法。

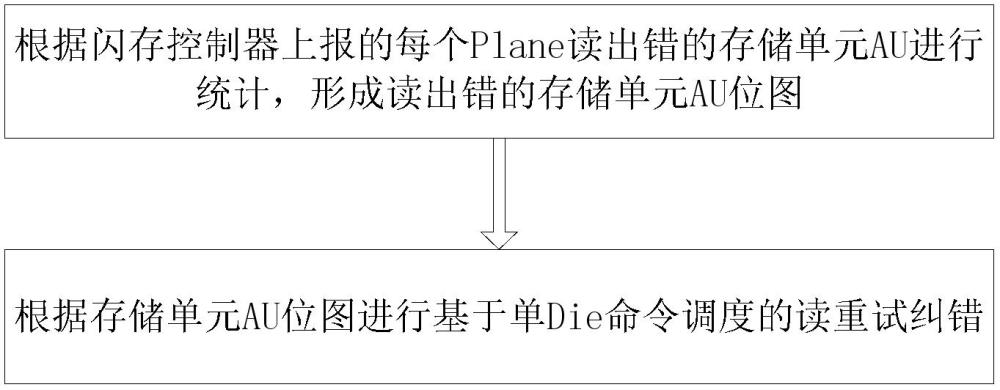

本发明解决其技术问题所采用的技术方案是:一种基于单Die读重试的纠错调度方法,包括以下步骤:

1)主机多Plane读出错后,对闪存控制器上报的每个Plane读出错的存储单元AU进行统计,形成读出错的存储单元AU位图;

其中,存储单元AU位图是同一个Die中每个Plane所在的Page页上4个存储单元AU的分布图,读出错的存储单元AU位图通过将读出错的存储单元AU在存储单元AU位图进行标记形成;

2)根据存储单元AU位图进行基于单Die命令调度的读重试纠错;

2.1)选择一个上报的读出错AU,获得当前有出错的AU所在Page的存储单元AU位图;

2.2)根据存储单元AU位图确定该Die中所有存在读出错的存储单元AU的Plane;

2.3)设定参考电压后进行读重试,将当前单Die所有出错Plane内部相应Page页数据都读到对应的页寄存器中,按照步骤1)建立的读出错的存储单元AU位图逐个将该Page页中各Plane读出错的AU数据传输到控制器中;

2.4)对传输到控制器内的AU数据进行读重试纠错,直到控制器中所有的存储单元AU被纠错成功或放弃。

按上述方案,步骤2.4)中对传输到控制器内的AU数据进行读重试纠错,具体如下:

对传输到控制器内的所有AU数据经过解码后,如果对应的读出错的数据经过解码后成功纠错,则将成功纠错的AU数据传输到主机端;

如果对应的读出错的数据经过解码后重新出错,对重新出错的所有AU数据,调整电压参数后进行新一轮的读重试纠错,直到遍历参考电压表的参数值或控制器中所有的存储单元AU被纠错成功。

本发明产生的有益效果是:

本发明方法与传统的单个4KB大小的AU数据逐个进行读重试纠错方法相比,通过设置读出错的4KB大小的AU分布位图,可以有效缩短读重试纠错方法时间,提升纠错效率。

附图说明

下面将结合附图及实施例对本发明作进一步说明,附图中:

图1是本发明实施例的方法流程图;

图2是本发明实施例的单个Page的存储单元AU位图分布图;

图3是本发明实施例的单个Page的读出错的存储单元AU位图分布图;

图4是本发明实施例的读命令在闪存阵列以页Page为单位执行流程图。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

如图1所示,一种基于单Die读重试的纠错调度方法,包括以下步骤:

1)主机多Plane读出错后,根据闪存控制器上报的每个Plane读出错的存储单元AU进行统计,形成读出错的存储单元AU位图;

如图2所示,存储单元AU位图是同一个Die中每个Plane所在的page页(page i)上4个存储单元AU的分布图,图2中一个单Die命令包含4个Plane,;一个单Die命令可包含2plane、4 Plane、6Plane或8Plane;

读出错的存储单元AU位图通过将读出错的存储单元AU在存储单元AU位图进行标记形成,如图3;每个Plane内部4个AU出错的概率与闪存阵列品质相关;

2)基于单Die命令调度的读重试纠错;

2.1)选择一个上报的读出错AU,获得当前有出错的AU所在page的存储单元AU位图;

2.2)根据存储单元AU位图确定该Die中所有存在读出错的存储单元AU所属的Plane;

2.3)设定参考电压后进行读重试,将当前单Die所有出错Plane内部相应Page页数据均读到对应的页寄存器中,按照上述建立的读出错的存储单元AU位图逐个将该Page页中各Plane读出错的AU数据传输到控制器中;

2.4)对传输到控制器内的所有AU数据经过解码后,如果对应的读出错的数据经过解码后成功纠错,则将成功纠错的AU数据传输到主机端;

如果对应的读出错的数据经过解码后重新出错,对重新出错的所有AU数据,调整电压参数后进行新一轮的读重试纠错,直到遍历参考电压表的参数值或控制器中所有的存储单元AU被纠错成功。

本发明方法的纠错时间对比:

如图3所示,主机端一个单Die命令包含4个Plane,该page页读出错位置分别发生在Plane0的AU1和AU3、Plane1的AU0和AU1、Plane2的AU1、Plane3的AU0和AU3,共计7个读出错的4KB的AU数据。

对同一个Page页的一轮读重试纠错中,假定一个Page页从闪存介质阵列中读取到页寄存器中的时间为Tr,单个4KB大小的AU数据从页寄存器传输到控制器的传输时间记为Td,一个4K大小的AU数据从闪存阵列中读到控制器固定地址空间的总耗时Tt,则:

Tt = Tr + Td;其中: Tr大小与所用的闪存介质相关,例如长江存储的X2-9060颗粒的Tr=50us;Td与传输的数据块大小和频率相关,一个4K大小的AU在频率Freq = 533MHz的Td = 6.68us;

那么,一个4K大小的数据总的读取时间Tt = 56.68us;则如果按照行业内通用的单个出错的4KB数据逐个纠错,总耗时为7*Tr + 7*Td,约为400 us。上述过程中当读取每一个出错的4KB数据时都需要从图4所示的闪存介质阵列中读取一个Page页大小的数据到页寄存器中,而且该时间长达50us,在数据传输时又仅仅只是传输4KB大小的出现读出错的AU数据到控制器中,由于Tr的时间远远大于数据传输到控制器的时间,导致整个ReadRetry读重试的时间很长,读命令响应慢。

使用本发明方法,将全部出错的4个Plane的数据全部读取到4个Plane上对应的4个独立的页寄存器中,然后根据步骤1)所示的每个Plane上的AU位图依次将出错的AU数据传输到控制器中,如此例中的Plane0上的AU1和AU3、Plane1的AU0和AU1、Plane2的AU1、Plane3的AU0和AU3,然后一起进行读重试纠错。因此,该过程中的读重试命令总耗时为Tt =4*Tr+7*Td = 4*50+7*6.68 = 246.76 us,相比较行业内单个4KB大小AU逐个进行读重试纠错方法总时间400 us,大幅提升了固件读重试纠错效率。

应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本发明所附权利要求的保护范围。