一种循环迭代乘加运算的硬件架构及方法

文献发布时间:2023-06-19 09:44:49

技术领域

本发明涉及计算机运算领域,主要涉及一种循环迭代乘加运算的硬件架构及方法。

背景技术

数学公式

现有技术中,通常采用计算机软件程序计算该数学公式,时间长,功耗高,成本贵,在许多需要计算大数乘法的领域,诸如密码学领域需要提供一种计算复杂度低、资源消耗低、占用面积小,在需要计算该公式且对面积以及时钟频率有要求的特定场合能起到重要作用的硬件架构及方法。

发明内容

基于上述问题,本申请的目的在于提供一种循环迭代乘加的方法及硬件架构及方法,以解决现有计算公式

第一方面,本申请示出一种循环迭代乘加运算的硬件架构,其特征在于,用于公式

所述接收单元用于接收参数;所述接收单元包括:第一接收端、第二接收端以及第三接收端;

所述选择单元用于筛选参数;所述选择单元包括:第一选择器、第二选择器、第三选择器、第四选择器、第五选择器以及第六选择器;

所述乘法器用于将筛选出的参数与R进行乘法运算,输出乘法结果;

所述加法器用于将乘法结果与筛选出的参数进行加法运算,输出加法结果;

所述存储单元与选择单元连接,用于寄存参数;所述存储单元包括:第一寄存器、第二寄存器和第三寄存器;

所述第一接收端用于接收R,所述第一接收端与乘法器连接;所述第二接收端用于接收a

第一寄存器用于寄存a

所述第三接收端用于接收S

第二方面,本申请示出一种循环迭代乘加运算的方法,其特征在于,用于公式

输入公式

对参数i从1遍历至n-1;对参数j从1遍历至i;

当i=1,j=1时,根据公式计算a

将高位S

由以上技术方案可知,本申请示出一种循环迭代乘加运算的硬件架构及方法,用于公式

附图说明

为了更清楚的说明申请的技术方案,下面将对实施例中所需要使用的附图作简单的介绍,显而易见地,对于本领域的普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

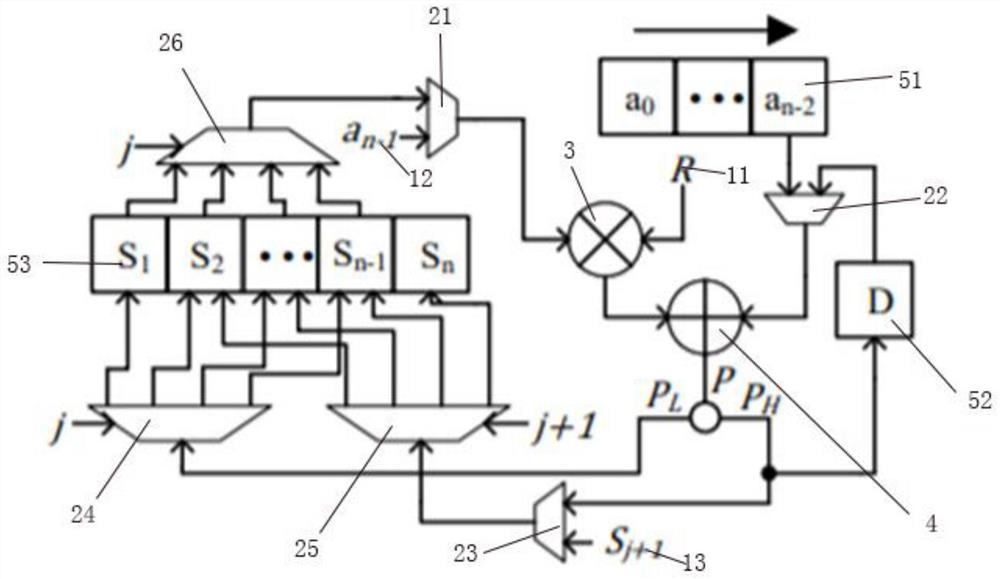

图1为本申请实施例中硬件架构图。

具体实施方式

为了使本技术领域的人员更好地理解本申请实施例中的技术方案,并使本申请实施例的上述目的、特征和优点能够更加明显易懂,下面结合附图对本申请实施例中的技术方案作进一步详细的说明。显然,所描述的示例性实施例仅是本申请一部分实施例,而不是全部的实施例。

为了便于理解,首先对本申请的背景进行介绍,公式

本申请示出的技术方案首先将公式

该公式适用于本申请提出的硬件架构。

参阅图1,图1为本申请示出的一种循环迭代乘加运算的硬件架构示意图,本申请示出的一种循环迭代乘加运算的硬件架构,用于公式

所述接收单元1用于接收参数;所述接收单元1包括:第一接收端11、第二接收端12以及第三接收端13;

所述选择单元2用于筛选参数;所述选择单元2包括:第一选择器21、第二选择器22、第三选择器23、第四选择器24、第五选择器25以及第六选择器26;

所述乘法器3用于将筛选出的参数与R进行乘法运算,输出乘法结果;

所述加法器4用于将乘法结果与筛选出的参数进行加法运算,输出加法结果;

所述存储单元5与选择单元2连接,用于寄存参数;所述存储单元5包括:第一寄存器51、第二寄存器52和第三寄存器53;

所述参数包括:i(i=0~n-1)、a

所述第一接收端11用于接收R,所述第一接收端11与乘法器3连接;所述第二接收端12用于接收a

第一寄存器51用于寄存a

所述第三接收端13用于接收S

所述一种循环迭代乘加运算的硬件架构依据于以下方法:

该方法可进一步参照以下方法:

参阅上述方法,所述一种循环迭代乘加运算的方法基于循环迭代乘加运算的硬件架构,所述循环迭代乘加运算的方法包括:

输入公式

对参数i从1遍历至n-1;对参数j从1遍历至i;

当i=1,j=1时,根据公式计算a

将高位S

该方法中,由于第i个R相加需要进行i次循环迭代乘加运算,共需要n-1个乘R相加的运算,因此总的循环迭代乘加次数为

在一可行性实施例中,当i=1,j=1时,第二接收端12接收a

在一可行性实施例中,当i=2,j=1~i时;在i=1,j=1基础上进行循环迭代乘加运算,当i=1,j=1时,输出高位S

当i=2,j=1时,第三寄存器53输入S

当i=2,j=2时,第三寄存器53输入S

对于i=1~n-1,j=1~i,其计算过程以此类推;

当i=n-1,j=n-1时,C={S

通过上述硬件架构,我们可以低资源消耗、短关键路径地完成计算

下表为一可行性实施例中本申请示出的一种循环迭代乘加运算的硬件架构的技术效果:

表1本申请所示方法实施例综合和布局布线的面积和时序结果

该实施例采用vivado设计套件2018.2版本在Xilinx Virtex-7xc7vx690tffg1157-3的集成电路板上对本申请示出的硬件架构进行了综合,取R的位宽为w=63,n=12。结果如上表所示,结果A的位宽为756bit,所消耗的数字信号处理器DSP、查找表LUT、触发器的资源都是比较少的,仅仅等效于746Slices(FPGA中的基本计数单元),且时钟频率能够达到200兆赫兹,由于本申请示出的硬件架构面积小、频率高,且计算量较大,完成这个计算需要132个时钟周期。

同时,为了明确本申请示出的硬件架构具有较优的技术效果,与其他计算

该硬件架构技术效果为:

表2其他硬件架构综合和布局布线的面积和时序结果

由表1和表2比较可知,本申请示出的技术方案能够占用更少面积,达到更高频率,较于其他硬件架构计算公式

本发明的关键点在于针对公式

应当理解,本申请中说明书和权利要求书及上述附图中的术语“第一”、“第二”、“第三”等是用于区别类似的对象,而不必用于描述特定的顺序或先后次序。应该理解这样使用的数据在适当情况下可以互换,例如能够根据本申请实施例图示或描述中给出那些以外的顺序实施。

此外,术语“包括”和“具有”以及他们的任何变形,意图在于覆盖但不排他的包含,例如,包含了一系列环节不必限于清楚列出的那些环节,而是可包括没有清楚地列出的或对于这些技术常规使用的其他环节。

最后应说明的是:以上各实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述各实施例对本申请进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例技术方案的范围。

- 一种循环迭代乘加运算的硬件架构及方法

- 一种基于脉动阵列硬件架构的深度学习卷积运算实现方法