数据块处理方法、装置、设备及存储介质

文献发布时间:2023-06-19 10:08:35

技术领域

本申请涉及计算机技术领域,尤其涉及一种数据块方法、装置、设备及存储介质。

背景技术

随着计算机技术的不断发展,人们在工作和生活中会产生大量的数据,通常情况下会将这些大量的数据存储到存储系统中。但是,存储系统中可能会存在冗余的数据,因此,需要对重复的数据进行去重即删除重复数据。

相关技术中的重复数据删除过程通常是将数据文件分割为多个数据块。进一步计算多个数据块中每个数据块的指纹信息,并将每个数据块的指纹信息作为每个数据块的关键字进行哈希查找,从而确定该数据块是否为重复数据块。

但是,在大量数据存储的情况下,针对数据块的索引效果较低,从而限制了去重技术在大容量存储系统中的应用。

发明内容

本申请实施例提供一种数据块处理方法、装置、设备及存储介质,以解决相关技术存在的问题,技术方案如下:

第一方面,本申请实施例提供了一种数据块处理方法,包括:

根据待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块;

根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块;

根据该目标物理地址对该目标数据块进行处理。

在一种实施方式中,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括:

在该目标数据块为非重复数据块的情况下,将该目标逻辑地址在该位图信息中对应的标志位设置为该非重复数据块对应的第一标识;

根据该目标存储单元对应的非重复数据块对应的物理地址的起始位置和该位图信息中该第一标识的个数,确定该目标逻辑地址对应的目标物理地址。

在一种实施方式中,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括:

在该目标存储单元在内存中的情况下,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

在一种实施方式中,该方法还包括:

在该目标存储单元不在内存中的情况下,确定该内存中已有的存储单元的数量是否大于或等于预设阈值;

在该内存中已有的存储单元的数量大于或等于预设阈值的情况下,删除该内存中在预设时间内未被访问过的存储单元。

在一种实施方式中,该方法还包括:

在该内存中已有的存储单元的数量小于预设阈值的情况下,从第一预设存储区中获取该目标存储单元;

将该目标存储单元读入到该内存中。

在一种实施方式中,将该目标存储单元读入到该内存中之后,该方法还包括:

确定该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址;

在该目标逻辑地址为该目标存储单元对应的多个逻辑地址中的首个逻辑地址的情况下,更新已用的物理地址,得到更新后的已用物理地址;

将该已用物理地址作为该目标存储单元包括的第一物理地址起始位置。

在一种实施方式中,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括:

在该目标数据块为重复数据块的情况下,确定该目标逻辑地址在该位图信息中对应的标志位是否为该重复数据块对应的第二标识;

在该目标逻辑地址在该位图信息中对应的标志位是该第二标识的情况下,从第二预设存储区中查询该目标逻辑地址对应的该目标物理地址。

在一种实施方式中,该目标存储单元还包括:第一物理地址起始位置和物理地址数目;该方法还包括:

在该目标逻辑地址在该位图信息中对应的标志位不是该第二标识的情况下,根据该位图信息、该目标存储单元对应的第一逻辑地址起始位置、该第一物理地址起始位置和该物理地址数目,确定多个三元组;

从该多个三元组中确定该目标逻辑地址对应的目标三元组,该目标三元组包括第二逻辑地址起始位置和第二物理地址起始位置;

根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址。

在一种实施方式中,根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址之后,该方法还包括:

将该目标逻辑地址在该位图信息中对应的标志位设置为该第二标识;

将该目标逻辑地址和该目标逻辑地址对应的该目标物理地址存储到第二预设存储区中。

第二方面,本申请实施例提供了一种数据块处理装置,该装置包括:

确定模块,用于根据待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块;根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块;

处理模块,用于根据该目标物理地址对该目标数据块进行处理。

在一种实施方式中,该确定模块具体用于:

在该目标数据块为非重复数据块的情况下,将该目标逻辑地址在该位图信息中对应的标志位设置为该非重复数据块对应的第一标识;

根据该目标存储单元对应的非重复数据块对应的物理地址的起始位置和该位图信息中该第一标识的个数,确定该目标逻辑地址对应的目标物理地址。

在一种实施方式中,该确定模块具体用于:在该目标存储单元在内存中的情况下,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

在一种实施方式中,该确定模块还用于:在该目标存储单元不在内存中的情况下,确定该内存中已有的存储单元的数量是否大于或等于预设阈值;

该装置还包括:删除模块,用于在该内存中已有的存储单元的数量大于或等于预设阈值的情况下,删除该内存中在预设时间内未被访问过的存储单元。

在一种实施方式中,该装置还包括:获取模块和读入模块;

该获取模块用于在该内存中已有的存储单元的数量小于预设阈值的情况下,从第一预设存储区中获取该目标存储单元;

该读入模块用于将该目标存储单元读入到该内存中。

在一种实施方式中,该确定模块还用于:确定该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址;

该装置还包括:更新模块,用于在该目标逻辑地址为该目标存储单元对应的多个逻辑地址中的首个逻辑地址的情况下,更新已用的物理地址,得到更新后的已用物理地址;

该处理模块还用于:将该已用物理地址作为该目标存储单元包括的第一物理地址起始位置。

在一种实施方式中,该确定模块具体用于:

在该目标数据块为重复数据块的情况下,确定该目标逻辑地址在该位图信息中对应的标志位是否为该重复数据块对应的第二标识;

该装置还包括:查询模块,用于在该目标逻辑地址在该位图信息中对应的标志位是该第二标识的情况下,从第二预设存储区中查询该目标逻辑地址对应的该目标物理地址。

在一种实施方式中,该目标存储单元还包括:第一物理地址起始位置和物理地址数目;

该确定模块还用于:在该目标逻辑地址在该位图信息中对应的标志位不是该第二标识的情况下,根据该位图信息、该目标存储单元对应的第一逻辑地址起始位置、该第一物理地址起始位置和该物理地址数目,确定多个三元组;

从该多个三元组中确定该目标逻辑地址对应的目标三元组,该目标三元组包括第二逻辑地址起始位置和第二物理地址起始位置;

根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址。

在一种实施方式中,该装置还包括:设置模块和存储模块;

该设置模块用于将该目标逻辑地址在该位图信息中对应的标志位设置为该第二标识;

该存储模块用于将该目标逻辑地址和该目标逻辑地址对应的该目标物理地址存储到第二预设存储区中。

第三方面,本申请实施例提供了一种数据块处理设备,该设备包括:存储器和处理器。其中,该存储器和该处理器通过内部连接通路互相通信,该存储器用于存储指令,该处理器用于执行该存储器存储的指令,并且当该处理器执行该存储器存储的指令时,使得该处理器执行上述各方面任一种实施方式中的方法。

第四方面,本申请实施例提供了一种计算机可读存储介质,计算机可读存储介质存储计算机程序,当计算机程序在计算机上运行时,上述各方面任一种实施方式中的方法被执行。

上述技术方案中的优点或有益效果至少包括:通过待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块。进一步,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块,并根据该目标物理地址对该目标数据块进行处理。由于位图信息占用的存储空间较小,因此根据位图信息即可快速确定出该目标数据块的目标物理地址。从而在大量数据存储的情况下,可以有效提高对目标数据块的索引效率,从而促进了去重技术在大容量存储系统中的应用。

上述概述仅仅是为了说明书的目的,并不意图以任何方式进行限制。除上述描述的示意性的方面、实施方式和特征之外,通过参考附图和以下的详细描述,本申请进一步的方面、实施方式和特征将会是容易明白的。

附图说明

在附图中,除非另外规定,否则贯穿多个附图相同的附图标记表示相同或相似的部件或元素。这些附图不一定是按照比例绘制的。应该理解,这些附图仅描绘了根据本申请公开的一些实施方式,而不应将其视为是对本申请范围的限制。

图1为本申请一实施例的数据块检索装置的结构示意图;

图2为本申请一实施例的逻辑空间的示意图;

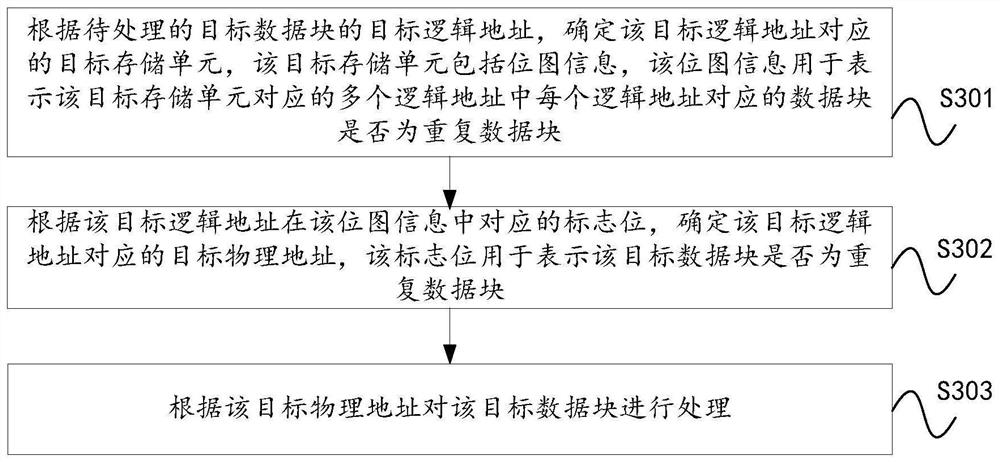

图3为本申请一实施例的数据块处理方法的流程图;

图4为本申请另一实施例的应用场景的示意图;

图5为本申请另一实施例的数据块处理方法的流程图;

图6为本申请另一实施例的数据块处理方法的流程图;

图7为本申请另一实施例的数据块处理方法的流程图;

图8为本申请另一实施例的数据块处理方法的流程图;

图9为本申请另一实施例的数据块处理方法的流程图;

图10为本申请另一实施例的数据块处理方法的流程图;

图11为本申请另一实施例的数据块处理方法的流程图;

图12为本申请另一实施例的数据块处理方法的流程图;

图13为本申请一实施例的数据块处理装置的示意图;

图14为本申请一实施例的数据块处理设备的示意图。

具体实施方式

在下文中,仅简单地描述了某些示例性实施例。正如本领域技术人员可认识到的那样,在不脱离本申请的精神或范围的情况下,可通过各种不同方式修改所描述的实施例。因此,附图和描述被认为本质上是示例性的而非限制性的。

随着计算机技术的不断发展,人们在工作和生活中会产生大量的数据,通常情况下会将这些大量的数据存储到存储系统中。但是,存储系统中可能会存在冗余的数据,因此,需要对重复的数据进行去重即删除重复数据。

例如,在一次写入,多次读取(Write Once Read Many,WORM)技术中涉及到“法规遵从”的概念。例如,在一些国家,新出台的政府法规加上不断增长的数据存储需求,使得企业更加迫切地需要保证他们的业务信息和记录被准确而有效地存档。相关法规的制定也已经影响并控制了公司行为,电子文档则成为法规制约的焦点所在。法规遵从的概念因此应运而生。WORM技术最大的特点,正是在于对数据存储法规遵从的应对。

由于通过WORM技术存储在介质中的数据,将不会因各种意外而丢失或被修改,从而保证了企业对一些重要的业务数据长期存储的需求。另,由于WORM技术的数据多用于归档,所以在WORM存储系统中常常伴随着重复删除技术的应用。

重复数据删除(De-duplication)可以简称为去重,是一种目前主流且非常热门的存储技术,可对存储容量进行有效优化。具体的,通过删除数据集中重复的数据,只保留其中一份,从而消除冗余数据。去重技术可以在很大程度上减少对物理存储空间的需求,从而满足日益增长的数据存储需求。因此,去重技术可以带来诸多实际的利益,例如,可以包括如下几方面的利益:

1)满足投资回报率(Return On Investment,ROI)或总持有成本(Total Cost ofOwnership,TCO)的需求。

2)可以有效控制数据的急剧增长。

3)增加有效存储空间,提高存储效率。

4)节省存储总成本和管理成本。

5)节省数据传输的网络带宽。

6)节省空间、电力供应、冷却等运维成本。

去重(Dedupe)技术目前大量应用于数据备份与归档系统中。由于对数据进行多次备份后,存在大量重复数据,因此可以通过去重技术进行数据去重。事实上,去重技术可以用于很多场合,例如,可以应用于在线数据、近线数据、离线数据等存储系统中。另外,去重技术还可以在文件系统、卷管理器、网络附属存储(Network Attached Storage,NAS)、存储区域网络(Storage Area Networks,SAN)中实施。此外,去重技术还可以用于数据容灾、数据传输与同步,作为一种数据压缩技术用于数据打包。去重技术可以帮助众多应用降低数据存储量、节省网络带宽、提高存储效率、减小备份窗口、节省成本等。

去重技术的衡量维度可以包括重复数据删除率(deduplication ratios)和性能。去重技术的性能取决于具体实现技术,而重复数据删除率可以由数据自身的特征和应用模式所决定,影响因素具体如下表1所示。目前各存储厂商公布的重复数据删除率从20:1到500:1不等。

表1

具体的,去重技术的实现要点可以包括如下几个方面:

1)对何种数据进行去重或消重。

例如,对时间数据或空间数据进行去重或消重,对全局数据或局部数据进行去重或消重。对何种数据进行去重或消重可以直接决定去重的实现技术和数据消重率即重复数据删除率。随时间变化的数据,如周期性的备份、归档数据,比空间数据具有更高的消重率,去重技术在备份归档领域中被广泛应用。另外,由于全局数据的重复率比局部数据的重复率高,因此,全局数据可以获得更高的数据消重率。

2)何时进行去重或消重。

数据消重时机分为如下几种情形:在线消重和离线消重。采用在线消重模式的情况下,数据写入存储系统的同时执行数据消重。因此,在线消重模式实际传输或写入的数据量较少,适合通过局域网(Local Area Network,LAN)或广域网(Wide Area Network,WAN)进行数据处理的存储系统,如网络备份归档、异地容灾系统等。由于在线消重模式需要实时进行文件切分、数据指纹计算、哈希(Hash)查找,因此,对系统资料消耗较大。离线消重模式可以先将数据写入存储系统,然后利用适当的时间再进行消重处理。离线消重模式与在线消重模式刚好相反,离线消重模式对系统资料消耗较少,但写入了包含重复的数据,需要更多的额外存储空间来预先存储消重前数据。因此,离线消重模式适合于直连式存储(Direct-Attached Storage,DAS)和存储区域网络(Storage Area Networks,SAN)的存储架构,数据传输不占用网络带宽。另外,离线消重模式需要保证有足够的时间窗口来进行数据去重操作。因此,在何时进行去重或消重,要根据实际存储应用场景来确定。

3)在何处进行去重或消重。

具体的,数据消重可以在源端(Source)或者目标端(Target)进行。在源端进行数据去重或消重的情况下,源端传输的数据是已经消重后的数据,因此,能够节省网络带宽,但会占用大量源端系统资源。在目标端进行数据去重或消重的情况下,由于数据在传输到目标端后再进行消重,因此不会占用源端系统资源,但是会占用大量网络带宽。在目标端进行数据去重或消重的优势在于对应用程序透明,并具有良好的互操作性,不需要使用专门的应用程序接口(Application Program Interface,API),现有应用软件不用作任何修改即可直接应用。

4)如何进行去重或消重。

例如,重复数据删除技术包括诸多技术实现细节,例如包括文件如何进行切分、数据块指纹如何计算、如何进行数据块检索、采用相同数据检测还是采用相似数据检测和差异编码技术、数据内容是否可以感知、是否需要对内容进行解析等。这些实现细节与去重或消重的具体实现息息相关。本申请主要针对相同数据检测技术,基于二进制文件进行消重处理,具有更广泛的适用性。

存储系统的重复数据删除过程通常是将数据文件或物理文件分割为多个数据块,进一步计算多个数据块中每个数据块的指纹信息,并将每个数据块的指纹信息作为每个数据块的关键字进行哈希查找。若匹配到相同的指纹信息,则表示该数据块为重复数据块,在这种情况下,可以仅存储该数据块的索引号。若未匹配到相同的指纹信息,则表示该数据块不是重复数据块即该数据块是一个新的唯一的数据块,在这种情况下,可以对该数据块进行存储,并创建与该数据块相关的元信息或元数据,例如,该数据块的指纹信息、存储位置等。如此,一个数据文件或物理文件在存储系统中对应一个逻辑表示,该逻辑表示由该数据文件或物理文件中的多个数据块分别对应的元信息或元数据构成。在对该数据文件或物理文件进行读取的情况下,可以先读取该逻辑表示,进一步根据该逻辑表示中的元信息或元数据从存储系统中读取相应的数据块,并将相应的数据块构成数据文件或物理文件的副本。从上述过程可以看出,去重的关键技术主要包括文件数据块切分、数据块指纹信息的计算、以及数据块检索。下面分别对文件数据块切分、数据块指纹信息的计算、以及数据块检索进行介绍。

1)文件数据块切分

具体的,按照去重的粒度可以分为文件级去重和数据块级去重。文件级的去重技术也称为单一实例存储(Single Instance Store,SIS),数据块级的重复数据删除其消重粒度更小,可以达到4-24KB之间。显然,数据块级的去重可以提供更高的数据消重率,因此,目前主流的去重技术是数据块级的去重。数据块的切分方法主要包括如下几种,例如,定长切分(fixed-size partition)、基于内容可变长度分块(content-defined chunking,CDC)切分和滑动块(sliding block)切分。其中,定长分块算法采用预先定义好的块大小对文件进行切分,并计算切分后形成的数据块的弱校验值和消息摘要算法第五版(MessageDigest Algorithm,MD5)强校验值。弱校验值主要是为了提升差异编码的性能,先计算弱校验值并进行哈希查找,如果发现有相同的弱校验值,则计算MD5强校验值并作进一步哈希查找。由于弱校验值的计算量比MD5强校验值的计算量小很多,因此,可以有效提高编码性能。定长分块算法的优点是简单、性能高。但是,定长分块算法对数据插入和删除非常敏感,因此,计算效率较低,不能根据内容变化作调整和优化。

CDC算法是一种变长分块算法,它应用数据指纹,例如拉宾(Rabin)指纹将文件分割成长度大小不等的分块。与定长分块算法不同,CDC算法可以基于文件内容进行数据块切分,因此,数据块大小是可变化的。CDC算法执行过程中,具体使用一个固定大小,例如48字节的滑动窗口对文件数据计算数据指纹。如果指纹满足某个条件,例如将指纹的值模特定的整数等于预先设定的数的情况下,则将窗口位置作为分块的边界。但是,CDC算法可能会出现病态现象,例如,在指纹不满足预设条件的情况下,分块的边界无法确定,从而导致数据块过大。实践中可以对数据块的大小进行限定,例如,设定数据块大小的上下限,从而解决数据块过大的问题。另外,CDC算法对文件内容变化并不敏感,例如,插入或删除数据只会影响到较少的数据块,其余数据块不受影响。此外,CDC算法也是有缺陷的,例如,数据块大小的确定比较困难,若数据块粒度太细则开销太大,若数据块粒度过粗则去重效果不佳。因此,如何在两者之间权衡折衷是一个难点。

滑动块(sliding block)算法结合了定长切分和CDC切分的优点,例如,分块大小固定。滑动块算法可以对定长数据块先计算弱校验值,如果匹配则再计算MD5强校验值,两者都匹配则认为是一个数据块边界。该数据块前面的数据碎片也是一个数据块,它是不定长的。如果滑动窗口移过一个块大小的距离仍无法匹配,则也认定为一个数据块边界。滑动块算法对插入和删除问题处理效率较高,并且能够检测到比CDC更多的冗余数据,它的不足是容易产生数据碎片。

2)数据块指纹计算

数据块指纹是数据块的本质特征。在理想状态下,每个数据块具有唯一的数据块指纹,即不同的数据块具有不同的数据块指纹。数据块本身往往较大,因此,数据块指纹的目标是期望以较小的数据表示,例如16、32、64、128字节来区别不同数据块。数据块指纹通常是对数据块内容进行相关数学运算后获得的,例如,通过MD5、安全哈希算法(SecureHash Algorithm,SHA)1、SHA-256、SHA-512、单项散列函数(One-Way hash function)、拉宾哈希(Rabin Hash)等哈希函数计算数据块指纹。另外,还有许多字符串哈希函数也可以用来计算数据块指纹。但是,哈希函数可能会存在碰撞问题,即不同数据块可能会产生相同的数据块指纹。相对来说,MD5、SHA系列等哈希函数具有较低的碰撞概率,因此,通常可作为指纹的计算方法。其中,MD5和SHA1是128位的,SHA-X(X表示位数)具有更低的碰撞发生概率,但同时计算量也会大大增加。实际应用中,需要在性能和数据安全性方面作权衡。另外,还可以同时使用多种哈希算法来计算数据块指纹。

3)数据块检索

对于大存储容量的去重系统来说,数据块数量非常庞大,尤其是在数据块粒度较细的情况下。因此,在这样一个大的指纹库中检索,性能会成为瓶颈。具体的检索方法可以有多种,例如,动态数组、数据库、红黑(RB)树、平衡二叉树(B-tree)、B+树、B*树、哈希表(Hash Table)等。其中,基于哈希表实现的哈希查找或哈希索引(Hash Index),由于具有O(1)的查找性能被广泛采用。因此,去重技术中也可以采用哈希查找或哈希索引。由于哈希表在内存中,因此,哈希查找或哈希索引会消耗大量内存资源,在进行去重前需要对内存需求作合理规划。例如,可以根据数据块指纹长度、数据块数量等估算出内存需求量。其中,数据块数量可以根据存储容量和平均数据块大小估算得出。

在一些情况下,哈希表也可以记为散列表,是根据关键码值(Key value)而直接进行访问的数据结构。通过映射函数可以将关键码值映射到哈希表中的一个位置来访问记录,以加快查找的速度。其中,映射函数也可以叫做散列函数,存放记录的数组叫做散列表。散列表的查找过程基本上和构建散列表的过程相同,一些关键码可通过散列函数转换后得到的地址直接找到,另一些关键码通过散列函数得到的地址可能会产生冲突,需要按照冲突处理方法进行查找。

但是,在大量数据存储的情况下,针对数据块的索引效果较低,从而限制了去重技术在大容量存储系统中的应用。为了解决该问题,本申请实施例提供了一种数据块处理方法。下面结合具体的实施例对本申请实施例提供的一种数据块处理方法进行详细介绍。该方法可以适用于图1所示的数据块检索装置。如图1所示,该数据块检索装置包括:非重复索引模块、重复属性管理模块、重复索引模块、内存交换单元读写器和逻辑空间模块。其中,逻辑空间模块用于隔离该数据块检索装置和物理存储介质,并且该逻辑空间模块还可以为该数据块检索装置提供连续可读写的逻辑空间。该逻辑空间可以是用于存储哈希表或哈希索引的一段连续的存储空间。该存储空间可以是物理存储介质中的存储空间。该物理存储介质包括但不限于固态硬盘(Solid State Disk,SSD)、硬盘驱动器(Hard Disk Drive,HDD)、磁盘介质、外部存储等。

该逻辑空间的示意图如图2所示,具体的,该逻辑空间包括一个超级块、一个或多个逻辑映射区、一个或多个重复块索引区。图2所示的逻辑空间以一个超级块、一个逻辑映射区和一个重复块索引区为例进行示意性说明。下面对图2中的各个名词进行解释。

内存交换单元可以是内存与物理存储介质之间进行一次交互的最小单元,该最小单元可以是1个扇区,或者可以更大。例如,如上所述的逻辑空间在物理存储介质中,内存可以从该物理存储介质中读取一个内存交换单元。

超级块是用于描述整个逻辑空间组成的内存交换单元,超级块包括4个重要组成部分,例如,物理空间大小、已用物理空间大小、逻辑映射区数组、重复块索引区数组。其中,物理空间大小用于描述如图1所示的数据块检索装置所能使用的物理地址个数。已用物理空间大小用于描述该数据块检索装置已经分配使用的物理地址个数,已用物理空间大小是一个变量。逻辑映射区数组用于描述逻辑空间内包含的多个“逻辑映射区”的起始位置和长度。重复块索引区数组用于描述逻辑空间内包含的多个“重复块索引区”的起始位置和长度。

逻辑映射区用于保存记录所有非重复数据块的逻辑地址与物理地址的索引关系,以及记录每个逻辑地址对应的数据块是否为重复数据块。逻辑映射区由一个或多个“非重复索引块”组成,每个“非重复索引块”包括固定个数的逻辑地址。因此,可以根据逻辑地址直接推算出该逻辑地址所对应的“非重复索引块”。

数据块的逻辑地址具体可以是数据块检索装置的使用者向该数据块检索装置发送数据块的情况下使用的数据块的序号,数据块的逻辑地址是该数据块检索装置提供索引功能查找使用的主键。

数据块的物理地址具体可以是该数据块检索装置向存储有数据块的存储系统发送数据块的情况下使用的数据块的序号,数据块的物理地址是该数据块检索装置提供索引功能要查找的内容。另外,数据块的物理地址可以是该数据块在该存储系统中的存储地址。

重复块索引区用于保存所有内容重复的数据块的逻辑地址与物理地址的索引关系,使用的组织结构是B+Tree。重复块索引区的组成单元也可以是内存交换单元。

非重复索引块代表一段逻辑地址,用于描述每个逻辑地址对应的数据块是否为重复数据块,并能描述非重复数据块的逻辑地址与物理地址的对应关系。非重复索引块由三部分组成,例如,物理地址起始位置、物理地址数目、重复块位图。

重复块位图用于描述一个“非重复索引块”中所有逻辑地址对应的数据块是否为重复数据块。重复块位图包括多个比特(bit)位。一个比特位对应一个逻辑地址,一个逻辑地址对应一个数据块。在比特位为0的情况下,表示该比特位对应的数据块为重复数据块。在比特位为1的情况下,表示该比特位对应的数据块为非重复数据块。

物理地址起始位置代表一个“非重复索引块”中所有非重复数据块对应的物理地址的起始位置。

物理地址数目代表一个“非重复索引块”对应的所有非重复数据块对应的物理地址总数,与“物理地址起始位置”共同描述一个连续的物理空间,这个物理空间和该“非重复索引块”内重复块位图对应bit位为1的逻辑地址一一对应。

下面结合图2对图1所述的几个模块进行描述。

非重复索引模块用于对图2中的非重复索引块进行处理,主要功能是修改重复块位图。

重复属性管理模块用于确定逻辑地址对应的数据块是否为重复数据块,并通过直接操作重复块位图来实现。

重复索引模块用于通过B+树(B+Tree)的调度方式对图2中的重复块索引区进行索引。

内存交换单元读写器包括各个区域的寻址方法,负责向上层三个模块提供读写内存交换单元的功能。

逻辑空间模块用于隔离该数据块检索装置和物理存储介质,并且该逻辑空间模块还可以为该数据块检索装置提供连续可读写的逻辑空间。

图3示出根据本申请一实施例的数据块处理方法的流程图。如图3所示,该方法可以包括:

S301、根据待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块。

例如,本实施例可以适用于图4所示的应用场景。该应用场景中包括预设设备41、数据块检索装置42和存储系统43。其中,预设设备41具体可以是用户设备。数据块检索装置42的结构具体如上所述,此处不再赘述。存储系统43用于存储数据,例如,数据块。

在预设设备41对目标数据块进行处理的情况下,可以向数据块检索装置42发送针对该目标数据块的处理指令,该处理指令可以是写指令或读指令。具体的,预设设备41可以将该目标数据块的目标逻辑地址发送给数据块检索装置42。数据块检索装置42可以根据该目标数据块的目标逻辑地址确定该目标逻辑地址对应的内存交换单元。该目标逻辑地址对应的内存交换单元可以记为目标存储单元。例如图2所示的逻辑映射区包括10个内存交换单元,每个内存交换单元对应10个逻辑地址。在逻辑地址从1开始计数的情况下,若该目标逻辑地址为99,则可以确定该目标逻辑地址对应的内存交换单元为该10个内存交换单元中的第10个内存交换单元,并且该目标逻辑地址对应于该第10个内存交换单元中重复块位图的第9个比特。该第10个内存交换单元为该目标逻辑地址对应的目标存储单元。该目标存储单元包括位图信息,例如,该目标存储单元中的重复块位图。该重复块位图包括10个比特,该10个比特中的每个比特对应一个逻辑地址,并且每个比特用于表示每个逻辑地址对应的数据块是否为重复数据块。

S302、根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块。

例如,该目标逻辑地址对应于该第10个内存交换单元中重复块位图的第9个比特,该第9个比特为该目标逻辑地址在该位图信息中对应的标志位。进一步,数据块检索装置42根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

S303、根据该目标物理地址对该目标数据块进行处理。

例如,在数据块检索装置42确定出该目标逻辑地址对应的目标物理地址的情况下,可以根据该目标物理地址对该目标数据块进行处理。例如,该目标物理地址可以是该目标数据块在该存储系统中的存储地址。数据块检索装置42可以从该存储系统的该目标物理地址中读取该目标数据块。或者,数据块检索装置42可以在该存储系统的该目标物理地址中写入该目标数据块。或者,数据块检索装置42还可以将该目标物理地址发送给预设设备41,由预设设备41从该存储系统的该目标物理地址中读取该目标数据块,或者在该存储系统的该目标物理地址中写入该目标数据块。

本申请实施例通过待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块。进一步,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块,并根据该目标物理地址对该目标数据块进行处理。由于位图信息占用的存储空间较小,因此根据位图信息即可快速确定出该目标数据块的目标物理地址。从而在大量数据存储的情况下,可以有效提高对目标数据块的索引效率,从而促进了去重技术在大容量存储系统中的应用。

在上述实施例的基础上,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括如图5所示的如下步骤:

S501、在该目标数据块为非重复数据块的情况下,将该目标逻辑地址在该位图信息中对应的标志位设置为该非重复数据块对应的第一标识。

例如,目标数据块对应于逻辑映射区中的第10个内存交换单元,该第10个内存交换单元中的位图信息即重复块位图包括10个比特,该目标数据块的目标逻辑地址对应该10个比特中的第9个比特,即该10个比特中的第9个比特为该目标逻辑地址在该位图信息中对应的标志位。在该目标数据块为非重复数据块的情况下,数据块检索装置42可以将该目标逻辑地址在该位图信息中对应的标志位设置为非重复数据块对应的第一标识,例如1。

S502、根据该目标存储单元对应的非重复数据块对应的物理地址的起始位置和该位图信息中该第一标识的个数,确定该目标逻辑地址对应的目标物理地址。

由于该目标存储单元即逻辑映射区中的第10个内存交换单元包括如图2所示的物理地址起始位置、物理地址数目和重复块位图,并且该物理地址起始位置表示该第10个内存交换单元对应的非重复数据块对应的物理地址的起始位置。另外,该第10个内存交换单元中的重复块位图中比特位即标志位为1的个数是该第10个内存交换单元对应的非重复数据块的个数,并且该第10个内存交换单元对应的非重复数据块的物理地址是连续的。因此,根据该第10个内存交换单元中的该物理地址起始位置和该第10个内存交换单元中的重复块位图中比特位为1的个数即可确定出该目标逻辑地址对应的目标物理地址。

可选的,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括:在该目标存储单元在内存中的情况下,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

例如,在目标数据块对应于逻辑映射区中的第10个内存交换单元的情况下,可进一步确定该第10个内存交换单元是否在内存中,该内存可以位于图1所示的数据块检索装置中。在该第10个内存交换单元在该内存的情况下,数据块检索装置42可以根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

可选的,该方法还包括:在该目标存储单元不在内存中的情况下,确定该内存中已有的存储单元的数量是否大于或等于预设阈值;在该内存中已有的存储单元的数量大于或等于预设阈值的情况下,删除该内存中在预设时间内未被访问过的存储单元。

例如,在第10个内存交换单元不在该内存的情况下,数据块检索装置42可以确定该内存中已有的存储单元的数量是否大于或等于预设阈值,即判断该内存中已有的存储单元的数量是否已经超过最大限制。在超过最大限制的情况下,数据块检索装置42可以进一步删除该内存中在预设时间内未被访问过的存储单元,该存储单元可以是内存交换单元。例如,数据块检索装置42可以通过最近最少使用(Least Recently Used,LRU)算法淘汰该内存中最早未被访问的内存交换单元。进一步,数据块检索装置42可以从逻辑映射区中读取第10个内存交换单元,并将该第10个内存交换单元读入到该内存中。

可选的,该方法还包括:在该内存中已有的存储单元的数量小于预设阈值的情况下,从第一预设存储区中获取该目标存储单元;将该目标存储单元读入到该内存中。

例如,在该内存中已有的存储单元的数量小于预设阈值,即该内存中已有的存储单元的数量未超过最大限制的情况下,数据块检索装置42可以从逻辑映射区中读取第10个内存交换单元,并将该第10个内存交换单元读入到该内存中。其中,如图2所示的逻辑映射区可记为第一预设存储区。

可选的,将该目标存储单元读入到该内存中之后,该方法还包括:确定该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址;在该目标逻辑地址为该目标存储单元对应的多个逻辑地址中的首个逻辑地址的情况下,更新已用的物理地址,得到更新后的已用物理地址;将该已用物理地址作为该目标存储单元包括的第一物理地址起始位置。

例如,在数据块检索装置42从逻辑映射区中读取第10个内存交换单元,并将该第10个内存交换单元读入到该内存中的情况下,可以进一步判断该目标数据块对应的目标逻辑地址是否为该第10个内存交换单元对应的多个逻辑地址中的首个逻辑地址。在该目标数据块对应的目标逻辑地址为该多个逻辑地址中的首个逻辑地址的情况下,数据块检索装置42可以更新已用的物理地址,例如,将已用的物理地址加1,从而得到更新后的已用物理地址。进一步,数据块检索装置42可以将该更新后的已用物理地址作为该目标存储单元中包括的物理地址起始位置。此处可以将该目标存储单元中包括的物理地址起始位置记为第一物理地址起始位置。

本申请实施例通过在该目标数据块为非重复数据块的情况下,将该目标逻辑地址在该位图信息中对应的标志位设置为该非重复数据块对应的第一标识,并根据该目标存储单元对应的非重复数据块对应的物理地址的起始位置和该位图信息中该第一标识的个数,确定该目标逻辑地址对应的目标物理地址。由于位图信息占用的存储空间较小,因此根据位图信息即可快速确定出该目标数据块的目标物理地址。从而在大量数据存储的情况下,可以有效提高对目标数据块的索引效率,从而促进了去重技术在大容量存储系统中的应用。另外,通过逻辑映射区和重复块索引区可以对非重复数据块和重复数据块进行分区索引,进一步提高了对数据块的索引效率。

下面结合一个具体的实施例对确定非重复数据块的物理地址的过程进行介绍。如图6所示,该过程包括如下几个步骤:

S601、开始。

S602、判断已用物理空间大小是否大于或等于物理空间。若是,则执行S611,否则执行S603。

S603、根据目标逻辑地址定位目标存储单元。

例如,目标存储单元可以是该目标逻辑地址对应的内存交互单元。每个内存交互单元包含的逻辑地址是固定的,并且每个内存交互单元内重复块位图的比特数是固定的。由于内存交互单元在物理存储介质中按照所含逻辑地址的高低顺序存放。因此,可以根据目标逻辑地址反推出该目标逻辑地址存放于第几个内存交互单元内。

S604、判断该目标存储单元是否在内存中。若是,则执行S605,否则执行S606。

S605、将该目标逻辑地址在位图信息中对应的比特位设置为1,将已用物理空间大小加1,将目标存储单元中物理地址数目加1,保存该目标存储单元,并返回原物理空间大小(即目标物理地址)。

例如,将该目标逻辑地址减去该目标存储单元对应的逻辑地址的起始位置可得到该目标逻辑地址在位图信息中对应的比特位,即该目标逻辑地址对应于该位图信息中的第几个比特位。

S606、判断内存中已有的内存交换单元的数量是否超过最大限制。若是,则执行S607,否则执行S608。

S607、根据LRU算法淘汰内存中最早未被访问的内存交换单元。

其中,最近最少使用(Least Recently Used,LRU)算法可以按照访问时间对内存中已有的内存交互单元进行排序,并保持一定的队列深度,每次淘汰最早未被访问的内存交互单元。

S608、将目标存储单元读入到内存中。

S609、判断该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址。若是,则执行S610,否则执行S605。

S610、将已用的物理地址加1,并作为该目标存储单元中包括的物理地址起始位置。

S611、报错。

S612、结束。

具体的,S601-S612的执行过程和具体原理可以参照上述实施例,此处不再赘述。

另外,S601-S612的执行过程可以记为分配新数据块流程。该分配新数据块流程在数据块内容被判定为首次写入的情况下调用,即数据块为非重复数据块的情况下调用S601-S612。该分配新数据块流程的输入为待写入到存储系统的数据块的逻辑地址。在物理空间足够的情况下,该分配新数据块流程的输出为该数据块的物理地址。在物理空间不足的情况下,流程报错。

在上述实施例的基础上,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,包括如图7所示的如下几个步骤:

S701、在该目标数据块为重复数据块的情况下,确定该目标逻辑地址在该位图信息中对应的标志位是否为该重复数据块对应的第二标识。

例如,该目标数据块的目标逻辑地址对应的目标存储单元为逻辑映射区中的第10个内存交换单元。该第10个内存交换单元中的重复块位图即位图信息包括10个比特。该目标逻辑地址对应该10个比特中的第9个比特,即该第9个比特为该目标逻辑地址在该位图信息中对应的标志位。在该目标数据块为重复数据块的情况下,数据块检索装置42可以确定该目标逻辑地址在该位图信息中对应的标志位是否为重复数据块对应的第二标识,例如0。

S702、在该目标逻辑地址在该位图信息中对应的标志位是该第二标识的情况下,从第二预设存储区中查询该目标逻辑地址对应的该目标物理地址。

例如,在该目标逻辑地址在该位图信息中对应的标志位为0的情况下,数据块检索装置42可以从如图2所示的重复块索引区中查询该目标逻辑地址对应的该目标物理地址。其中,如图2所示的重复块索引区可以记为第二预设存储区。

S703、在该目标逻辑地址在该位图信息中对应的标志位不是该第二标识的情况下,根据该位图信息、该目标存储单元对应的第一逻辑地址起始位置、该第一物理地址起始位置和该物理地址数目,确定多个三元组。

例如,逻辑映射区中的第10个内存交换单元为该目标数据块对应的目标存储单元。该目标存储单元除了包括重复块位图之外,该目标存储单元还包括:第一物理地址起始位置和物理地址数目。该第一物理地址起始位置可以是该目标存储单元例如逻辑映射区中第10个内存交换单元对应的非重复数据块对应的物理地址的起始位置。物理地址数目为该第10个内存交换单元对应的所有非重复数据块对应的物理地址总数。

在该目标逻辑地址在该位图信息中对应的标志位不为0的情况下,数据块检索装置42可以根据该目标存储单元中的位图信息、该目标存储单元对应的第一逻辑地址起始位置、该第一物理地址起始位置和该物理地址数目,确定多个三元组。其中,该目标存储单元对应的第一逻辑地址起始位置可以是该目标存储单元对应的多个逻辑地址的起始位置。每个三元组包括三个变量,该三个变量表示一段连续的逻辑地址与一段连续的物理地址的映射关系。其中,该三个变量中的第一个变量用于表示该段连续的逻辑地址的起始地址,第二个变量用于表示该段连续的物理地址的起始地址,第三个变量表示该段映射区间的长度。

S704、从该多个三元组中确定该目标逻辑地址对应的目标三元组,该目标三元组包括第二逻辑地址起始位置和第二物理地址起始位置。

例如,从多个三元组中确定该目标逻辑地址对应的目标三元组。该目标三元组包括三个变量,此处可以将该目标三元组的第一个变量记为第二逻辑地址起始位置。将该目标三元组的第二个变量记为第二物理地址起始位置。

S705、根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址。

例如,该目标逻辑地址可以记为laddress,该第二逻辑地址起始位置可以记为lstart,该第二物理地址起始位置可以记为pstart。该目标逻辑地址对应的该目标物理地址为laddress-lstart+pstart。

本申请实施例通过在该目标数据块为重复数据块的情况下,确定该目标逻辑地址在该位图信息中对应的标志位是否为该重复数据块对应的第二标识。在该目标逻辑地址在该位图信息中对应的标志位是该第二标识的情况下,从第二预设存储区中查询该目标逻辑地址对应的该目标物理地址。在该目标逻辑地址在该位图信息中对应的标志位不是该第二标识的情况下,确定该目标逻辑地址对应的目标三元组,并根据该目标逻辑地址、该目标三元组中的第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址。从而在大量数据存储的情况下,可以有效提高对目标数据块的索引效率,从而促进了去重技术在大容量存储系统中的应用。另外,充分利用了WORM类型的存储中数据块的逻辑地址和物理地址的映射关系一旦确定就不需要或很少需要对该映射关系进行修改的特性。此外,可以分段保存大容量存储中重复数据块的索引和非重复数据块的索引。

下面结合一个具体的实施例对查找逻辑地址的数据块的流程进行介绍。该过程包括如图8所示的如下几个步骤:

S801、开始。

S802、根据目标逻辑地址定位目标存储单元。

S803、判断该目标存储单元是否在内存中。若是,则执行S807,否则执行S804。

S804、判断内存中已有的内存交换单元的数量是否超过最大限制。若是,则执行S805,否则执行S806。

S805、根据LRU算法淘汰内存中最早未被访问的内存交换单元。

S806、将目标存储单元读入到内存中。

S807、判断目标逻辑地址在位图信息中对应的标志位是否为0。若是,则执行S809,否则执行S808。

S808、确定多个三元组,从该多个三元组中确定该目标逻辑地址对应的目标三元组,根据该目标三元组确定该目标逻辑地址对应的目标物理地址。

S809、从重复块索引区查询该目标逻辑地址对应的目标物理地址。

S810、结束。

具体的,S801-S810的执行过程和具体原理可以参照上述实施例,此处不再赘述。具体的,查找逻辑地址的数据块的流程的输入为目标数据块的目标逻辑地址。该流程的输出为该目标数据块的目标物理地址。

下面结合具体的实施例对S808中的确定多个三元组的过程、以及从该多个三元组中确定该目标逻辑地址对应的目标三元组,根据该目标三元组确定该目标逻辑地址对应的目标物理地址的过程分别进行介绍。其中,确定多个三元组的过程可以记为内部流程1。从该多个三元组中确定该目标逻辑地址对应的目标三元组,根据该目标三元组确定该目标逻辑地址对应的目标物理地址的过程可以记为内部流程2。下面对内部流程1和内部流程2分别进行介绍。具体的,内部流程1包括如图9所示的如下几个步骤:

S901、开始。

S902、令遍历计数器i=0,物理地址的偏移量off=0,记第一逻辑地址起始位置为lstart1,第一物理地址起始位置为pstart1,记物理地址数目为len,记区间映射关系的三元数组为res[][3]。

其中,第一逻辑地址起始位置lstart1可以是如上所述的目标存储单元对应的多个逻辑地址的起始位置。第一物理地址起始位置pstart1可以是如上所述的目标存储单元中包括的物理地址起始位置。物理地址数目len可以是如上所述的目标存储单元中包括的物理地址数目。

区间映射关系的三元数组可以包括多个三元组。每个三元组可以用三个变量表示一段连续的逻辑地址与一段连续的物理地址的映射关系,第一个变量表示这段逻辑地址的起始地址,第二个变量表示该段物理地址的起始地址,第三个变量表示这段映射区间的长度。例如,三元组[0,10,10]表示逻辑地址为0到9的区间对应物理地址10到19的区间。三元组[10,0,10]表示逻辑地址10到19的区间对应物理地址0到9的区间。多个三元组可以构成三元数组,例如,三元组[0,10,10]和三元组[10,0,10]可以构成三元数组[[0,10,10],[10,0,10]]。

S903、在位图信息中连续1的个数不超过len的情况下,将位图信息转换为线段数组,该线段数组记为二维数组a[][2]。

例如,该位图信息可以是如上所述的目标存储单元中的重复块位图。例如,该重复块位图包括10个比特,该10个比特为0101100000。此处可以将重复块位图中连续的1用多个有序的线段来表示,每个线段包括起始位置和长度。例如,0101100000的第0个比特为0,第1个比特为1,第3个比特开始有连续的2个比特为1。因此,0101100000可以表示为[[1,1],[3,2]],[[1,1],[3,2]]可以记为二维数组a[][2]。

S904、判断off是否小于。若是,则执行S905,否则执行S906。

S905、令res[i][0]=a[i][0]+lstart1,令res[i][1]=pstart1+off,令res[i][2]=a[i][1],令off=off+a[i][1],令i=i+1。

S906、返回res[][3]。

S907、结束。

具体的,图9描述了根据目标存储单元中的位图信息、该目标存储单元对应的第一逻辑地址起始位置、该目标存储单元中的第一物理地址起始位置、以及该目标存储单元中的物理地址数目,获取区间映射关系的三元数组的过程。

下面结合具体的实施例对内部流程2进行介绍。具体的,内部流程2包括如图10所示的如下几个步骤:

S1001、开始。

S1002、从该多个三元组中确定目标逻辑地址laddress对应的目标三元组。

由于区间映射关系的三元数组中的每个三元组是按照逻辑地址的起始地址顺序排列的。因此,根据目标逻辑地址laddress,可以确定出该目标逻辑地址laddress对应的三元组,并将该目标逻辑地址laddress对应的三元组记为目标三元组。具体的,在从区间映射关系的三元数组中查找该目标三元组的过程中,可以采用折半查找方法进行查找。

S1003、判断该目标三元组是否存在。若是,则执行S1004,否则执行S1005。

S1004、记该目标三元组中的第二逻辑地址起始位置为lstart2,记该目标三元组中的第二物理起始位置为pstart2。

其中,该目标三元组中的第二逻辑地址起始位置lstart2可以是该目标三元组中的第一个变量。该目标三元组中的第二物理起始位置pstart2可以是该目标三元组中的第二个变量。

S1005、流程报错。

S1006、返回laddress-lstart2+pstart2。

具体的,laddress-lstart2+pstart2为该目标逻辑地址laddress对应的目标物理地址。

S1007、结束。

具体的,图10描述了根据目标逻辑地址和区间映射关系的三元数组,获取目标逻辑地址对应的目标物理地址的流程。

可选的,根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址之后,该方法还包括如图11所示的如下几个步骤:

S1101、将该目标逻辑地址在该位图信息中对应的标志位设置为该第二标识。

例如,在根据目标逻辑地址laddress、第二逻辑地址起始位置lstart2和第二物理地址起始位置pstart2确定出该目标逻辑地址laddress对应的该目标物理地址laddress-lstart2+pstart2的情况下,进一步,可以将该目标逻辑地址laddress在目标存储单元包括的重复块位图中对应的标志位设置为第二标识,例如0。从而表示该目标逻辑地址对应的目标数据块为重复数据块。

S1102、将该目标逻辑地址和该目标逻辑地址对应的该目标物理地址存储到第二预设存储区中。

进一步,可以将该目标逻辑地址和laddress和该目标逻辑地址对应的该目标物理地址laddress-lstart2+pstart2存储到第二预设存储区例如图2所示的重复块索引区中。也就是说,将laddress和laddress-lstart2+pstart2的对应关系存储到重复块索引区中。

本申请实施例通过将该目标逻辑地址在该位图信息中对应的标志位设置为该第二标识,并将该目标逻辑地址和该目标逻辑地址对应的该目标物理地址存储到第二预设存储区中,使得位图信息可以直观的表示出非重复数据块和重复数据块。另外,将重复数据块的目标逻辑地址和目标物理地址存储到第二预设存储区中,可以分段保存大容量存储中重复数据块的索引和非重复数据块的索引,使得大部分情况下的查找性能更好,例如时间复杂度能够达到O(1),并且不受整体存储容量的限制。通过对去重数据块的索引和对非去重数据块的索引区分对待,利用WORM的单次写入的特性,在无去重的情况下,索引的逻辑地址与物理地址对应关系是单调递增的且一一对应,使得可以根据逻辑地址,通过线性计算直接定位描述逻辑地址与物理地址之间的对应关系。另外,在重复的数据块远小于不重复的数据块的情况下,在更大容量的存储系统中,即便重复块索引区采用传统的方式,例如红黑(RB)树、平衡二叉树(B-tree)、B+树、B*树,也不会影响整体的查找性能。

下面结合一个具体的实施例对指定逻辑地址到重复块流程进行介绍。该指定逻辑地址到重复块流程可以在数据块内容被判定为内容重复数据写入的情况下调用。该流程的输入可以是待写入的数据块的逻辑地址和物理地址。对于任意一个逻辑地址,可以选择指定逻辑地址到重复块流程和如上所述的分配新数据块流程中的一个。如图12所示,指定逻辑地址到重复块流程包括如下几个步骤:

S1201、开始。

S1202、根据目标逻辑地址定位目标存储单元。

S1203、判断该目标存储单元是否在内存中。若是,则执行S1204,否则执行S1205。

S1204、将目标逻辑地址在位图信息中对应的比特位设置为0,保存目标存储单元,将目标逻辑地址和目标物理地址保存在重复块索引区中。

具体可以使用B+Tree的方式将目标逻辑地址和目标物理地址保存在重复块索引区中。

S1205、判断内存中已有的内存交换单元的数量是否超过最大限制。若是,则执行S1206,否则执行S1207。

S1206、根据LRU算法淘汰内存中最早未被访问的内存交换单元。

S1207、将目标存储单元读入到内存中。

S1208、判断该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址。若是,则执行S1209,否则执行S1204。

S1209、将已用的物理地址加1,并作为该目标存储单元中包括的物理地址起始位置。

S1210、结束。

具体的,可以将图6所示的流程记为“分配新数据块流程”,将图8所示的流程记为“查找逻辑地址的数据块流程”,将图12所示的流程记为“指定逻辑地址到重复块流程”。在向一个逻辑地址写入数据块的情况下,若该数据块为非重复数据块即该数据块的内容为新值,则调用“分配新数据块流程”获取该数据块的物理地址,并将该数据块写入到该物理地址中。若该数据块为重复数据块,则调用“查找逻辑地址的数据块流程”获取该数据块的物理地址,进一步调用“指定逻辑地址到重复块流程”将该数据块的逻辑地址和物理地址记录到重复块索引区中。在从一个逻辑地址读取数据块的情况下,可以调用“查找逻辑地址的数据块流程”获取该数据块的物理地址,并从该物理地址中读取该数据块。

图13示出根据本申请一实施例的数据块处理装置的结构框图。如图13所示,该装置130可以包括:

确定模块131,用于根据待处理的目标数据块的目标逻辑地址,确定该目标逻辑地址对应的目标存储单元,该目标存储单元包括位图信息,该位图信息用于表示该目标存储单元对应的多个逻辑地址中每个逻辑地址对应的数据块是否为重复数据块;根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址,该标志位用于表示该目标数据块是否为重复数据块;

处理模块132,用于根据该目标物理地址对该目标数据块进行处理。

可选的,确定模块131具体用于:

在该目标数据块为非重复数据块的情况下,将该目标逻辑地址在该位图信息中对应的标志位设置为该非重复数据块对应的第一标识;

根据该目标存储单元对应的非重复数据块对应的物理地址的起始位置和该位图信息中该第一标识的个数,确定该目标逻辑地址对应的目标物理地址。

可选的,确定模块131具体用于:在该目标存储单元在内存中的情况下,根据该目标逻辑地址在该位图信息中对应的标志位,确定该目标逻辑地址对应的目标物理地址。

可选的,确定模块131还用于:在该目标存储单元不在内存中的情况下,确定该内存中已有的存储单元的数量是否大于或等于预设阈值;该装置130还包括:删除模块133,用于在该内存中已有的存储单元的数量大于或等于预设阈值的情况下,删除该内存中在预设时间内未被访问过的存储单元。

可选的,该装置130还包括:获取模块134和读入模块135;获取模块134用于在该内存中已有的存储单元的数量小于预设阈值的情况下,从第一预设存储区中获取该目标存储单元;读入模块135用于将该目标存储单元读入到该内存中。

可选的,确定模块131还用于:确定该目标逻辑地址是否为该目标存储单元对应的多个逻辑地址中的首个逻辑地址;该装置130还包括:更新模块136,用于在该目标逻辑地址为该目标存储单元对应的多个逻辑地址中的首个逻辑地址的情况下,更新已用的物理地址,得到更新后的已用物理地址;处理模块132还用于:将该已用物理地址作为该目标存储单元包括的第一物理地址起始位置。

可选的,确定模块131具体用于:在该目标数据块为重复数据块的情况下,确定该目标逻辑地址在该位图信息中对应的标志位是否为该重复数据块对应的第二标识;该装置130还包括:查询模块137,用于在该目标逻辑地址在该位图信息中对应的标志位是该第二标识的情况下,从第二预设存储区中查询该目标逻辑地址对应的该目标物理地址。

可选的,该目标存储单元还包括:第一物理地址起始位置和物理地址数目;确定模块131还用于:在该目标逻辑地址在该位图信息中对应的标志位不是该第二标识的情况下,根据该位图信息、该目标存储单元对应的第一逻辑地址起始位置、该第一物理地址起始位置和该物理地址数目,确定多个三元组;从该多个三元组中确定该目标逻辑地址对应的目标三元组,该目标三元组包括第二逻辑地址起始位置和第二物理地址起始位置;根据该目标逻辑地址、该第二逻辑地址起始位置和该第二物理地址起始位置,确定该目标逻辑地址对应的该目标物理地址。

可选的,该装置130还包括:设置模块138和存储模块139,设置模块138用于将该目标逻辑地址在该位图信息中对应的标志位设置为该第二标识;存储模块139用于将该目标逻辑地址和该目标逻辑地址对应的该目标物理地址存储到第二预设存储区中。

本申请实施例各装置中的各模块的功能可以参见上述方法中的对应描述,在此不再赘述。

图14示出根据本申请一实施例的数据块处理设备的结构框图。如图14所示,该设备包括:存储器1410和处理器1420,存储器1410内存储有可在处理器1420上运行的计算机程序。处理器1420执行该计算机程序时实现上述实施例中的数据块处理的方法。存储器1410和处理器1420的数量可以为一个或多个。

该应用程序现场还原设备还包括:

通信接口1430,用于与外界设备进行通信,进行数据交互传输。

如果存储器1410、处理器1420和通信接口1430独立实现,则存储器1410、处理器1420和通信接口1430可以通过总线相互连接并完成相互间的通信。该总线可以是工业标准体系结构(Industry Standard Architecture,ISA)总线、外部设备互连(PeripheralComponent Interconnect,PCI)总线或扩展工业标准体系结构(Extended IndustryStandard Architecture,EISA)总线等。该总线可以分为地址总线、数据总线、控制总线等。为便于表示,图14中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

可选的,在具体实现上,如果存储器1410、处理器1420及通信接口1430集成在一块芯片上,则存储器1410、处理器1420及通信接口1430可以通过内部接口完成相互间的通信。

本申请实施例提供了一种计算机可读存储介质,其存储有计算机程序,该程序被处理器执行时实现本申请实施例中提供的方法。

本申请实施例还提供了一种芯片,该芯片包括,包括处理器,用于从存储器中调用并运行存储器中存储的指令,使得安装有芯片的通信设备执行本申请实施例提供的方法。

本申请实施例还提供了一种芯片,包括:输入接口、输出接口、处理器和存储器,输入接口、输出接口、处理器以及存储器之间通过内部连接通路相连,处理器用于执行存储器中的代码,当代码被执行时,处理器用于执行申请实施例提供的方法。

应理解的是,上述处理器可以是中央处理器(Central Processing Unit,CPU),还可以是其他通用处理器、数字信号处理器(digital signal processing,DSP)、专用集成电路(application specific integrated circuit,ASIC)、现场可编程门阵列(fieldprogrammablegate array,FPGA)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者是任何常规的处理器等。值得说明的是,处理器可以是支持进阶精简指令集机器(advanced RISC machines,ARM)架构的处理器。

进一步地,可选的,上述存储器可以包括只读存储器和随机存取存储器,还可以包括非易失性随机存取存储器。该存储器可以是易失性存储器或非易失性存储器,或可包括易失性和非易失性存储器两者。其中,非易失性存储器可以包括只读存储器(read-onlymemory,ROM)、可编程只读存储器(programmable ROM,PROM)、可擦除可编程只读存储器(erasable PROM,EPROM)、电可擦除可编程只读存储器(electrically EPROM,EEPROM)或闪存。易失性存储器可以包括随机存取存储器(random access memory,RAM),其用作外部高速缓存。通过示例性但不是限制性说明,许多形式的RAM可用。例如,静态随机存取存储器(static RAM,SRAM)、动态随机存取存储器(dynamic random access memory,DRAM)、同步动态随机存取存储器(synchronous DRAM,SDRAM)、双倍数据速率同步动态随机存取存储器(double data date SDRAM,DDR SDRAM)、增强型同步动态随机存取存储器(enhancedSDRAM,ESDRAM)、同步连接动态随机存取存储器(synchlink DRAM,SLDRAM)和直接内存总线随机存取存储器(direct rambus RAM,DR RAM)。

在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行计算机程序指令时,全部或部分地产生按照本申请的流程或功能。计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输。

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包括于本申请的至少一个实施例或示例中。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或隐含地包括至少一个该特征。在本申请的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更多个用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分。并且本申请的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能。

在流程图中表示或在此以其他方式描述的逻辑和/或步骤,例如,可以被认为是用于实现逻辑功能的可执行指令的定序列表,可以具体实现在任何计算机可读介质中,以供指令执行系统、装置或设备(如基于计算机的系统、包括处理器的系统或其他可以从指令执行系统、装置或设备取指令并执行指令的系统)使用,或结合这些指令执行系统、装置或设备而使用。

应理解的是,本申请的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。上述实施例方法的全部或部分步骤是可以通过程序来指令相关的硬件完成,该程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

此外,在本申请各个实施例中的各功能单元可以集成在一个处理模块中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。上述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读存储介质中。该存储介质可以是只读存储器,磁盘或光盘等。

以上所述,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到其各种变化或替换,这些都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

- 数据块处理方法、装置、设备及存储介质

- 数据块的处理方法、装置及存储介质