双斜坡型倒装DBR的LED芯片结构及其制作方法

文献发布时间:2023-06-19 11:39:06

技术领域

本发明涉及半导体技术领域,尤其是一种双斜坡型倒装DBR的LED芯片结构及其制作方法。

背景技术

发光二极管(LED)是一种将电能转化为光能的固体发光器件,其中GaN基的LED芯片得到了长足的发展和应用。发光二极管的发光效率主要有两方面因素:器件的内量子效率和外量子效率。由于菲涅尔损失、全反射损失和材料吸收损失的存在,使LED芯片的光提取效率降低。光提取效率是指出射到空气中的光子占电子-空穴对通过辐射复合在芯片有源区产生光子的比例,其主要与LED的几何结构和材料光学特性有关。倒装LED芯片因具有低电压、高亮度、高可靠性、高饱和电流密度等特点,成为下一代LED技术的发展方向。倒装LED芯片在芯片正面增加了一道反射层,通常反射层为金属反射层或者分布布拉格反射镜(DBR)。分布布拉格反射镜的反射率可达到99%以上,它没有金属反射层的吸收问题,又可以通过改变材料的折射率或厚度来调整能隙位置。在DBR层之前通常会镀一层绝缘层(PV)提高DBR的出光,由于蚀刻较快,绝缘层的坡度单一且陡峭,不利于焊盘电极的覆盖,可靠性差。

发明内容

本申请人针对现有技术中存在的DBR之前绝缘层的坡度单一且陡峭、不利于焊盘电极覆盖等缺陷,提供一种双斜坡型倒装DBR的LED芯片结构及其制作方法,能够形成先缓后陡的双斜坡,有利于焊盘电极的覆盖,具有更好的包覆效果,使焊盘电极更加稳定可靠。

本发明所采用的技术方案如下:

一种双斜坡型倒装DBR的LED芯片结构,在芯片衬底上生长LED芯片外延结构,至少包括依次生长的N-GaN层、多量子阱层和P-GaN层,通过刻蚀技术将暴漏区域的N-GaN层刻蚀出来,形成N-GaN台阶,在LED芯片外延结构上设有电流阻挡层和透明导电层,在此基础上设置N、P导电金属层,N、P导电金属层图形与电流阻挡层图形均对应N、P焊盘电极的预留位置,在芯片结构表面形成第一PV层,再在芯片结构的表面形成第二PV层,在此基础上形成介质膜DBR层,DBR层和第二PV层的蚀刻速度大于第一PV层蚀刻速度,形成先缓后陡的双斜坡,在蚀刻位置制作N、P焊盘电极。

作为上述技术方案的进一步改进:

通过原子蒸镀机在芯片结构表面形成第一PV层。

第一PV层是SiO2、AlN、Al

第二PV层为利用PECVD技术沉积的SiO

DBR层为利用光学镀膜机交替沉积SiO

芯片衬底为蓝宝石、硅片、碳化硅片或金属。

本发明还采用的技术方案如下:

一种双斜坡型倒装DBR的LED芯片结构制作方法,包括以下步骤:

步骤S1,提供芯片衬底,在芯片衬底上生长LED芯片外延结构;

步骤S2,通过ICP刻蚀技术将暴漏区域的N-GaN层刻蚀出来,形成N-GaN台阶;

步骤S3,制作电流阻挡层,电流阻挡层图形对应位于在N、P焊盘电极对应的预留位置上;

步骤S4,制作透明导电层;

步骤S5,制作N、P导电金属层,N、P导电金属层图形与电流阻挡层图形均对应N、P焊盘电极的预留位置;

步骤S6,通过原子蒸镀机的镀膜技术在芯片结构表面沉积第一PV层,再利用PECVD技术在芯片结构的表面沉积一层SiO

步骤S7,对PV+DBR膜层结构进行蚀刻,将N、P导电金属层暴露出来,DBR层和第二PV层的蚀刻速度大于第一PV层蚀刻速度,形成先缓后陡的双斜坡;

步骤S8,制作N、P焊盘电极。

作为上述技术方案的进一步改进:

第一PV层的制作工艺条件为:工艺温度为250℃,镀率为2 Å/s,沉积厚度为1KA。

第一PV层是SiO

第二PV层的制作工艺条件为:镀率为4 Å/s,沉积厚度为10KA。

本发明的有益效果如下:

本发明通过原子蒸镀机的镀膜技术在芯片结构表面沉积一层薄膜为第一PV层,再利用PECVD技术在芯片结构的表面沉积一层SiO

附图说明

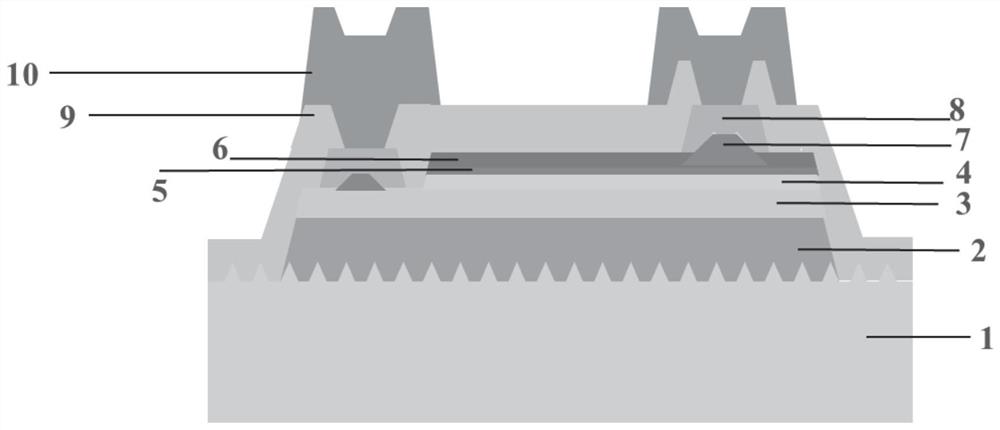

图1为本发明的结构示意图。

图2为本发明PV+DBR膜层结构的示意图。

图中:1、芯片衬底;2、U-GaN层;3、N-GaN层;4、多量子阱层;5、P-GaN层;6、透明导电层;7、电流阻挡层;8、导电金属层;9、PV+DBR膜层结构;10、焊盘电极。

具体实施方式

下面结合附图,说明本发明的具体实施方式。

如图1所示,本发明所述的双斜坡型倒装DBR的LED芯片结构在芯片衬底1上生长LED芯片外延结构,芯片衬底1包括但不限于蓝宝石、硅片、碳化硅片或金属。例如利用MOCVD设备(MOCVD,Metal-organic Chemical Vapor Deposition,金属有机化合物化学气相沉淀)在芯片衬底1上生长LED芯片外延结构,LED芯片外延结构是多层结构,根据实际需要而定,例如可以是依次生长的U-GaN层2、N-GaN层3、多量子阱层4和P-GaN层5,也可以是依次生长的N-GaN层3、多量子阱层4和P-GaN层5,所述LED芯片外延结构覆盖在芯片衬底1的整面。MOCVD是在气相外延生长(VPE)的基础上发展起来的一种新型气相外延生长技术。

在芯片生长完成外延结构后,利用光刻掩膜版的遮挡,通过ICP刻蚀技术(ICP,Inductively Coupled Plasma,感应耦合等离子体刻蚀)将暴漏区域的N-GaN层3刻蚀出来,形成N-GaN台阶。在LED芯片外延结构上制作电流阻挡层7(CBL,Current Blocking Layer),即利用PECVD技术在芯片结构上沉积SiO

在此基础上制作透明导电层6,即利用sputter溅射技术和光刻掩膜版的 遮挡在芯片结构表面上镀ITO膜(ITO,Indium Tin Oxide,氧化铟锡)。然后在此基础上利用金属镀膜技术和光刻掩膜版制作N、P导电金属层8,N、P导电金属层8图形与电流阻挡层7图形分别对应且位于其上方,均对应N、P焊盘电极10的预留位置。

通过原子蒸镀机的镀膜技术在芯片结构表面沉积一层薄膜为第一PV层,原子蒸镀机优选为ALD设备,工艺条件为:工艺温度为250℃,镀率为2 Å/s,沉积厚度为1KA。第一PV层可以是SiO

通过ICP刻蚀技术对PV+DBR膜层结构9进行蚀刻,将N、P导电金属层8暴露出来。由于DBR层和第二PV层的蚀刻速度快,形成的蚀刻角度较大,第一PV层蚀刻慢,形成蚀刻角度更小的倾斜坡度,最终形成先缓后陡的双斜坡(见图2)。

然后,通过光刻掩膜版的遮挡,利用电子束蒸发技术制作N、P焊盘电极10。N、P焊盘电极10优选为圆台状。

参照图1,本发明所述双斜坡型倒装DBR的LED芯片结构的制作方法,包括以下步骤:

步骤S1:提供芯片衬底1包括但不限于蓝宝石、硅片、碳化硅片或金属,利用MOCVD设备在芯片衬底1上生长LED芯片外延结构,LED芯片外延结构是多层结构,根据实际需要而定,例如可以是依次生长的N-GaN层3、多量子阱层4和P-GaN层5,也可以是依次生长的U-GaN层2、N-GaN层3、多量子阱层4和P-GaN层5,所述LED芯片外延结构覆盖在芯片衬底1的整面。

步骤S2:将生长完成的LED芯片外延结构清洗干净,利用正性光刻掩膜技术,制作掩膜图形,通过ICP刻蚀技术将暴漏区域的N-GaN层3刻蚀出来,形成N-GaN台阶。

步骤S3:在LED芯片外延结构上制作电流阻挡层7图形,电流阻挡层7图形对应位于在N、P焊盘电极10对应的预留位置上。即利用PECVD技术在芯片结构上沉积SiO

步骤S4:在LED芯片外延结构上制作透明导电层6,即利用sputter溅射技术镀ITO膜。

步骤S5:利用金属镀膜技术和光刻掩膜版制作N、P导电金属层8,N、P导电金属层8图形与电流阻挡层7图形分别对应且位于其上方,均对应N、P焊盘电极10的预留位置。

步骤S6:通过原子蒸镀机的镀膜技术在芯片结构表面沉积一层薄膜为第一PV层,原子蒸镀机优选为ALD设备,工艺条件为:工艺温度为250℃,镀率为2 Å/s,沉积厚度为1KA。第一PV层可以是SiO

步骤S7:通过ICP刻蚀技术对PV+DBR膜层结构9进行蚀刻,将N、P导电金属层8暴露出来。由于DBR层和第二PV层的蚀刻速度快,形成的蚀刻角度较大,第一PV层蚀刻慢,形成蚀刻角度更小的倾斜坡度,最终形成先缓后陡的双斜坡。

步骤S8:通过光刻掩膜版的遮挡,利用电子束蒸发技术制作N、P焊盘电极10。

在本发明中,正性光刻掩膜技术是利用正性光刻胶制成掩膜图形的技术,凡是在能量束(光束、电子束、离子束等)的照射下,以降解反应为主的光刻胶称为正性光刻胶,简称正胶。负性光刻掩膜技术是利用负性光刻胶制成掩膜图形的技术,凡是在能量束(光束、电子束、离子束等)的照射下,以交联反应为主的光刻胶称为负性光刻胶,简称负胶。

以上描述是对本发明的解释,不是对发明的限定,在不违背本发明精神的情况下,本发明可以作任何形式的修改。

- 双斜坡型倒装DBR的LED芯片结构及其制作方法

- 双斜坡型倒装DBR的LED芯片结构