一种具有抑制振荡效果的IGBT器件及其制造方法

文献发布时间:2023-06-19 12:13:22

技术领域

本发明属于半导体功率器件技术领域,特别是涉及一种具有抑制振荡效果的IGBT器件及其制造方法。。

背景技术

IGBT(绝缘栅双极型晶体管)是由双极性晶体管和MOSFET组合而成的复合全控型电压驱动式功率半导体器件,同时具有MOSFET高输入阻抗和GTR低导通压降。现阶段IGBT已经成为电力电子设备的主流器件,在开关电源、整流器、逆变器、UPS等领域有着广泛的应用。

IGBT器件在实际应用中大电流芯片较为常见,这些大电流的IGBT芯片往往搭配使用大电流的二极管芯片,大电流的二极管芯片在小电流使用工况下开启和关断时,速度极快,极易引发电路振荡,严重时甚至导致器件失效。。

发明内容

发明目的:针对现有技术中存在的问题,本发明公开了一种具有抑制振荡效果的IGBT器件及其制造方法,IGBT器件具有两种或两种以上不同沟槽间距的结构,小沟槽间距的区域对应更低的阈值电压,大沟槽间距的区域对应更高的阈值电压,能够有效避免小电流状态开启时的电压振荡及失效,同时当电路处于大电流状态时,开关速度并不会明显降低。

技术方案:为实现上述技术目的,本发明采用以下技术方案:一种具有抑制振荡效果的IGBT器件,其特征在于,包括N型漂移区,在N型漂移区上侧内设有若干沟槽,在沟槽内填充沟槽多晶硅;

所述IGBT器件包括至少两个阈值电压不同的区域,阈值电压不同的区域的沟槽之间的间距不同,阈值电压不同的区域的栅极电阻不同:低阈值电压区域的沟槽之间的间距小于高阈值电压区域的沟槽之间的间距,低阈值电压区域的栅极电阻值大于高阈值电压区域的栅极电阻值。

优选地,低阈值电压区域的沟槽之间的间距比高阈值电压区域的沟槽之间的间距小0.2μm~1μm。

优选地,在沟槽多晶硅外侧和沟槽侧壁之间填充栅氧化层,在沟槽之间的N型漂移区上侧设置P型体区,P型体区的下表面高于沟槽底部,在P型体区上侧设置N型发射区,沟槽上表面、栅氧化层上表面、沟槽多晶硅上表面均与N型发射区上表面齐平,在沟槽和N型发射区上侧设置绝缘介质层,位于N型发射区上侧的绝缘介质层内部开设源区接触孔区,在绝缘介质层上侧设置源极金属,源极金属通过源区接触孔区与N型发射区欧姆接触;

N型漂移区下侧设置N型缓冲层,N型缓冲层下侧设置P型漏区,P型漏区下侧设置漏极金属,P型漏区与漏极金属形成欧姆接触。

优选地,位于同一阈值电压区域中的沟槽内的全部沟槽多晶硅经过该区域的栅极电阻连接到栅极金属。

优选地,位于同一阈值电压区域中的沟槽内的一部分沟槽多晶硅经过该区域的栅极电阻连接到栅极金属,一部分沟槽多晶硅连接到源极金属。

一种具有抑制振荡效果的IGBT器件的制造方法,其特征在于,包括如下步骤:

步骤一:选择N型半导体衬底作为N型漂移区,在N型半导体衬底的上部,不同阈值电压区域内分别刻蚀出若干沟槽,不同阈值电压区域内的沟槽间距不同;

步骤二:在N型半导体衬底上表面以及沟槽表面形成栅氧化层,并在栅氧化层上完成多晶硅淀积,使得存在多晶硅填充在沟槽内得到沟槽多晶硅;

步骤三:进行光刻,保留沟槽内的沟槽多晶硅和栅氧化层,刻蚀掉一部分N型半导体衬底上表面的多晶硅和栅氧化层,保留另一部分N型半导体衬底上表面的多晶硅和栅氧化层;

步骤四:在沟槽之间进行P型离子注入,在不同阈值电压区域内形成了P型体区;

步骤五:在P型体区上进行发射极区光刻,进行N型离子注入,在P型体区的上部形成N型发射区;

步骤六:在步骤五所形成的结构上表面淀积、覆盖绝缘介质层,之后刻蚀绝缘介质层,在该绝缘介质层的内部形成源区接触孔;

步骤七:在步骤六所形成的结构上表面淀积、覆盖源极金属,源极金属覆盖绝缘介质层并填满源区接触孔;

步骤八:在N型半导体衬底片下表面进行N型离子注入并激活,形成N型缓冲层;在N型缓冲层下表面再进行P型离子注入并激活,形成P型漏区;

步骤九:在P型漏区下表面覆盖漏极金属,并与P型漏区形成欧姆接触。

有益效果:与现有技术相比,本发明具有如下有益效果:

1、本发明提出的一种IGBT器件对开启时的产生的电压、电流振荡现象有着明显的改善作用,且不会明显降低正常使用时的开关速度;

2、本发明提出的一种IGBT器件的制造方法,制造工艺简单,和现有工艺兼容,无需增加额外成本。

附图说明

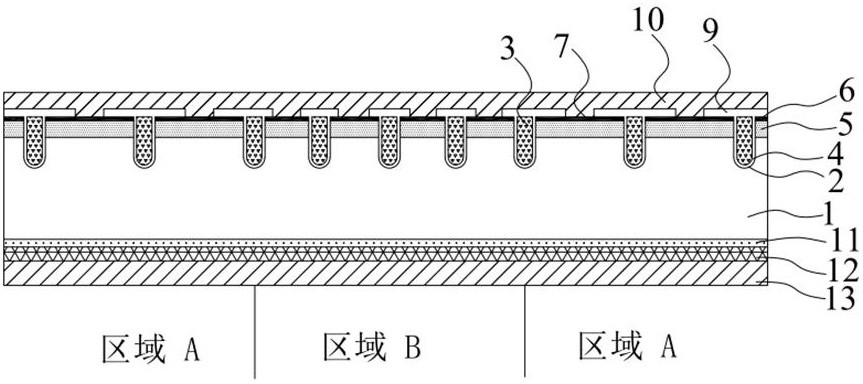

图1是本发明提出的一种IGBT器件的一个实施例的剖面示意图;

图2是本发明提出的一种IGBT器件的一个实施例的俯视示意图;

其中,1:N型漂移区;2:沟槽;3:沟槽多晶硅;4:栅氧化层;5:P型体区;6:N型发射区;7:源区接触孔;8:栅极电阻;81:区域A的栅极电阻;82:区域B的栅极电阻;9:绝缘介质层;10:源极金属;11:N型缓冲层;12:P型漏区;13:漏极金属;14:栅极金属。

具体实施方式

下面结合附图和实施例对本发明的具体实施方式作进一步详细的说明。

为清楚地说明本发明的具体实施方式,说明书附图中所列示意图,放大了本发明所述的层和区域的厚度,且所列图形大小并不代表实际尺寸;说明书附图是示意性的,不应限定本发明的范围。说明书中所列实施例不应仅限于说明书附图中所示区域的特定形状,而是包括所得到的形状如制造引起的偏差等,如刻蚀得到的曲线通常具有弯曲或圆润的特点,在本发明实施例中均以矩形表示。

本发明公开了一种具有抑制振荡效果的IGBT器件,在IGBT器件中包含不同阈值电压的区域,并在不同阈值电压的区域中搭配使用不同的栅极电阻阻值:低阈值电压区域使用更大的栅极电阻,使得IGBT器件的低阈值电压区域先开启,由于该区域有着更大的栅极电阻,开启过程更为缓慢,在开启过程中难以出现电压和电流波形的振荡,随着栅极电压继续上升,随后IGBT器件的高阈值电压区域迅速导通,并不会影响IGBT器件整体的开关速度。

本发明所述的一种具有抑制振荡效果的IGBT器件,包括N型漂移区1,在N型漂移区1上侧内设有若干沟槽2,在沟槽2内填充沟槽多晶硅3,在沟槽多晶硅3外侧和沟槽2侧壁之间填充栅氧化层4,在沟槽2之间的N型漂移区1上侧设置P型体区5,P型体区5的下表面高于沟槽2底部,在P型体区5上侧设置N型发射区6,沟槽2上表面、栅氧化层4上表面、沟槽多晶硅3上表面均与N型发射区6上表面齐平,在沟槽2和N型发射区6上侧设置绝缘介质层9,在位于沟槽2之间、N型发射区6上侧的绝缘介质层9内部开设源区接触孔区7,源区接触孔区7底部与N型发射区6上表面齐平,源区接触孔区7用于与金属形成欧姆接触,在绝缘介质层9上侧设置源极金属10,且源极金属10通过源区接触孔区7与N型发射区6上表面欧姆接触。

N型漂移区1下侧设置N型缓冲层11,N型缓冲层11下侧设置P型漏区12,P型漏区12下侧设置漏极金属13,且P型漏区12与漏极金属13形成欧姆接触。

本发明所述的IGBT器件包括至少两个不同阈值电压区域,不同阈值电压区域的特征尺寸不同,即不同阈值电压区域中的沟槽2之间的间距不同:低阈值电压区域的沟槽2之间的间距比高阈值电压区域的沟槽2之间的间距小0.2μm~1μm。通过沟槽2之间间距的变化,可在保持同样注入工艺的情况下,实现阈值电压的差异,可避免多次注入带来的成本增加。

位于同一阈值电压区域中的若干沟槽2内的沟槽多晶硅3在IGBT器件的特定位置汇集,并经过该区域的栅极电阻8连接到栅极金属14,或者,位于同一阈值电压区域中的沟槽2内的部分沟槽多晶硅3在IGBT器件的特定位置汇集,并经过该区域的栅极电阻8连接到栅极金属14,另外部分沟槽多晶硅3连接源极金属10。栅极电阻8是位于沟槽2外的块状独立的多晶硅,与沟槽2内的沟槽多晶硅3同时形成,通过控制处于沟槽2外的多晶硅的长宽比来控制栅极电阻8阻值的大小。

本发明所述的IGBT器件具有两种或两种以上不同沟槽间距的结构,相比之下,小沟槽间距的区域对应更低的阈值电压,IGBT器件开启时该区域会先有电流,当电路处于小电流状态开启时,该区域集中了大部分电流,通过增加该区域的栅极电阻8阻值来降低该区域的开启速度,从而有效避免了开启时的电压振荡及失效;同时当电路处于大电流状态时,因为IGBT器件其他区域的栅极电阻8阻值并没有增加,开关速度并不会明显降低。

本发明还公开了一种具有抑制振荡效果的IGBT器件的制造方法,包括如下步骤:

步骤一:选择N型半导体衬底作为N型漂移区,在N型半导体衬底的上部,不同阈值电压区域内分别刻蚀出若干沟槽,不同阈值电压区域内的沟槽间距不同;

步骤二:在N型半导体衬底上表面和沟槽表面形成栅氧化层,并在栅氧化层上完成多晶硅淀积,使得存在多晶硅填充在沟槽栅内得到沟槽多晶硅;

步骤三:进行光刻,保留沟槽内的沟槽多晶硅和栅氧化层,刻蚀掉部分N型半导体衬底上表面的多晶硅和栅氧化层,保留部分N型半导体衬底上表面的多晶硅和栅氧化层;此步骤是为了将沟槽内的沟槽多晶硅引出和栅极金属或者源极金属相连接,同时也为了留下不同阈值电压区域的不同的栅极电阻,即保留的部分N型半导体衬底上表面的多晶硅;

步骤四:在沟槽之间进行P型离子注入,在不同阈值电压区域内,由于沟槽间距的不同,自然形成了不同的、掺杂分布的P型体区;

步骤五:在P型体区上进行发射极区光刻,进行N型离子注入,在P型体区的上部形成N型发射区;

步骤六:在步骤五所形成的结构上表面淀积、覆盖绝缘介质层,之后刻蚀绝缘介质层,在该绝缘介质层的内部形成源区接触孔;

步骤七:在步骤六所形成的结构上表面淀积、覆盖源极金属,源极金属覆盖绝缘介质层并填满源区接触孔。

步骤八:在N型半导体衬底片下表面进行N型离子注入并激活,形成N型缓冲层;在N型缓冲层下表面再进行P型离子注入并激活,形成P型漏区;

步骤九:在P型漏区下表面覆盖漏极金属,并与P型漏区形成欧姆接触。

实施例

本实施例提供一种具有抑制振荡效果的IGBT器件,如图1、图2所示,包括N型漂移区1,N型漂移区1分为区域A和区域B,分别对应高阈值电压区域和低阈值电压区域,区域A和区域B内均设有若干沟槽2,沟槽2深度均为5um,宽度1um,区域A内的沟槽2间距为2um,区域B内的沟槽间距为1.5um。

如图1所示,本实施例中,在沟槽2内均填充有沟槽多晶硅3,沟槽多晶硅3全部和栅极金属相连接;沟槽多晶硅3外侧和沟槽2侧壁之间填充有栅氧化层4,栅氧化层4厚度120nm;沟槽2之间为P型体区5,深度2.5um,在P型体区5上表面形成有N型发射区6,在N型漂移区1下侧有N型缓冲层11,在N型缓冲层11下侧有P型漏区12。

如图2所示,本实施例中,区域A和区域B分别有着不同的栅极电阻,栅极电阻由保留的多晶硅的长宽比来调节,区域A的栅极电阻81值为5Ω,区域B的栅极电阻82值为10Ω。

本实施例中IGBT器件具有两种不同沟槽间距的结构,小沟槽间距的区域B对应的更低的阈值电压,IGBT器件开启时区域B先有电流,当电路处于小电流状态开启时,区域B集中了大部分电流,通过增加区域B的栅极电阻至10Ω来降低区域B的开启速度,从而有效避免了开启时的电压振荡及失效;同时当电路处于大电流状态时,因为IGBT器件高阈值电压区域A的栅极电阻为5Ω并没有增加,总的开关速度并不会明显增加。

以上所述仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 一种具有抑制振荡效果的IGBT器件及其制造方法

- 一种具有抑制振荡效果的IGBT器件及其制造方法