一种指令驱动的商用密码专用处理器系统

文献发布时间:2023-06-19 09:38:30

技术领域

本发明属于集成电路设计和电子信息安全技术领域,具体涉及一种基于中国国家标准商用密码算法的定制化指令集及其处理器实现。

背景技术

自从进入21世纪以来,技术日新月异,信息技术飞速发展,人们生活在大数据和物联网的大时代。移动通信、电子商务、智慧医疗、可携带设备等新兴信息储存、交互方式的兴起和普及,带来了极大的便利的同时,也使得人们越来越关注信息安全和传播风险相关的问题。密码技术毫无疑问是降低信息安全风险的基础与核心。

现代密码学的兴起可以追溯到20世纪70年代“密码学新方向”的发表和1972年美国IBM公司研制的并被美国采纳作为标准的DES分组密码算法。

中国自己的现代密码体制起步较晚。ZUC算法,又称祖冲之算法,是中国第一个自主设计并成为国际密码标准的密码算法,在2009年正式立项,后被3GPP SA全会正式通过,成为3GPP LTE第三套加密标准核心算法。

尔后,国家密码管理局在2010年12月公布了SM2椭圆曲线公钥密码算法和SM3密码杂凑算法,在2012年3月公布了SM4分组密码算法,在2016年3月公布了SM9标识密码算法。中国逐渐形成了完整的国密/商用密码体系,并获得了国际上的认可:2017年11月3日,SM2与SM9算法成为ISO/IEC国际标准;2018年10月,SM3算法正式成为ISO/IEC国际标准:2020年4月24日,ZUC序列密码算法获得一致通过,成为ISO/IEC国际标准。

一般来说,加密算法的实现都可以选择基于通用处理器或微处理器的软件实现,这种实现方式控制便捷、设计难度低且具有极强的灵活性。然而如今,大量的安全需求场景都有低成本、低功耗、高实时性、高运算效率等要求,这就需要利用硬件资源去分担运算。根据其硬件实现和处理器的耦合度关系,一般有以下几种方式:

(1)ASIC专用集成电路实现。一般针对单一算法或同类算法定制设计,硬件资源少、速度快、能效高,但是灵活性差、应用范围窄、安全性局限,一旦出现算法升级就失去其作用。

(2)扩展指令集实现。可集成协处理器,也可以直接修改处理器定制单元。基于已有的处理器架构,设计额外的加解密专用指令并引入相关的硬件模块,在不显著影响通用处理器性能的同时有针对性地加速密码算法中的部分运算。但也存在吞吐率低,功耗受限的问题。

(3)ASIP专用处理器实现。针对应用本身,设计一套专用处理器架构,引入并行处理、可重构计算、定制存储结构等等实现方式,追求性能和能耗的同时具备一定的灵活性。

发明内容

为了克服现有技术的不足,本发明旨在针对中国国家标准密码算法,考虑到高性能、资源消耗少的需求,提出一套定制指令集及其专用处理器实现。

本发明采用如下的技术方案:

一种指令驱动的商用密码专用处理器系统,所述系统包括:

密码配置模块,用于在处理器流水线空闲时接收总线写入的密码算法配置信息,并在配置信息完备后,启动处理器的流水线;

内部存储单元,用于存储处理器流水线中的预设数据或中间数据,包括内部指令存储器和寄存器堆;所述内部指令存储器,用于存储相应加解密算法配置的指令序列,可以更改配置;所述寄存器堆,由32个128位寄存器构成,具有2个读口和1个写口,且都可以操作变长连续寄存器,其读写兼顾相关性和优先级;

处理器流水线模块,用于完成密码算法的执行,所述处理器流水线模块包括:

取指模块,接收密码配置模块传来的密码算法及模式信息,从内部指令存储器中相应地地址开始获取指令,执行指令序列递增或是接收分支跳转模块的有效地址,并把指令传输给译码级;

译码模块,接收取指模块传来的有效指令及有效信号,依据定制指令的编码方式进行译码,读取寄存器堆的数据,并将执行模块、执行功能、执行数据等传入下一级执行级,或是接收回写级各执行模块传回的有效回写数据,并执行寄存器堆的回写;

运算集成模块接收由译码模块传来的有效执行信号和执行数据,根据指令操作执行相应的加解密运算,并将运算结果送入回写级;

分支跳转模块根据译码模块传来的判断模式选择信号,判断是否发生跳转,并将计算跳转目的PC值传给取指模块,根据执行模式选择信号,判断是否回写,并将回写数据传入回写级;

数据存取模块根据译码模块传来的读写选择信号,向片外数据存储器读取或写入数据,根据地址自增信号,将自增后地址送入回写级。

进一步,所述处理器流水线模块根据面向中国国家标准商用密码算法的定制指令集进行取指、译码和执行操作。

再进一步,所述定制指令集包括密码运算指令、数据存取指令和分支跳转指令。

更进一步,所述指令集长度为32位,第31至第30位代表指令类型,01代表密码运算指令,10代表分支跳转指令,11代表数据存取指令;其中,

对于密码运算指令,第24至21位为运算操作选择,第20至16位为目的寄存器,第15至10位为源寄存器0,第10至6位为源寄存器1;最低6位为立即数;

对于分支跳转指令,第29至27位为分支跳转条件,第26至25为比较方式和操作,第20至16位和低6位组成分支跳转绝对地址或相对地址,第15至10位为源寄存器0,第10至6位可为源寄存器1,也可与第23至21位组成立即数;

对于数据存取指令,第29位为读写选择,第24位为地址自增选择,第23至21位为数据长度,第15至10位为源寄存器0;当指令为读取数据时,第20至16位为目的寄存器,低11位为基址偏移量;当指令为写入数据时,第10至6位为源寄存器1,第20至16位和低6位组成基址偏移量。

所述处理器流水线包括:取指、译码、执行和回写。

所述运算集成模块包含数据前馈通路,用于所述译码模块寄存器取值的相关性依据和数据选择。

本发明与中央处理器的交互方式如下:密码配置模块在加解密运算空闲时,接收中央处理器向控制寄存器写入的密码配置信息。在接收足够的密码配置信息后,即可进入加解密运算流程。直到运算结束并写入输出结果前,不接受新的密码配置信息和加解密请求。写入输出结果后,回馈给中央处理器加解密运算结束信号。

一般地,密码配置信息包括密码算法和模式、初始向量地址、初始密钥地址、输入信息地址、输入信息位长度、输出信息地址。

进一步地,加解密运算流程采用与传统处理器类似的流水线结构,具体为取指-译码-执行-回写4级流水线结构。

其中,

取指模块接收密码配置模块传来的密码算法及模式信息,从内部指令存储器中相应地地址开始获取指令,传输给译码级。

译码模块接收取指模块传来的指令及有效信号,依据加解密定制指令集的编码方式进行译码,并读取寄存器堆的数据。译码模块将执行模块、执行功能、执行数据等传入下一级执行级。

另一方面,译码模块接收回写级各执行模块传回的回写有效信号、回写寄存器、回写数据等信息,执行寄存器堆的回写。

进一步地,为了数据通路的高效性和流水线的推动顺畅,在数据回写的基础上,额外添加了数据前馈通路。当指令序列前后存在写后读相关性时,译码模块通过数据前馈通路获取执行级的运算结果。

进一步地,译码模块的寄存器堆设计包含了32个寄存器,每个寄存器基础位宽为128比特,寄存器堆包含2个读口和1个写口。考虑到,中国国家标准密码算法中,SM3消息摘要算法的消息分组长度为512比特,摘要长度为256比特,压缩函数状态长256比特;SM4分组密码算法的分组长度为128比特,密钥长度为128比特;ZUC祖冲之序列密码算法的密钥长度为128比特,初始向量长度为128比特,中间变量长度为32比特,每轮输出长度为32比特,线性反馈移位寄存器总长度可视为512比特。将处理器的寄存器位宽设计为128比特,既是为了满足密码算法运算的中间数据数量较多、长度较宽、相关性强的需求,又可以更加完整地存储、计算数据。特别地,基于同样的需求,本处理器支持变长的数据宽度,一次寄存器号的读取或写入,可以操作1到4个寄存器的数据,即一次可以读写128比特、256比特、384比特或是最大512比特的数据,满足更加丰富多样的密码算法应用场景。

运算集成模块接收由译码模块传来的控制信号,如使能信号、运算选择信号等,以及运算数据,包括寄存器堆读取的数据和指令中的立即数,根据指令选择的操作执行相应的加解密运算,并在运算完成后将运算结果和控制信号传入回写级,送往译码模块。

分支跳转模块接收由译码模块传来的控制信号,如使能信号、判断模式选择、执行模式选择等,以及运算数据,可包括待比较的寄存器操作数、待比较的立即数和跳转的PC偏移量等。然后根据判断模式进行判断是否发生跳转,将跳转使能信号和跳转目的PC值传给取指模块;根据执行模式判断是否进行回写,将回写数据和控制信号传入回写级,送往译码模块。

数据存取模块接收由译码模块传来的控制信号,如使能信号、读写选择、数据长度、地址自增选择等,以及操作数据,包括存取基地址、地址选择信号、地址偏移量、待存入数据等、然后向外部存储器发起读或写请求。一般地,数据存取模块会读取初始密钥、初始向量、输入信息等数据,并写入运算结果/输出信息。在一条指令完整的数据读取结束时,将传输数据和控制信号送入回写级,送往译码模块。根据地址自增选择,在一条指令完整的数据传输结束后,会把最后一笔传输的下一个地址数据和控制信号送入回写级,送往译码模块。

此外,关于本发明的总线传输接口,采用的是AMBA2 AHB总线协议,满足加解密专用处理器的性能和时钟需求,且不需要太大的带宽。

本发明的有益效果为:面向加解密算法,通过指令驱动专用的执行模块,提供合理的中间数据方案,可以额外增加执行单元,灵活地支持更多的加解密算法。

附图说明

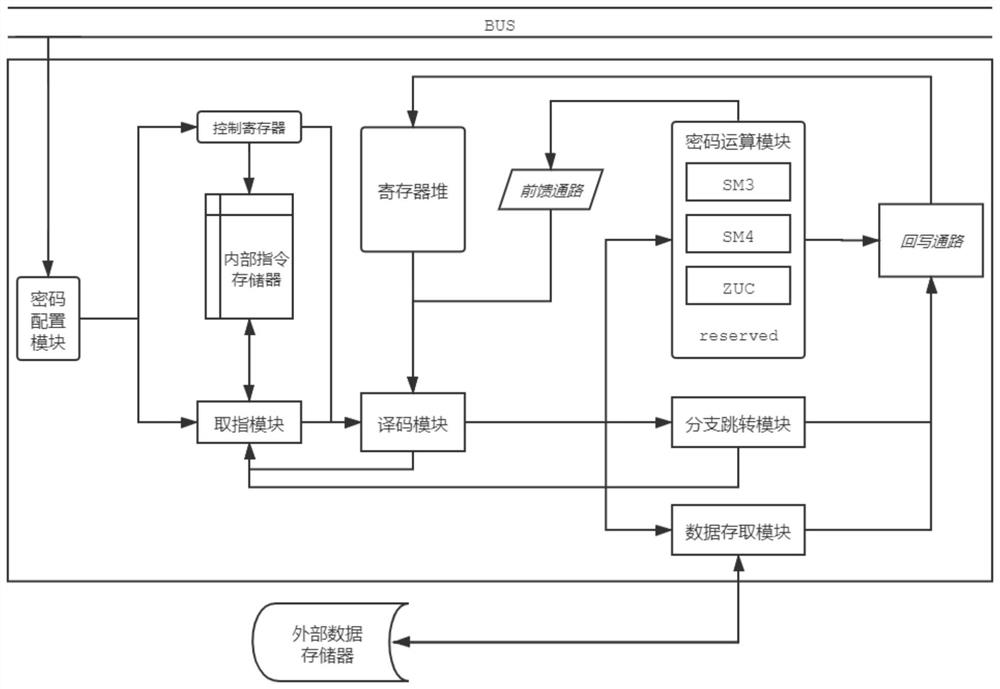

图1为本发明实施例的处理器结构示意图。

图2为本发明编程模型示意图。

具体实施方式

为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍。

参照图1和图2,一种指令驱动的商用密码专用处理器系统,针对中国国家密码管理局公布的SM3密码杂凑算法、SM4分组密码算法和ZUC祖冲之序列算法设计了相应的指令,同时也为其他新增密码算法预留了编码空间,具备一定的可扩展性。

可以从图1中看到,需要唤醒加解密专用处理器时,中央处理器需要将密码算法配置信息写入本发明实例的控制寄存器中。本发明实例涉及的控制寄存器有:8位的密码算法配置寄存器crypt_cfg、32位的初始向量地址寄存器iv_addr、32位的初始密钥地址寄存器key_addr、32位的输入信息地址寄存器txt_in_addr、32位的结果输出地址寄存器txt_out_addr以及64位的输入信息长度寄存器txt_len。当中央处理器把全部输入输出相关信息写入,并配置好密码算法后,即进入加解密专用处理器主流水线。密码配置模块将有效信号送入主流水线取值级。

密码算法配置寄存器crypt_cfg共8位可配。高2位用于指示加密模式,00表示信息解密,01表示信息加密,10表示数字签名验证,11表示数字签名生成。低6位表示密码算法。对于目前的设计来说,0x0对应SM2椭圆曲线公钥密码算法,0x1对应SM3密码杂凑算法和SM4分组密码算法,0x2对应SM9标识密码算法,0x3对应ZUC祖冲之序列密码算法。预留了相当的算法配置空间。

考虑到SM3密码杂凑算法输入消息长度不大于2

进入处理器主流水线后,首先是取指模块读取从密码配置模块收到的密码算法有效信号,并读取密码算法配置寄存器crypt_cfg,得到相应算法的初始PC,作为主流水线的开始。

取指模块对应取指级流水线,主要负责取值PC维护、指令分支跳转等工作。一般地,取指模块按顺序递增PC,并从内部指令存储器按照PC取出32位指令。当取指模块接收到分支跳转模块传来的分支跳转有效信号时,会把PC更新为分支跳转PC。

另外,取指模块会接收来自译码模块的流水线暂缓信号,等待分支跳转指令或数据存取指令的执行完成。一方面,一般地,当一组数据开始处理前和处理完全后,才会执行分支跳转指令和数据存取指令,不会影响一组数据的运算;另一方面,密码算法的运算普遍数据依赖性强、处理紧凑,无法在流水线上执行其他运算指令。

译码模块主要对应译码级流水线和回写级流水线,主要负责指令的译码、寄存器的调度和回写、操作数的准备等工作。在译码级,译码模块接收取指模块传来的指令及其有效信号,根据定制加解密指令集的编码格式进行译码,然后根据译码结果准备好操作数,将指令操作数和操作信息推入执行级,分发至各个执行单元。

在回写级,译码模块接收到各个执行单元传回的回写有效信号、回写寄存器号、回写数据和回写寄存器长度,将有效的回写送入寄存器堆。进一步地,译码模块接收运算执行单元传回的前馈有效信号、前馈寄存器号、前馈数据和前馈寄存器长度,当当前译码指令与执行指令的操作数存在相关性时,译码模块将选取相应的前馈数据作为操作数。

译码模块需要维护一个寄存器堆,寄存器堆包含32个通用寄存器,通用寄存器位宽为128比特,寄存器堆具有2个读口和1个写口,寄存器读写口都是位宽变长读写口。寄存器堆的1个读写口,通过指定寄存器编号和寄存器长度,可以对自指定寄存器编号开始连续的1到4个寄存器的数据进行读写,即一次可以读写单个寄存器128比特、或是连续若干个寄存器共计256比特、384比特以至于最大512比特的数据。如果寄存器堆的读口和寄存器堆的回写口和前馈通路存在寄存器的相关性,则会对每个寄存器的数据按照先前馈通路、再回写口的顺序获取数据。整个寄存器堆支持输入输出和中间结果的暂存,不存在读写冲突。

执行单元对应于执行级,共分为3部分,如图1所示,包括运算集成模块、分支跳转模块和数据存取模块。主要负责执行译码级传过来的指令操作,并把指令结果按操作送入回写级。

表1

运算集成模块集成了各个加解密算法的运算实现,是作为核心的定制指令集的映射。密码运算指令编码如表1所示。第31位到第30位固定为01,代表加解密运算指令;第29位到第25位保留;第24位到第21位用于表示运算操作;第20位到第16位表示目的寄存器;第15位到第10位表示源寄存器0;第10位到第6位表示源寄存器1;最低6位表示算法运行的轮数或阶段,最大匹配SM3密码杂凑算法的64轮迭代压缩。考虑到密码算法运算的复杂性和灵活的调试能力,每种密码算法模块之间相互独立,每种密码算法模块的内部都包含各个运算操作的子模块。密码运算指令可能不含源操作数1,但一定需要源操作数0和回写结果数据。一条密码运算指令执行完成后,将前馈信号和回写信号送往译码模块。

表2

分支跳转指令主要的应用场景主要包括算法配置的不同模式分支跳转、基于长度的迭代分支跳转、基于长度的消息填充分支跳转、运算结果是否合理的分支跳转、回到迭代循环开始的直接跳转、回到流水线空闲状态的直接跳转等,对应的是密码算法运算阶段的划分、开始或结束。分支跳转指令的编码格式如表2所示。第31位到第30位固定为10,代表分支跳转指令;第29位到第27位表示分支跳转条件,000对应绝对地址跳转,001对应相对地址跳转,010对应相等分支指令,011对应不相等分支指令,100对应大于等于分支指令,101对应大于分支指令,110对应小于等于分支指令,11对应小于分支指令;第26位到第25表示比较方式和操作,在分支指令时生效,00表示寄存器值与寄存器值作比较,01表示寄存器值与立即数值作比较,10表示寄存器值与立即数值作比较,并在寄存器值大于等于立即数时减去立即数,11表示寄存器值减去立即数并与0作比较;第20位到第16位和低6位组成11比特的分支跳转绝对地址或相对地址;第15位到第10位表示源寄存器0;第10位到第6位或表示源寄存器1,或作为低位与第23位到第21位组成8比特立即数。

特别地,指令出现寄存器值减去立即数值的操作,都是在判断迭代循环或退出的场景里,此时源操作数0即对应信息长度。此时,分支跳转模块会在送出分支跳转有效信号和目标PC的同时,把回写信息和回写数据送回译码模块,且目的寄存器号应与源寄存器0相同。

另外,基于场景连贯性和数据连续性的考虑,分支跳转指令会暂缓流水线一拍。

表3

表4

数据存取模块负责向片外处理器读写信息,包括初始向量、初始密码、输入信息和输出信息,其中输入信息按照分组长度读取并进行运算,输出信息在加解密模式下按照分组长度写入。数据存取指令的编码格式如表3表4所示。第31位到第30位固定为11,代表数据存取指令;第29位代表数据方向,0表示读取数据,1表示写入数据;第24位代表数据存取结束后,地址是否更新;第23位到第21位代表存取数据的字节数,000代表存取1字节8比特宽度的数据,110代表存取64字节512比特宽度的数据;第15位到第10位表示源寄存器0,源操作数0对应数据存取基址。当指令为读取数据时,第20位到第16位为目的寄存器,低11位作为基址偏移量;当指令为写入数据时,第10位到第6位表示源寄存器1,源操作数1即为待写入数据,第20位到第16位和低6位组成11比特的基址偏移量。

地址自增应用于读取输入信息和写入输出信息的场景中,一次密码算法运算对一组定长数据进行操作,连续操作至最后一组数据或消息额外填充的一组数据结束,其地址连续,地址自增有效优化指令数和指令操作。

一般地,输入数据宽度为128比特或256比特,输出数据宽度为32比特、128比特或256比特。

本申请的实施例可提供为方法、系统、或计算机程序产品,以上所述仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案、对本发明的修改和变型均属于本发明的保护范围。