GaN基LED外延片及其制备方法、LED

文献发布时间:2024-04-18 19:48:15

技术领域

本发明涉及半导体技术领域,尤其涉及一种GaN基LED外延片及其制备方法、LED。

背景技术

现有的GaN基LED外延片,通常采用Al

发明内容

本发明的目的在于针对已有的技术现状,提供一种GaN基LED外延片及其制备方法、LED,本发明的外延片设置复合位错阻挡层,通过复合位错阻挡层的位错阻挡基层、位错扭转层及晶格扭转层共同作用,有效阻挡刃位错和螺旋位错的向上延伸,降低位错密度,提高晶格质量,减少漏电,提高多量子阱层的辐射复合效率,提升发光二极管的发光效率。

为达到上述目的,本发明采用如下技术方案:

首先,本发明提供一种GaN基LED外延片的制备方法,包括:

提供衬底;

在所述衬底上沉积外延层;

所述外延层包括沿外延方向依次沉积于所述衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

所述复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,所述位错阻挡基层为掺杂Mg的AlN层,所述位错扭转层为Si

在一些实施例中,所述位错阻挡基层的厚度为1nm~100nm,所述所述位错扭转层的厚度为1nm~50nm,所述晶格扭转层的厚度为1nm~100nm。

在一些实施例中,所述位错阻挡基层中,Mg的含量为0.01~0.1。

在一些实施例中,所述晶格扭转层中,Cr的含量为0.01~0.5,Mg的含量为0.01~0.1。

在一些实施例中,所述复合位错阻挡层的生长气氛为N

在一些实施例中,所述复合位错阻挡层的生长压力为100torr~150torr,生长温度为800℃~1100℃。

在一些实施例中,所述衬底与所述复合位错阻挡层之间还设有缓冲层及非掺杂GaN层,所述多量子阱层上沿外延方向沉积有电子阻挡层及P型GaN层。

其次,本发明还提供一种GaN基LED外延片,所述外延层包括沿外延方向依次设置于所述衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

所述复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,所述位错阻挡基层为掺杂Mg的AlN层,所述位错扭转层为Si

在一些实施例中,所述位错阻挡基层中,Mg的含量为0.01~0.1;所述晶格扭转层中,Cr的含量为0.01~0.5,Mg的含量为0.01~0.1。

再者,本发明提供一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

本发明的有益效果在于:

本发明中,在N型GaN层之前先沉积复合位错阻挡层,其中,复合位错阻挡层由位错阻挡基层、位错扭转层及晶格扭转层组成,位错阻挡基层为掺杂Mg的AlN层,由于AlN的晶格常数小于GaN,能够在GaN上形成致薄膜,同时,通过掺杂少量的Mg弥补AlN层的晶格缺陷,阻挡底层位错向多量子阱层延伸;其次,在经过位错阻挡基层的初步过滤后,部分的螺旋位错仍然会穿过AlN层,因此,在位错阻挡基层上设置位错扭转层,位错扭转层采用Si

附图说明

图1为本发明的GaN基LED外延片的制备方法的流程图。

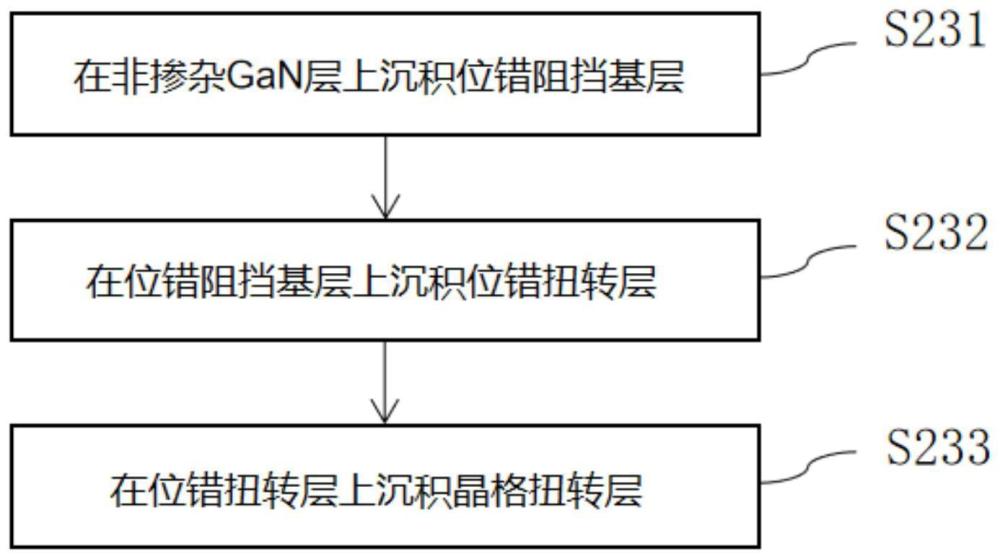

图2为本发明的复合位错阻挡层的制备方法的流程图。

图3为本发明的GaN基LED外延片的结构示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面对本发明作进一步地详细描述。

首先,参见图1及图2所示,本发明公开一种GaN基LED外延片的制备方法,包括:

S10.提供衬底1;

S20.在衬底1上沉积外延层;

外延层包括沿外延方向依次沉积于所述衬底1上的缓冲层2、非掺杂GaN层3、复合位错阻挡层4、N型GaN层5及多量子阱层6;

复合位错阻挡层4包括沿外延方向依次设置的位错阻挡基层41、位错扭转层42及晶格扭转层43,位错阻挡基层41为掺杂Mg的AlN层,位错扭转层42为Si

本实施例中,在N型GaN层5之前先沉积复合位错阻挡层4,其中,复合位错阻挡层4由位错阻挡基层41、位错扭转层42及晶格扭转层43组成,位错阻挡基层41为掺杂Mg的AlN层,由于AlN的晶格常数小于GaN,能够在GaN上形成致薄膜,同时,通过掺杂少量的Mg弥补AlN层的晶格缺陷,阻挡底层位错向多量子阱层6延伸;其次,在经过位错阻挡基层41的初步过滤后,部分的螺旋位错仍然会穿过AlN层,因此,在位错阻挡基层41上设置位错扭转层42,位错扭转层42采用Si

示例性的,衬底1可为蓝宝石衬底、SiO

其中,位错阻挡基层41的厚度为1nm~100nm,位错扭转层42的厚度为1nm~50nm,晶格扭转层43的厚度为1nm~100nm,示例性的,位错阻挡基层41的厚度为1nm、5nm、10nm、20nm、30nm、40nm、50nm、60nm、70nm、80nm、90nm或100nm,但不限于此,位错阻挡基层41太薄起不到阻挡位错的作用,太厚则会因AlN的势垒过高导致LED电压升高;示例性的,位错扭转层42的厚度为1nm、5nm、10nm、20nm、30nm、40nm或50nm,但不限于此,位错扭转层42太厚反而会导致晶格失配增加,后续沉积的外延层晶体质量会下降;示例性的,晶格扭转层43的厚度为1nm、5nm、10nm、20nm、30nm、40nm、50nm、60nm、70nm、80nm、90nm或100nm,但不限于此,晶格扭转层43太薄则起不到扭转晶格的作用,太厚则浪费原材,导致不必要的成本升高。

其中,位错阻挡基层41中,Mg的含量为0.01~0.1,示例性的,Mg的含量为0.01、0.03、0.05、0.07、0.09或0.1,但不限于此,AlN层中少量掺杂Mg能够弥补AlN层的晶格缺陷,Mg掺杂过量反而会导致位错阻挡基层41的位错阻挡效果下降。

其中,晶格扭转层43中,Cr的含量为0.01~0.5,Mg的含量为0.01~0.1,示例性的,Cr的含量为0.01、0.05、0.1、0.2、0.3、0.4或0.5,但不限于此,Mg的含量为0.01、0.03、0.05、0.06、0.08或0.1,但不限于此,Cr及Mg的含量过高会降低晶格质量。

其中,复合位错阻挡层4的生长气氛为N

其中,复合位错阻挡层4的生长压力为100torr~150torr,生长温度为800℃~1100℃,示例性的,生长压力为100torr、120torr、140torr或150torr,但不限于此,较低的生长压力能够促进复合位错阻挡层4的二维生长,提高阻挡位错的能力,降低底层延伸至多量子阱层6的缺陷密度;示例性的,生长温度为800℃、850℃、900℃、950℃、1000℃或1100℃,但不限于此,合适的生长温度能够提高复合位错阻挡层4的晶体质量,温度太低,位错密度增加,温度太高,则会破坏其他外延层晶体质量。

其中,衬底1与复合位错阻挡层4之间还设有缓冲层2及非掺杂GaN层3,多量子阱层6上沿外延方向沉积有电子阻挡层7及P型GaN层8。

其中,缓冲层2可为AlN/GaN复合缓冲层,电子阻挡层7可为AlInGaN层。

其中,步骤S20在衬底1上沉积外延层的具体步骤如下:

S21.在衬底1上沉积缓冲层2:

缓冲层2可为AlN/GaN复合缓冲层,其中,AlN子层可采用溅射法沉积于衬底1上,GaN子层可采用MOCVD法沉积于AlN子层上,AlN子层提供了与衬底1取向相同的成核中心,释放了GaN和衬底1之间的晶格失配产生的应力以及热膨胀系数失配所产生的热应力,进一步的生长提供了平整的成核表面,减少其成核生长的接触角使岛状生长的GaN晶粒在较小的厚度内能连成面,转变为二维外延生长。

S22.在缓冲层2上沉积非掺杂GaN层3:

非掺杂GaN层3可采用MOCVD法沉积于缓冲层2,生长温度为1050℃~1200℃,生长压力为100torr~600torr,厚度为1μm~5μm。

S23.在非掺杂GaN层3上沉积复合位错阻挡层4:

复合位错阻挡层4的制备方法为MBE法、HVPE法、VPE法或MOCVD法中的任意一种或多种组合。

S231.在非掺杂GaN层3上沉积位错阻挡基层41;

S232.在位错阻挡基层41上沉积位错扭转层42;

S233.在位错扭转层42上沉积晶格扭转层43。

S24.在复合位错阻挡层4上沉积N型GaN层5:

N型GaN层5可采用MOCVD法沉积于复合位错阻挡层4上,N型GaN层5中,Si掺杂浓度为1.0×10

S25.在N型GaN层5上沉积多量子阱层6:

多量子阱层6可为周期性交替堆叠的InGaN量子阱层和AlGaN量子垒层,周期数为5个~20个,单个InGaN量子阱层的厚度为2nm~5nm,单个AlGaN量子垒层的厚度为5nm~15nm。

S26.在多量子阱层6上沉积电子阻挡层7:

电子阻挡层7可为AlInGaN层,厚度为10nm~40nm。

S27.在电子阻挡层7上沉积P型GaN层8:

P型GaN层8中,Mg的掺杂浓度为1.0×10

其次,参见图3所示,本发明还公开一种GaN基LED外延片,包括衬底1及设置于衬底1上的外延层,外延层包括沿外延方向依次设置于所述衬底1上的缓冲层2、非掺杂GaN层3、复合位错阻挡层4、N型GaN层5及多量子阱层6;

复合位错阻挡层4包括沿外延方向依次设置的位错阻挡基层41、位错扭转层42及晶格扭转层43,位错阻挡基层41为掺杂Mg的AlN层,位错扭转层42为Si

其中,位错阻挡基层41中,Mg的含量为0.01~0.1;晶格扭转层43中,Cr的含量为0.01~0.5,Mg的含量为0.01~0.1。

再者,本发明公开一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

下面结合附图及实施例对本发明作进一步说明:

实施例1

本实施例公开一种GaN基LED外延片的制备方法,包括:

提供衬底;

在衬底上沉积外延层;

外延层包括沿外延方向依次沉积于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

其中,位错阻挡基层的厚度为50nm,位错扭转层的厚度为20nm,晶格扭转层的厚度为60nm。

其中,位错阻挡基层中,Mg的含量为0.1。

其中,晶格扭转层中,Cr的含量为0.5,Mg的含量为0.1。

其中,复合位错阻挡层的生长气氛为N

其中,复合位错阻挡层的生长压力为150torr。

其中,衬底与复合位错阻挡层之间还设有缓冲层及非掺杂GaN层,多量子阱层上沿外延方向沉积有电子阻挡层及P型GaN层。

其中,在衬底上沉积外延层的具体步骤如下:

S21.在衬底上沉积缓冲层:缓冲层为AlN/GaN复合缓冲层。

S22.在缓冲层上沉积非掺杂GaN层。

S23.在非掺杂GaN层上沉积复合位错阻挡层:

S231.在非掺杂GaN层上沉积位错阻挡基层;

S232.在位错阻挡基层上沉积位错扭转层;

S233.在位错扭转层上沉积晶格扭转层。

S24.在复合位错阻挡层上沉积N型GaN层。

S25.在N型GaN层上沉积多量子阱层:

多量子阱层为周期性交替堆叠的InGaN量子阱层和AlGaN量子垒层。

S26.在多量子阱层上沉积电子阻挡层:电子阻挡层为AlInGaN层。

S27.在电子阻挡层上沉积P型GaN层。

本实施例还公开一种GaN基LED外延片,外延层包括沿外延方向依次设置于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

本实施例公开一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

实施例2

本实施例公开一种GaN基LED外延片的制备方法,包括:

提供衬底;

在衬底上沉积外延层;

外延层包括沿外延方向依次沉积于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

其中,位错阻挡基层的厚度为50nm,位错扭转层的厚度为20nm,晶格扭转层的厚度为60nm。

其中,位错阻挡基层中,Mg的含量为0.05。

其中,晶格扭转层中,Cr的含量为0.25,Mg的含量为0.05。

其中,复合位错阻挡层的生长气氛为N

其中,复合位错阻挡层的生长压力为150torr。

其中,衬底与复合位错阻挡层之间还设有缓冲层及非掺杂GaN层,多量子阱层上沿外延方向沉积有电子阻挡层及P型GaN层。

其中,在衬底上沉积外延层的具体步骤如下:

S21.在衬底上沉积缓冲层:缓冲层为AlN/GaN复合缓冲层。

S22.在缓冲层上沉积非掺杂GaN层。

S23.在非掺杂GaN层上沉积复合位错阻挡层:

S231.在非掺杂GaN层上沉积位错阻挡基层;

S232.在位错阻挡基层上沉积位错扭转层;

S233.在位错扭转层上沉积晶格扭转层。

S24.在复合位错阻挡层上沉积N型GaN层。

S25.在N型GaN层上沉积多量子阱层:

多量子阱层为周期性交替堆叠的InGaN量子阱层和AlGaN量子垒层。

S26.在多量子阱层上沉积电子阻挡层:电子阻挡层为AlInGaN层。

S27.在电子阻挡层上沉积P型GaN层。

本实施例还公开一种GaN基LED外延片,外延层包括沿外延方向依次设置于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

本实施例公开一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

实施例3

本实施例公开一种GaN基LED外延片的制备方法,包括:

提供衬底;

在衬底上沉积外延层;

外延层包括沿外延方向依次沉积于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

其中,位错阻挡基层的厚度为50nm,位错扭转层的厚度为20nm,晶格扭转层的厚度为60nm。

其中,位错阻挡基层中,Mg的含量为0.01。

其中,晶格扭转层中,Cr的含量为0.01,Mg的含量为0.01。

其中,复合位错阻挡层的生长气氛为N

其中,复合位错阻挡层的生长压力为150torr。

其中,衬底与复合位错阻挡层之间还设有缓冲层及非掺杂GaN层,多量子阱层上沿外延方向沉积有电子阻挡层及P型GaN层。

其中,在衬底上沉积外延层的具体步骤如下:

S21.在衬底上沉积缓冲层:缓冲层为AlN/GaN复合缓冲层。

S22.在缓冲层上沉积非掺杂GaN层。

S23.在非掺杂GaN层上沉积复合位错阻挡层:

S231.在非掺杂GaN层上沉积位错阻挡基层;

S232.在位错阻挡基层上沉积位错扭转层;

S233.在位错扭转层上沉积晶格扭转层。

S24.在复合位错阻挡层上沉积N型GaN层。

S25.在N型GaN层上沉积多量子阱层:

多量子阱层为周期性交替堆叠的InGaN量子阱层和AlGaN量子垒层。

S26.在多量子阱层上沉积电子阻挡层:电子阻挡层为AlInGaN层。

S27.在电子阻挡层上沉积P型GaN层。

本实施例还公开一种GaN基LED外延片,外延层包括沿外延方向依次设置于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

本实施例公开一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

实施例4

本实施例公开一种GaN基LED外延片的制备方法,包括:

提供衬底;

在衬底上沉积外延层;

外延层包括沿外延方向依次沉积于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

其中,位错阻挡基层的厚度为100nm,位错扭转层的厚度为50nm,晶格扭转层的厚度为100nm。

其中,位错阻挡基层中,Mg的含量为0.1。

其中,晶格扭转层中,Cr的含量为0.5,Mg的含量为0.1。

其中,复合位错阻挡层的生长气氛为N

其中,复合位错阻挡层的生长压力为150torr。

其中,衬底与复合位错阻挡层之间还设有缓冲层及非掺杂GaN层,多量子阱层上沿外延方向沉积有电子阻挡层及P型GaN层。

其中,在衬底上沉积外延层的具体步骤如下:

S21.在衬底上沉积缓冲层:缓冲层为AlN/GaN复合缓冲层。

S22.在缓冲层上沉积非掺杂GaN层。

S23.在非掺杂GaN层上沉积复合位错阻挡层:

S231.在非掺杂GaN层上沉积位错阻挡基层;

S232.在位错阻挡基层上沉积位错扭转层;

S233.在位错扭转层上沉积晶格扭转层。

S24.在复合位错阻挡层上沉积N型GaN层。

S25.在N型GaN层上沉积多量子阱层:

多量子阱层为周期性交替堆叠的InGaN量子阱层和AlGaN量子垒层。

S26.在多量子阱层上沉积电子阻挡层:电子阻挡层为AlInGaN层。

S27.在电子阻挡层上沉积P型GaN层。

本实施例还公开一种GaN基LED外延片,外延层包括沿外延方向依次设置于衬底上的缓冲层、非掺杂GaN层、复合位错阻挡层、N型GaN层及多量子阱层;

复合位错阻挡层包括沿外延方向依次设置的位错阻挡基层、位错扭转层及晶格扭转层,位错阻挡基层为掺杂Mg的AlN层,位错扭转层为Si

本实施例公开一种LED,包括上述的GaN基LED外延片的制备方法制得的外延层。

对比例1

本对比例与实施例1的不同之处在于,复合位错阻挡层不设置位错阻挡基层,相应省略制备该层的步骤。

对比例2

本对比例与实施例1的不同之处在于,复合位错阻挡层不设置位错扭转层,相应省略制备该层的步骤。

对比例3

本对比例与实施例1的不同之处在于,复合位错阻挡层不设置晶格扭转层,相应省略制备该层的步骤。

对比例4

本对比例与实施例1的不同之处在于,将复合位错阻挡层替换为AlGaN位错阻挡层,厚度为130nm。

XRD测试及光电性能测试:

测试方法:

1)取实施例1~实施例4及对比例1~对比例4制得的外延片,采用XRD测试其(002)面及(102)面,其中,(002)面主要表征外延片的刃位错情况,(102)面主要表征外延片的螺旋位错情况。

2)将实施例1~实施例4及对比例1~对比例4的外延结构制备成芯片,在120mA/60mA电流下测试,获取实施例1~实施例4及对比例1~对比例3相对于对比例4的光效提升率。

3)测试结果如下:

以上所述仅是本发明的较佳实施例而已,并非对本发明作任何形式上的限制,虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明,任何熟悉本领域的技术人员在不脱离本发明技术方案范围内,当可利用上述提示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明方案的范围内。